# **Analog/HDMI Dual Display Interface**

AD9880

#### **FEATURES**

Analog/HDMI dual interface Supports high bandwidth digital content protection **RGB-to-YCbCr 2-way color conversion Automated clamping level adjustment** 1.8 V/3.3 V power supply 100-lead LQFP Pb-free package **RGB and YCbCr output formats Analog interface**

8-bit triple ADC 100 MSPS maximum conversion rate Macrovision® detection 2:1 input mux **Full sync processing** Sync detect for hot plugging Midscale clamping

**HDMI v 1.1, DVI v 1.0** 150 MHz HDMI receiver Supports high bandwidth digital content protection (HDCP 1.1)

Digital audio interface

Digital video interface

**HDMI 1.1-compatible audio interface** S/PDIF (IEC90658-compatible) digital audio output Multichannel I2S audio output (up to 8 channels)

#### **APPLICATIONS**

**Advanced TV HDTV Projectors LCD** monitor

### **GENERAL DESCRIPTION**

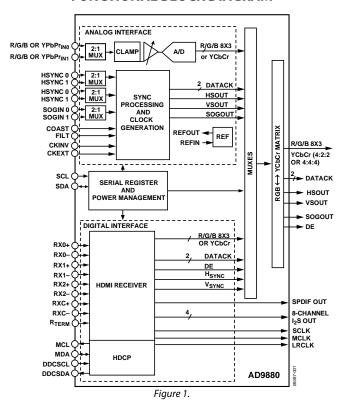

The AD9880 offers designers the flexibility of an analog interface and high definition multimedia interface (HDMI) receiver integrated on a single chip. Also included is support for high bandwidth digital content protection (HDCP).

## **Analog Interface**

The AD9880 is a complete 8-bit 150 MSPS monolithic analog interface optimized for capturing component video (YPbPr) and RGB graphics signals. Its 150 MSPS encode rate capability and full power analog bandwidth of 330 MHz supports all HDTV formats (up to 1080 p) and FPD resolutions up to SXGA (1280  $\times$  1024 @ 75 Hz).

The analog interface includes a 150 MHz triple ADC with internal 1.25 V reference, a phase-locked loop (PLL), and programmable gain, offset, and clamp control. The user provides only 1.8 V and 3.3 V power supplies, analog input, and Hsync. Three-state

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

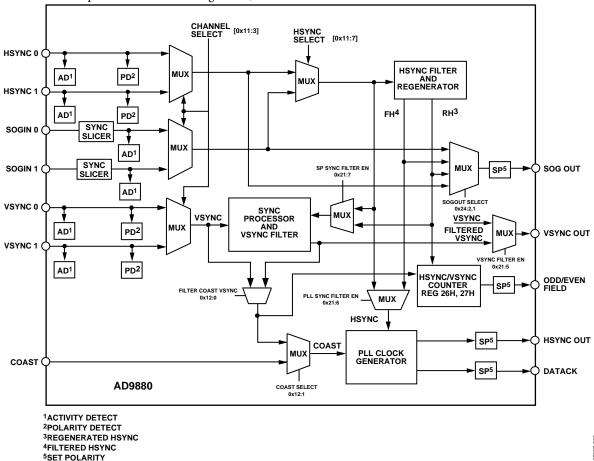

#### FUNCTIONAL BLOCK DIAGRAM

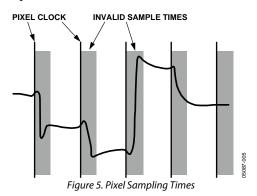

CMOS outputs can be powered from 1.8 V to 3.3 V. The AD9880's on-chip PLL generates a pixel clock from Hsync. Pixel clock output frequencies range from 12 MHz to 150 MHz. PLL clock jitter is typically less than 700 ps p-p at 150 MHz. The AD9880 also offers full sync processing for composite sync and sync-on-green (SOG) applications.

#### **Digital Interface**

The AD9880 contains a HDMI 1.1-compatible receiver and supports all HDTV formats (up to 1080 p and 720 p) and display resolutions up to SXGA (1280 × 1024 @75 Hz). The receiver features an intrapair skew tolerance of up to one full clock cycle. With the inclusion of HDCP, displays can now receive encrypted video content. The AD9880 allows for authentication of a video receiver, decryption of encoded data at the receiver, and renewability of the authentication during transmission, as specified by the HDCP v 1.1 protocol.

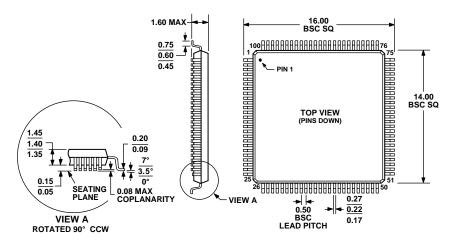

Fabricated in an advanced CMOS process, the AD9880 is provided in a space-saving, 100-lead LQFP surface-mount Pb-free plastic package and is specified over the 0°C to 70°C temperature range.

© 2005 Analog Devices, Inc. All rights reserved.

# **TABLE OF CONTENTS**

| Specifications                               |

|----------------------------------------------|

| Analog Interface Electrical Characteristics  |

| Digital Interface Electrical Characteristics |

| Absolute Maximum Ratings6                    |

| Explanation of Test Levels6                  |

| ESD Caution6                                 |

| Pin Configuration and Function Descriptions7 |

| Design Guide12                               |

| General Description12                        |

| Digital Inputs                               |

| Analog Input Signal Handling12               |

| Hsync and Vsync Inputs12                     |

| Serial Control Port                          |

| Output Signal Handling12                     |

| Clamping                                     |

| Timing                                       |

| HDMI Receiver                                |

| DE Generator                                 |

| 4:4:4 to 4:2:2 Filter                        |

| Audio PLL Setup21                            |

| Audio Board Level Muting                     |

| Timing Diagrams21                              |

|------------------------------------------------|

| 2-Wire Serial Register Map                     |

| 2-Wire Serial Control Register Detail          |

| Chip Identification                            |

| PLL Divider Control                            |

| Clock Generator Control                        |

| Input Gain                                     |

| Input Offset                                   |

| Sync                                           |

| Coast and Clamp Controls                       |

| Status of Detected Signals                     |

| Polarity Status                                |

| BT656 Generation                               |

| Macrovision                                    |

| Color Space Conversion                         |

| 2-Wire Serial Control Port56                   |

| PCB Layout Recommendations                     |

| Color Space Converter (CSC) Common Settings 60 |

| Outline Dimensions                             |

| Ordering Guide62                               |

# **REVISION HISTORY**

8/05—Revision 0: Initial Version

# **SPECIFICATIONS**

# **ANALOG INTERFACE ELECTRICAL CHARACTERISTICS**

$V_{\text{DD}}, V_{\text{D}} = 3.3 \text{ V}, DV_{\text{DD}} = PV_{\text{DD}} = 1.8 \text{ V}, ADC \ clock} = \text{maximum}.$

Table 1.

|                                         | AD9880KSTZ-100 |            | 100                   | AD           |               |                       |            |               |               |

|-----------------------------------------|----------------|------------|-----------------------|--------------|---------------|-----------------------|------------|---------------|---------------|

| Parameter                               | Temp           | Test Level | Min                   | Тур          | Max           | Min                   | Тур        | Max           | Unit          |

| RESOLUTION                              |                |            |                       | 8            |               |                       | 8          |               | Bits          |

| DC ACCURACY                             |                |            |                       |              |               |                       |            |               |               |

| Differential Nonlinearity               | 25°C           | I          |                       | -0.6         | +1.6/-<br>1.0 |                       | ±0.7       | +1.8/-<br>1.0 | LSB           |

| Integral Nonlinearity                   | 25°C           | 1          |                       | ±1.0         | ±2.1          |                       | ±1.1       | ±2.25         | LSB           |

| No Missing Codes                        | Full           |            |                       | Guaranteed   | '<br>k        |                       | Guaranteed | ŀ             |               |

| ANALOG INPUT                            |                |            |                       |              |               |                       |            |               |               |

| Input Voltage Range                     |                |            |                       |              |               |                       |            |               |               |

| Minimum                                 | Full           | VI         |                       |              | 0.5           |                       |            | 0.5           | V р-р         |

| Maximum                                 | Full           | VI         | 1.0                   |              |               | 1.0                   |            |               | V p-p         |

| Gain Tempco                             | +25°C          | V          |                       | 100          |               |                       | 220        |               | ppm/°C        |

| Input Bias Current                      | +25°C          | V          |                       | 0.2          |               |                       | 1          |               | μΑ            |

| Input Full-Scale Matching               | 25C            | VI         |                       | 1.25         | 5             |                       | 1.25       | 5             | %FS           |

|                                         | Full           | VI         |                       | 1.50         | 7             |                       | 1.50       | 7             | %FS           |

| Offset Adjustment Range                 | Full           | V          |                       | 50           |               |                       | 50         |               | %FS           |

| SWITCHING PERFORMANCE <sup>1</sup>      |                |            |                       |              |               |                       |            |               |               |

| Maximum Conversion Rate                 | Full           | VI         | 100                   |              |               | 150                   |            |               | MSPS          |

| Minimum Conversion Rate                 | Full           | VI         |                       |              | 10            |                       |            | 10            | MSPS          |

| Data to Clock Skew                      | Full           | IV         | -0.5                  |              | +2.0          | -0.5                  |            | +2.0          | ns            |

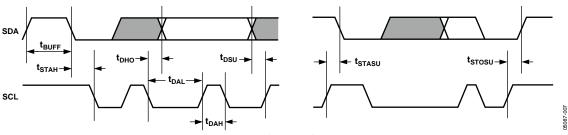

| Serial Port Timing                      |                |            |                       |              |               |                       |            |               |               |

| t <sub>BUFF</sub>                       | Full           | VI         | 4.7                   |              |               | 4.7                   |            |               | μs            |

| t <sub>stah</sub>                       | Full           | VI         | 4.0                   |              |               | 4.0                   |            |               | μs            |

| t <sub>DHO</sub>                        | Full           | VI         | 0                     |              |               | 0                     |            |               | μs            |

| t <sub>DAL</sub>                        | Full           | VI         | 4.7                   |              |               | 4.7                   |            |               | μs            |

| t <sub>DAH</sub>                        | Full           | VI         | 4.0                   |              |               | 4.0                   |            |               | μs            |

| t <sub>DSU</sub>                        | Full           | VI         | 250                   |              |               | 250                   |            |               | ns            |

| t <sub>stasu</sub>                      | Full           | VI         | 4.7                   |              |               | 4.7                   |            |               | μs            |

| <b>t</b> stosu                          | Full           | VI         | 4.0                   |              |               | 4.0                   |            |               | μs            |

| HSYNC Input Frequency                   | Full           | VI         | 15                    |              | 110           | 15                    |            | 110           | KHz           |

| Maximum PLL Clock Rate                  | Full           | VI         | 100                   |              |               | 150                   |            |               | MHz           |

| Minimum PLL Clock Rate                  | Full           | IV         |                       |              | 12            | 1.55                  |            | 12            | MHz           |

| PLL Jitter                              | +25°C          | IV         |                       | 700          | '-            |                       | 700        |               | ps p-p        |

| Sampling Phase Tempco                   | Full           | IV         |                       | 15           |               |                       | 15         |               | ps/°C         |

| DIGITAL INPUTS: (5V tolerant)           |                |            |                       | 1.5          |               |                       | 1.5        |               | P3, C         |

| Input Voltage, High (V <sub>H</sub> )   | Full           | VI         | 2.6                   |              |               | 2.6                   |            |               | V             |

| Input Voltage, Low (V <sub>IL</sub> )   | Full           | VI         | 2.0                   |              | 0.8           | 2.0                   |            | 0.8           | V             |

| Input Current, High (I <sub>H</sub> )   | Full           | V          |                       | -82          | 0.0           |                       | -82        | 0.0           | μA            |

| Input Current, Low (I <sub>IL</sub> )   | Full           | V          |                       | 82           |               |                       | 82         |               | μΑ            |

| Input Carrent, Low (IIL)                | 25°C           | V          |                       | 3            |               |                       | 3          |               | pF            |

| DIGITAL OUTPUTS                         | 25 C           | V          |                       | <del> </del> | +             |                       | +          |               | P'            |

| Output Voltage, High (V <sub>OH</sub> ) | Full           | VI         | V <sub>DD</sub> – 0.1 |              |               | V <sub>DD</sub> - 0.1 |            |               | V             |

| Output Voltage, Fight (Vol.)            | Full           | VI         | טטע — ט. ו            |              | 0.4           | - טט א – טע א         |            | 0.4           | V             |

| Duty Cycle, DATACK                      | Full           | V          | 45                    | 50           | 55            | 45                    | 50         | 55            | <b>v</b><br>% |

| Output Coding                           | i uli          | , v        | 75                    | Binary       |               | "                     | Binary     |               | /0            |

| POWER SUPPLY                            |                |            |                       | טווומו y     | +             | +                     | טווומן y   |               |               |

| V <sub>D</sub> Supply Voltage           | Full           | IV         | 3.15                  | 3.3          | 2 /17         | 3.15                  | 3.3        | 2.47          | V             |

| DV <sub>DD</sub> Supply Voltage         |                |            |                       |              | 3.47          |                       |            | 3.47          |               |

| DVDD Supply voltage                     | Full           | IV         | 1.7                   | 1.8          | 1.9           | 1.7                   | 1.8        | 1.9           | V             |

|                                                      |      |            | А   | D9880KST2 | <b>Z-100</b> | А   | D9880KST2 | <b>'</b> -150    |      |

|------------------------------------------------------|------|------------|-----|-----------|--------------|-----|-----------|------------------|------|

| Parameter                                            | Temp | Test Level | Min | Тур       | Max          | Min | Тур       | Max              | Unit |

| V <sub>DD</sub> Supply Voltage                       | Full | IV         | 1.7 | 3.3       | 3.47         | 1.7 | 3.3       | 3.47             | V    |

| PV <sub>DD</sub> Supply Voltage                      | Full | IV         | 1.7 | 1.8       | 1.9          | 1.7 | 1.8       | 1.9              | V    |

| I <sub>D</sub> Supply Current (V <sub>D</sub> )      | 25°C | VI         |     | 260       | 300          |     |           | 330              | mA   |

| I <sub>DVDD</sub> Supply Current (DV <sub>DD</sub> ) | 25°C | VI         |     | 45        | 60           |     |           | 85               |      |

| IDD Supply Current (VDD) <sup>2</sup>                | 25°C | VI         |     | 37        | 100³         |     |           | 130 <sup>3</sup> | mA   |

| IP <sub>VDD</sub> Supply Current (P <sub>VDD</sub> ) | 25°C | VI         |     | 10        | 15           |     |           | 20               | mA   |

| Total Power                                          | Full | VI         |     | 1.1       | 1.4          |     | 1.15      | 1.4              | W    |

| Power-Down Dissipation                               | Full | VI         |     | 130       |              |     | 130       |                  | mW   |

| DYNAMIC PERFORMANCE                                  |      |            |     |           |              |     |           |                  |      |

| Analog Bandwidth, Full                               | 25°C | V          |     | 330       |              |     | 330       |                  | MHz  |

| Power                                                |      |            |     |           |              |     |           |                  |      |

| Signal-to-Noise Ratio (SNR)                          | 25°C | I          |     | 46        |              |     | 46        |                  | dB   |

| Without Harmonics                                    | Full | V          |     | 45        |              |     | 45        |                  | dB   |

| $f_{\text{IN}} = 40.7 \text{ MHz}$                   |      |            |     |           |              |     |           |                  |      |

| Crosstalk                                            | Full | V          |     | 60        |              |     | 60        |                  | dBc  |

| THERMAL CHARACTERISTICS                              |      |            |     |           |              |     |           |                  |      |

| $\theta_{JA}$ -Junction-to-Ambient                   |      | V          |     | 35        |              |     | 35        |                  | °C/W |

# **DIGITAL INTERFACE ELECTRICAL CHARACTERISTICS**

$V_{DD}$  =  $V_{D}$  = 3.3 V,  $DV_{DD}$  =  $PV_{DD}$  = 1.8 V, ADC clock = maximum.

Table 2.

|                                                       |               |                     | AD9880KSTZ-100      |     | AD9880KSTZ-150 |     |     |     |      |

|-------------------------------------------------------|---------------|---------------------|---------------------|-----|----------------|-----|-----|-----|------|

| Parameter                                             | Test<br>Level | Conditions          | Min                 | Тур | Max            | Min | Тур | Max | Unit |

| RESOLUTION                                            |               |                     |                     | 8   |                |     | 8   |     | Bit  |

| DC DIGITAL I/O Specifications                         |               |                     |                     |     |                |     |     |     |      |

| High-Level Input Voltage, (V <sub>IH</sub> )          | VI            |                     | 2.5                 |     |                | 2.5 |     |     | V    |

| Low-Level Input Voltage, (V <sub>IL</sub> )           | VI            |                     |                     |     | 0.8            |     |     | 0.8 | V    |

| High-Level Output Voltage, (V <sub>OH</sub> )         | VI            |                     | $V_{\text{DD}}-0.1$ |     |                |     |     |     | V    |

| Low-Level Output Voltage, (Vol)                       | VI            |                     | $V_{\text{DD}}-0.1$ |     | 0.1            |     |     | 0.1 | V    |

| DC SPECIFICATIONS                                     |               |                     |                     |     |                |     |     |     |      |

| Output High Level                                     | IV            | Output drive = high |                     | 36  |                |     | 36  |     | mA   |

| $(I_{OHD})$ $(V_{OUT} = V_{OH})$                      | IV            | Output drive = low  |                     | 24  |                |     | 24  |     | mA   |

| Output Low Level                                      | IV            | Output drive = high |                     | 12  |                |     | 12  |     | mA   |

| $I_{OLD}$ , $(V_{OUT} = V_{OL})$                      | IV            | Output drive = low  |                     | 8   |                |     | 8   |     | mA   |

| DATACK High Level                                     | IV            | Output drive = high |                     | 40  |                |     | 40  |     | mA   |

| $V_{OHC}$ , $(V_{OUT} = V_{OH})$                      | IV            | Output drive = low  |                     | 20  |                |     | 20  |     | mA   |

| DATACK Low Level                                      | IV            | Output drive = high |                     | 30  |                |     | 30  |     | mA   |

| $V_{OLC}$ , $(V_{OUT} = V_{OL})$                      | IV            | Output drive = low  |                     | 15  |                |     | 15  |     | mA   |

| Differential Input Voltage, Single Ended<br>Amplitude | IV            |                     | 75                  |     | 700            | 75  |     | 700 | mV   |

<sup>&</sup>lt;sup>1</sup> Drive strength = high.

<sup>2</sup> DATACK load = 15 pF, data load = 5 pF.

<sup>3</sup> Specified current and power values with a worst case pattern (on/off).

|                                                                       |               |                                               | AD9880KSTZ-100 |     |      | AD9880KSTZ-150 |     |      |                 |  |

|-----------------------------------------------------------------------|---------------|-----------------------------------------------|----------------|-----|------|----------------|-----|------|-----------------|--|

| Parameter                                                             | Test<br>Level | Conditions                                    | Min            | Тур | Max  | Min            | Тур | Max  | Unit            |  |

| POWER SUPPLY                                                          |               |                                               |                |     |      |                | 7.  |      |                 |  |

| V <sub>D</sub> Supply Voltage                                         | IV            |                                               | 3.15           | 3.3 | 3.47 | 3.15           | 3.3 | 3.47 | V               |  |

| V <sub>DD</sub> Supply Voltage                                        | IV            |                                               | 1.7            | 3.3 | 347  | 1.7            | 3.3 | 347  | V               |  |

| DV <sub>DD</sub> Supply Voltage                                       | IV            |                                               | 1.7            | 1.8 | 1.9  | 1.7            | 1.8 | 1.9  | V               |  |

| PV <sub>DD</sub> Supply Voltage                                       | IV            |                                               | 1.7            | 1.8 | 1.9  | 1.7            | 1.8 | 1.9  | V               |  |

| I <sub>VD</sub> Supply Current (Typical Pattern) <sup>1</sup>         | V             |                                               |                | 80  | 100  |                | 80  | 110  | mA              |  |

| I <sub>VDD</sub> Supply Current (Typical Pattern) <sup>2</sup>        | V             |                                               |                | 40  | 100³ |                | 55  | 175* |                 |  |

| I <sub>DVDD</sub> Supply Current (Typical Pattern) <sup>1, 4</sup>    | V             |                                               |                | 88  | 110  |                | 110 | 145  | mA              |  |

| I <sub>PVDD</sub> Supply Current (Typical Pattern) <sup>1</sup>       | V             |                                               |                | 26  | 35   |                | 30  | 40   | mA              |  |

| Power-Down Supply Current (IPD)                                       | VI            |                                               |                | 130 |      |                | 130 |      | mA              |  |

| AC SPECIFICATIONS                                                     |               |                                               |                |     |      |                |     |      |                 |  |

| Intrapair (+ to $-$ ) Differential Input Skew ( $T_{DPS}$ )           | IV            |                                               |                |     |      |                |     | 360  | pS              |  |

| Channel to Channel Differential Input<br>Skew (T <sub>CCS</sub> )     | IV            |                                               |                |     |      |                |     | 6    | Clock<br>Period |  |

| Low-to-High Transition Time for Data and Controls ( $D_{LHT}$ )       | IV            | Output drive = high;<br>$C_L = 10 \text{ pF}$ |                |     |      |                |     | 900  | ps              |  |

|                                                                       | IV            | Output drive = low;<br>$C_L = 5 \text{ pF}$   |                |     |      |                |     | 1300 | ps              |  |

| Low-to-High Transition Time for DATACK (D <sub>LHT</sub> )            | IV            | Output drive = high;<br>$C_L = 10 \text{ pF}$ |                |     |      |                |     | 650  | ps              |  |

|                                                                       | IV            | Output drive = low;<br>$C_L = 5 pF$           |                |     |      |                |     | 1200 | ps              |  |

| High-to-Low Transition Time for Data and Controls (D <sub>HLT</sub> ) | IV            | Output drive = high;<br>$C_L = 10 \text{ pF}$ |                |     |      |                |     | 850  | ps              |  |

|                                                                       | IV            | Output drive = low;<br>$C_L = 5 pF$           |                |     |      |                |     | 1250 | ps              |  |

| High-to-Low Transition Time for DATACK (D <sub>HLT</sub> )            | IV            | Output drive = high;<br>$C_L = 10 \text{ pF}$ |                |     |      |                |     | 800  | ps              |  |

|                                                                       | IV            | Output drive = low;<br>$C_L = 5 \text{ pF}$   |                |     |      |                |     | 1200 | ps              |  |

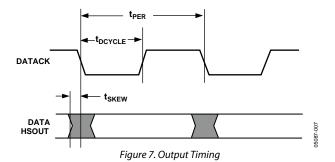

| Clock to Data Skew <sup>5</sup> (T <sub>SKEW</sub> )                  | IV            |                                               | -0.5           |     | 2.0  | -0.5           |     | 2.0  | ns              |  |

| Duty Cycle, DATACK <sup>5</sup>                                       | IV            |                                               | 45             | 50  |      |                |     | 55   | %               |  |

| DATACK Frequency (F <sub>CIP</sub> )                                  | VI            |                                               | 20             |     |      |                |     | 150  | MHz             |  |

<sup>&</sup>lt;sup>1</sup> The typical pattern contains a gray scale area, output drive = high. Worst case pattern is alternating black and white pixels. <sup>2</sup> The typical pattern contains a gray scale area, output drive = high. <sup>3</sup> Specified current and power values with a worst case pattern (on/off). <sup>4</sup> DATACK load = 10 pF, data load = 5 pF. <sup>5</sup> Drive strength = high.

# **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                             | Rating           |

|---------------------------------------|------------------|

| VD                                    | 3.6 V            |

| VDD                                   | 3.6 V            |

| DVDD                                  | 1.98 V           |

| PVDD                                  | 1.98 V           |

| Analog Inputs                         | $V_D$ to 0.0 $V$ |

| Digital Inputs                        | 5 V to 0.0 V     |

| Digital Output Current                | 20 mA            |

| Operating Temperature                 | −25°C to +85°C   |

| Storage Temperature                   | −65°C to + 150°C |

| Maximum Junction Temperature          | 150°C            |

| Maximum Case Temperature              | 150°C            |

| · · · · · · · · · · · · · · · · · · · | ·                |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **EXPLANATION OF TEST LEVELS**

### **Test Level**

- I. 100% production tested.

- II. 100% production tested at 25°C and sample tested at specified temperatures.

- III. Sample tested only.

- IV. Parameter is guaranteed by design and characterization testing.

- V. Parameter is a typical value only.

- VI. 100% production tested at 25°C; guaranteed by design and characterization testing.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 4. Complete Pinout List**

| Pin Type | Pin No. | Mnemonic          | Function                                      | Value          |

|----------|---------|-------------------|-----------------------------------------------|----------------|

| INPUTS   | 79      | R <sub>AIN0</sub> | Analog Input for Converter R Channel 0        | 0.0 V to 1.0 V |

|          | 77      | R <sub>AIN1</sub> | Analog Input for Converter R Channel 1        | 0.0 V to 1.0 V |

|          | 74      | GAINO             | Analog Input for Converter G Channel 0        | 0.0 V to 1.0 V |

|          | 71      | G <sub>AIN1</sub> | Analog Input for Converter G Channel 1        | 0.0 V to 1.0 V |

|          | 68      | B <sub>AIN0</sub> | Analog Input for Converter B Channel 0        | 0.0 V to 1.0 V |

|          | 66      | B <sub>AIN1</sub> | Analog Input for Converter B Channel 1        | 0.0 V to 1.0 V |

|          | 64      | HSYNC0            | Horizontal SYNC Input for Channel 0           | 3.3 V CMOS     |

|          | 63      | HSYNC1            | Horizontal SYNC Input for Channel 1           | 3.3 V CMOS     |

|          | 61      | VSYNC0            | Vertical SYNC Input for Channel 0             | 3.3 V CMOS     |

|          | 60      | VSYNC1            | Vertical SYNC Input for Channel 1             | 3.3 V CMOS     |

|          | 73      | SOGIN0            | Input for Sync-on-Green Channel 0             | 0.0 V to 1.0 V |

|          | 70      | SOGIN1            | Input for Sync-on-Green Channel 1             | 0.0 V to 1.0 V |

|          | 62      | EXTCLK            | External Clock Input—Shares Pin with COAST    | 3.3 V CMOS     |

|          | 62      | COAST             | PLL COAST Signal Input—Shares Pin with EXTCLK | 3.3 V CMOS     |

|          | 81      | PWRDN             | Power-Down Control                            | 3.3 V CMOS     |

| Pin Type                   | Pin No.                   | Mnemonic         | Function                                            | Value           |

|----------------------------|---------------------------|------------------|-----------------------------------------------------|-----------------|

| OUTPUTS                    | 92 to 99                  | RED [7:0]        | Outputs of Red Converter, Bit 7 is MSB              | V <sub>DD</sub> |

|                            | 2 to 9                    | GREEN [7:0]      | Outputs of Green Converter, Bit 7 is MSB            | $V_{DD}$        |

|                            | 12 to 19                  | BLUE [7:0]       | Outputs of Blue Converter, Bit 7 is MSB             | $V_{DD}$        |

|                            | 89                        | DATACK           | Data Output Clock                                   | $V_{DD}$        |

|                            | 87                        | HSOUT            | HSYNC Output Clock (Phase-Aligned with DATACK)      | $V_{DD}$        |

|                            | 85                        | VSOUT            | VSYNC Output Clock (Phase-Aligned with DATACK)      | $V_{DD}$        |

|                            | 86                        | SOGOUT           | SOG Slicer Output                                   | $V_{DD}$        |

|                            | 84                        | O/E FIELD        | Odd/Even Field Output                               | $V_{DD}$        |

| REFERENCES                 | 57                        | FILT             | Connection For External Filter Components For PLL   |                 |

| POWER SUPPLY               | 80, 76, 72,<br>67, 45, 33 | V <sub>D</sub>   | Analog Power Supply and DVI Terminators             | 3.3 V           |

|                            | 100, 90, 10               | $V_{DD}$         | Output Power Supply                                 | 1.8 V to 3.3 V  |

|                            | 59, 56, 54                | $PV_{DD}$        | PLL Power Supply                                    | 1.8 V           |

|                            | 48, 32, 30                | DV <sub>DD</sub> | Digital Logic Power Supply                          | 1.8 V           |

|                            |                           | GND              | Ground                                              | 0 V             |

| CONTROL                    | 83                        | SDA              | Serial Port Data I/O                                | 3.3 V CMOS      |

|                            | 82                        | SCL              | Serial Port Data Clock                              | 3.3 V CMOS      |

| HDCP                       | 49                        | DDC_SCL          | HDCP Slave Serial Port Data Clock                   | 3.3 V CMOS      |

|                            | 50                        | DDC_SDA          | HDCP Slave Serial Port Data I/O                     | 3.3 V CMOS      |

|                            | 51                        | MCL              | HDCP Master Serial Port Data Clock                  | 3.3 V CMOS      |

|                            | 52                        | MDA              | HDCP Master Serial Port Data I/O                    | 3.3 V CMOS      |

| AUDIO DATA OUTPUTS         | 28                        | S/PDIF           | S/PDIF Digital Audio Output                         | V <sub>DD</sub> |

|                            | 27                        | 1250             | I <sup>2</sup> S Audio (Channels 1, 2)              | $V_{DD}$        |

|                            | 26                        | I2S1             | I <sup>2</sup> S Audio (Channels 3, 4)              | $V_{DD}$        |

|                            | 25                        | 1252             | I <sup>2</sup> S Audio (Channels 5, 6)              | $V_{DD}$        |

|                            | 24                        | 1253             | I <sup>2</sup> S Audio (Channels 7, 8)              | $V_{DD}$        |

|                            | 20                        | MCLKIN           | External Reference Audio Clock In                   | $V_{DD}$        |

|                            | 21                        | MCLKOUT          | Audio Master Clock Output                           | $V_{DD}$        |

|                            | 22                        | SCLK             | Audio Serial Clock Output                           | $V_{DD}$        |

|                            | 23                        | LRCLK            | Data Output Clock For Left And Right Audio Channels | $V_{DD}$        |

| DIGITAL VIDEO DATA         | 35                        | Rx0+             | Digital Input Channel 0 True                        | TMDS            |

|                            | 34                        | Rx0-             | Digital Input Channel 0 Complement                  | TMDS            |

|                            | 38                        | Rx1+             | Digital Input Channel 1 True                        | TMDS            |

|                            | 37                        | Rx1-             | Digital Input Channel 1 Complement                  | TMDS            |

|                            | 41                        | Rx2+             | Digital Input Channel 2 True                        | TMDS            |

|                            | 40                        | Rx2-             | Digital Input Channel 2 Complement                  | TMDS            |

| DIGITAL VIDEO CLOCK INPUTS | 43                        | RxC+             | Digital Data Clock True                             | TMDS            |

|                            | 44                        | RxC-             | Digital Data Clock Complement                       | TMDS            |

| DATA ENABLE                | 88                        | DE               | Data Enable                                         | 3.3 V CMOS      |

| RTERM                      | 46                        | RTERM            | Sets Internal Termination Resistance                | 500Ω            |

**Table 5. Pin Function Descriptions**

|                   | ion Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| INPUTS            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R <sub>AIN0</sub> | Analog Input for the Red Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| G <sub>AINO</sub> | Analog Input for the Green Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| B <sub>AIN0</sub> | Analog Input for the Blue Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| R <sub>AIN1</sub> | Analog Input for the Red Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $G_{AIN1}$        | Analog Input for the Green Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| B <sub>AIN1</sub> | Analog Input for Blue Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

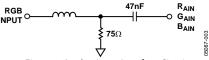

|                   | High impedance inputs that accept the red, green, and blue channel graphics signals, respectively. The three channels are identical, and can be used for any colors, but colors are assigned for convenient reference. They accommodate input signals ranging from 0.5 V to 1.0 V full scale. Signals should be ac-coupled to these pins to support clamp operation. (see Figure 3 for an input reference circuit).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Rx0+              | Digital Input Channel 0 True.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Rx0-              | Digital Input Channel 0 Complement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Rx1+              | Digital Input Channel 1 True.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Rx1-              | Digital Input Channel 1 Complement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Rx2+              | Digital Input Channel 2 True.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Rx2-              | Digital input Channel 2 Complement. These six pins receive three pairs TMDS (Transition Minimized Differential Signaling) pixel data (at 10X the pixel rate) from a digital graphics transmitter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RxC+              | Digital Data Clock True.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RxC-              | Digital Data Clock Complement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                   | This clock pair receives a TMDS clock at 1× pixel data rate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| HSYNC0            | Horizontal Sync Input Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HSYNC1            | Horizontal Sync Input Channel 1.  These inputs receive a logic signal that establishes the horizontal timing reference and provides the frequency reference for pixel clock generation. The logic sense of this pin is controlled by serial register 0x12 Bits 5:4 (Hsync polarity). Only the leading edge of Hsync is active; the trailing edge is ignored. When Hsync Polarity = 0, the falling edge of Hsync is used. When Hsync Polarity = 1, the rising edge is active. The input includes a Schmitt trigger for noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                  |

| VSYNC0            | Vertical Sync Input Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VSYNC1            | Vertical Sync Input Channel 1. These are the inputs for vertical sync.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SOGIN0            | Sync-On-Green Input Channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SOGIN1            | Sync-On-Green Input Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

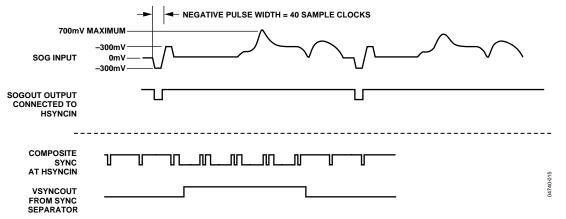

|                   | These inputs are provided to assist with processing signals with embedded sync, typically on the green channel. The pin is connected to a high speed comparator with an internally generated threshold. The threshold level can be programmed in 10 mV steps to any voltage between 10 mV and 330 mV above the negative peak of the input signal. The default voltage threshold is 150 mV. When connected to an ac-coupled graphics signal with embedded sync, it produces a noninverting digital output on SOGOUT. (This is usually a composite sync signal, containing both vertical and horizontal sync (Hsync) information that must be separated before passing the horizontal sync signal to Hsync.) When not used, this input should be left unconnected. For more details on this function and how it should be configured, refer to the Hsync and Vsync Inputs section.                                                       |

| EXTCLK/COAST      | Coast Input to Clock Generator (Optional). This input may be used to cause the pixel clock generator to stop synchronizing with Hsync and continue producing a clock at its current frequency and phase. This is useful when processing signals from sources that fail to produce horizontal sync pulses during the vertical interval. The Coast signal is generally not required for PC-generated signals. The logic sense of this pin is controlled by Coast polarity (Register 0x18, Bits 6:5). When not used, this pin may be grounded and input Coast polarity programmed to 1 (Register 0x18, Pin 5), or tied high (to $V_D$ through a 10 K $\Omega$ resistor) and input Coast polarity programmed to 0. Input Coast polarity defaults to 1 at power-up. This pin is shared with the EXTCLK function, which does not affect Coast functionality. For more details on Coast, see the description in the Clock Generation section. |

| EXTCLK/COAST      | External Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   | This allows the insertion of an external clock source rather than the internally generated PLL locked clock. This pin is shared with the Coast function, which will not affect EXTCLK functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pin                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWRDN                | Power-Down Control/Three-State Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                      | The function of this pin is programmable via Register 0x26 [2:1].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FILT                 | External Filter Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

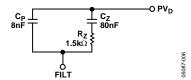

|                      | For proper operation, the pixel clock generator PLL requires an external filter. Connect the filter shown in Figure 6 to this pin. For optimal performance, minimize noise and parasitics on this node. For more information see the section on PCB Layout Recommendations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OUTPUTS              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| HSOUT                | Horizontal Sync Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                      | A reconstructed and phase-aligned version of the Hsync input. Both the polarity and duration of this output can be programmed via serial bus registers. By maintaining alignment with DATACK and Data, data timing with respect to horizontal sync can always be determined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VSOUT                | Vertical Sync Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                      | The separated Vsync from a composite signal or a direct pass through of the Vsync signal. The polarity of this output can be controlled via serial bus bit (Register 0x24 [6]).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SOGOUT               | Sync-On-Green Slicer Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

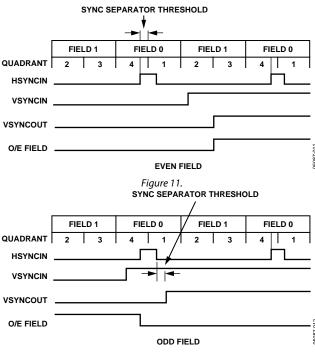

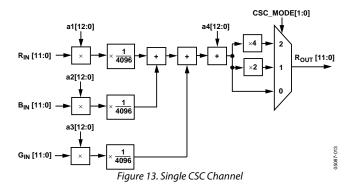

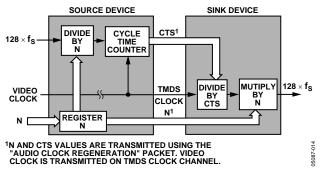

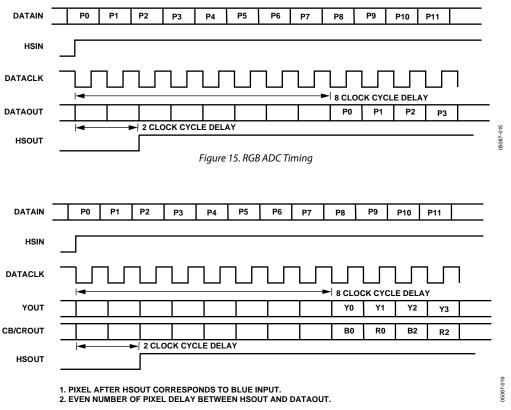

|                      | This pin outputs one of four possible signals (controlled by Register 0x1D [1:0]): raw SOG, raw Hsync, regenerated Hsync from the filter, or the filtered Hsync. See the Sync processing block diagram (see Figure 8) to view how this pin is connected. (Note: besides slicing off SOG, the output from this pin is not processed on the AD9880. Vsync separation is performed via the sync separator.                                                                                                                                                                                                                                                                                                                                                                                                                   |