# 10-Bit Current output D to A Converter

# **DAC100**

## 1.0 SCOPE

This specification documents the detail requirements for space qualified product manufactured on Analog Devices, Inc.'s QML certified line per MIL-PRF-38535 Level V except as modified herein. The manufacturing flow described in the STANDARD SPACE LEVEL PRODUCTS PROGRAM brochure is to be considered a part of this specification. This brochure can be found at: http://www.analog.com/aerospace

This data sheet specifically details the space grade version of this product. A more detailed operational description and a complete data sheet for commercial product grades can be found at <a href="http://www.analog.com/DAC100">www.analog.com/DAC100</a>

### 2.0 **Part Number**. The complete part number(s) of this specification follow:

| Part Number | Description                                              |  |  |

|-------------|----------------------------------------------------------|--|--|

| DAC100-703Q | 10-Bit Current output D to A Converter                   |  |  |

| DAC100-713Q | Radiation tested, 10-Bit Current output D to A Converter |  |  |

#### 2.1 Case Outline.

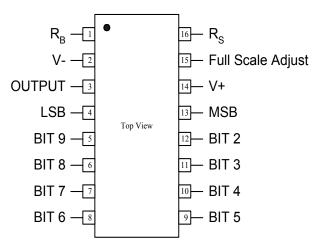

LetterDescriptive designatorCase Outline (Lead Finish per MIL-PRF-38535)QGDIP1-T1616-Lead ceramic dual-in-line package (CERDIP)

ASD0011162

Rev. F

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.326.8703 © 2008 Analog Devices, Inc. All rights reserved.

# **DAC100**

### **3.0** Absolute Maximum Ratings. (TA = 25°C, unless otherwise noted)

| V+ supply to V- supply                      | 0V to 36V |

|---------------------------------------------|-----------|

| V+ supply to output                         |           |

| V- supply to output                         |           |

| Power dissipation                           |           |

| Logic inputs to outputs                     |           |

| Operating temperature range                 |           |

| Storage temperature range                   |           |

| Lead temperature (soldering, 60 sec.)       |           |

| Dice junction temperature (T <sub>J</sub> ) |           |

#### **3.1** Thermal Characteristics:

Thermal resistance, CERDIP (Q) Package Junction-to-case ( $\Theta_{JC}$ ) = 29°C/W Max Junction-to-ambient ( $\Theta_{JA}$ ) = 91 °C/W Max Thermal resistance, FLATPAK (N) Package Junction-to-case ( $\Theta_{JC}$ ) = 22°C/W Max Junction-to-ambient ( $\Theta_{JA}$ ) = 90 °C/W Max

| TABLE I                            |                   |                                                                                                                                                 |               |              |              |       |

|------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|--------------|-------|

| Parameter                          | Symbol            | Conditions <u>1</u> /                                                                                                                           | Sub-<br>group | Limit<br>Min | Limit<br>Max | Units |

| Power supply current               | I+                | V <sub>IH</sub> = 2.1V                                                                                                                          |               |              | 8.33         | mA    |

|                                    | I-                | $V_{IH} = 2.1 V$                                                                                                                                | 1, 2, 3       |              | 8.33         |       |

| Full range output voltage          | V <sub>FR</sub>   | $V_{IL} = 0.7V$ , Full Adjust pin tied to V-                                                                                                    | 1, 2, 3       | 10.0         | 11.1         | V     |

| Zero scale output voltage          | V <sub>ZS</sub>   | $V_{IH} = 2.1 V$                                                                                                                                | 1, 2, 3       |              | ±.013        | %FS   |

| Integral nonlinearity              | NL                | $\pm \frac{1}{2}$ LSB – 9 Bits                                                                                                                  | 1, 2, 3       |              | ±0.1         |       |

| Full scale temperature coefficient | TCV <sub>FR</sub> | $V_{IL} = 0.7V$ , Full Scale Adjust pin tied to V-                                                                                              | 8             |              | ±60          | ppm/° |

| Logic inputs high                  | V <sub>IH</sub>   | $V_{IN} = 2.1V$ to 3V (all inputs)<br>Measured with respect to output<br>pin allowing $\leq \pm \frac{1}{2}$ LSB change<br>with $\Delta V_{IN}$ | 1, 2, 3       | 2.1          |              | V     |

| Logic inputs low                   | V <sub>IL</sub>   | $V_{IN} = 0.7V$ to 0V (all inputs)<br>Measured with respect to output<br>pin allowing $\leq \pm \frac{1}{2}$ LSB change<br>with $\Delta V_{IN}$ | 1, 2, 3       |              | 0.7          |       |

| Logic input current high           | I <sub>IH</sub>   | $V_{IH} = 6.0V$ , Each Input                                                                                                                    | 1, 2, 3       |              | 5            | μΑ    |

| Logic input current low            | I <sub>IL</sub>   | $V_{IL} = 0V$ , Each Input                                                                                                                      | 1, 2, 3       |              | 5            |       |

| Power supply sensitivity           | PSS               | $V_{IL} = 0.7V \text{ (all inputs) } V_S = \pm 6V \text{ to } \pm 18V$                                                                          | 1, 2, 3       |              | ±0.1         | %/V   |

| Monotonicity <u>2</u> /            | $\Delta I_{O}$    | Measured at each major carry code point                                                                                                         | 1             | 0            |              | μΑ    |

| Settling time $\underline{3}/$     | T <sub>SHL</sub>  | $R_L = 1K\Omega, C_L \le 10pF$                                                                                                                  | 9             |              | 375          | nS    |

#### 4.0 Electrical Table: See notes at end of table

Table I notes:

- <u>1/</u> V<sub>S</sub> = ±15V, unless otherwise specified.

- 2/ The change in output current either increases or remains the same for an increasing digital input code.

- <u>3/</u> Output within  $\pm \frac{1}{2}$  LSB of 10-bit accuracy final settled nominal value of V<sub>OUT</sub>.

Input pulse characteristics:

Input frequency = 1MHz square wave, 50% duty cycle.

Input amplitude = 0V to 2.1V

Input signal =  $t_r$ ,  $t_f \le 20$  nS

Measurement referenced to input High-to-Low Transition. DUT Settling Time to ±0.05 % FS

# **DAC100**

#### 4.1 Electrical Test Requirements:

| Table II                                                                  |                         |  |  |

|---------------------------------------------------------------------------|-------------------------|--|--|

| MIL-STD-883 Test<br>Requirements                                          | Subgroups (see table I) |  |  |

| Interim electrical parameters<br>(pre Burn-In)                            | 1                       |  |  |

| Final Electrical Test Parameters                                          | 1, 2, 3, 8 <u>1/ 2/</u> |  |  |

| Group A Test Requirements                                                 | 1, 2, 3, 8, 9           |  |  |

| Group C Test Requirements                                                 | 1 <u>2/</u>             |  |  |

| Group D Test Requirements                                                 | 1                       |  |  |

| * PDA applies to Subgroup 1 only. No other subgroups are included in PDA. |                         |  |  |

<u>1/</u>PDA applies to subgroup 1. Deltas not included in PDA <u>2/</u>See table III for deltas. See table I for test conditions.

| Table III       |                     |                      |                |       |

|-----------------|---------------------|----------------------|----------------|-------|

| TEST<br>ITLE    | BURN-IN<br>ENDPOINT | LIFETEST<br>ENDPOINT | DELTA<br>LIMIT | UNITS |

| V <sub>FR</sub> | $10.55 \pm 0.55$    | $10.55 \pm 0.75$     | ±0.2           | V     |

| V <sub>ZS</sub> | ±0.013              | ±0.018               | $\pm 0.005$    | %FS   |

| I+              | 8.33                | 8.33                 | ±10%           | mA    |

| I-              | 8.33                | 8.33                 | ±10%           | mA    |

#### 4.2 Table III. Burn-in test delta limits.

### 5.0 Life Test/Burn-In Circuit:

- 5.1 HTRB is not applicable for this drawing.

- 5.2 Burn-in is per MIL-STD-883 Method 1015 test condition B.

- 5.3 Steady state life test is per MIL-STD-883 Method 1005.

# DAC100

| Rev | Description of Change                                                           | Date           |

|-----|---------------------------------------------------------------------------------|----------------|

| Α   | Initiate                                                                        | 30-Jun-00      |

| В   | Update web address                                                              | Feb. 18, 2002  |

| С   | Update web address. Add Group C and D to table II. Add life test endpoint based | Feb. 28, 2003  |

|     | on delta to table III.                                                          |                |

| D   | Delete Burn-In circuit                                                          | Aug. 5, 2003   |

| Е   | Update header/footer & add to 1.0 Scope description                             | Feb. 21,2008   |

| F   | Remove minimum Dice Junction Temp. range in 3.0 Absolute Max. Ratings           | March 31, 2008 |

|     |                                                                                 |                |

|     |                                                                                 |                |

|     |                                                                                 |                |

© 2008 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective companies. Printed in the U.S.A. 03/08

www.analog.com

ASD0011162 Rev. F | Page 5 of 5