| LTR                                                                                                                                    |                                                                               |                                                                  |         |                                                     |                                                                       |                                                                                   |                                     | 1       | REVISI | ONS                   |                   |                                          |                              |                                                       |                                   |                                                  |                                       |                                 |                         |         |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|---------|-----------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------|---------|--------|-----------------------|-------------------|------------------------------------------|------------------------------|-------------------------------------------------------|-----------------------------------|--------------------------------------------------|---------------------------------------|---------------------------------|-------------------------|---------|

|                                                                                                                                        | DESCRIPTION                                                                   |                                                                  |         |                                                     |                                                                       |                                                                                   | DATE (YR-MO-DA)                     |         |        |                       | APPROVED          |                                          |                              |                                                       |                                   |                                                  |                                       |                                 |                         |         |

| А                                                                                                                                      | Add                                                                           | device                                                           | type 02 | 2. Dele                                             | te devi                                                               | ce clas                                                                           | s M ref                             | ference | s ro   |                       |                   |                                          |                              |                                                       | C. S.                             | AFFLE                                            |                                       |                                 |                         |         |

|                                                                                                                                        |                                                                               |                                                                  |         |                                                     |                                                                       |                                                                                   |                                     |         |        |                       |                   |                                          |                              |                                                       |                                   |                                                  |                                       |                                 |                         |         |

| 1                                                                                                                                      |                                                                               |                                                                  |         |                                                     |                                                                       |                                                                                   |                                     |         |        |                       |                   |                                          |                              |                                                       |                                   |                                                  |                                       |                                 |                         |         |

| REV                                                                                                                                    |                                                                               |                                                                  |         | 1                                                   | 1                                                                     | T                                                                                 | T                                   |         |        |                       |                   | 1                                        | T                            | 1                                                     |                                   | T                                                |                                       | 1                               | T                       | ,<br>T  |

| REV                                                                                                                                    |                                                                               |                                                                  |         |                                                     |                                                                       |                                                                                   |                                     |         |        |                       |                   |                                          |                              |                                                       |                                   | <u> </u>                                         |                                       |                                 | <u> </u>                |         |

| REV<br>SHEET<br>REV                                                                                                                    | A                                                                             | A                                                                | A       | A                                                   | A                                                                     | A                                                                                 |                                     |         |        |                       |                   |                                          |                              |                                                       |                                   |                                                  |                                       |                                 |                         |         |

| SHEET                                                                                                                                  | A<br>15                                                                       | A<br>16                                                          | A<br>17 | A<br>18                                             | A<br>19                                                               | A<br>20                                                                           |                                     |         |        |                       |                   |                                          |                              |                                                       |                                   |                                                  |                                       |                                 |                         |         |

| SHEET<br>REV                                                                                                                           | 15                                                                            |                                                                  |         |                                                     | 19                                                                    | -                                                                                 | A                                   | A       | A      | A                     | A                 |                                          |                              | A                                                     | A                                 | A                                                | A                                     | A                               | A                       | A       |

| SHEET<br>REV<br>SHEET                                                                                                                  | 15                                                                            |                                                                  |         | 18                                                  | 19<br>/                                                               | -                                                                                 | A<br>1                              | A<br>2  | A<br>3 | A 4                   | A<br>5            | A<br>6                                   | A<br>7                       | A<br>8                                                | A<br>9                            | A<br>10                                          | A<br>11                               | A<br>12                         | A<br>13                 | A<br>14 |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A                                                                           | 15<br>5                                                                       | 16                                                               |         | 18<br>REV<br>SHE<br>PRE<br>RIC                      | 19<br>/<br>EET<br>PAREE<br>CK OFF                                     | 20<br>D BY<br>FICER                                                               |                                     |         |        |                       | L                 | 6                                        | 7<br>DLA I                   | 8<br>LAND                                             | 9<br><b>AND</b>                   | 10                                               | 11<br><b>RITIM</b>                    | 12<br>E                         |                         |         |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STA<br>MICR                                                            | 15<br>S<br>ANDAF                                                              | 16<br>RD<br>CUIT                                                 |         | 18<br>REV<br>SHE<br>RIC<br>CHE<br>RA                | 19<br>/<br>EET<br>CK OFF<br>CK OFF<br>CKED<br>JESH F                  | 20<br>D BY<br>FICER<br>BY<br>PITHAE                                               | 1                                   |         |        |                       | L                 | 6<br>CC                                  | 7<br>DLA I<br>DLUM           | 8<br>LAND                                             | 9<br>) AND<br>, OHI0              | 10                                               | 11<br>RITIM<br>218-3                  | 12<br>E<br>990                  | 13                      |         |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STA<br>MICR<br>DR<br>THIS DRAW<br>FOR U                                | 15<br>S<br>ANDAF<br>OCIRC<br>AWIN<br>ING IS A<br>USE BY                       |                                                                  | 17      | 18<br>REV<br>SHE<br>RIC<br>CHE<br>RA.<br>APPI<br>CH | 19<br>/<br>EET<br>PAREE<br>CK OFF<br>CKED<br>JESH F<br>ROVEL<br>ARLES | 20<br>D BY<br>FICER<br>BY<br>PITHAE<br>D BY<br>S F. SAI                           | 1<br>DIA<br>FFLE                    | 2       |        | 4<br>MIC              | 5<br>CROC         | 6<br>CC<br><u>http:</u><br>CIRCI         | 7<br>DLA I<br>DLUM<br>://www | 8<br>IBUS<br>w.land                                   | 9<br>O AND<br>, OHIO<br>dandi     | 10<br>D MAF<br>O 432<br>mariti                   | 11<br><b>RITIM</b><br>218-39<br>ime.d | 12<br>E<br>990<br>Ila.mi        | <u>13</u>               |         |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STA<br>MICR<br>DR<br>THIS DRAW<br>FOR U                                | 15<br>S<br>ANDAF<br>OCIRC<br>AWIN<br>ING IS A<br>USE BY<br>ARTMEN<br>ENCIES ( | TIG<br>RD<br>CUIT<br>G<br>VAILAI<br>ALL<br>ITS<br>OF THE         | BLE     | 18<br>REV<br>SHE<br>RIC<br>CHE<br>RA.<br>APPI<br>CH | 19<br>/<br>EET<br>PAREE<br>CK OFF<br>CKED<br>JESH F<br>ROVEL<br>ARLES | 20<br>D BY<br>FICER<br>BY<br>PITHAE<br>D BY<br>S F. SAI                           | 1<br>DIA                            | 2       |        | 4<br>MIC<br>HAI       | 5<br>CROC<br>RDEI | 6<br>CC<br>http:<br>CIRCI<br>NED,        | 7<br>DLA I<br>DLUM<br>://www | 8<br>IAND<br>IBUS<br>w.lan<br>LINE                    | 9<br><b>AND</b><br>, OHIC<br>dand | 10<br>D MAF<br>O 432<br>mariti                   | 11<br>RITIM<br>218-3<br>ime.d         | 12<br><b>E</b><br>990<br>Ila.mi | <u>13</u>               | 14      |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STA<br>MICR<br>DR<br>THIS DRAW<br>FOR I<br>DEP/<br>AND AGE<br>DEPARTME | 15<br>S<br>ANDAF<br>OCIRC<br>AWIN<br>ING IS A<br>USE BY<br>ARTMEN<br>ENCIES ( | 16<br>RD<br>CUIT<br>G<br>VAILAI<br>ALL<br>ITS<br>OF THE<br>DEFEN | BLE     | 18<br>REV<br>SHE<br>RIC<br>CHE<br>RA<br>APPI<br>CH  | 19<br>/<br>EET<br>PAREE<br>CK OFF<br>CKED<br>JESH F<br>ROVEL<br>ARLES | 20<br>D BY<br>FICER<br>BY<br>PITHAC<br>D BY<br>S F. SAI<br>APPRC<br>11-0<br>LEVEL | 1<br>DIA<br>FFLE<br>DVAL D<br>D3-21 | 2       |        | 4<br>MIC<br>HAI<br>AC | 5<br>CROC<br>RDEI | 6<br>CC<br>http:<br>CIRCI<br>NED,<br>MUL | 7<br>DLA I<br>DLUM<br>://www | 8<br>ILAND<br>IBUS<br>w.lan<br>LINE<br>LL 2:1<br>EXEF | 9<br><b>AND</b><br>, OHIC<br>dand | 10<br>D MAF<br>O 432<br>mariti<br>RADIA<br>DE BA | 11<br>RITIM<br>218-39<br>ime.d        | 12<br><b>E</b><br>990<br>Ila.mi | 13<br>[<br>-H,<br>_ICOI | 14      |

# 1. SCOPE

1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device class Q) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels is reflected in the PIN.

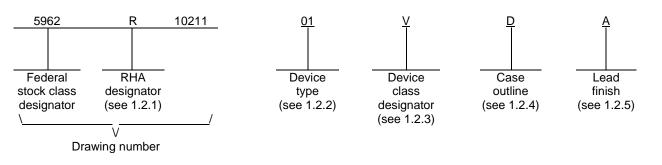

1.2 <u>PIN</u>. The PIN is as shown in the following example:

1.2.1 <u>RHA designator</u>. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number | Circuit function                                                    |

|-------------|----------------|---------------------------------------------------------------------|

| 01          | AD8182         | Radiation hardened, dual 2:1, wide<br>bandwidth, active multiplexer |

| 02          | AD8182         | Radiation hardened, dual 2:1, wide<br>bandwidth, active multiplexer |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

| Device class               | Device requirements documentation                                   |

|----------------------------|---------------------------------------------------------------------|

| Q or V                     | Certification and qualification to MIL-PRF-38535                    |

| 1.2.4 Case outline(s). The | e case outline(s) are as designated in MIL-STD-1835 and as follows: |

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style |

|----------------|------------------------|------------------|---------------|

| D              | GDFP1-F14              | 14               | Flat pack     |

1.2.5 Lead finish. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                     | 5962-10211 |

|----------------------------------------------------|-----------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>A | SHEET 2    |

| 1.3 | Absolute | maximum | ratings. | 1/ |

|-----|----------|---------|----------|----|

|     |          |         |          |    |

|            | Supply voltage ( $+V_S$ to $-V_S$ )<br>Input voltage ( $V_{IN}$ )                                                               |                     |                                          |                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------|-------------------|

|            | Power dissipation (P <sub>D</sub> )                                                                                             |                     | -                                        |                   |

|            | Junction temperature (T <sub>J</sub> )                                                                                          |                     |                                          |                   |

|            | Lead temperature (soldering, 10 seconds)                                                                                        |                     |                                          |                   |

|            | Storage temperature range                                                                                                       |                     |                                          |                   |

|            | Thermal resistance, junction-to-case ( $\theta_{JC}$ )                                                                          |                     |                                          |                   |

|            | Thermal resistance, junction-to-ambient ( $\theta_{JA}$ )                                                                       |                     |                                          |                   |

| 1          | .4 <u>Recommended operating conditions</u> .                                                                                    |                     |                                          |                   |

|            | Supply voltages (symmetrical operation recommended): (+                                                                         |                     |                                          |                   |

|            |                                                                                                                                 | -,                  | 4 V to -6 V                              |                   |

|            | Ambient operating temperature range (T <sub>A</sub> )                                                                           |                     | 55°C to +125°C                           |                   |

| 1          | .4.1 <u>Operating performance characteristics</u> . $T_A = +25^{\circ}C$ .                                                      |                     |                                          |                   |

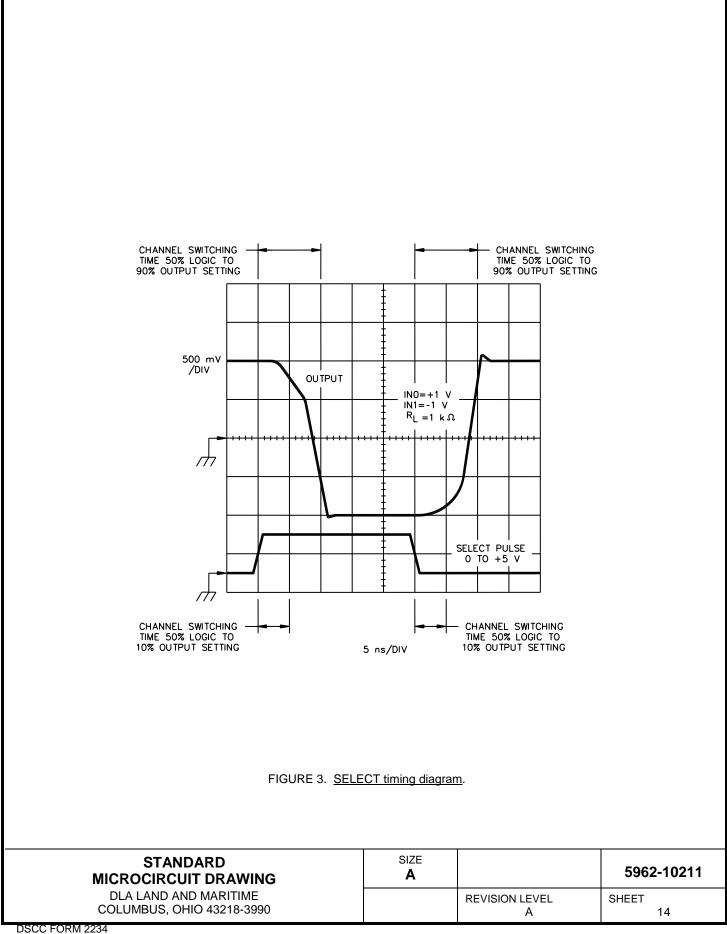

|            | Switching characteristics: $R_L = 1 k\Omega$ .                                                                                  |                     |                                          |                   |

|            | Channel switching time 50% logic to 10% output settling                                                                         |                     |                                          |                   |

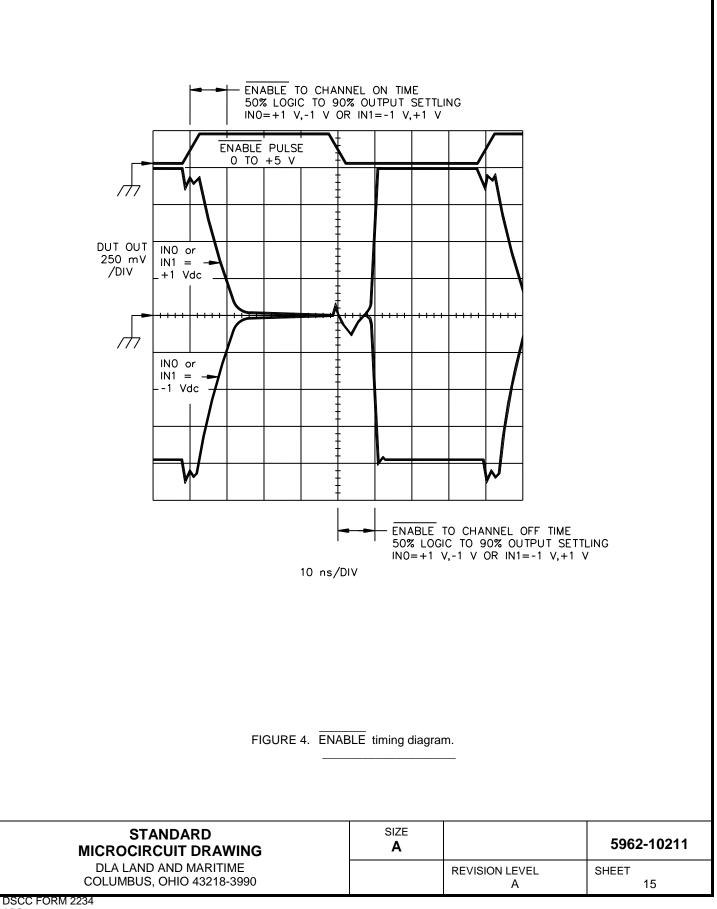

|            | Channel switching time 50% logic to 90% output settling<br>ENABLE to channel on time 50% logic to 90% output set                |                     | 10 ns <u>5</u> /                         |                   |

|            | -1 V or $IN1 = -1$ V, +1 V                                                                                                      |                     | 10.5 ns 6/                               |                   |

|            | ENABLE to channel off time 50% logic to 90% output se                                                                           |                     | _                                        |                   |

|            | -1 V or IN1 = -1 V, +1 V                                                                                                        |                     | 11 ns <u>6</u> /                         |                   |

|            | Distortion / noise performance:                                                                                                 |                     |                                          |                   |

|            | Voltage noise, f = 10 kHz - 30 MHz, $R_L$ = 2 k $\Omega$                                                                        |                     | 4.5 nV / √Hz                             |                   |

|            | Total harmonic distortion, $f_{C} = 10 \text{ MHz}$ , $V_{O} = 2 \text{ V}_{PP}$ , $R_{L} =$                                    |                     |                                          |                   |

|            | Output observatoriation                                                                                                         |                     |                                          |                   |

|            | Output characteristics:<br>Disabled output capacitance                                                                          |                     | 1.9 pF                                   |                   |

|            | Input characteristics:                                                                                                          |                     |                                          |                   |

|            | Input characteristics:<br>Disabled input capacitance                                                                            |                     |                                          |                   |

|            | Enabled input capacitance                                                                                                       |                     |                                          |                   |

| 1/         | Stresses above the absolute maximum rating may cause pe                                                                         | ermanent damage     | to the device. Extended o                | peration at the   |

|            | maximum levels may degrade performance and affect relia                                                                         | bility.             |                                          |                   |

| <u>2</u> / | Maximum internal power dissipation is specified so that $T_J$                                                                   |                     |                                          |                   |

|            | In product application, additional power dissipation created                                                                    | by output load cur  | rrent must not allow T <sub>J</sub> to e | xceed +175°C with |

| ~ /        | $T_A \leq +125^{\circ}C.$                                                                                                       |                     |                                          |                   |

| <u>3</u> / | Measurement taken under absolute worst case condition. I location. See MIL-STD-1835 for average package thermal                 | Data taken with the | ermai camera at highest po               | ower density      |

| <u>4</u> / | Measurement taken under absolute worst case conditions.<br>location.                                                            |                     | hermal camera at highest p               | ower density      |

| <u>5</u> / | <b>ENABLE</b> pin is grounded. $IN0 = +1 V dc$ , $IN1 = -1 V dc$ . S transition time from 50% of the SELECT input value (+2.5 V |                     |                                          |                   |

|            | IN0 channel voltage (+1 V) to IN1 (-1 V), or vice versa. See                                                                    |                     | ,,,                                      |                   |

| <u>6</u> / | ENABLE pin is driven with 0 V to +5 V pulse (with 3 ns edg<br>activated (for example, if SELECT = Logic 0, IN0 is selected      |                     |                                          |                   |

|            | of $\overline{\text{ENABLE}}$ pulse (+2.5 V) to 90% of the total output voltage                                                 | ge change. See fig  | gures 3 and 4.                           |                   |

|            |                                                                                                                                 |                     |                                          |                   |

|            | STANDARD                                                                                                                        | SIZE                |                                          | E000 40044        |

|            | MICROCIRCUIT DRAWING                                                                                                            | Α                   |                                          | 5962-10211        |

|            | DLA LAND AND MARITIME                                                                                                           |                     | REVISION LEVEL                           | SHEET             |

3

А

COLUMBUS, OHIO 43218-3990

#### 1.5 Radiation features.

| Maximum total dose available (dose rate = $50 - 300 \text{ rads}(Si)/s$ ): |                 |            |

|----------------------------------------------------------------------------|-----------------|------------|

| Device type 01                                                             | . 100 krads(Si) | <u>7</u> / |

| Maximum total dose available (dose rate $\leq$ 10 mrads(Si)/s):            |                 |            |

| Device type 02                                                             | . 50 krads(Si)  | <u>8</u> / |

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

## DEPARTMENT OF DEFENSE STANDARDS

| MIL-STD-883 -  | Test Method Standard Microcircuits.                    |

|----------------|--------------------------------------------------------|

| MIL-STD-1835 - | Interface Standard Electronic Component Case Outlines. |

# DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings. MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at <u>https://assist.dla.mil/quicksearch/</u> or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

## 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 as specified herein, or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V.

3.2.1 <u>Case outline</u>. The case outline shall be in accordance with 1.2.4 herein.

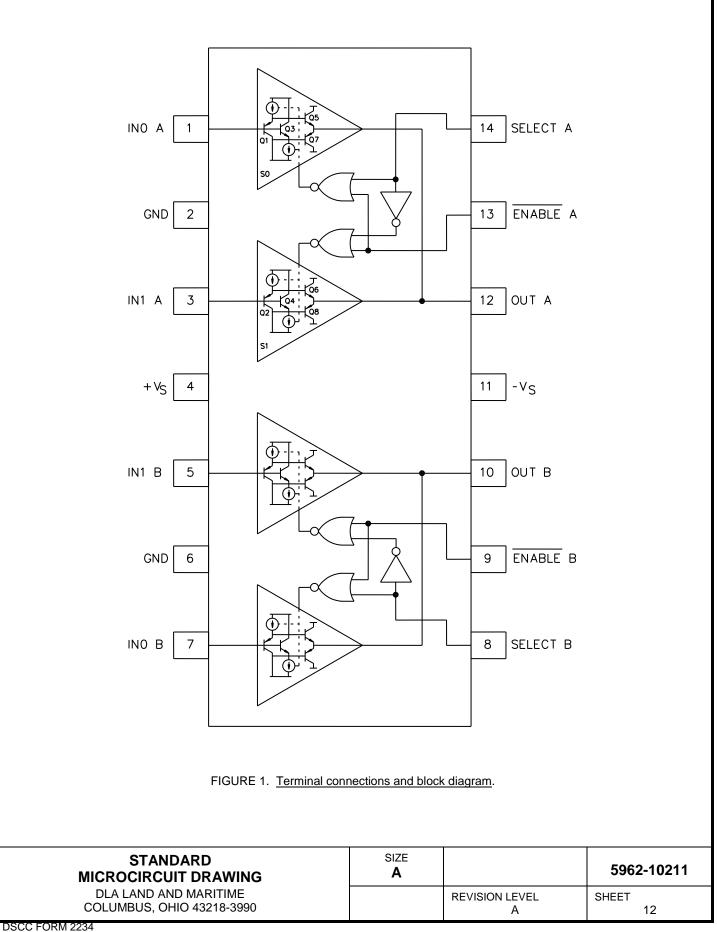

3.2.2 Terminal connections and block diagram. The terminal connections shall be as specified on figure 1.

3.2.3 <u>Truth table</u>. The truth table shall be as specified on figure 2.

<u>7</u>/ Device type 01 may be dose rate sensitive in a space environment and may demonstrate enhanced low dose rate effects. Radiation end point limits for the noted parameters are guaranteed only for the conditions specified in MIL-STD-883, method 1019, condition A.

8/ Device type 02 radiation end point limits for the noted parameters are guaranteed only for the conditions specified in MIL-STD-883 method 1019, condition D.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-10211 |

|----------------------------------|-----------|----------------|------------|

| DLA LAND AND MARITIME            |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | A              | 4          |

3.2.4 Timing diagrams. The timing diagrams shall be as specified on figures 3 and 4.

3.2.5 <u>Radiation exposure circuit</u>. The radiation exposure circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing and acquiring activity upon request.

3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full ambient operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535.

3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535.

3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). The certificate of compliance submitted to DLA Land and Maritime-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 shall be provided with each lot of microcircuits delivered to this drawing.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-10211 |

|----------------------------------|-----------|----------------|------------|

| DLA LAND AND MARITIME            |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | A              | 5          |

|                                    | TA         | ABLE I. Electrical pe                            | erformance ch | aracteristics. |          |        |     |      |

|------------------------------------|------------|--------------------------------------------------|---------------|----------------|----------|--------|-----|------|

| Test                               | Symbol     | Conditions $-55^{\circ}C \le T_A \le 10^{\circ}$ |               | -              |          | Limits |     | Unit |

|                                    |            | unless otherwise                                 | e specified   |                |          | Min    | Max |      |

| Digital inputs section.            |            |                                                  |               | [              |          |        |     |      |

| Logic "1' voltage                  | VIH        | SELECT and ENA                                   | BLE inputs    | 1,2,3          | 01,02    | 2.0    |     | V    |

|                                    |            | N                                                | 1, D, P, L, R | 1              | 01       | 2.0    |     |      |

|                                    |            | N                                                | 1, D, P, L    |                | 02       | 2.0    |     |      |

| Logic "0' voltage                  | VIL        | SELECT and ENA                                   | BLE inputs    | 1,2,3          | 01,02    |        | 0.8 | V    |

|                                    |            | Ν                                                | 1, D, P, L, R | 1              | 01       |        | 0.8 |      |

|                                    |            | N                                                | 1, D, P, L    |                | 02       |        | 0.8 |      |

| Logic "1" input current            | IIH        | SELECT, ENABLE                                   | = +4 V        | 1,2,3          | 01,02    |        | 200 | nA   |

|                                    |            | N                                                | 1, D, P, L, R | 1              | 01       |        | 200 |      |

|                                    |            | N                                                | 1, D, P, L    |                | 02       |        | 200 |      |

| Logic "0" input current            | IIL        | SELECT, ENABLE                                   | = +0.4 V      | 1,2,3          | 01,02    | -3     |     | μA   |

|                                    |            | N                                                | 1, D, P, L, R | 1              | 01       | -3     |     |      |

|                                    |            | N                                                | 1, D, P, L    |                | 02       | -3     |     |      |

| DC transfer / Input characteristic | s section. | · · ·                                            |               |                |          |        |     |      |

| Voltage gain <u>4</u> /            | Gain       | V <sub>IN</sub> = ±1 V, R <sub>L</sub> = 1       | 0 kΩ          | 1,2,3          | 01,02    | 0.986  |     | V/V  |

|                                    |            | N                                                | 1, D, P, L, R | 1              | 01       | 0.986  |     |      |

|                                    |            | N                                                | 1, D, P, L    |                | 02       | 0.986  |     |      |

| Input offset voltage               | Vos        |                                                  |               | 1              | 01,02    | -12    | 12  | mV   |

|                                    |            |                                                  |               | 2,3            |          | -15    | 15  |      |

|                                    |            | N                                                | 1, D, P, L, R | 1              | 01       | -15    | 15  |      |

|                                    |            | N                                                | 1, D, P, L    |                | 02       | -15    | 15  |      |

| Input offset voltage matching      | Vos        | Channel to channe                                | el            | 1,2,3          | 01,02    | -4     | 4   | mV   |

|                                    | match      | N                                                | 1, D, P, L, R | 1              | 01       | -8     | 8   |      |

|                                    |            | N                                                | 1, D, P, L    |                | 02       | -8     | 8   | ]    |

| See footnotes at end of table.     |            | ·                                                |               |                | <b>.</b> |        |     |      |

| STANE<br>MICROCIRCU                | SIZE<br>A  |                                                  |               |                |          | -10211 |     |      |

| DLA LAND AN<br>COLUMBUS, OH        |            | REVIS                                            | ION LEVE<br>A | L              | SHEET    | 6      |     |      |

|                                     | TA                | BLE I. Electrical                                              | performance ch          | aracteristics.       |                |        |       |        |

|-------------------------------------|-------------------|----------------------------------------------------------------|-------------------------|----------------------|----------------|--------|-------|--------|

| Test                                | Symbol            | Conditions <u>1/ 2/ 3</u> /<br>-55°C ≤ T <sub>A</sub> ≤ +125°C |                         | Group A<br>subgroups | Device<br>type | Limits |       | Unit   |

|                                     |                   | unless otherw                                                  |                         |                      |                | Min    | Max   |        |

| DC transfer / Input characteristics |                   | continued.                                                     |                         | 1                    | 1              |        | 1     |        |

| Input bias current                  | IBIAS             |                                                                |                         | 1                    | 01,02          | -5     | 5     | μA     |

|                                     |                   | Г                                                              |                         | 2,3                  |                | -7     | 7     |        |

|                                     |                   | -                                                              | M, D, P, L, R           | 1                    | 01             | -5     | 5     |        |

|                                     |                   |                                                                | M, D, P, L              |                      | 02             | -5     | +5    |        |

| Input resistance                    | R <sub>IN</sub>   |                                                                |                         | 1,2,3                | 01,02          | 1      |       | MΩ     |

|                                     |                   |                                                                | M, D, P, L, R           | 1                    | 01             | 1      |       |        |

|                                     |                   |                                                                | M, D, P, L              |                      | 02             | 1      |       |        |

| Output characteristics section.     | _                 |                                                                |                         |                      |                |        |       | _      |

| Output voltage swing <u>4</u> /     | V <sub>OUT4</sub> | $+V_{S} = +4 V$ and                                            | -V <sub>S</sub> = -4 V, | 1                    | 01,02          | 2.0    | -2.0  | V      |

|                                     |                   | IL = ±3.5 mA                                                   |                         | 2                    |                | 2.2    | -2.2  |        |

|                                     |                   |                                                                |                         | 3                    |                | 1.8    | -1.8  |        |

|                                     |                   |                                                                | M, D, P, L, R           | 1                    | 01             | 2.0    | -2.0  |        |

|                                     |                   |                                                                | M, D, P, L              |                      | 02             | 2.0    | -2.0  |        |

|                                     | V <sub>OUT5</sub> | $+V_{S} = +5 V$ and                                            | -V <sub>S</sub> = -5 V, | 1                    | 01,02          | 3.0    | -3.0  |        |

|                                     |                   | I <sub>L</sub> = ±3.5 mA                                       |                         | 2                    |                | 3.2    | -3.2  |        |

|                                     |                   | _                                                              |                         | 3                    |                | 2.8    | -2.8  |        |

|                                     |                   |                                                                | M, D, P, L, R           | 1                    | 01             | 3.0    | -3.0  |        |

|                                     |                   |                                                                | M, D, P, L              |                      | 02             | 3.0    | -3.0  |        |

|                                     | VOUT6             | $+V_{S} = +6 V$ and                                            | -V <sub>S</sub> = -6 V, | 1                    | 01,02          | 4.0    | -4.0  |        |

|                                     |                   | I <sub>L</sub> = ±3.5 mA                                       |                         | 2                    |                | 4.2    | -4.2  |        |

|                                     |                   | _                                                              |                         | 3                    |                | 3.8    | -3.8  |        |

|                                     |                   |                                                                | M, D, P, L, R           | 1                    | 01             | 4.0    | -4.0  |        |

|                                     |                   |                                                                | M, D, P, L              |                      | 02             | 4.0    | -4.0  |        |

| See footnotes at end of table.      |                   |                                                                |                         |                      |                |        |       |        |

| STAND<br>MICROCIRCUI                | T DRAW            |                                                                | SIZE<br>A               |                      |                |        |       | -10211 |

| DLA LAND ANE<br>COLUMBUS, OHI       |                   |                                                                |                         | REVIS                | ION LEVEI<br>A | L      | SHEET | 7      |

|                              | TABLE                 | E I. <u>Electrical pe</u>                                      | erforman  | ce characte          | e <u>ristics</u> - Conti | nued.  |     |      |        |

|------------------------------|-----------------------|----------------------------------------------------------------|-----------|----------------------|--------------------------|--------|-----|------|--------|

| Test                         | Symbol                | Conditions <u>1/ 2/ 3</u> /<br>-55°C ≤ T <sub>A</sub> ≤ +125°C |           | Group A<br>subgroups | Device<br>type           | Limits |     | Unit |        |

|                              |                       | unless othe                                                    | erwise sp | pecified             |                          |        | Min | Max  |        |

| Output characteristics sec   | tion – continued      | d.                                                             |           |                      |                          |        |     |      |        |

| Output resistance ON         | ROUT-ON               |                                                                |           |                      | 1,2,3                    | 01,02  |     | 40   | Ω      |

|                              |                       |                                                                | M, E      | D, P, L, R           | 1                        | 01     |     | 40   |        |

|                              |                       |                                                                | M, E      | D, P, L              |                          | 02     |     | 40   |        |

| Output resistance OFF        | R <sub>OUT-OFF</sub>  | ENABLE A =                                                     | ENABLE    | B = 2.0 V            | 1,2,3                    | 01,02  | 1   |      | MΩ     |

|                              |                       |                                                                | M, E      | D, P, L, R           | 1                        | 01     | 1   |      |        |

|                              |                       |                                                                | M, E      | D, P, L              |                          | 02     | 1   |      |        |

| Power supply rejection se    | ction.                |                                                                |           |                      |                          |        |     |      |        |

| Power supply rejection ratio | +PSRR4                | $+V_{S} = +3.5 V \text{ to } +4.5 V,$                          |           | 1                    | 01,02                    | 54     |     | dB   |        |

| Tatio                        |                       | -V <sub>S</sub> = -4 V                                         |           |                      | 2                        |        | 52  |      |        |

|                              |                       |                                                                | M, D, I   | P, L, R              | 1                        | 01     | 54  |      |        |

|                              |                       |                                                                | M, D, I   | P, L                 |                          | 02     | 54  |      |        |

|                              |                       | +V <sub>S</sub> = +3.8 V<br>-V <sub>S</sub> = -4 V             | to +4.8 \ | Ι,                   | 3                        | 01,02  | 54  |      |        |

|                              | -PSRR4                | -V <sub>S</sub> = -3.5 V to                                    | o -4.5 V, |                      | 1,2,3                    | 01,02  | 45  |      |        |

|                              |                       | +V <sub>S</sub> = +4 V                                         | M, D, I   | P, L, R              | 1                        | 01     | 45  |      |        |

|                              |                       |                                                                | M, D, I   | P, L                 |                          | 02     | 45  |      |        |

|                              | +PSRR5                | +V <sub>S</sub> = +4.5 V                                       | to +5.5 \ | ν,                   | 1,3                      | 01,02  | 54  |      |        |

|                              |                       | -V <sub>S</sub> = -5 V                                         |           |                      | 2                        |        | 52  |      |        |

|                              |                       |                                                                | M, D, I   | P, L, R              | 1                        | 01     | 54  |      |        |

|                              |                       |                                                                | M, D, I   | P, L                 |                          | 02     | 54  |      |        |

|                              | -PSRR5                | -V <sub>S</sub> = -4.5 V to                                    | o -5.5 V, |                      | 1,2,3                    | 01,02  | 45  |      | 1      |

|                              |                       | +V <sub>S</sub> = +5 V                                         | M, D, I   |                      | 1                        | 01     | 45  |      | 1      |

|                              |                       |                                                                | M, D, I   |                      |                          | 02     | 45  |      | 1      |

| See footnotes at end of t    | able.                 | 1                                                              |           |                      |                          | 1 1    |     | L    |        |

|                              | TANDARD<br>RCUIT DRAV | WING                                                           |           | SIZE<br>A            |                          |        |     | 5962 | -10211 |

**REVISION LEVEL**

А

SHEET

8

| TABLE I | Electrical | performance | characteristics | - Continued |

|---------|------------|-------------|-----------------|-------------|

|         | LICOUIDUI  | periormanee | characteristics | Continucu.  |

DSCC FORM 2234 APR 97

**MICROCIRCUIT DRAWING** DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990

| Test                            | Symbol            | Conditions <u>1/ 2/ 3</u> /<br>-55°C ≤ T <sub>A</sub> ≤ +125°C |                                       | Group A<br>subgroup<br>s | Devic<br>e<br>type | Limits |     | Unit |

|---------------------------------|-------------------|----------------------------------------------------------------|---------------------------------------|--------------------------|--------------------|--------|-----|------|

|                                 |                   | unless othe                                                    | rwise specified                       |                          |                    | Min    | Max |      |

| Power supply rejection sec      | ction – contin    | nued.                                                          |                                       |                          |                    |        |     |      |

| Power supply rejection<br>ratio | +PSRR6            | $+V_{S} = +5.5 V tc$                                           | $+V_{S} = +5.5 V \text{ to } +6.5 V,$ |                          | 01,02              | 54     |     | dB   |

|                                 |                   | -V <sub>S</sub> = -6 V                                         |                                       | 2                        |                    | 52     |     |      |

|                                 |                   |                                                                | M, D, P, L, R                         | 1                        | 01                 | 54     |     |      |

|                                 |                   |                                                                | M, D, P, L                            |                          | 02                 | 54     |     |      |

|                                 | -PSRR6            | -V <sub>S</sub> = -6.5 V to                                    | -6.5 V,                               | 1,2,3                    | 01,02              | 45     |     |      |

|                                 |                   | +V <sub>S</sub> = +6 V                                         | M, D, P, L, R                         | 1                        | 01                 | 45     |     |      |

|                                 |                   |                                                                | M, D, P, L                            |                          | 02                 | 45     |     |      |

| Power supply current secti      | ion.              |                                                                |                                       |                          |                    |        |     |      |

| Quiescent current               | +IS <sub>ON</sub> | $\overline{ENABLE} A = \overline{E}$                           | NABLE B = 0.8 V,                      | 1                        | 01,02              |        | 8   | mA   |

| (All channels "ON")             |                   | SELECT A = SE                                                  | ELECT B = 0.8 V,                      |                          |                    |        |     |      |

|                                 |                   | IN0 A = IN1 A =                                                | 0 V,                                  | 2,3                      |                    |        | 8.5 |      |

|                                 |                   | IN0 B = IN1 B =                                                | 0 V                                   |                          |                    |        |     |      |

|                                 |                   |                                                                | M, D, P, L, R                         | 1                        | 01                 |        | 8   |      |

|                                 |                   |                                                                | M, D, P, L                            |                          | 02                 |        | 8   |      |

|                                 | -IS <sub>ON</sub> | $\overline{ENABLE} A = \overline{E}$                           | NABLE B = 0.8 V,                      | 1                        | 01,02              | -8     |     |      |

|                                 |                   | SELECT A = SE                                                  | ELECT B = 0.8 V,                      |                          |                    |        |     |      |

|                                 |                   |                                                                |                                       |                          |                    |        |     |      |

|                                 |                   | IN0 A = IN1 A =                                                | 0 V,                                  | 2,3                      |                    | -8.5   |     |      |

|                                 |                   | IN0 A = IN1 A =<br>IN0 B = IN1 B =                             |                                       | 2,3                      |                    | -8.5   |     |      |

|                                 |                   |                                                                |                                       | 2,3                      | 01                 | -8.5   |     | -    |

SIZE

Α

**REVISION LEVEL**

А

5962-10211

9

SHEET

| TABLE I. | Electrical | performance | characteristics - | <ul> <li>Continued.</li> </ul> |

|----------|------------|-------------|-------------------|--------------------------------|

DSCC FORM 2234 APR 97 STANDARD

MICROCIRCUIT DRAWING DLA LAND AND MARITIME

COLUMBUS, OHIO 43218-3990

|                                      | TABLE                          | I. Electrical perform                                          | mance characteris          | <u>stics</u> – Continue | ed.            |            |            |      |

|--------------------------------------|--------------------------------|----------------------------------------------------------------|----------------------------|-------------------------|----------------|------------|------------|------|

| Test                                 | Symbol                         | Conditions <u>1/ 2/ 3</u> /<br>-55°C ≤ T <sub>A</sub> ≤ +125°C |                            | Group A<br>subgroups    | Device<br>type | L          | imits      | Unit |

|                                      |                                | unless otherw                                                  | ise specified              |                         |                | Min        | Max        |      |

| Power supply current sec             | tion.                          |                                                                |                            | 1                       | 1              | <b></b>    |            |      |

| Quiescent current                    | +IS <sub>OFF</sub>             | $\overline{ENABLE} A = \overline{ENA}$                         | $\overline{ABLE} B = 2 V,$ | 1,2,3                   | 01,02          |            | 3          | mA   |

| (All channels "OFF")                 |                                | SELECT A = SELE                                                | ECT B = 0.8 V,             |                         |                |            |            |      |

|                                      |                                | IN0 A = IN1 A = 0                                              | V,                         |                         |                |            |            |      |

|                                      |                                | IN0 B = IN1 B = 0                                              | V                          |                         |                |            |            |      |

|                                      |                                | Ν                                                              | <i>I</i> I, D, P, L, R     | 1                       | 01             |            | 3          |      |

|                                      |                                | N                                                              | /I, D, P, L                |                         | 02             |            | 3          |      |

|                                      | -ISOFF                         | $\overline{ENABLE} A = \overline{ENA}$                         | $\overline{ABLE} B = 2 V,$ | 1,2,3                   | 01,02          | -3         |            |      |

|                                      |                                | SELECT A = SELE                                                | ECT B = 0.8 V,             |                         |                |            |            |      |

|                                      |                                | IN0 A = IN1 A = 0                                              | V,                         |                         |                |            |            |      |

|                                      |                                | IN0 B = IN1 B = 0                                              | V                          |                         |                |            |            |      |

|                                      |                                | N                                                              | <i>I</i> , D, P, L, R      | 1                       | 01             | -3         |            |      |

|                                      |                                | N                                                              | /I, D, P, L                |                         | 02             | -3         |            |      |

| Dynamic performance se               | ction. <u>5</u> / <u>6</u> /   | ·                                                              |                            |                         |                |            |            |      |

| Settling time to <u>7</u> /<br>0.2 % | ts                             | 1 V step:<br>-1 V to 0 V and +1                                | V to 0 V                   | 9,10,11                 | 01,02          |            | 14         | ns   |

| Slew rate                            | SR                             | 2 V step:<br>+1 V to -1 V and -                                | 1 V to +1 V                | 4<br>5,6                | 01,02          | 650<br>550 |            | V/µs |

| -3 dB large signal<br>bandwidth      | BW-3dB                         | V <sub>IN</sub> = 0.5 Vrms                                     |                            | 4,5,6                   | 01,02          | 110        |            | MHz  |

| 0.1 dB large signal<br>bandwidth     | BW <sub>0.1dB</sub>            | V <sub>IN</sub> = 0.5 Vrms                                     |                            | 4,5,6                   | 01,02          | 40         |            | MHz  |

| Distortion / noise perform           | nance section. 5               | <u>/ 6</u> /                                                   |                            |                         |                |            |            |      |

| All hostile crosstalk <u>8</u> /     | XTLK <sub>5MHz</sub>           | f = 5 MHz, RL = 1                                              | kΩ,                        | 4                       | 01,02          |            | -71        | dB   |

|                                      |                                | V <sub>IN</sub> = 0.707 Vrms                                   |                            | 5                       |                |            | -69        |      |

|                                      |                                |                                                                |                            | 6                       |                |            | -70        |      |

|                                      | XTLK <sub>30MHz</sub>          | f = 30 MHz, RL = 7                                             | 1 kΩ,                      | 4,6                     |                |            | -55        |      |

|                                      |                                | V <sub>IN</sub> = 0.707 Vrms                                   |                            | 5                       |                |            | -54        |      |

| See footnotes at end of              | table.                         |                                                                |                            |                         | 1              |            |            | 11   |

|                                      | TANDARD                        | WING                                                           | SIZE<br>A                  |                         |                |            | 5962-1     | 0211 |

|                                      | ND AND MARIT<br>JS, OHIO 43218 |                                                                |                            | REVISION                | LEVEL<br>A     | S          | HEET<br>10 |      |

| Test Symbol        |                         | Conditions <u>1/ 2/ 3</u> /<br>-55°C ≤ T <sub>A</sub> ≤ +125°C                                            | Group A<br>subgroups | Device<br>type | Lir | nits | Unit |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------------------------|----------------------|----------------|-----|------|------|

|                    |                         | unless otherwise specified                                                                                |                      |                | Min | Max  |      |

| Distortion / noise | performance section     | – continued. <u>5/ 6/</u>                                                                                 |                      |                |     |      |      |

| OFF isolation      | ISOdis <sub>5MHz</sub>  | $f = 5 \text{ MHz}, \text{ R}_{L} = 30 \Omega,$                                                           | 4                    | 01,02          |     | -96  | dB   |

|                    |                         | V <sub>IN</sub> = 0.446 Vrms,                                                                             | 5                    |                |     | -89  |      |

|                    |                         | ENABLE A = ENABLE B > 2 V                                                                                 | 6                    |                |     | -91  |      |

|                    | ISOdis <sub>30MHz</sub> | f = 5 MHz, $R_L$ = 30 Ω,                                                                                  | 4                    |                |     | -80  | _    |

|                    |                         | V <sub>IN</sub> = 0.446 Vrms,                                                                             | 5                    |                |     | -77  |      |

|                    |                         | $\overline{ENABLE} A = \overline{ENABLE} B > 2 V$                                                         | 6                    |                |     | -79  |      |

|                    | ISO <sub>5MHz</sub>     | f = 5 MHz, $R_L$ = 30 Ω,                                                                                  | 4,5,6                |                |     | -87  |      |

|                    |                         | V <sub>IN</sub> = 0.446 Vrms,                                                                             |                      |                |     |      |      |

|                    |                         | $\overline{\text{ENABLE}} \text{ A} > 2 \text{ V}, \ \overline{\text{ENABLE}} \text{ B} < 0.8 \text{ V};$ |                      |                |     |      |      |

|                    |                         | $\overline{ENABLE} \; A < 0.8 \; V, \; \overline{ENABLE} \; B > 2 \; V$                                   |                      |                |     |      |      |

|                    | ISO <sub>30MHz</sub>    | $f = 30 \text{ MHz}, \text{ R}_{L} = 30 \Omega,$                                                          | 4,5,6                |                |     | -72  |      |

|                    |                         | V <sub>IN</sub> = 0.446 Vrms,                                                                             |                      |                |     |      |      |

|                    |                         | $\overline{\text{ENABLE}} \text{ A} > 2 \text{ V}, \ \overline{\text{ENABLE}} \text{ B} < 0.8 \text{ V};$ |                      |                |     |      |      |

|                    |                         | $\overline{ENABLE} A < 0.8 V, \overline{ENABLE} B > 2 V$                                                  |                      |                |     |      |      |

# TABLE I. Electrical performance characteristics - Continued.

<u>1</u>/ Device type 01 supplied to this drawing has been characterized through all levels P, L, and R of irradiation. Device type 02 supplied to this drawing has been characterized through levels P and L of irradiation. However, device type 01, is only tested at the "R" level and device type 02 is only tested at the "L" level. Pre and Post irradiation values are identical unless otherwise specified in table I. When performing post irradiation electrical measurements for any RHA level, T<sub>A</sub> = +25°C.

- 2/ Device type 01 may be dose rate sensitive in a space environment and demonstrate enhanced low dose rate effects. Radiation end point limits for the noted parameters are guaranteed only for the conditions as specified in MIL-STD-883, method 1019, condition A for device type 01 and condition D for device type 02. Device type 02 is tested at low dose rate.

- <u>3</u>/ Unless otherwise specified,  $R_L = 2 k\Omega$ ,  $\overline{ENABLE} A = \overline{ENABLE} B = 0.8 V$ ,  $+V_S = +4 V$  and  $-V_S = -4 V$ ; + $V_S = +5 V$  and  $-V_S = -5 V$ ;  $+V_S = +6 V$  and  $-V_S = -6 V$ . Refer to section 6.7 for detailed application notes.

- 4/ Larger values of RL provide wider output voltage swings, as well as better gain accuracy.

- 5/ Subgroups 4, 5, 6, 9, 10, and 11 are part of device initial characterization which is only repeated after design and process changes or with subsequent wafer lots.

- 6/ Not tested post irradiation.

- $\underline{7}$  +V<sub>S</sub> = +5 V and -V<sub>S</sub> = -5 V.

- 8/ XTLK measured on both inputs of each mux with the other mux in all four possible states of ENABLE and SELECT.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-10211 |

|----------------------------------|-----------|----------------|------------|

| DLA LAND AND MARITIME            |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | A              | 11         |

| Terminal<br>symbol | Description                                                                                             |

|--------------------|---------------------------------------------------------------------------------------------------------|

| IN0                | One of two inputs to each multiplexer.                                                                  |

| GND                | Analog, digital, and power ground.                                                                      |

| IN1                | One of two inputs to each multiplexer.                                                                  |

| +V <sub>S</sub>    | Positive power supply.                                                                                  |

| -V <sub>S</sub>    | Negative power supply.                                                                                  |

| OUT                | Multiplexer output.                                                                                     |

| ENABLE             | Enables multiplexer output when logic low.<br>Multiplexer output is high impedance when logic high.     |

| SELECT             | Selects IN0 to multiplexer output when logic low.<br>Selects IN1 to multiplexer output when logic high. |

FIGURE 1. <u>Terminal connections and block diagram</u> - continued.

| SELECT | ENABLE | OUTPUT |

|--------|--------|--------|

| 0      | 0      | INO    |

| 1      | 0      | IN1    |

| 0      | 1      | High Z |

| 1      | 1      | High Z |

FIGURE 2. Truth table.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                     | 5962-10211  |

|----------------------------------------------------|-----------|---------------------|-------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>A | SHEET<br>13 |

| SCC FORM 2224                                      |           |                     |             |

APR 97

## 4. VERIFICATION

4.1 <u>Sampling and inspection</u>. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

4.2 <u>Screening</u>. For device classes Q and V, screening shall be in accordance with MIL-PRF-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection.

- 4.2.1 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in MIL-PRF-38535, appendix B.

4.3 <u>Qualification inspection for device classes Q and V</u>. Qualification inspection for device classes Q and V shall be in accordance with MIL-PRF-38535. Inspections to be performed shall be those specified in MIL-PRF-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

4.4 <u>Conformance inspection</u>. Technology conformance inspection for classes Q and V shall be in accordance with MIL-PRF-38535 including groups A, B, C, D, and E inspections, and as specified herein.

4.4.1 Group A inspection.

- a. Tests shall be as specified in table IIA herein.

- b. Subgroups 7 and 8 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroups 4, 5, 6, 9, 10, and 11 are part of device initial characterization which is only repeated after design and process changes or with subsequent wafer lots.

4.4.2 Group C inspection. The group C inspection end-point electrical parameters shall be as specified in table IIA herein.

4.4.2.1 Additional criteria for device classes Q and V. The steady-state life test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The test circuit shall be maintained under document revision level control by the device manufacturer's TRB in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1005 of MIL-STD-883.

4.4.3 <u>Group D inspection</u>. The group D inspection end-point electrical parameters shall be as specified in table IIA herein.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-10211 |

|----------------------------------|-----------|----------------|------------|

| DLA LAND AND MARITIME            |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | A              | 16         |

| Test requirements            | Suba                      | roupe                        |  |

|------------------------------|---------------------------|------------------------------|--|

| restrequirements             | Subgroups                 |                              |  |

|                              | (in accordance with       |                              |  |

|                              | MIL-PRF-38535, table III) |                              |  |

|                              | Device                    | Device                       |  |