# **Programmable High Speed Single Channel Laser Diode Driver**

#### ISL58214

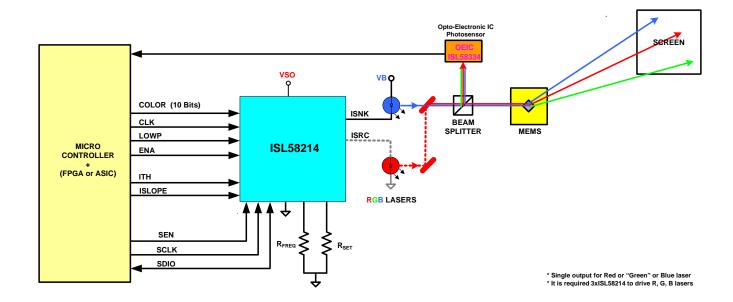

The ISL58214 is a highly integrated laser diode driver designed to support a laser beam scanning MEMS projector. Operating from a single 5V analog supply, it directly drives either a cathodegrounded laser, or a floating laser whose anode is connected to a high voltage supply. The ISL58214 is configured through a serial interface.

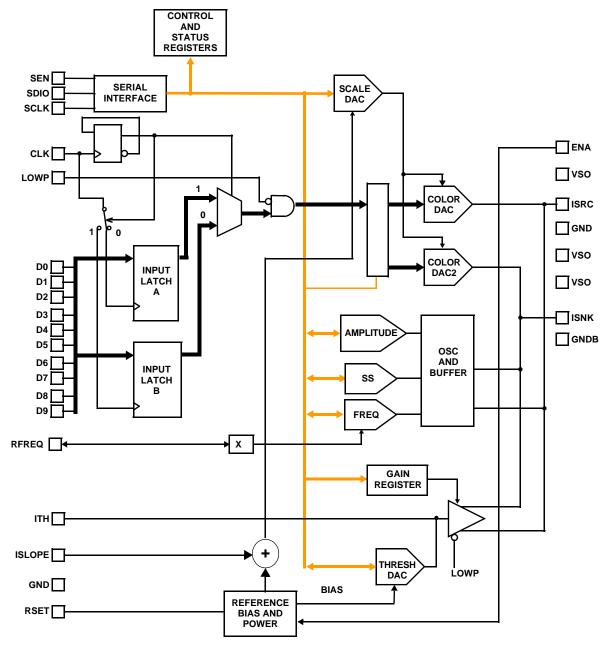

An integrated 10-bit high power DAC drives the selected laser. The desired current level can be scaled by a 10 bit DAC programmed through a serial interface or the I<sub>SLOPE</sub> pin to compensate for ambient brightness, speed variation or laser sensitivity change.

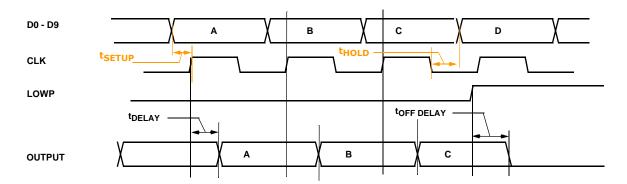

The CLK pin clocks in the data on the rising edge of CLK. The LOWP line gates the output off when HIGH.

#### **Related Literature**

See AN1502 for ISL58214 Evaluation Board Appnote "ISL58214 Application Note (Design Migration from ISL58215)"

#### **Features**

- Direct drive for floating laser, or cathode grounded. Supports Red, 'Green' or Blue laser

- Up to 1000mA maximum total output (I<sub>SRC</sub>) with 1.5ns typical tr/tf

- Up to 500mA maximum total output (I<sub>SNK</sub>) with 1ns typical tr/tf.

- 10-bit x 10-bit multiplying DAC output provides 10-bit full scale adjustment and 10-bit resolution at any full scale output

- I<sub>SLOPE</sub> input allows compensation for laser slope, ambient light, and sweep speed variation

- High-Speed SPI Serial input works up to 50MHz

- 10-bit Video Code capable of operating up to 100MHz pixel data rate

- Integrated Programmable HFM (High Frequency Modulation) for laser stabilization and speckle reduction

- Pb-Free (RoHS Compliant)

### **Applications**

- · RGB Laser based Projector or Pico Projector

- Hand held Projector

- General Purpose Laser Diode Driver

- General Purpose High Current Driver/Controller

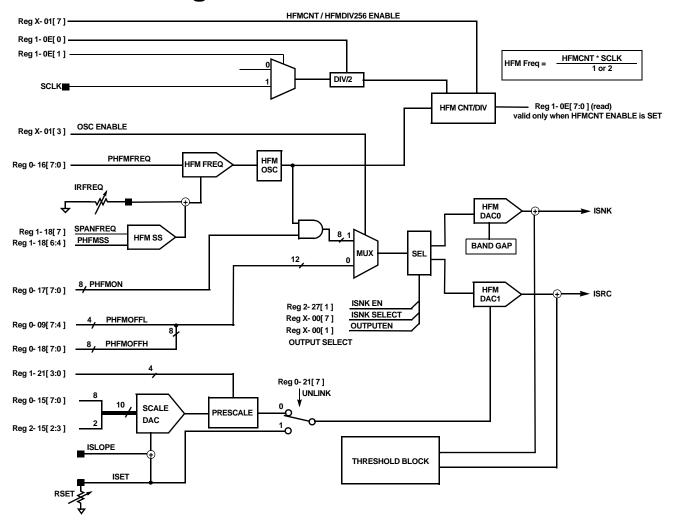

# **System Block Diagram**

# **Pin Configuration**

**TOP VIEW** SDIO CLK SEN 21 ENA vso D5 **ISRC** THERMAL **PAD** D6 5 GND **D7** 6 vso **D8** vso

SLOPE

RSET

15 ISNK

ISL58214 (28 LD QFN)

# **Ordering Information**

| PART<br>NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | PACKAGE<br>Tape & Reel<br>(Pb-free) | PKG.<br>DWG. # |

|-----------------------------------|-----------------|-------------------------------------|----------------|

| ISL58214CRZ-T13                   | 58214 CRZ       | 28 Ld QFN                           | L28.4x5A       |

| ISL58214CRZ-EVAL                  | Evaluation Boar | rd                                  |                |

- 1. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- For Moisture Sensitivity Level (MSL), please see device information page for ISL58214. For more information on MSL please see techbrief TB363.

# **Pin Descriptions**

D9 8

| PIN#                              | PIN NAME                                     | 1/0    | PIN TYPE | PIN DESCRIPTION                                                                                                                                                                        |

|-----------------------------------|----------------------------------------------|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27, 28, 1, 2, 3, 4,<br>5, 6, 7, 8 | D0, D1, D2, D3,<br>D4, D5, D6, D7,<br>D8, D9 | Input  | Digital  | These inputs specify the color current. $I_{COLOR} = I_{Max} (512*D9 + 256*D8 + 4*D2 + 2*D1 + D0)$ . Imax is set by the scale DAC register (Page 0, Addr 15h), $I_{SLOPE}$ , and RSET. |

| 9                                 | RFREQ                                        | Input  | Analog   | The resistor to GND sets the reference for the HFM (anti-speckle) oscillator.                                                                                                          |

| 10                                | lth                                          | Input  | Analog   | Current into this pin becomes laser Threshold current; it has a 1000 $\Omega$ input impedance. The gain is programmable.                                                               |

| 11                                | ISLOPE                                       | Input  | Analog   | Current into this pin sets the full scale DAC amplitude                                                                                                                                |

| 12, 14, 18                        | GND                                          | GND    | GND      | Ground (connect all)                                                                                                                                                                   |

| 13                                | RSET                                         | Input  | Analog   | RSET to GND is the reference for the current DAC.                                                                                                                                      |

| 15                                | ISNK                                         | Output | Analog   | Floating laser diode output. Laser anode tied to a high supply.                                                                                                                        |

| 16, 17, 20                        | VSO                                          | Power  | Power    | The +5V power for the output drivers (connect all)                                                                                                                                     |

| 19                                | ISRC                                         | Output | Analog   | The output current into a grounded anode laser diode                                                                                                                                   |

| 21                                | ENA                                          | Input  | Digital  | When high the chip is enabled. When low, the chip is powered down and the outputs disabled.                                                                                            |

| 22                                | SEN                                          | Input  | Digital  | The enable for the serial port.                                                                                                                                                        |

| 23                                | SDIO                                         | 1/0    | Digital  | The data for the serial port                                                                                                                                                           |

| 24                                | SCLK                                         | Input  | Digital  | Serial clock for SDIO data                                                                                                                                                             |

| 25                                | CLK                                          | Input  | Digital  | The Dn data is clocked in on the rising edge of CLK                                                                                                                                    |

| 26                                | LOWP                                         | Input  | Digital  | When high the output is disable for laser safety                                                                                                                                       |

| -                                 | PD                                           | Power  | Analog   | The thermal pad must be heavily grounded as a heat sink.                                                                                                                               |

NOTE: Pins with the same name are internally connected together; however, LDD pins must not be used for connecting together external components or features.

# **Table of Contents**

| Related Literature                              |                |

|-------------------------------------------------|----------------|

| System Block Diagram                            | . 2            |

| Pin Descriptions                                | . 3            |

| Absolute Maximum Ratings                        | . 5            |

| Thermal Information                             | . 5            |

| Recommended Operating Conditions                | . 5            |

| Electrical Specifications                       | . 5            |

| Scale DAC (10-bit) DC Specifications            | . 6            |

| ISLOPE DC Specifications                        | . 6            |

| ISRC Color Power DAC (10-bit) DC Specifications | . 6            |

| ISNK Color Power DAC (10-bit) DC Specifications | . 6            |

| ISNK Threshold Amplifier DC Specifications      | . 7            |

| ISRC Threshold Amplifier DC Specifications      | . 7            |

| Threshold DAC (12-bit) DC Specifications        | . 7            |

| HFM (High Frequency Modulator)                  | . 8            |

| Serial Interface AC Performance                 | . 8            |

| Laser Driver AC Performance                     | . 9            |

| Application Block Diagram                       | 10             |

| Timing Diagram                                  | 10             |

| Typical Performance Curves                      | 11             |

| Applications Information                        | 12             |

| RSET Scaling                                    | .12            |

| Scaling DAČ and I <sub>SLOPE</sub> Scaling      | .12<br>12      |

| Color Output Operation                          | 12             |

| HFM Operation                                   |                |

| Power Consumption                               | 12             |

| Register Usage                                  |                |

| Register List                                   |                |

| Register Bit Description                        | 13             |

| Scale DAC Block Diagram                         | 17             |

| Color Block Diagram                             |                |

| Detailed Timing Diagram                         |                |

| Threshold Block Diagram                         | 19             |

| Threshold DAC                                   |                |

| Oscillator Block Diagram                        |                |

| Oscillator Control                              |                |

| HFM I <sub>OUT</sub> Equations                  | 21             |

|                                                 |                |

| Serial Interface Protocol                       |                |

| Serial Interface Protocol                       | 22             |

| Revision History                                | 22<br>23       |

|                                                 | 22<br>23<br>23 |

#### **Absolute Maximum Ratings**

| V <sub>SO,</sub> Supply Voltages                                                      |

|---------------------------------------------------------------------------------------|

| I <sub>SRC</sub> , Output Current1000mApk                                             |

| I <sub>SNK</sub> , Output Current                                                     |

| V <sub>IH DATA.</sub> Logic Input Voltages0.5V to Lesser of                           |

| V <sub>S0</sub> + 0.5V or 3V                                                          |

| V <sub>IH.</sub> Logic Input Voltages0.5V to V <sub>SO</sub> + 0.5V                   |

| I <sub>IN,</sub> Current into R <sub>SET</sub> , R <sub>FREQ</sub> , I <sub>APC</sub> |

| Human Body Model (Tested per JESD22-A114E) 2kV                                        |

| Machine Model (Tested per JESD22-A115-A) 100V                                         |

| Charged Device Model1500V                                                             |

| Latch Up (Tested per JESD-78B; Class 2, Level A)                                      |

#### **Thermal Information**

| Thermal Resistance (Typical)               | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (° C/W) |

|--------------------------------------------|----------------------|-----------------------|

| 28 Ld QFN Package (Notes 4, 5)             | 37                   | 2.9                   |

| T <sub>S</sub> , Storage Temperature Range | 6                    | 0°C to +150°C         |

| Pb-Free Reflow Profile                     |                      | . see link below      |

| http://www.intersil.com/pbfree/Pb-FreeRe   | eflow.asp            |                       |

### **Recommended Operating Conditions**

| T <sub>A</sub> , Temperature Range    | 5°C to +85°C   |

|---------------------------------------|----------------|

| T <sub>J</sub> , Junction Temperature | -5°C to +150°C |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 5. For  $\theta_{1C}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# **Electrical Specifications** Unless otherwise indicated, all of the following tables are: $V_{SO} = V_{HI} = 5V$ , $R_{SET} = 620\Omega$ , $R_{FREQ} = 4700\Omega$ , CLK = 100MHZ, $R_{LOAD-ISRC} = 8\Omega$ to GND, $R_{LOAD-ISNK} = 10\Omega$ to $V_{HI}$ , Scale DAC = 0x3FF, Reg 1-21 = 0x88, $T_A = +25$ °C.

| PARAMETER            | DESCRIPTION                                            | MIN | TYP | MAX | UNIT |

|----------------------|--------------------------------------------------------|-----|-----|-----|------|

| DC ELECTRICAL S      | PECIFICATIONS                                          | 1   | l'  | '   | l.   |

| V <sub>SO</sub>      | (Notes 6, 7)                                           | 4.5 |     | 5.5 | V    |

| I <sub>VSO</sub>     | Supply Current (No Current Output)                     |     | 25  | 40  | mA   |

| I <sub>S</sub> , dis | Supply Currents, Disable Mode                          |     | 10  | 15  | mA   |

| V <sub>ISNK</sub>    | Allowable Operating Range of ISNK Pin (see Figure 2)   |     |     | 5.8 | v    |

| V <sub>IH_DATA</sub> | Input Logic High Level for Data lines (D0-D9)          | 1.5 |     | 3   | v    |

| V <sub>IH</sub>      | Input Logic High Level                                 | 2.4 |     |     | v    |

| V <sub>IL</sub>      | Input Logic Low Level                                  |     |     | 0.8 | V    |

| v <sub>oh</sub>      | SDIO, Monitor Output High Level, I <sub>L</sub> = -5mA | 2.4 |     |     | v    |

| V <sub>OL</sub>      | SDIO, Monitor Output Low Level, I <sub>L</sub> = 5mA   |     |     | 0.4 | V    |

| I <sub>INH</sub>     | Input Current High Level                               | -1  |     | +1  | μΑ   |

| I <sub>INL</sub>     | Input Current High Level, except ENA pin               | -1  |     | +1  | μΑ   |

| I <sub>INL_ENA</sub> | Input Current Low Level for ENA pin                    | -15 |     | -5  | μΑ   |

#### NOTES:

- 6. Required voltage at the device pins. Allowance must be made for any voltage drop between the power supply and the device.

- 7. Required voltage also depends on laser diode manufacturer and pickup optical efficiency.

#### Scale DAC (10-bit) DC Specifications Standard conditions unless otherwise noted.

| PARAMETER              | DESCRIPTION                | CONDITIONS                        | MIN  | TYP  | MAX  | UNIT |

|------------------------|----------------------------|-----------------------------------|------|------|------|------|

| DNL-P <sub>SCALE</sub> | Differential Non-Linearity | (Note 8)                          | -3.5 |      | +2.5 | LSB  |

| INL-P <sub>SCALE</sub> | Integral Non-Linearity     | At 200h Resistive Load ~0V to ~3V |      | +40  |      | LSB  |

| ZS-P <sub>SCALE</sub>  | Zero-Scale Error           | (Note 9)                          | -2   | 0    | +2   | LSB  |

| V <sub>RSET</sub>      | RSET Pin Voltage           |                                   | 1.03 | 1.06 | 1.11 | ٧    |

#### NOTE:

### I<sub>SLOPE</sub> DC Specifications Standard conditions unless otherwise noted.

| PARAMETER             | DESCRIPTION                                         | CONDITIONS                                     | MIN | TYP | MAX | UNIT  |

|-----------------------|-----------------------------------------------------|------------------------------------------------|-----|-----|-----|-------|

| R <sub>IN</sub>       | I <sub>SLOPE</sub> Input Impedance to GND           |                                                |     | 570 |     | Ω     |

| I <sub>GAIN</sub> SRC | I <sub>SLOPE</sub> Current Gain to I <sub>SRC</sub> | P <sub>SCALE</sub> = 0x3FF, Input Code = 0x3FF |     | 450 |     | mA/mA |

| I <sub>GAIN</sub> SNK | I <sub>SLOPE</sub> Current Gain to I <sub>SNK</sub> | P <sub>SCALE</sub> = 0x3FF, Input Code = 0x3FF |     | 135 |     | mA/mA |

### I<sub>SRC</sub> Color Power DAC (10-bit) DC Specifications Standard conditions unless otherwise noted.

| PARAMETER                        | DESCRIPTION                                             | CONDITIONS                                                                  | MIN | TYP | MAX  | UNIT   |

|----------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|------|--------|

| DNL <sub>COLR_SRC</sub>          | Differential Non-Linearity                              |                                                                             | -2  |     | +0.5 | LSB    |

| INL <sub>COLR_SRC</sub>          | Integral Non-Linearity                                  |                                                                             |     | 21  |      | LSB    |

| FS <sub>OUT</sub> -H1.1          | Input code Full-Scale Output Current<br>Headroom = 1.1V | Input Code = 0x3FF, $V_{ISRC}$ = 3.9V, VSO = 5.0V, $R_{SET}$ = 620 $\Omega$ | 625 |     |      | mA     |

| SFS <sub>OUT</sub> -<br>COLR_SRC | Full-Scale Current Power Supply Rejection               | vs V <sub>SO</sub> (Note 10)                                                |     | 40  |      | dB     |

| TFS <sub>OUT</sub><br>COLR_SRC   | Full-Scale Current Temperature Coefficient              | (Note 11)                                                                   |     | 600 |      | ppm/°C |

| ZS <sub>COLR_SRC</sub>           | Zero-Scale error                                        | V <sub>ISRC</sub> = 2V (Note 9)                                             | -2  | 0   | +2   | LSB    |

### I<sub>SNK</sub> Color Power DAC (10-bit) DC Specifications Standard conditions unless otherwise noted.

| PARAMETER                      | DESCRIPTION                                                                      | CONDITIONS                      | MIN  | TYP | MAX  | UNIT   |

|--------------------------------|----------------------------------------------------------------------------------|---------------------------------|------|-----|------|--------|

| DNL <sub>COLR_SNK</sub>        | Differential Non-Linearity                                                       |                                 | -4.9 |     | +2.0 | LSB    |

| INL <sub>COLR_SNK</sub>        | Integral Non-Linearity                                                           |                                 |      | 60  |      | LSB    |

| FS <sub>OUT</sub> -620         | Input code Full-Scale Output Current<br>R <sub>SET</sub> = 620Ω, Reg 1-21 = 0x88 | Input code = 0x3FF              | 200  | 250 |      | mA     |

| SFS <sub>OUT</sub><br>COLR_SNK | Full-Scale Current Power Supply Rejection                                        | vs V <sub>SO</sub> (Note 10)    |      | 20  |      | dB     |

| TFS <sub>OUT</sub> -COLR_SNK   | Full-Scale Current Temperature Coefficient                                       | (Note 11)                       |      | 600 |      | ppm/°C |

| ZS <sub>COLR_SNK</sub>         | Zero-Scale Error                                                                 | V <sub>ISNK</sub> = 2V (Note 9) | -8   | 0   | +8   | LSB    |

#### NOTES:

- 9. Zero-scale error (ZS) is the deviation from zero current output when the digital input code is zero.

- Full-scale output current power supply sensitivity (SFS) is measured by varying the V<sub>SO</sub> from 4.5V to 5.5V DC and measuring the effect of this signal

on the full-scale output current.

- 11. Full-scale output current temperature coefficient (TFS) is given by delta (full-scale output current)/ $\Delta$ (T).

<sup>8.</sup> Differential non-linearity (DNL) is the differential between the measured and ideal 1 LSB change of any two adjacent codes.

# $\textbf{I}_{\textbf{SNK}} \textbf{ Threshold Amplifier DC Specifications} \text{ } \textbf{Standard condition unless otherwise noted.}$

| PARAMETER                | DESCRIPTION                                                            | CONDITIONS                                           | MIN | TYP | MAX  | UNIT  |

|--------------------------|------------------------------------------------------------------------|------------------------------------------------------|-----|-----|------|-------|

| I <sub>th_MIN-GAIN</sub> | Current Gain @ Min Gain                                                | Reg1-21h = 1X, $I_{APC}$ = 0 $\mu$ A, 500 $\mu$ A    | 8   | 17  | 25   | mA/mA |

| I <sub>th_MAX-GAIN</sub> | Current Gain @ Max Gain                                                | Reg1-21h = FX, $I_{APC} = 0\mu A$ , 500 $\mu A$      | 180 | 240 | 295  | mA/mA |

| I <sub>th_GAIN</sub>     | Current Gain                                                           | I <sub>th</sub> = 0μΑ, 500μΑ                         | 80  | 135 | 170  | mA/mA |

| I <sub>th_OS</sub>       | Current Offset                                                         | I <sub>th</sub> = 0μA                                | -2  | 1   | 3    | mA    |

| LIN <sub>th</sub>        | Output Current Linearity                                               | I <sub>th</sub> = 0μA, 500μA, <b>1</b> .0mA          | -2  |     | 4    | %     |

| I <sub>SNK</sub> -th     | I <sub>SNK</sub> Threshold Output Current, Using I <sub>th</sub> Input | I <sub>th</sub> = 1.5mA                              | 120 |     |      | mA    |

| R <sub>IN</sub>          | I <sub>th</sub> Input Impedance to GND                                 |                                                      | 800 |     | 1300 | Ω     |

| PSRR <sub>th</sub>       | I <sub>th</sub> Current Power Supply Rejection                         | I <sub>th-IN</sub> = 0.45mA, varying V <sub>SO</sub> |     | 20  |      | dB    |

# I<sub>SRC</sub> Threshold Amplifier DC Specifications Standard condition unless otherwise noted.

| PARAMETER                 | DESCRIPTION                                                            | CONDITIONS                                           | MIN | TYP | MAX  | UNIT  |

|---------------------------|------------------------------------------------------------------------|------------------------------------------------------|-----|-----|------|-------|

| I <sub>th_MIN</sub> -GAIN | Current Gain @ Min Gain                                                | Reg1-21h = 1X, $I_{APC}$ = $0\mu A$ , $500\mu A$     | 9   | 13  | 18   | mA/mA |

| I <sub>th_MAX-GAIN</sub>  | Current Gain @ Max Gain                                                | Reg1-21h = FX, $I_{APC}$ = $0\mu A$ , $500\mu A$     | 150 | 170 | 195  | mA/mA |

| I <sub>th_GAIN</sub>      | Current Gain                                                           | I <sub>th</sub> = 0μΑ, 500μΑ                         | 80  | 95  | 115  | mA/mA |

| I <sub>th_OS</sub>        | Current Offset                                                         | I <sub>th</sub> = ΟμΑ                                | -2  | 1   | 3    | mA    |

| LIN <sub>th</sub>         | Output Current Linearity                                               | I <sub>th</sub> = 0μA, 500μA, <b>1</b> .0mA          | -2  |     | 4    | %     |

| I <sub>SRC</sub> -th      | I <sub>SRC</sub> Threshold Output Current, Using I <sub>th</sub> Input | I <sub>th</sub> = 1.5mA                              | 120 |     |      | mA    |

| R <sub>IN</sub>           | I <sub>th</sub> Input Impedance to GND                                 | Same amplifier as for I <sub>SNK</sub>               | 800 |     | 1300 | Ω     |

| PSRR <sub>th</sub>        | I <sub>th</sub> Current Power Supply Rejection                         | I <sub>th-IN</sub> = 0.45mA, varying V <sub>SO</sub> |     | 20  |      | dB    |

### Threshold DAC (12-bit) DC Specifications Standard conditions unless otherwise noted.

| PARAMETER                                                                                      | DESCRIPTION                                                             | CONDITIONS                                                       | MIN | TYP | MAX | UNIT   |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|-----|-----|-----|--------|

| DNL-T                                                                                          | Threshold DAC Differential Non-Linearity                                | P <sub>th:</sub> Reg 0-19 + Reg 1-09                             | -2  |     | +2  | LSB    |

| INL-T Threshold DAC Integral Non-Linearity                                                     |                                                                         | @ 900h on Resistive Load. 0V to ~3V                              |     | +90 |     | LSB    |

| I <sub>SRC</sub> -T-DAC Threshold Output Current, Threshold DAC a Full-Scale, I <sub>SRC</sub> |                                                                         | P <sub>th</sub> = 0xFFF, I <sub>APC</sub> = 0, Reg 1-21 = 8F     | 110 | 130 | 170 | mA     |

| I <sub>SNK</sub> -T-DAC                                                                        | Threshold Output Current, Threshold DAC at Full-Scale, I <sub>SNK</sub> | P <sub>th</sub> = 0xFFF, I <sub>APC</sub> = 0, Reg 1-21 = 8F     | 160 | 200 | 240 | mA     |

| PSRR <sub>-FS</sub>                                                                            | Power Supply Rejection - Full-Scale Current                             | Varying the V <sub>SO</sub> (Note 10)                            |     | -42 |     | dB     |

| TC <sub>-FS-T</sub> Temperature Coefficient - Full-Scale Current                               |                                                                         | Not including the R <sub>SET</sub> tempco (Note 11) 0°C to +85°C |     | -48 |     | ppm/°C |

| ZS-R                                                                                           | Zero-Scale Error                                                        | V <sub>IOUT</sub> = 2V (Note 9)                                  | -80 | 0   | 80  | LSB    |

### HFM (High Frequency Modulator) Standard conditions unless otherwise noted.

| PARAMETER                    | DESCRIPTION                                                        | CONDITIONS                                                        | MIN  | TYP     | MAX  | UNIT              |

|------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|------|---------|------|-------------------|

| I <sub>MAX-ISRC-OFF</sub>    | Max HFM Off DC Output, I <sub>SRC</sub>                            | HFMOFF = 0x7FF                                                    | 90   | 120     | 160  | mA                |

| I <sub>MAX-SNK-OFF</sub>     | Max HFM Off DC Output, I <sub>SNK</sub>                            | HFMOFF = 0x7FF                                                    | 45   | 62      | 80   | mA                |

| I <sub>MIN-SRC-OFF</sub>     | Min HFM Off DC Output, I <sub>SRC</sub>                            | HFMOFF = 0x000                                                    | -3   | 0       | 3    | mA                |

| I <sub>MIN-SNK-OFF</sub>     | Min HFM Off DC Output, I <sub>SNK</sub>                            | HFMOFF = 0x000                                                    | -3   | 0       | 3    | mA                |

| I <sub>MAX-SRC-ON</sub>      | Max HFM Oscillator Output, I <sub>SRC</sub>                        | HFMON = Reg 0-17h = 0xFF                                          |      | 118     |      | mA <sub>P-P</sub> |

| I <sub>MAX-SNK-ON</sub>      | Max HFM Oscillator Output, I <sub>SNK</sub>                        | HFMON = 0xFF<br>Reg 1-21 = x8h                                    |      | 60      |      | mA <sub>P-P</sub> |

| Fosc-Max                     | Max HFM Frequency                                                  | Reg 0-16 = 0xFF;<br>$R_{FREQ} = 4.7k\Omega$                       | 850  | 980     | 1150 | MHz               |

| F <sub>OSC-MIN</sub>         | Min HFM Frequency                                                  | Reg 0-16 = 0x01;<br>$R_{FREQ} = 4.7k\Omega$                       | 275  | 345     | 400  | MHz               |

| PSRR <sub>OSC-AMP-ISNK</sub> | PSRR - HFM Amplitude                                               | 700MHz; HFMON = 0xFF                                              |      | 1.2     |      | %/V               |

| TF <sub>OSC400MAX</sub>      | HFM Frequency Temperature Coefficient                              | Range from 200MHz to 400MHz                                       |      | 0 - 900 |      | ppm/°C            |

| TF <sub>OSC900MAX</sub>      | HFM Frequency Temperature Coefficient                              | Range from 400MHz to 900MHz                                       |      | ±250    |      | ppm/°C            |

| VR <sub>FREQ</sub>           | R <sub>FREQ</sub> Pin Voltage                                      | $R_{FREQ} = 4.7k\Omega$                                           | 0.85 | 1.01    | 1.1  | V                 |

| SS <sub>-WIDTH-RANGE</sub>   | Spread Spectrum Spreading Width Adjustment Range                   | R <sub>FREQ</sub> = 4.7kΩ, Reg 1-18 = 10h, Reg 0-16 = 0x26        | 0.1  | 0.293   | 1.1  | %                 |

| SS_Shift                     | Shift of Center Frequency when SS is Enabled vs when it's Disabled | R <sub>FREQ</sub> = 4.7kΩ, Reg 1-18-00h<br>to 30h, Reg 0-16 = 26h |      | 0.4     |      | %                 |

| SS_Mod                       | Spread Spectrum Modulation Frequency                               | REG 1-18h Bit 7 = 0                                               | 30   | 53      | 80   | kHz               |

| SS_Mod                       | Spread Spectrum Modulation Frequency                               | REG 1-18h Bit 7 = 1                                               | 15   | 37      | 55   | kHz               |

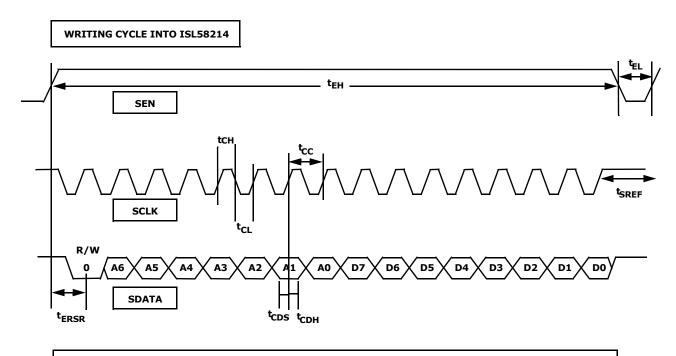

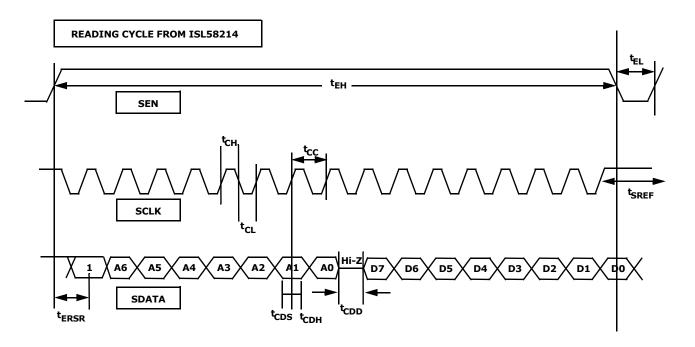

# **Serial Interface AC Performance** Standard conditions unless otherwise noted.

| PARAMETER         | DESCRIPTION                                   | CONDITIONS                                | MIN | TYP | MAX | UNIT |

|-------------------|-----------------------------------------------|-------------------------------------------|-----|-----|-----|------|

| F <sub>SER</sub>  | SCLK Operating Range                          | Static logic not limited at low frequency | 0   |     | 50  | MHz  |

| t <sub>EH</sub>   | SEN "H" Time                                  | @ 50MHz                                   | 320 |     |     | ns   |

| t <sub>EL</sub>   | SEN "L" Time                                  | @ 50MHz                                   | 160 |     |     | ns   |

| t <sub>ERSR</sub> | SEN Rising Edge to the First SCLK Rising Edge | @ 50MHz                                   | 10  |     |     | ns   |

| t <sub>CDS</sub>  | SDIO Set-Up Time                              | @ 50MHz                                   |     | 10  |     | ns   |

| t <sub>CDH</sub>  | SDIO Hold Time                                | @ 50MHz                                   |     | 10  |     | ns   |

| t <sub>SREF</sub> | Last SCLK Rising Edge to SEN Falling Edge     | @ 50MHz                                   | 10  |     |     | ns   |

| t <sub>CC</sub>   | SCLK Cycle Time1                              | @ 50MHz                                   | 20  |     |     | ns   |

| Duty              | SCLK "H" Duty Cycle                           | @ 50MHz                                   | 40  | 50  | 60  | %    |

| t <sub>CDD</sub>  | SDIO Output Delay                             | @ 50MHz                                   |     |     | 4   | ns   |

| t <sub>EDH</sub>  | SDIO Output Hold Time                         | @ 50MHz                                   | 2   |     |     | ns   |

Laser Driver AC Performance Demoboard test, 10% duty cycle pulse, load = equivalent circuitry to [laser + flex cable] and/or as noted.  $V_{SO}$  = 5V.  $T_A$  = +25°C.

| PARAMETER              | DESCRIPTION                                   | CONDITIONS | MIN | TYP | MAX  | UNIT |

|------------------------|-----------------------------------------------|------------|-----|-----|------|------|

| t <sub>R-ISRCx</sub>   | I <sub>SRC</sub> Write Rise Time (10% to 90%) | Note 12    |     | 1.0 | 2.0  | ns   |

| t <sub>F-ISRCx</sub>   | I <sub>SRC</sub> Write Fall Time (10% to 90%) | Note 12    |     | 1.0 | 2.0  | ns   |

| 0/S <sub>-ISRCx</sub>  | I <sub>SRC</sub> Write Fast Overshoot         | Note 12    |     | 10  |      | %    |

| t <sub>R-ISNK</sub>    | I <sub>SNK</sub> Write Rise Time (10% to 90%) | Note 12    |     | 0.8 | 1.5  | ns   |

| t <sub>F-ISNK</sub>    | I <sub>SNK</sub> Write Fall Time (10% to 90%) | Note 12    |     | 0.5 | 1.0  | ns   |

| t <sub>DELAY</sub>     | From CLK at 50% to OUTPUT at 10%              | Note 12    |     | 4.5 |      | ns   |

| t <sub>OFF-DELAY</sub> | From LOWP at 50% to OUTPUT at 10%             | Note 12    |     | 7   |      | ns   |

| t <sub>SETUP</sub>     | DATA to CLK                                   |            |     |     | 700  | ps   |

| t <sub>HOLD</sub>      | DATA to CLK                                   |            |     |     | 1500 | ps   |

| 0/S <sub>-ISNK</sub>   | ISNK Write Fast Overshoot                     | Note 12    |     | 10  |      | %    |

| BW <sub>Ith</sub>      | I <sub>th</sub> Amplifier 3dB Bandwidth       | Note 12    |     | 0.3 |      | MHz  |

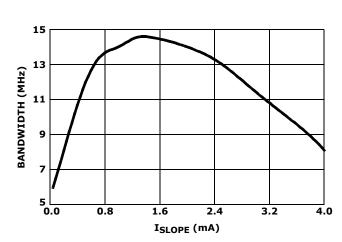

| BW <sub>ISLOPE</sub>   | I <sub>SLOPE</sub> Amplifier 3dB Bandwidth    | Note 12    |     | 3   |      | MHz  |

#### NOTE:

<sup>12.</sup> Limits established by characterization and are not production tested.

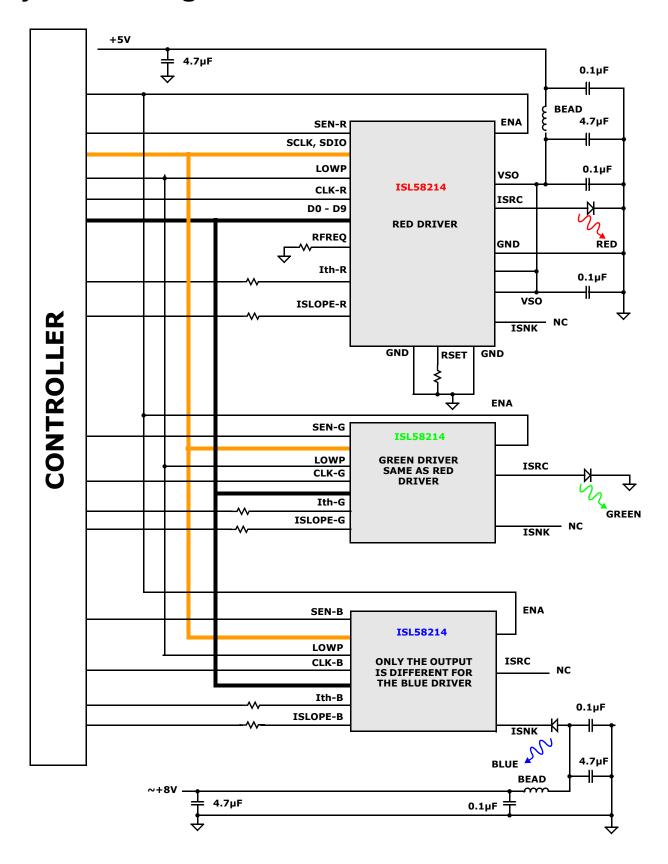

# **Application Block Diagram**

# **Timing Diagram**

90

80

70

60

50

30

200

ISO CONSUMPTION (mA)

# **Typical Performance Curves**

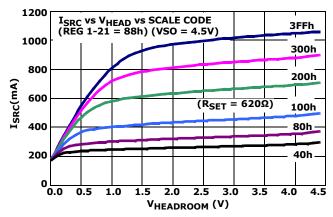

FIGURE 1. I<sub>SRC</sub> CURRENT vs V<sub>SD</sub> vs I<sub>SCALE\_BIAS</sub>

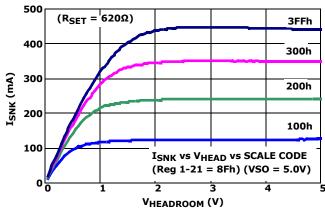

FIGURE 2. I<sub>SNK</sub> CURRENT vs V<sub>DS</sub> vs I<sub>SCALE\_BIAS</sub>

PHFMON = 0xFF

PHFMON = 0x80

PHFMON = 0x01

1**G**

800M

HFM FREQUENCY (Hz)

FIGURE 4. HFM OSCILLATOR CURRENT CONSUMPTION

400M

600M

FIGURE 5. IOUT/ITH BANDWIDTH vs ITH

FIGURE 6. I<sub>OUT</sub>/I<sub>SLOPE</sub> BANDWIDTH vs I<sub>SLOPE</sub>

# **Applications Information**

#### **RSET Scaling**

The data sheet values for threshold current, and fast current are based on an  $R_{SET}$  of  $620\Omega$  when scaling DAC and input code are both set to full scale. The user may choose  $R_{SET}$  to match the output current needs of the application.

### Scaling DAC and I<sub>SLOPE</sub> Scaling

The scale DAC is biased equivalently by either  $I_{SLOPE}$  or  $I_{RSET}$  (=  $V_{RSET}/R_{SET}$ ). That is, 1mA of either bias current results in the same  $I_{SRC}$ . In the figures of this section, Scaling DAC output current is used to represent current either into  $I_{SLOPE}$  or out of RSET pins.

#### **Color Output Current**

The color output current capability for a typical part is shown in Figures 1 and 2. In addition to scaling DAC output, the amount of I<sub>SRC</sub> will be limited by the available headroom voltage at the ISRC pin.

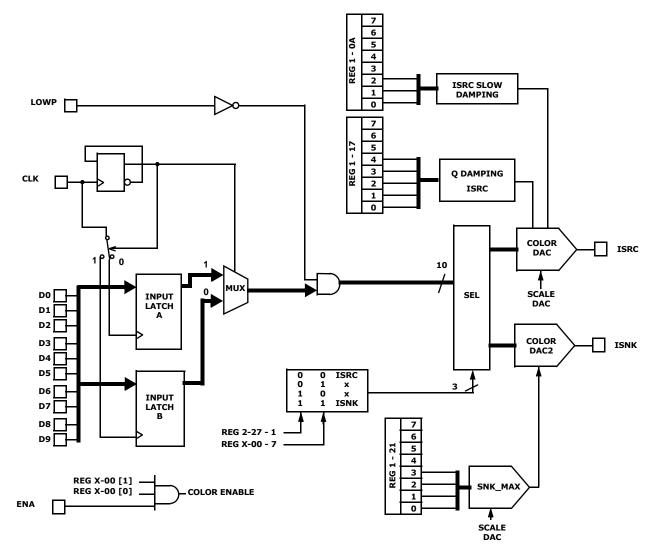

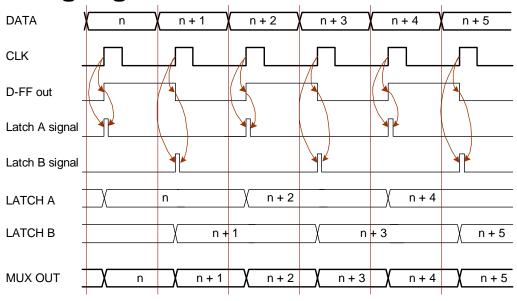

#### **Color Output Operation**

On the rising edge of CLK, the data on the Dn lines is captured. A single data bus can be shared by the three different ISL58214 chips. A separate CLK line is needed for each chip. After the data is loaded in all three colors, the rising edge of LOWP will clock the data from the first flip-flop and into the output flip-flop. Then the output current will be applied to the respective lasers at the same time.

#### **HFM Operation**

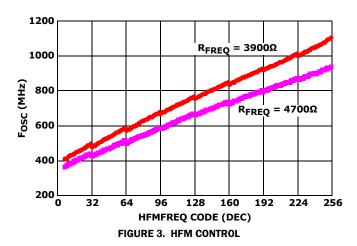

The HFM oscillator is provided to reduce speckle. The frequency range is determined by RFREQ. The actual frequency is controlled by a register. The HFM includes a spread spectrum function. The frequency of the spread spectrum oscillator and the amplitude of the frequency shift can be programmed.

#### **Threshold Current**

Threshold current may be controlled by either the Threshold DAC or the  $\rm I_{th}$  input. When set by PTHRESH register (Page 0, Addr 19h, Page 1, Addr 09h),  $\rm I_{th}$  is limited to the data sheet value, whereas the  $\rm I_{TH}$  input will allow a significantly higher value to be obtained. The threshold DAC and  $\rm I_{TH}$  currents sum together producing an input voltage on the net resistance at the ITH pin.

#### **Power Consumption**

The primary power consumption is caused by the headroom voltage across the output stage ( $V_{SO}$  -  $V_{ISRC}$ ) x  $I_{SRC}$ . In a power sensitive application, the  $V_{SO}$  can be reduced below 5.0V (but above VSOgood), so long as sufficient headroom is available to obtain the desired output current. The chip power dissipation depends on the size of the heat sink because the die is attached to a metal plate that is exposed under the package.

#### **Register Usage**

Upon power-up all registers are initialized to zero. All registers are read/writable unless otherwise specified.

Bit settings marked as "Reserved" or blank must not be used. They may be wired to legacy circuitry.

#### **Memory Map**

The address space is organized into three pages with 128 bytes each. Registers CR0, CR1, CR2, and STATUS, can be accessed from any page at the same addresses. The active page is selected via the PAGESEL bits in CR2.

#### **Register List**

| Control Register 0 Reg                | ≰X-00         |

|---------------------------------------|---------------|

| Control Register 1                    |               |

| Control Register 2 Reg                |               |

| Status Register                       | _             |

| Scale DAC High Order Bits             | <b>g0-1</b> 5 |

| HFM Frequency Setting Reş             | <b>30-16</b>  |

| HFM Amplitude Setting Reş             | g0-17         |

| Threshold Current High Order Bits Reş | <b>ؤ0-19</b>  |

| Unlink Control                        | g0-21         |

| Control Register 3 Reş                | <b>£1-08</b>  |

| Threshold Current Low Order Bits      | <b>1-09</b>   |

| Slow Damping                          | 1-0A          |

| HFM Frequency Counter Reş             | g1-0E         |

| Device ID Reş                         |               |

| Revision ID                           |               |

| Q Damping Re                          |               |

| Spread Spectrum Control Reg           | <u> </u>      |

| Threshold & Scale DAC Gain Select     |               |

| Scale DAC Low Order Bits              | 2-15          |

| OUT SelectRe                          | _             |

# **Register Bit Description**

### TABLE 1. CRO: CONTROL REGISTER 0 (REG X-00)

| BIT   | NAME                    | BIT DEFINITION                                                                                                                                                                    |

|-------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В7    | SELECT I <sub>SNK</sub> | Use in conjunction with Reg 2-27 bit 1  If B7 = 0 and Reg 2-27[1] = 0, $I_{SRC}$ is selected.  If B7 = 1 and Reg 2-27[1] = 1, $I_{SNK}$ is selected.                              |

| B6-B2 | Reserved                | Leave as 00000                                                                                                                                                                    |

| B1    | OE                      | Laser Output Enable 1: Enable laser output stage. 0: Disable laser output stage.                                                                                                  |

| во    | CE                      | Chip Enable  1: Enable device.  0: Deep sleep, analog portion of the chip is powered down. SDIO still active.  The ENA pin is ANDed with CE bit to generate internal Chip Enable. |

#### TABLE 2. CR1: CONTROL REGISTER 1 (REG X-01)

| BIT   | NAME     | BIT DEFINITION                                                                                                   |

|-------|----------|------------------------------------------------------------------------------------------------------------------|

| В7    | HFMCNTEN | HFM Counter Enable for measuring HFM frequency  1: Enable HFM counter.  0: Disable HFM counter (conserve power). |

| B6-B4 | Reserved | Leave 000                                                                                                        |

| В3    | HFMOSCEN | HFM Oscillator Enable 1: Enable. 0: Disable.                                                                     |

| B2-B0 | Reserved | Leave 000                                                                                                        |

#### TABLE 3. CR2: CONTROL REGISTER 2 (Reg X-02)

| BIT      | NAME                 | BIT DEFINITION                                                                                                                     |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| В7       | Reserved             | Leave 0                                                                                                                            |

| В6       | PAGEAUTO             | B6 = 0 means that the memory page will not auto toggle. B6 = 1 means that the Memory Page will Auto-toggle between Page0 and Page2 |

| B5<br>B4 | PAGESEL1<br>PAGESEL0 | Memory Page Select 00: Set accessed page to Page 0 01: Set accessed page to Page 1 10: Set accessed page to Page 2 11: Reserved    |

| B3-B0    | Reserved             | Leave 0000                                                                                                                         |

#### TABLE 4. SR1: STATUS REGISTER (REG X-03)

| BIT    | NAME          | BIT DEFINITION                                                                                                                                                                                              |

|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7, B3 | Reserved      |                                                                                                                                                                                                             |

| B2     | Color Enabled | 1 means color current is enabled. 0 means color current is not enabled                                                                                                                                      |

| B1     | reserved      |                                                                                                                                                                                                             |

| во     | PWR OK        | 1 means that both the 5V and internal 2.5V supplies are above the detection levels. 0 means that one or both supplies are below the detection levels. The detection levels are below the minimum specified. |

#### TABLE 5. SCALE-H: POWER MAX HIGH (REG 0-15)

| BIT   | NAME    | BIT DEFINITION                                                        |

|-------|---------|-----------------------------------------------------------------------|

| B7-B0 | SCALE-H | SCALE-H - High Order Bits Iw = k(512B7 +256B6 + +8B1 +4B0 + Reg 2-15) |

FN6944.1

July 29, 2013

#### TABLE 6. HFMFREQ: HFM FREQUENCY SETTING (REG 0-16)

| BIT   | NAME    | BIT DEFINITION                                                                                                                      |

|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------|

| B7-B0 | HFMFREQ | HFMFREQ = $F_{MIN}$ + $F_{STEP}$ (128B7 +64B6 + 32B5 + 16B4 + 8B3 + 4B2 + 2B1 + B0)<br>Note: If HFMFREQ = 00h, the HFM output is DC |

#### TABLE 7. HFMON: HFM ON-AMPLITUDE (REG 0-17)

| BIT   | NAME  | BIT DEFINITION                                                                                                                               |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| B7-B0 | HFMON | HFMON = k(128B7 +64B6 + 32B5 + 16B4 + 8B3 + 4B2 + 2B1 + B0) See "Oscillator Block Diagram" on page 20 for more details on the HFM amplitude. |

#### TABLE 8. THRESHH: THRESHOLD CURRENT HIGH ORDER BITS (REG 0-19)

| BIT   | NAME    | BIT DEFINITION                                                                    |

|-------|---------|-----------------------------------------------------------------------------------|

| B7-B0 | THRESHH | THRESH = k(2048B7 +1024B6 + + 32B1 + 16B0 + THRESHL) THRESHL bits are in Reg 1-0A |

#### TABLE 9. UNLINK: UNLINK CONTROL (REG 0-21)

| BIT   | NAME     | BIT DEFINITION                                                                                                                                                   |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В7    | Unlink   | If unlink = 1, the SCALE DAC gets its reference from the ISLOPE pin only.  If unlink = 0, the SCALE DAC gets its reference from the RSET pin and the ISLOPE pin. |

| B6-B0 | Reserved | Leave 0000000                                                                                                                                                    |

#### TABLE 10. CR3: CONTROL REGISTER 3 (REG 1-08)

| ВІТ   | NAME     | BIT DEFINITION                                                                                                                                                            |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В7    | REGRST   | Resets all registers.  1: Reset. Safety interlock allows reset bit to have effect only when lower three bits of CRO are cleared (CE = OE = WE = 0).  0: Normal operation. |

| B6-B0 | Reserved |                                                                                                                                                                           |

#### TABLE 11. THRESHL: THRESHOLD CURRENT LOW ORDER BITS (REG 1-09)

| BIT   | NAME     | BIT DEFINITION                                                      |

|-------|----------|---------------------------------------------------------------------|

| B7-B4 | Reserved | Leave 0000                                                          |

| B3-B0 | THRESH-L | THRESH-L = k(THRESH-H + 8B3 + 4B2 + 2B1 + B0), THRESH-H is Reg 0-19 |

#### TABLE 12. SLOW DAMPING CONTROL (REG 1-0A)

| ВІТ   | NAME     | BIT DEFINITION                          |

|-------|----------|-----------------------------------------|

| B7-B3 | Reserved | Leave 0000                              |

| B2-B0 | SDAMP1   | I <sub>SRC</sub> Write Waveform Damping |

#### TABLE 13. HFM FREQUENCY COUNT REGISTER (READ MODE) (REG 1-0E)

| BIT     | NAME   | BIT DEFINITION                                                                                                                                                                                                             |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7 - B0 | HFMCNT | HFM cycles when SEN is high when HFM counting is enabled. B7 is the MSB. The counter will roll-over if the count exceeds 255.  Reg X-01, bit 7 = 1 enables the HFM counter. Reg 1-0E bit 1 enables the serial HFM counter. |

FN6944.1

July 29, 2013

#### TABLE 14. HFM FREQUENCY COUNT REGISTER (WRITE MODE) (REG 1-0E)

| BIT     | NAME                    | BIT DEFINITION                                                                                                                                                                      |

|---------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7 - B2 | Reserved                |                                                                                                                                                                                     |

| B1      | Enable Serial HFM Count | If B1 = 1, the HFM counter will count when SCLK is high.  If B1 = 0, the HFM counter will not count.                                                                                |

| во      | SCLK Mode               | IF B1 above = 1, and B0 = 0, SCLK is the interval for the HFM frequency count.  If B1 above = 1, and B0 = 1, SCLK/2 is the interval for the HFM frequency count (two SCLK periods). |

#### TABLE 15. DEVICE ID (REG 1-15)

| BIT     | NAME      | BIT DEFINITION                                                                |

|---------|-----------|-------------------------------------------------------------------------------|

| B7 - B0 | Device ID | Device ID = <b>0x77</b> A different number is available for each chip family. |

#### TABLE 16. REVISION ID (REG 1-16)

| BIT     | NAME        | BIT DEFINITION                                                                   |

|---------|-------------|----------------------------------------------------------------------------------|

| B7 - B0 | Revision ID | This Rev ID is <b>0xC8</b> A number to identify the member of the device family. |

#### TABLE 17. WRITE Q DAMPING AND LD SAMPLE (REG 1-17)

| BIT     | NAME          | BIT DEFINITION                                                                                                           |

|---------|---------------|--------------------------------------------------------------------------------------------------------------------------|

| В7      | LD Sample Ena | B7 = 1 means that laser voltage sampling is enabled. B7 = 0 means that laser voltage sampling is disabled.               |

| B6 - B5 | Reserved      | Do not use                                                                                                               |

| B4 - B0 | QD4 - QD0     | Write "Q" Damping for lout1 is related to (16 QD4 + 8 QD3 + 4 QD2 + 2 QD1 + QD0). A larger number provides more damping. |

#### TABLE 18. SPREAD SPECTRUM CONTROL (REG 1-18)

| BIT     | NAME                     | BIT DEFINITION                                                                                                                                  |

|---------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| В7      | SS Frequency and Disable | If bits B7, B6, B5, and B4 are all 0, the SS is disabled. If SS width is non zero, this bit selects about 34kHz when 1, and about 53kHz when 0. |

| B6 - B4 | SS Width                 | Width ≅ k (24B6 + 2 B5 + B4)                                                                                                                    |

| B3 - B0 | Reserved                 | Do not use                                                                                                                                      |

#### TABLE 19. THRESHOLD AND SCALE DAC GAIN SELECT (REG 1-21)

| BIT     | NAME                        | BIT DEFINITION                                                                                                                                                                                                                                                                                |  |  |  |

|---------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| B7 - B4 | I <sub>THRESHOLD</sub> GAIN | The Gain of the threshold amplifier is = K(8B7 + 4B6 + 2B5 + B4). The power-up register value is 1000. A setting of 0000 defaults to a setting of 0001 to prevent zero gain.                                                                                                                  |  |  |  |

| B3 - B0 | I <sub>SNK_MAX</sub>        | If $I_{SNK}$ output is selected, these 4 bits multiply by the existing SCALE output to determine the $I_{SNK}$ fast current. The power-up register value is 1000. A setting of 0000 defaults to a setting of 0001 to prevent zero gain.  If $I_{SRC}$ is selected, these bits should be 0000. |  |  |  |

FN6944.1 July 29, 2013

#### TABLE 20. SCALE-L: POWER MAX LOW (REG 2-15)

| BIT    | NAME     | BIT DEFINITION                                                                                                                                                                      |  |  |  |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| B7, B6 | SCALE-L  | Read Only, these are the register bits.                                                                                                                                             |  |  |  |

| B5, B4 | Reserved | Do not use                                                                                                                                                                          |  |  |  |

| B3, B2 | SCALE-L  | SCALE-L - Low Order Bits Iw = k(Reg 0-15 + 2B3 +B2) see SCALE-H in Table 5. When written these bits go the SCALE-L register. When read back, these are the SCALE DAC register bits. |  |  |  |

| B1, B0 | Reserved | Do not use                                                                                                                                                                          |  |  |  |

NOTE: The lower SCALE bits and the high SCALE bits are both written from their register to the SCALE DAC at the same time that the SCALE high bits are written to their register.

#### TABLE 21. I<sub>OUT</sub> SELECT (REG 2-27)

| BIT     | NAME     | BIT DEFINITION                                                                                                                                                     |  |  |  |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| B7 - B2 | Reserved | o not use                                                                                                                                                          |  |  |  |

| B1      |          | Use in conjunction with Reg X-00 Bit 7  If B0 = 0 and Reg X-00[7] = 0, I <sub>SRC</sub> is selected.  If B1 = 1 and Reg X-00[7] = 1, I <sub>SNK</sub> is selected. |  |  |  |

| во      | Reserved | Leave 0                                                                                                                                                            |  |  |  |

#### TABLE 22. THRESHOLD CURRENT DAC REPRESENTATION

| Register bits  | THRESHH         |     |    |    |    |    |    | THRESHL |    |    |    |

|----------------|-----------------|-----|----|----|----|----|----|---------|----|----|----|

|                | В7              | В6  | B5 | В4 | В3 | B2 | B1 | во      | В3 | B2 | B1 |

| Representation | Unsigned 12-bit |     |    |    |    |    |    |         |    |    |    |

|                | B11             | B10 | В9 | В8 | В7 | В6 | B5 | В4      | В3 | B2 | B1 |

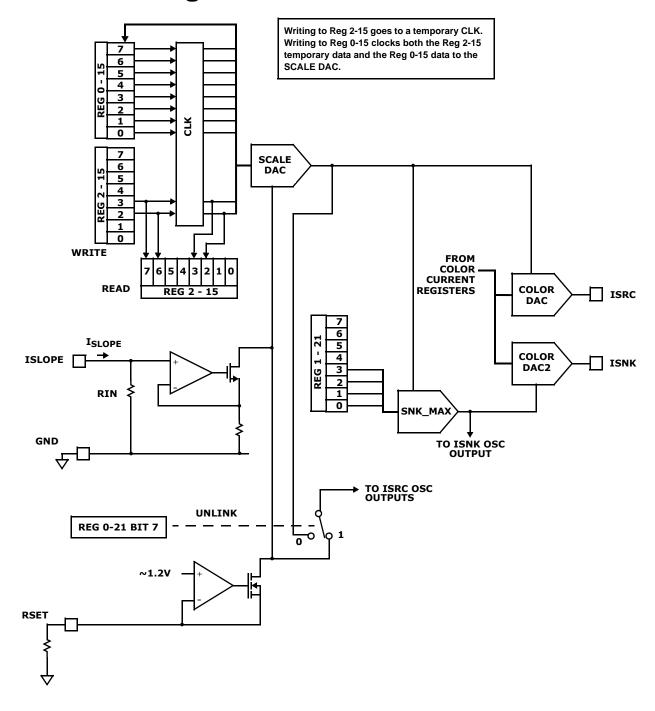

# **Scale DAC Block Diagram**

· All of the DAC's are multiplying DAC's, where the output is the product of the input code, and the applied reference signal.

# **Color Block Diagram**

# **Detailed Timing Diagram**

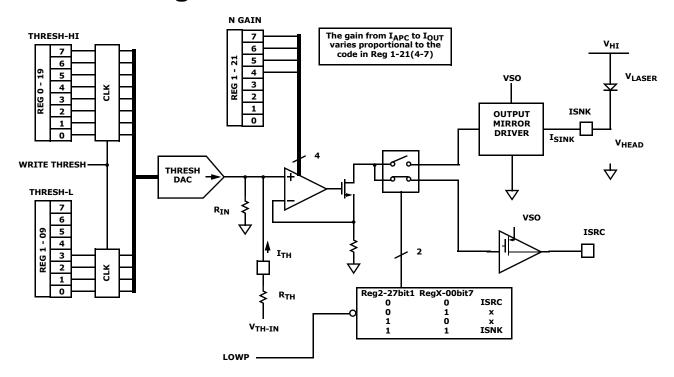

# **Threshold Block Diagram**

#### **Threshold DAC**

The THRESH DAC outputs a positive current into the net resistance at the input of the  $I_{TH}$  voltage-to-current converter amplifier. The external  $V_{TH}$  independently creates a voltage at the input of the  $I_{APC}$  amplifier. The net voltage at the input of the  $I_{APC}$  amplifier divided by  $R_{IN}$  is defined as the APC amplifier input current, even though the current is to ground. This input current multiplied by the specified gain ITH\_GAIN gives the output current IOUT\_TH. The Threshold amplifier gain varies from 0 to full scale proportional to Reg 1-21-(4-7).

The 12-bit THRESH DAC register is CLKed when THRESH-H is loaded to prevent glitches. It is designed to be a 12-bit monotonic DAC.

When Reg 1-21 = 80h, the gain from  $I_{APC}$  to  $I_{OUT}$  is about 100mA/mA for any selected output channel.

If LOWP = 1, the threshold current is set to zero.

#### **Threshold Current**

The threshold current is approximately determined by interpolation from data specs.

I<sub>OUT-THRESH</sub> = IOUT<sub>THRESH-DAC</sub> + IOUT<sub>THRESH-Ith</sub>

#### Where:

- IOUT<sub>THRESH-DAC</sub>  $\sim$ = IOUT-R-DAC x THRESH<sub>MULT</sub> x R<sub>TH</sub> / (R<sub>TH</sub> + R<sub>IN</sub>)

- IOUT<sub>THRESH-Ith</sub> ~= ITH<sub>GAIN</sub> x V<sub>TH-IN</sub> / (R<sub>TH</sub> + R<sub>IN</sub>)

- · where:

IOUT-T-DAC Gives for example: 110mA.

$R_{\mbox{\footnotesize{IN}}}$  Gives for example: 1000 typ ohms.

ITH\_GAIN Gives for example: 100 typ mA/mA.

THRESH<sub>DAC</sub>/4095, where THRESH<sub>DAC</sub>

The above equations assume a linear transfer function. At high currents there are saturation effects. Below 1V headroom, depending on the current, the predicted output will be less than predicted.

# **Oscillator Block Diagram**

#### **Oscillator Control**

A high frequency component can be added to the laser current to reduce speckle.

The HFM block has two states determined by whether the oscillator is enabled or disabled. The HFM block outputs RF modulation when the oscillator is enabled and a DC level when the oscillator is disabled. The DC level is PHFMOFF in HFMOFF mode

**TABLE 23. OSCILLATOR CONTROL LOGIC**

| X-01-3 | OSCILLATOR OUTPUT |

|--------|-------------------|

| 0      | Off               |

| 1      | On                |

### **HFM I<sub>OUT</sub> Equations**

The oscillator current is approximately determined by interpolation from the data sheet.

$IOUT_{OSC\text{-}ON} \cong A_{ON,max} \times PHFMON/255 \times K_{REF} \text{ OR Zero.}$  where:

- A<sub>ON.max</sub> = for example: 100mA (typ).

- K<sub>REF</sub> = (RSET<sub>SPEC</sub>/RSET)

- RSET<sub>SPEC</sub> = for example 620 $\Omega$ .

When the HFM oscillator is turned on, the oscillator current reaches a peak value set by PHFMON. The relation between PHFMON and average optical power is difficult to derive deterministically. First, the AC current reaching the laser is attenuated by parasitics. The higher the HFM frequency, the larger the loss. Second, if the laser is biased near threshold, the turn-on delay reduces the optical pulse width. Third, laser relaxation oscillation further shapes the optical pulse.

An empirical procedure is to first find the best conditions for the AC current (PHFMON) and frequency (HFMFREQ) in terms of read noise reduction.

#### **HFM Frequency Counter**

HFM frequency can be monitored via internal counter. The way to monitor the HFM frequency is to measure how many cycles occur during a serial clock period. If the serial clock period is known, this enables the HFM to be measured and adjusted by the drive firmware. To enable this measurement, follow the following steps:

- First clear Reg X-01 Bit 7 = 0. This allows the serial port to use the control register at Reg 1-0E.

- Set Reg 1-0E bit 1 = 1. This enables the serial clock to gate the counter.

- Set Reg1-0E bit 0 = 1. This step is optional, but recommended.

This would divide the serial clock by 2, hence increase the number of count of cycles by 2. Since SEN is not synchronized with the HFM, higher number of counts means lower the error.

- Set Reg X-01 bit 7 = 1. This allows the control logic to measure

the burst of HFM between serial clock edges. The control logic

will continue to do this on any serial transfer, either a write or a

read. The measurement is done during the address portion of

the serial cycle.

- By reading Reg 1-0E, the measurement is done.

- The HFM frequency then can be calculated as HFM freq = HFMCNT(dec) x known SCLK/2.

The amount of HFM current that reaches the laser and produces light modulation is a very complex transfer function. Although the HFM circuit simply switches between zero and the specified current, the frequency is so high that the result is heavily influenced by the chip, packages and layout.

# **Serial Interface Protocol**

R/W BIT, ADDRESS BITS, AND DATA BITS ARE CLOCKED INTO ISL58214 AT RISING EDGE OF SCLK.

R/W BIT AND ADDRESS BITS ARE CLOCKED INTO ISL58214 AT RISING EDGE OF SCLK.

DATA BITS ARE CLOCKED OUT FROM ISL58214 AT FALLING EDGE OF SCLK.

THE LAST BIT (D0) OF DATA IS CLOCKED BY THE FALLING EDGE OF SEN.

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE          | REVISION | CHANGE                                                                              |  |  |  |

|---------------|----------|-------------------------------------------------------------------------------------|--|--|--|

| July 29, 2013 | FN6944.1 | Converted to New Intersil Template. Changed Products information to About Intersil. |  |  |  |

| May 13, 2010  | FN6944.0 | Initial Release                                                                     |  |  |  |

### **About Intersil**

Intersil Corporation is a leader in the design and manufacture of high-performance analog, mixed-signal and power management semiconductors. The company's products address some of the largest markets within the industrial and infrastructure, personal computing and high-end consumer markets. For more information about Intersil, visit our website at <a href="https://www.intersil.com">www.intersil.com</a>.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com/en/support/ask-an-expert.html">www.intersil.com/en/support/ask-an-expert.html</a>. Reliability reports are also available from our website at <a href="https://www.intersil.com/en/support/qualandreliability.html#reliability">https://www.intersil.com/en/support/qualandreliability.html#reliability</a>

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

intersil

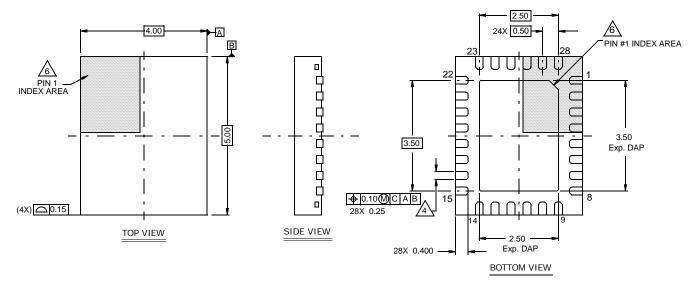

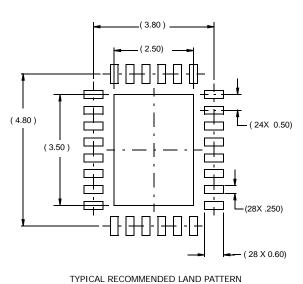

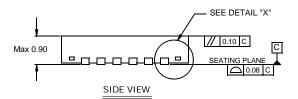

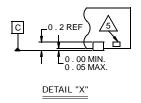

### **Package Outline Drawing**

### L28.4x5A

28 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE

Rev 2, 06/08

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.