# 2.5A Regulator with Integrated High-Side MOSFET for Synchronous Buck or Boost Buck Converter

# ISL85402

The ISL85402 is a synchronous buck controller with a  $125m\Omega$  high-side MOSFET and low-side driver integrated. The ISL85402 supports a wide input range of 3V to 36V in buck mode. It supports 2.5A continuous load under conditions of 5V  $V_{OUT}$ ,  $V_{IN}$  range of 8V to 36V, 500kHz and +105 °C ambient temperature with still air. For any specific application, the actual maximum output current depends upon the die temperature not exceeding +125 °C with the power dissipated in the IC, which is related to input voltage, output voltage, duty cycle, switching frequency, board layout and ambient temperature, etc. Refer to "Output Current" on page 14 for more details.

The ISL85402 has a flexible selection of operation modes of forced PWM mode and PFM mode. In PFM mode, the quiescent input current is as low as 180 $\mu$ A (AUXVCC connected to V<sub>OUT</sub>). The load boundary between PFM and PWM can be programmed to cover wide applications.

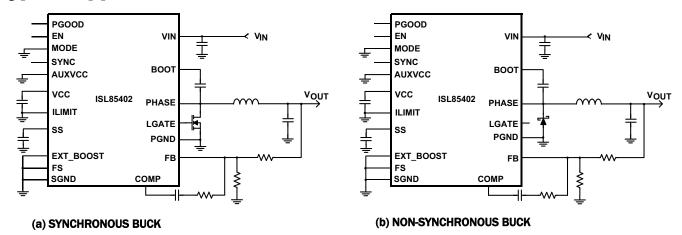

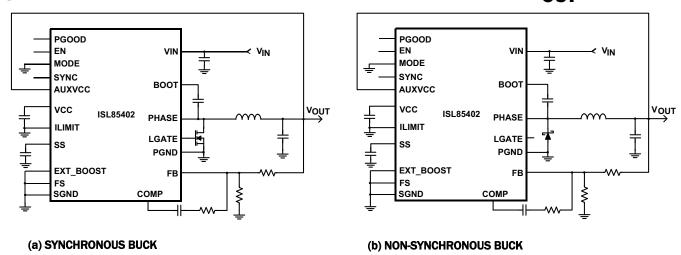

The low-side driver can be either used to drive an external low-side MOSFET for a synchronous buck, or left unused for a standard non-synchronous buck. The low-side driver can also be used to drive a boost converter as a pre-regulator followed by a buck controlled by the same IC, which greatly expands the operating input voltage range down to 2.5V or lower (Refer to "Typical Application Schematic III - Boost Buck Converter" on page 5).

The ISL85402 offers the most robust current protections. It uses peak current mode control with cycle-by-cycle current limiting. It is implemented with frequency foldback under current limit condition; besides that, the hiccup overcurrent mode is also implemented to guarantee reliable operations under harsh short conditions.

The ISL85402 has comprehensive protections against various faults including overvoltage and over-temperature protections, etc.

## **Features**

- Buck Mode: Input Voltage Range 3V to 36V (Refer to "Input Voltage" on page 13 for more details)

- Boost Mode Expands Operating Input Voltage Lower Than 2.5V (Refer to "Input Voltage" on page 13 for more details)

- Selectable Forced PWM Mode or PFM Mode

- 300µA IC Quiescent Current (PFM, No Load); 180µA Input Quiescent Current (PFM, No Load, V<sub>OUT</sub> Connected to AUXVCC)

- Less than 3µA Shut Down Input Current (IC Disabled)

- · Operational Topologies

- Synchronous Buck

- Non-Synchronous Buck

- Two-Stage Boost Buck

- Programmable Frequency from 200kHz to 2.2MHz and Frequency Synchronization Capability

- ±1% Tight Voltage Regulation Accuracy

- Reliable Overcurrent Protection

- Temperature Compensated Current Sense

- Cycle-by-Cycle Current Limiting with Frequency Foldback

- Hiccup Mode for Worst Case Short Condition

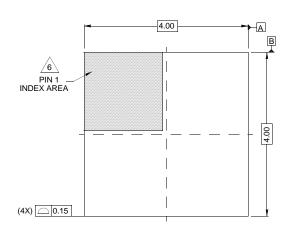

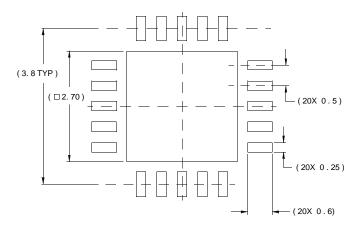

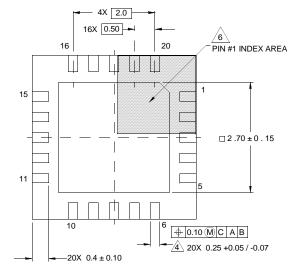

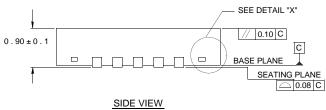

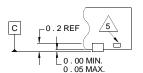

- 20 Ld 4x4 QFN Package

- Pb-Free (RoHS Compliant)

# **Applications**

- General Purpose

- 24V Bus Power

- · Battery Power

- Point of Load

- Embedded Processor and I/O Supplies

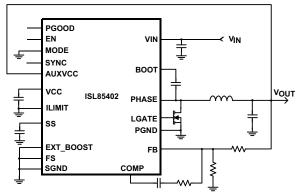

FIGURE 1. TYPICAL APPLICATION

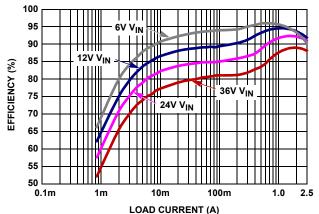

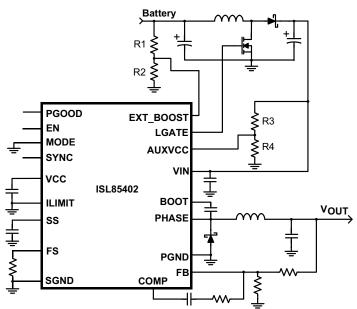

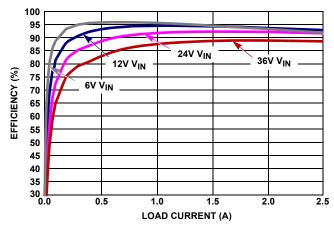

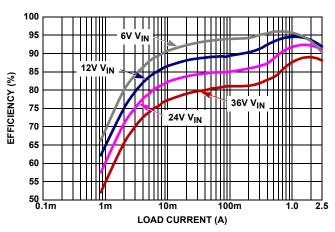

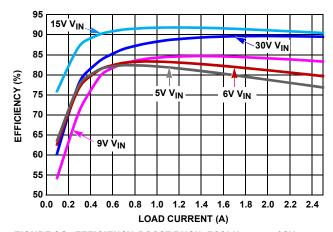

FIGURE 2. EFFICIENCY, SYNCHRONOUS BUCK, PFM MODE,

V<sub>OUT</sub> 5V, T<sub>A</sub> = +25°C

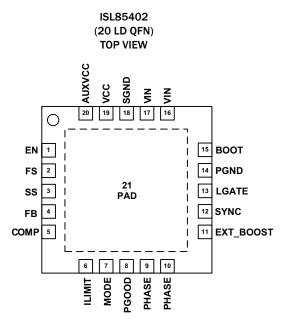

# **Pin Configuration**

# **Functional Pin Descriptions**

| PIN NAME PIN # |                                                                                                                                                                                                                                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| EN             | 1                                                                                                                                                                                                                                             | The controller is enabled when this pin is left floating or pulled HIGH. The IC is disabled when this pin is pulled LOW. Range: OV to 5.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| FS             | 2                                                                                                                                                                                                                                             | Connecting this pin to VCC, or GND, or leaving it open will force the IC to have 500kHz switching frequency. The oscillator switching frequency can also be programmed by adjusting the resistor from this pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| SS             | 3                                                                                                                                                                                                                                             | Connect a capacitor from this pin to ground. This capacitor, along with an internal 5µA current source, sets the soft-start interval of the converter. Also, this pin can be used to track a ramp on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| FB             | 4                                                                                                                                                                                                                                             | This pin is the inverting input of the voltage feedback error amplifier. With a properly selected resistor divider connected from V <sub>OUT</sub> to FB, the output voltage can be set to any voltage between the power rail (reduced by maximum duty cycle and voltage drop) and the 0.8V reference. Loop compensation is achieved by connecting an RC network across COMP and FB. The FB pin is also monitored for overvoltage events.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| COMP           | 5                                                                                                                                                                                                                                             | Output of the voltage feedback error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| ILIMIT         | Programmable current limit pin. With this pin connected to the VCC pin, or to GND, or left open, the current limiting thres is set to default of 3.6A; the current limiting threshold can be programmed with a resistor from this pin to GND. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| MODE           | 7                                                                                                                                                                                                                                             | Mode selection pin. Pull this pin to GND for forced PWM mode; to have it floating or connected to VCC will enable PFM m when the peak inductor current is below the default threshold of 700mA. The current boundary threshold between PFM PWM can also be programmed with a resistor at this pin to ground. Check for more details in the "PFM Mode Operation page 13.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| PGOOD          | 8                                                                                                                                                                                                                                             | PG00D is an open drain output that will be pulled low immediately under the events when the output is out of regulation (0V or UV) or when the EN pin is pulled low. PG00D is equipped with a fixed delay of 1000 cycles upon output power-up ( $V_0 > 90\%$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| PHASE          | 9, 10                                                                                                                                                                                                                                         | These pins are the PHASE nodes that should be connected to the output inductor. These pins are connected to the source of the high-side N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| EXT_BOOST      | 11                                                                                                                                                                                                                                            | This pin is used to set boost mode and monitor the battery voltage that is the input of the boost converter. After VCC POR, the controller will detect the voltage on this pin; if voltage on this pin is below 200mV, the controller is set in synchronous/non-synchronous buck mode and will latch in this state unless VCC is below POR falling threshold; if the voltage on this pin after VCC POR is above 200mV, the controller is set in boost mode and latch in this state. In boost mode, the low-side driver output PWM with same duty cycle with upper-side driver to drive the boost switch.  In boost mode, this pin is used to monitor input voltage through a resistor divider. By setting the resistor divider, the high threshold and hysteresis can be programmed. When voltage on this pin is above 0.8V, the PWM output (LGATE) for the boost converter is disabled, and when voltage on this pin is below 0.8V minus the hysteresis, the boost PWM is enabled.  In boost mode operation, PFM is disabled when boost PWM is enabled. Check the "Boost Converter Operation" on page 14 for more details. |  |  |  |  |

# Functional Pin Descriptions (Continued)

| PIN NAME | PIN#   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SYNC     | 12     | This pin can be used to synchronize two or more ISL85402 controllers. Multiple ISL85402s can be synchronized with their SYNC pins connected together. 180 degree phase shift is automatically generated between the master and slave ICs. The internal oscillator can also lock to an external frequency source applied on this pin with square pulse waveform (with frequency 10% higher than the IC's local frequency, and pulse width higher than 150ns). Range: 0V to 5.5V. This pin should be left floating if not used.                                                     |  |  |

| LGATE    | 13     | In synchronous buck mode, this pin is used to drive the lower side MOSFET to improve efficiency.  In non-synchronous buck when a diode is used as the bottom side power device, this pin should be connected to VCC before VCC startup to have low-side driver (LGATE) disabled.  In boost mode, it can be used to drive the boost power MOSFET. The boost control PWM is same with the buck control PWM.                                                                                                                                                                         |  |  |

| PGND     | 14     | This pin is used as the ground connection of the power flow including driver. Connect it to large ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| воот     | 15     | This pin provides bias voltage to the high-side MOSFET driver. A bootstrap circuit is used to create a voltage suitable to drive the internal N-channel MOSFET. The boot charge circuitries are integrated inside of the IC. No external boot diode is needed. A 1µF ceramic capacitor is recommended to be used between BOOT and PHASE pin.                                                                                                                                                                                                                                      |  |  |

| VIN      | 16, 17 | Connect the input rail to these pins that are connected to the drain of the integrated high-side MOSFET as well as the so for the internal linear regulator that provides the bias of the IC. Range: 3V to 36V.  With the part switching, the operating input voltage applied to the VIN pins must be under 36V. This recommendation all for short voltage ringing spikes (within a couple of ns time range) due to switching while not exceeding "Absolute Maxim Ratings" on page 6.                                                                                             |  |  |

| SGND     | 18     | This pin provides the return path for the control and monitor portions of the IC. Connect it to a quiet ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| vcc      | 19     | This pin is the output of the internal linear regulator that supplies the bias for the IC including the driver. A minimum 4.7µF decoupling ceramic capacitor is recommended between VCC to ground.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| AUXVCC   | 20     | This pin is the input of the auxiliary internal linear regulator, which can be supplied by the regulator output after power-up. With such configuration, the power dissipation inside of the IC is reduced. The input range for this LDO is 3V to 20V. In boost mode operation, this pin works as boost output overvoltage detection pin. It detects the boost output through a resistor divider. When voltage on this pin is above 0.8V, the boost PWM is disabled; and when voltage on this pin is below 0.8V minus the hysteresis, the boost PWM is enabled. Range: 0V to 20V. |  |  |

| PAD      | 21     | Bottom thermal pad. It is not connected to any electrical potential of the IC. In layout it must be connected to PCB ground copper plane with area as large as possible to effectively reduce the thermal impedance.                                                                                                                                                                                                                                                                                                                                                              |  |  |

# **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING  | TEMP.<br>RANGE (°C) | PACKAGE<br>(PB-Free) | PKG. DWG. # |

|--------------------------------|------------------|---------------------|----------------------|-------------|

| ISL85402IRZ                    | 85 402IRZ        | -40 to +105         | 20 Ld 4x4 QFN        | L20.4x4C    |

| ISL85402EVAL1Z                 | Evaluation Board |                     |                      |             |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL85402</u>. For more information on MSL please see techbrief <u>TB363</u>.

4

intersil

# **Typical Application Schematic I**

# Typical Application Schematic II - VCC Switch-Over to $V_{OUT}$

# **Typical Application Schematic III - Boost Buck Converter**

# **Absolute Maximum Ratings**

| VIN, PHASE                                                                |

|---------------------------------------------------------------------------|

| VCC                                                                       |

| AUXVCC                                                                    |

| Absolute Boot Voltage, V <sub>BOOT</sub> +50.0V                           |

| Upper Driver Supply Voltage, V <sub>BOOT</sub> - V <sub>PHASE</sub> +6.0V |

| All Other Pins GND - 0.3V to VCC + 0.3V                                   |

| ESD Rating                                                                |

| Human Body Model (Tested per JESD22-A114F)2000V                           |

| Machine Model (Tested per JESD22-A115C) 200V                              |

| Charged Device Model (Tested per JESD22-C101E) 1000V                      |

| Latchup Rating (Tested per JESD78B; Class II, Level A) 100mA              |

## **Thermal Information**

| Thermal Resistance                          | $\theta_{JA}(^{\circC/W})$ | $\theta_{JC}(\mathrm{^{\circ}C/W})$ |

|---------------------------------------------|----------------------------|-------------------------------------|

| ISL85402 QFN 4x4 Package (Notes 4, 5)       | 40                         | 3.5                                 |

| Maximum Junction Temperature (Plastic Packa | age)                       | +150°C                              |

| Maximum Storage Temperature Range           | 6                          | 5°C to +150°C                       |

| Pb-free reflow profile                      |                            | see link below                      |

| http://www.intersil.com/pbfree/Pb-FreeR     | eflow.asp                  |                                     |

# **Recommended Operating Conditions**

| Supply Voltage on V <sub>IN</sub> | 3V to 36V          |

|-----------------------------------|--------------------|

| AUXVCC                            | GND - 0.3V to +20V |

| Ambient Temperature Range         | 40°C to +105°C     |

| Junction Temperature Range        | 40°C to +125°C     |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. For  $\theta_{1C}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Refer to "Block Diagram" on page 4 and "Typical Application Schematics" on page 5. Operating Conditions Unless Otherwise Noted:  $V_{IN} = 12V$ , or  $V_{CC} = 4.5V \pm 10\%$ ,  $T_A = -40$ °C to  $\pm 105$ °C. Typicals are at  $T_A = \pm 25$ °C. **Boldface limits apply over the operating temperature range, -40**°C to  $\pm 105$ °C.

| PARAMETER                                     | SYMBOL                    | TEST CONDITIONS                                                                             | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS |

|-----------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------|-----------------|------|-----------------|-------|

| V <sub>IN</sub> PIN SUPPLY                    |                           |                                                                                             | •               |      | •               |       |

| VIN Pin Voltage Range                         |                           | VIN Pin                                                                                     | 3.05            |      | 36              | V     |

|                                               |                           | VIN Pin connected to VCC                                                                    | 3.05            |      | 5.5             | V     |

| Operating Supply Current                      | IQ                        | MODE = VCC/FLOATING (PFM), no load at the output                                            |                 | 300  |                 | μΑ    |

|                                               |                           | MODE = GND (Forced PWM), V <sub>IN</sub> = 12V, IC Operating, Not Including Driving Current |                 | 1.2  |                 | mA    |

| Shut Down Supply Current                      | I <sub>IN_SD</sub>        | EN connected to GND, V <sub>IN</sub> = 12V                                                  |                 | 1.8  | 3               | μΑ    |

| INTERNAL MAIN LINEAR REGULATOR                |                           |                                                                                             |                 |      |                 |       |

| MAIN LDO V <sub>CC</sub> Voltage              | v <sub>cc</sub>           | V <sub>IN</sub> > 5V                                                                        | 4.2             | 4.5  | 4.8             | ٧     |

| MAIN LDO Dropout Voltage                      | V <sub>DROPOUT_MAIN</sub> | V <sub>IN</sub> = 4.2V, I <sub>VCC</sub> = 35mA                                             |                 | 0.3  | 0.5             | V     |

|                                               |                           | V <sub>IN</sub> = 3V, I <sub>VCC</sub> = 25mA                                               |                 | 0.25 | 0.3             | V     |

| V <sub>CC</sub> Current Limit of MAIN LDO     |                           |                                                                                             |                 | 60   |                 | mA    |

| INTERNAL AUXILIARY LINEAR REGULATOR           |                           |                                                                                             |                 |      |                 |       |

| AUXVCC Input Voltage Range                    | V <sub>AUXVCC</sub>       |                                                                                             | 3               |      | 20              | V     |

| AUX LDO V <sub>CC</sub> Voltage               | v <sub>cc</sub>           | V <sub>AUXVCC</sub> > 5V                                                                    | 4.2             | 4.5  | 4.8             | V     |

| LDO Dropout Voltage                           | V <sub>DROPOUT_AUX</sub>  | V <sub>AUXVCC</sub> = 4.2V, I <sub>VCC</sub> = 35mA                                         |                 | 0.3  | 0.5             | V     |

|                                               |                           | V <sub>AUXVCC</sub> = 3V, I <sub>VCC</sub> = 25mA                                           |                 | 0.25 | 0.3             | V     |

| Current Limit of AUX LDO                      |                           |                                                                                             |                 | 60   |                 | mA    |

| AUX LDO Switch-over Rising Threshold          | V <sub>AUXVCC_RISE</sub>  | AUXVCC voltage rise; Switch to Auxiliary LDO                                                | 3               | 3.1  | 3.2             | V     |

| AUX LDO Switch-over Falling Threshold Voltage | V <sub>AUXVCC_FALL</sub>  | AUXVCC voltage fall; Switch back to main BIAS LDO                                           | 2.73            | 2.87 | 2.97            | V     |

| AUX LDO Switch-over Hysteresis                | V <sub>AUXVCC_HYS</sub>   | AUXVCC Switch-over Hysteresis                                                               |                 | 0.2  |                 | ٧     |

**Electrical Specifications** Refer to "Block Diagram" on page 4 and "Typical Application Schematics" on page 5. Operating Conditions Unless Otherwise Noted:  $V_{IN} = 12V$ , or  $V_{CC} = 4.5V \pm 10\%$ ,  $T_A = -40$  °C to  $\pm 105$  °C. Typicals are at  $T_A = \pm 25$  °C. **Boldface limits apply over the operating temperature range, -40** °C to  $\pm 105$  °C. (Continued)

| PARAMETER                                                 | SYMBOL                 | TEST CONDITIONS                            | MIN<br>(Note 6) | TYP          | MAX<br>(Note 6) | UNITS |

|-----------------------------------------------------------|------------------------|--------------------------------------------|-----------------|--------------|-----------------|-------|

| POWER-ON RESET                                            |                        |                                            | •               |              |                 |       |

| Rising V <sub>CC</sub> POR Threshold                      | V <sub>PORH_RISE</sub> |                                            | 2.82            | 2.9          | 3.05            | V     |

| Falling V <sub>CC</sub> POR Threshold                     | V <sub>PORL_FALL</sub> |                                            |                 | 2.6          | 2.8             | V     |

| V <sub>CC</sub> POR Hysteresis                            | V <sub>PORL_HYS</sub>  |                                            |                 | 0.3          |                 | V     |

| ENABLE                                                    |                        |                                            | 1               | I            | J.              |       |

| Required Enable On Voltage                                | V <sub>ENH</sub>       |                                            | 2               |              |                 | V     |

| Required Enable Off Voltage                               | V <sub>ENL</sub>       |                                            |                 |              | 0.8             | V     |

| EN Pull-up Current                                        | I <sub>EN_PULLUP</sub> | EN Left Floating, V <sub>IN</sub> = 24V    |                 | 0.8          |                 | μΑ    |

|                                                           |                        | EN Left Floating, V <sub>IN</sub> = 12V    |                 | 0.5          |                 | μA    |

|                                                           |                        | EN Left Floating, V <sub>IN</sub> = 5V     |                 | 0.25         |                 | μΑ    |

| OSCILLATOR                                                | 1                      |                                            | - 11            |              |                 |       |

| PWM Frequency                                             | Fosc                   | R <sub>FS</sub> = 665kΩ                    | 160             | 200          | 240             | kHz   |

|                                                           |                        | $R_{FS} = 51.1k\Omega$                     | 1950            | 2200         | 2450            | kHz   |

|                                                           |                        | FS Pin Connected to VCC or Floating or GND | 450             | 500          | 550             | kHz   |

| MIN ON Time                                               | t <sub>MIN_ON</sub>    |                                            |                 | 130          | 225             | ns    |

| MIN OFF Time                                              | t <sub>MIN_OFF</sub>   |                                            |                 | 210          | 325             | ns    |

| SYNCHRONIZATION                                           | 1                      |                                            |                 |              |                 | ı     |

| Input High Threshold                                      | VIH                    |                                            |                 | 2            |                 | V     |

| Input Low Threshold                                       | VIL                    |                                            |                 | 0.5          |                 | V     |

| Input Minimum Pulse Width                                 |                        |                                            |                 | 25           |                 | ns    |

| Input Impedance                                           |                        |                                            |                 | 100          |                 | kΩ    |

| Input Minimum Frequency Divided by Free Running Frequency |                        |                                            |                 | 1.1          |                 |       |

| Input Maximum Frequency Divided by Free Running Frequency |                        |                                            |                 | 1.6          |                 |       |

| Output Pulse Width                                        |                        | C <sub>SYNC</sub> = 100pF                  |                 | 100          |                 | ns    |

| Output Pulse High                                         | VOH                    | $R_{LOAD} = 1k\Omega$                      |                 | VCC-<br>0.25 |                 | V     |

| Output Pulse Low                                          | VOL                    |                                            |                 | GND          |                 | V     |

| REFERENCE VOLTAGE                                         |                        |                                            |                 |              |                 |       |

| Reference Voltage                                         | V <sub>REF</sub>       |                                            |                 | 0.8          |                 | V     |

| System Accuracy                                           |                        |                                            | -1.0            |              | +1.0            | %     |

| FB Pin Source Current                                     |                        |                                            |                 | 5            |                 | nA    |

| Soft-start                                                |                        |                                            |                 |              |                 |       |

| Soft-Start Current                                        | I <sub>SS</sub>        |                                            | 3               | 5            | 7               | μΑ    |

| ERROR AMPLIFIER                                           | 1                      |                                            | 1               | 1            | 1               | 1     |

| Unity Gain-Bandwidth                                      |                        | C <sub>LOAD</sub> = 50pF                   |                 | 10           |                 | MHz   |

| DC Gain                                                   |                        | C <sub>LOAD</sub> = 50pF                   |                 | 88           |                 | dB    |

| Maximum Output Voltage                                    |                        |                                            |                 | 3.6          |                 | V     |

**Electrical Specifications** Refer to "Block Diagram" on page 4 and "Typical Application Schematics" on page 5. Operating Conditions Unless Otherwise Noted:  $V_{IN} = 12V$ , or  $V_{CC} = 4.5V \pm 10\%$ ,  $T_A = -40$  °C to  $\pm 105$  °C. Typicals are at  $T_A = \pm 25$  °C. **Boldface limits apply over the operating temperature range, -40** °C to  $\pm 105$  °C. (Continued)

| PARAMETER                                      | SYMBOL                               | TEST CONDITIONS                                      | MIN<br>(Note 6) | TYP   | MAX<br>(Note 6) | UNITS |

|------------------------------------------------|--------------------------------------|------------------------------------------------------|-----------------|-------|-----------------|-------|

| Minimum Output Voltage                         |                                      |                                                      |                 | 0.5   |                 | ٧     |

| Slew Rate                                      | SR                                   | C <sub>LOAD</sub> = 50pF                             |                 | 5     |                 | V/µs  |

| PFM MODE CONTROL                               |                                      |                                                      |                 |       |                 |       |

| Default PFM Current Threshold                  |                                      | MODE = VCC or Floating                               |                 | 700   |                 | mA    |

| INTERNAL HIGH-SIDE MOSFET                      |                                      |                                                      |                 |       |                 |       |

| Upper MOSFET r <sub>DS(ON)</sub>               | r <sub>DS(ON)_</sub> UP              |                                                      |                 | 125   | 180             | mΩ    |

| LOW-SIDE MOSFET GATE DRIVER                    |                                      |                                                      | ll .            |       |                 |       |

| LGate Source Resistance                        |                                      | 100mA Source Current                                 |                 | 3.5   |                 | Ω     |

| LGATE Sink Resistance                          |                                      | 100mA Sink Current                                   |                 | 3.3   |                 | Ω     |

| BOOST CONVERTER CONTROL                        |                                      |                                                      |                 |       |                 |       |

| EXT_BOOST Boost_Off Threshold Voltage          |                                      |                                                      | 0.74            | 0.8   | 0.86            | V     |

| EXT_BOOST Hysteresis Sink Current              | I <sub>EXT_BOOST_HYS</sub>           |                                                      | 2.4             | 3.2   | 3.8             | μΑ    |

| AUXVCC Boost Turn-Off Threshold Voltage        |                                      |                                                      | 0.74            | 0.8   | 0.86            | V     |

| AUXVCC Hysteresis Sink Current                 | I <sub>AUXVCC_HYS</sub>              |                                                      | 2.4             | 3.2   | 3.8             | μΑ    |

| POWER-GOOD MONITOR                             |                                      |                                                      |                 |       |                 |       |

| Overvoltage Rising Trip Point                  | V <sub>FB/</sub> V <sub>REF</sub>    | Percentage of Reference Point                        | 104             | 110   | 116             | %     |

| Overvoltage Rising Hysteresis                  | V <sub>FB/</sub> V <sub>OVTRIP</sub> | Percentage Below OV Trip Point                       |                 | 3     |                 | %     |

| Undervoltage Falling Trip Point                | V <sub>FB/</sub> V <sub>REF</sub>    | Percentage of Reference Point                        | 84              | 90    | 96              | %     |

| Undervoltage Falling Hysteresis                | V <sub>FB/</sub> V <sub>UVTRIP</sub> | Percentage Above UV Trip Point                       |                 | 3     |                 | %     |

| PGOOD Rising Delay                             | t <sub>PGOOD_DELAY</sub>             | f <sub>OSC</sub> = 500kHz                            |                 | 2     |                 | ms    |

| PGOOD Leakage Current                          |                                      | PGOOD HIGH, V <sub>PGOOD</sub> = 4.5V                |                 | 10    |                 | nA    |

| PGOOD Low Voltage                              | V <sub>PGOOD</sub>                   | PGOOD LOW, IPGOOD = 0.2mA                            |                 | 0.10  |                 | V     |

| OVERCURRENT PROTECTION                         |                                      |                                                      |                 |       |                 |       |

| Default Cycle-by-Cycle Current Limit Threshold | loc_1                                | I <sub>LIMIT</sub> = GND or VCC or Floating          | 3               | 3.6   | 4.2             | Α     |

| Hiccup Current Limit Threshold                 | I <sub>OC_2</sub>                    | Hiccup, I <sub>OC_2</sub> /I <sub>OC_1</sub>         |                 | 115   |                 | %     |

| OVERVOLTAGE PROTECTION                         |                                      |                                                      |                 |       |                 |       |

| OV Latching-off Trip Point                     |                                      | Percentage of Reference Point<br>LG = UG = LATCH LOW |                 | 120   |                 | %     |

| OV Non-Latching-off Trip Point                 |                                      | Percentage of Reference Point<br>LG = UG = LOW       |                 | 110   |                 | %     |

| OV Non-Latching-off Release Point              |                                      | Percentage of Reference Point                        |                 | 102.5 |                 | %     |

| OVER-TEMPERATURE PROTECTION                    |                                      |                                                      | ·               |       | •               |       |

| Over-Temperature Trip Point                    |                                      |                                                      |                 | 155   |                 | °C    |

| Over-Temperature Recovery Threshold            |                                      |                                                      |                 | 140   |                 | °C    |

#### NOTE:

<sup>6.</sup> Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

# **Performance Curves**

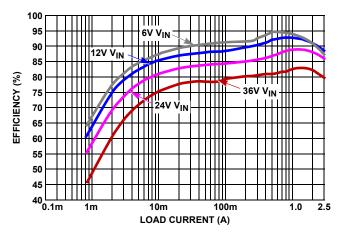

FIGURE 3. EFFICIENCY, SYNCHRONOUS BUCK, FORCED PWM MODE, 500kHz,  $V_{OUT}$  5V,  $T_A$  = +25°C

FIGURE 4. EFFICIENCY, SYNCHRONOUS BUCK, PFM MODE,  $V_{OUT}$  5V,  $T_A$  = +25 °C

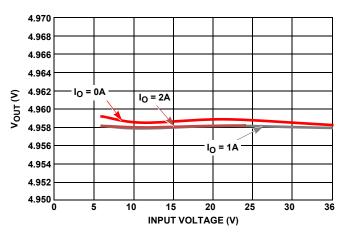

FIGURE 5. LINE REGULATION, V<sub>OUT</sub> 5V, T<sub>A</sub> = +25°C

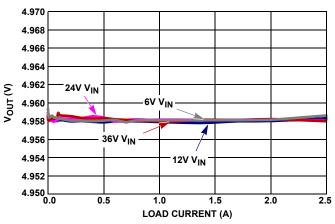

FIGURE 6. LOAD REGULATION, V<sub>OUT</sub> 5V, T<sub>A</sub> = +25°C

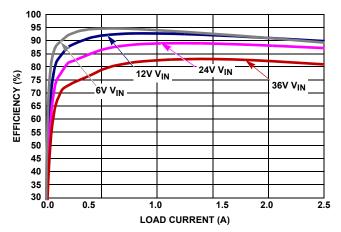

FIGURE 7. EFFICIENCY, SYNCHRONOUS BUCK, FORCED PWM MODE, 500kHz, V<sub>OUT</sub> 3.3V, T<sub>A</sub> = +25°C

FIGURE 8. EFFICIENCY, SYNCHRONOUS BUCK, PFM MODE,  $V_{OUT}$  3.3V,  $T_A$  = +25 °C

# Performance Curves (Continued)

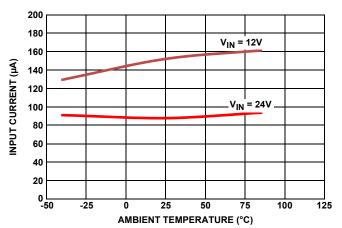

FIGURE 9. INPUT QUIESCENT CURRENT UNDER NO LOAD, PFM MODE,  $V_{OUT} = 5V$

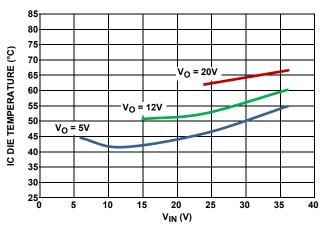

FIGURE 10. IC DIE TEMPERATURE UNDER +25°C AMBIENT TEMPERATURE, STILL AIR, 500kHz, I<sub>0</sub> = 2A

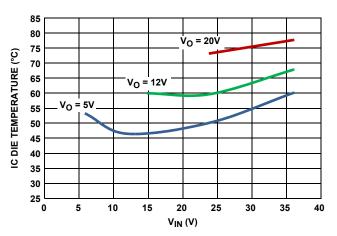

FIGURE 11. IC DIE TEMPERATURE UNDER +25°C AMBIENT TEMPERATURE, STILL AIR, 500kHz,  $I_0 = 2.5$ A

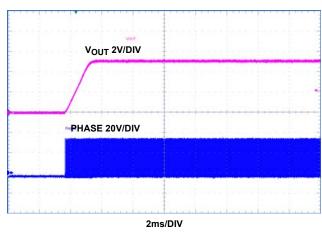

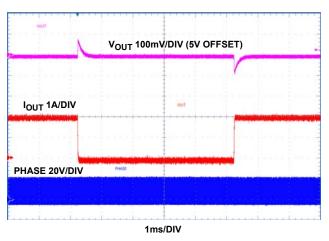

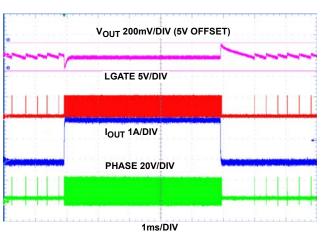

FIGURE 12. SYNCHRONOUS BUCK MODE,  $V_{\mbox{\footnotesize IN}}$  36V,  $I_{\mbox{\footnotesize O}}$  2A, ENABLE ON

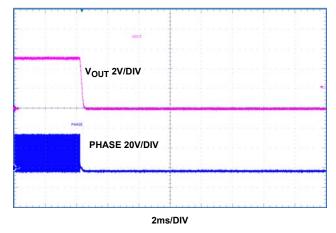

FIGURE 13. SYNCHRONOUS BUCK MODE,  $V_{\mbox{\footnotesize IN}}$  36V,  $I_{\mbox{\footnotesize O}}$  2A, ENABLE OFF

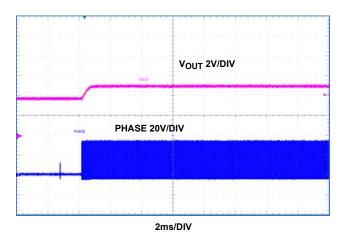

FIGURE 14. V<sub>IN</sub> 36V, PREBIASED START-UP

# Performance Curves (Continued)

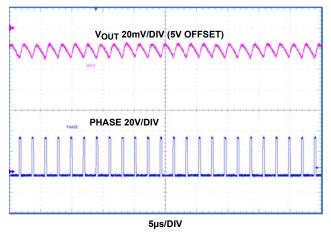

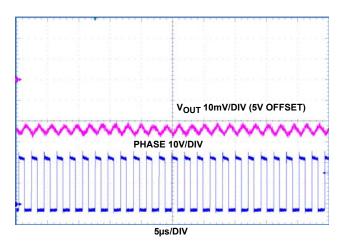

FIGURE 15. SYNCHRONOUS BUCK WITH FORCE PWM MODE,  $V_{IN}$  36V,  $I_{O}$  2A

FIGURE 16. V<sub>IN</sub> 24V, 0 TO 2A STEP LOAD, FORCE PWM MODE

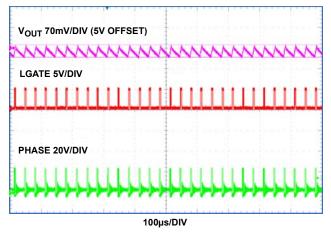

FIGURE 17. V<sub>IN</sub> 24V, 80mA LOAD, PFM MODE

FIGURE 18. V<sub>IN</sub> 24V, 0 TO 2A STEP LOAD, PFM MODE

FIGURE 19. NON-SYNCHRONOUS BUCK, FORCE PWM MODE,  $V_{\mbox{\scriptsize IN}}$  12V, NO LOAD

FIGURE 20. NON-SYNCHRONOUS BUCK, FORCE PWM MODE,  $V_{\text{IN}}$  12V, 2A

# Performance Curves (Continued)

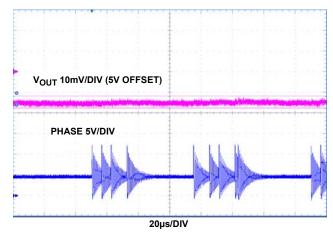

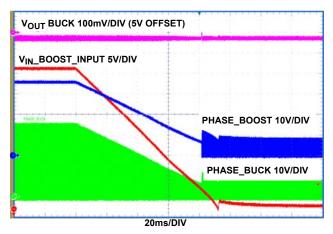

FIGURE 21. BOOST BUCK MODE, BOOST INPUT STEP FROM 36V TO 3V,  $V_{OUT}$  BUCK = 5V,  $I_{OUT}$ \_BUCK = 1A

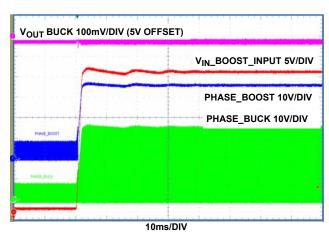

FIGURE 22. BOOST BUCK MODE, BOOST INPUT STEP FROM 3V TO 36V, V<sub>OUT</sub> BUCK = 5V, I<sub>OUT</sub>BUCK = 1A

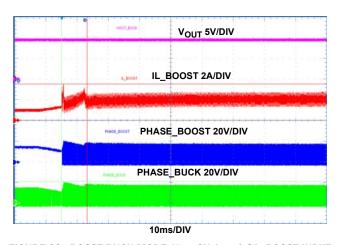

FIGURE 23. BOOST BUCK MODE,  $V_0 = 9V$ ,  $I_0 = 1.8A$ , BOOST INPUT DROPS FROM 16V TO 9V DC

FIGURE 24. EFFICIENCY, BOOST BUCK, 500kHz,  $V_{OUT}$  12V,  $T_A = +25\,^{\circ}\text{C}$

# **Functional Description**

#### Initialization

Initially the ISL85402 continually monitors the voltage at the EN pin. When the voltage on the EN pin exceeds its rising ON threshold, the internal LDO will start up to build up VCC. After Power-On Reset (POR) circuits detect that VCC voltage has exceeded the POR threshold, the soft-start will be initiated.

#### **Soft-Start**

The soft-start (SS) ramp is built up in the external capacitor on the SS pin that is charged by an internal 5µA current source.

$$\textbf{C}_{\textbf{SS}}[\mu\textbf{F}] = \textbf{6.5} \cdot \textbf{t}_{\textbf{SS}}[\textbf{S}] \tag{EQ. 1}$$

The SS ramp starts from 0 to a voltage above 0.8V. Once SS reaches 0.8V, the bandgap reference takes over and IC gets into steady state operation.

The SS plays a vital role in the hiccup mode of operation. The IC works as cycle-by-cycle peak current limiting at over load condition. When a harsh condition occurs and the current in the upper side MOSFET reaches the second overcurrent threshold, the SS pin is pulled to ground and a dummy soft-start cycle is initiated. At dummy SS cycle, the current to charge soft-start cap is cut down to 1/5 of its normal value. So a dummy SS cycle takes 5x of the regular SS cycle. During the dummy SS period, the control loop is disabled and no PWM output. At the end of this cycle, it will start the normal SS. The hiccup mode persist until the second overcurrent threshold is no longer reached.

The ISL85402 is capable of starting up with prebiased output.

#### **PWM Control**

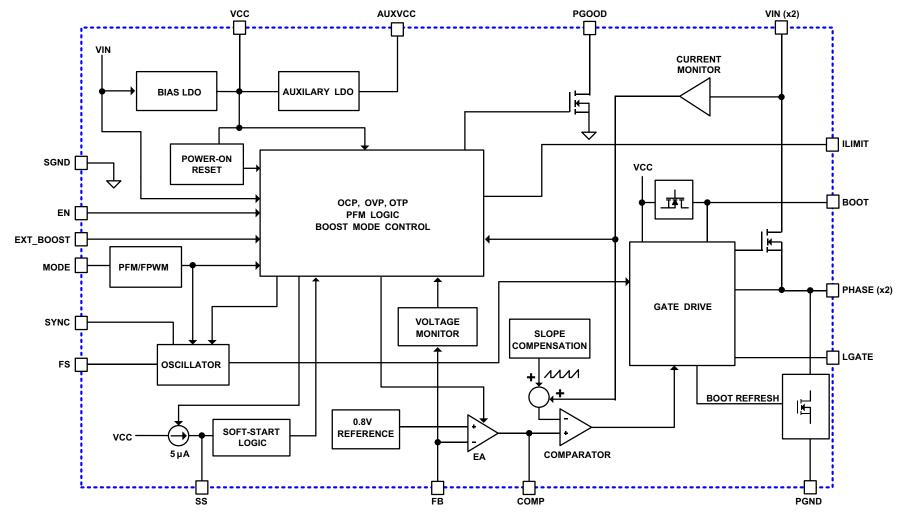

Pulling the MODE pin to GND will set the IC in forced PWM mode. The ISL85402 employs the peak current mode PWM control for fast transient response and cycle-by-cycle current limiting. See "Block Diagram" on page 4.

The PWM operation is initialized by the clock from the oscillator. The upper MOSFET is turned on by the clock at the beginning of a PWM cycle and the current in the MOSFET starts to ramp up. When the sum of the current sense signal and the slope compensation signal reaches the error amplifier output voltage level, the PWM comparator is trigger to shut down the PWM logic to turn off the high-side MOSFET. The high-side MOSFET stays off until the next clock signal comes for next cycle.

The output voltage is sensed by a resistor divider from  $V_{OUT}$  to the FB pin. The difference between the FB voltage and 0.8V reference is amplified and compensated to generate the error voltage signal at the COMP pin. Then the COMP pin signal is compared with the current ramp signal to shut down the PWM.

#### **PFM Mode Operation**

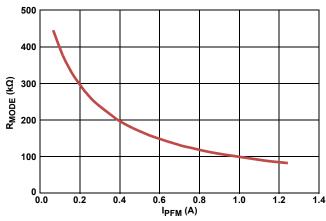

To pull the MODE pin HIGH (>2.5V) or leave the MODE pin floating will set the IC to have PFM (Pulse Frequency Modulation) operation in light load. In PFM mode, the switching frequency is dramatically reduced to minimize the switching loss. The ISL85402 enters PFM mode when the MOSFET peak current is lower than the PWM/PFM boundary current threshold. The

default threshold is 700mA when there is no programming resistor at the MODE pin.

The current threshold for PWM/PFM boundary can be programmed by choosing the MODE pin resistor value calculated from Equation 2, where IPFM is the desired PWM/PFM boundary current threshold and  $R_{\mbox{\scriptsize MODE}}$  is the programming resistor.

$$R_{MODE} = \frac{118500}{IPFM + 0.2}$$

(EQ. 2)

FIGURE 25.  $R_{MODE}$  vs  $I_{PFM}$

## **Synchronous and Non-Synchronous Buck**

The ISL85402 supports both Synchronous and non-synchronous buck operations. For a non-synchronous buck operation when a power diode is used as the low-side power device, the LGATE driver can be disabled with LGATE connected to VCC (before IC start-up).

## **AUXVCC Switch-Over**

The ISL85402 has an auxiliary LDO integrated as shown in the "Block Diagram" on page 4. It is used to replace the internal MAIN LDO function after the IC startup. "Typical Application Schematic II - VCC Switch-Over to  $V_{OUT}$ " on page 5 shows its basic application setup with output voltage connected to AUXVCC. After IC soft-start is done and the output voltage is built up to steady state, and once the AUXVCC pin voltage is over the AUX LDO Switch-over Rising Threshold, the MAIN LDO is shut off and the AUXILIARY LDO is activated to bias VCC. Since the AUXVCC pin voltage is lower than the input voltage  $V_{\rm IN}$ , the internal LDO dropout voltage and the consequent power loss is reduced. This feature brings substantial efficiency improvements in light load range, especially at high input voltage applications.

When the voltage at AUXVCC falls below the AUX LDO Switch-over Falling Threshold, the AUXILIARY LDO is shut off and the MAIN LDO is re-activated to bias VCC. At the OV/UV fault events, the IC also switches back over from AUXILIARY LDO to MAIN LDO.

The AUXVCC switchover function is offered in buck configuration. It is not offered in boost configuration when the AUXVCC pin is used to monitor the boost output voltage for OVP.

#### Input Voltage

With the part switching, the operating ISL85402 input voltage must be under 36V. This recommendation allows for short voltage ringing spikes (within a couple of ns time range) due to

part switching while not exceeding the 44V, as stated in the Absolute Maximum Ratings.

The lowest IC operating input voltage (VIN pin) depends on VCC voltage and the Rising and Falling V<sub>CC</sub> POR Threshold in Electrical Specifications table on page 7. At IC startup when VCC is just over rising POR threshold, there is no switching before the soft-start starts. Therefore, the IC minimum startup voltage on the VIN pin is 3.05V (MAX of Rising  $V_{CC}$  POR). When the soft-start is initiated, the regulator is switching and the dropout voltage across the internal LDO increases due to driving current. Thus, the IC VIN pin shutdown voltage is related to driving current and VCC POR falling threshold. The internal upper side MOSFET has typical 10nC gate drive. For a typical example of synchronous buck with 4nC lower MOSFET gate drive and 500kHz switching frequency, the driving current is 7mA total causing 70mV drop across internal LDO under 3V VIN. Then the IC shut down voltage on the VIN pin is 2.87V (2.8V+0.07V). In practical design, extra room should be taken into account with concern to voltage spikes at VIN.

With boost buck configuration, the input voltage range can be expanded further down to 2.5V or lower depending on the boost stage voltage drop upon maximum duty cycle. Since the boost output voltage is connected to the VIN pin as the buck inputs, after the IC starts up, the IC will keep operating and switching as long as the boost output voltage can keep the VCC voltage higher than falling threshold. Refer to "Boost Converter Operation" on page 14 for more details.

# **Output Voltage**

The ISL85402 output voltage can be programmed down to 0.8V by a resistor divider from  $V_{OUT}$  to FB. The maximum achievable voltage is  $(V_{IN}*D_{MAX}-V_{DROP})$ , where  $V_{DROP}$  is the voltage drop in the power path including mainly the MOSFET  $r_{DS(ON)}$  and inductor DCR. The maximum duty cycle  $D_{MAX}$  is decided by  $(1-Fs*t_{MIN(OFF)})$ .

## **Output Current**

With the high-side MOSFET integrated, the maximum output current, which the ISL85402 can support is decided by the package and many operating conditions. Thus, including input voltage, output voltage, duty cycle, switching frequency and temperature, etc. Note the following points.

- The maximum output current is limited by the maximum OC threshold that is 4.18A (TYP).

- From the thermal perspective, the die temperature shouldn't exceed +125°C with the power loss dissipated inside of the IC.

Figures 10 and 11 show the thermal performance of this part operating at different conditions.

Figures 10 and 11 show 2A and 2.5A applications under +25°C still air conditions over  $V_{\mbox{\scriptsize IN}}$  range. The temperature rise data in these figures can be used to estimate the die temperature at different ambient temperatures under various operating conditions. Note that more temperature rise is expected at higher ambient temperature due to more conduction loss caused by  $r_{\mbox{\scriptsize DS(ON)}}$  increase.

Generally, the part can output 2.5A in typical application conditions (V  $_{IN}$  8~30V, V  $_{O}$  5V, 500kHz, still air and +105  $^{\circ}$  C

ambient conditions). For any other operating conditions, refer to the previous mentioned thermal curves to estimate the maximum output current. The output current should be derated under any conditions causing the die temperature to exceed +125°C.

Basically, the die temperature is equal to the sum of ambient temperature and the temperature rise resulting from the power dissipated by the IC package with a certain junction to ambient thermal impedance  $\theta_{JA}$ . The power dissipated in the IC is related to the MOSFET switching loss, conduction loss and the internal LDO loss. Besides the load, these losses are also related to input voltage, output voltage, duty cycle, switching frequency and temperature. With the exposed pad at the bottom, the heat of the IC mainly goes through the bottom pad and  $\theta_{JA}$  is greatly reduced. The  $\theta_{IA}$  is highly related to layout and air flow conditions. In layout, multiple vias (≥9) are strongly recommended in the IC bottom pad. The bottom pad with its vias should be placed in the ground copper plane with an area as large as possible across multiple layers. The  $\theta_{\text{JA}}$  can be reduced further with air flow. Refer to Figures 8 and 9 for the thermal performance with 100 CFM air flow.

#### **Boost Converter Operation**

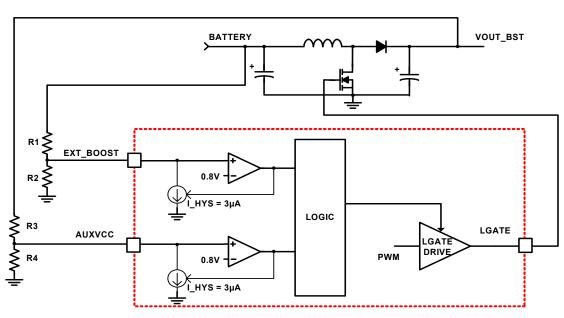

"Typical Application Schematic III - Boost Buck Converter" on page 5, shows the circuits where the boost works as a pre-stage to provide input to the following Buck stage. This is for applications when the input voltage could drop to a very low voltage in some constants (in some battery powered systems as for example), causing the output voltage to drop out of regulation. The boost converter can be enabled to boost the input voltage up to keep the output voltage in regulation. When system input voltage recovers back to normal, the boost stage is disabled while only the buck stage is switching.

The EXT\_BOOST pin is used to set boost mode and monitor the boost input voltage. At IC start-up before soft-start, the controller will be latched in boost mode when the voltage is at or above 200mV; it will latch in synchronous buck mode if voltage on this pin is below 200mV. In boost mode the low-side driver output PWM has the same PWM signal with the buck regulator.

In boost mode, the EXT\_BOOST pin is used to monitor boost input voltage to turn on and turn off the boost PWM. The AUXVCC pin is used to monitor the boost output voltage to turn on and turn off the boost PWM.

Referring to Figure 26 on page 15, a resistor divider from boost input voltage to the EXT\_BOOST pin is used to detect the boost input voltage. When the voltage on EXT\_BOOST pin is below 0.8V, the boost PWM is enabled with a fixed 500 $\mu$ s soft-start and the boost duty cycle increases linearly from  $t_{MIN(ON)}$ \*Fs to  $\sim\!50\%$ . A 3 $\mu$ A sinking current is enabled at the EXT\_BOOST pin for hysteresis purposes. When the voltage on the EXT\_BOOST pin recovers to be above 0.8V, the boost PWM is disabled immediately. Use Equation 3 to calculate the upper resistor  $R_{UP}$  (R1 in Figure 26) for a desired hysteresis  $V_{HYS}$  at boost input voltage.

$$R_{UP}[M\Omega] = \frac{VHYS}{3[\mu A]}$$

(EQ. 3)

Use Equation 4 to calculate the lower resistor  $R_{LOW}$  (R2 in Figure 26) according to a desired boost enable threshold.

$$R_{LOW} = \frac{R_{UP} \cdot 0.8}{VFTH - 0.8}$$

(EQ. 4)

Where VFTH is the desired falling threshold on boost input voltage to turn on the boost,  $3\mu A$  is the hysteresis current, and 0.8V is the reference voltage to be compared with.

Note the boost start-up threshold has to be selected in a way that the buck is operating working well and kept in close loop regulation before boost start-up. Otherwise, large in-rush current at boost start-up could occur at boost input due to the buck open loop saturation.

Similarly, a resistor divider from the boost output voltage to the AUXVCC pin is used to detect the boost output voltage. When the voltage on the AUXVCC pin is below 0.8V, the boost PWM is enabled with a fixed 500µs soft-start, and a 3µA sinking current is enabled at AUXVCC pin for hysteresis purposes. When the voltage on the AUXVCC pin recovers to be above 0.8V, the boost PWM is disabled immediately. Use Equation 3 to calculate the upper resistor  $R_{UP} \ (R_3 \ in \ Figure \ 26)$  according to a desired hysteresis  $V_{HY}$  at boost output voltage. Use Equation 4 to calculate the lower resistor  $R_{LOW} \ (R_4 \ in \ Figure \ 26)$  according to a desired boost enable threshold at boost output.

Assuming  $V_{BAT}$  is the boost input voltage,  $V_{OUTBST}$  is the boost output voltage and  $V_{OUT}$  is the buck output voltage, the steady state transfer function are:

$$V_{OUTBST} = \frac{1}{1-D} \cdot V_{BAT}$$

(EQ. 5)

$$V_{OUT} = D \cdot V_{OUTBST} = \frac{D}{1 - D} \cdot V_{BAT}$$

(EQ. 6)

From Equations 5 and 6, Equation 7 can be derived to estimate the steady state boost output voltage as function of  $V_{BAT}$  and  $V_{OUT}$ :

$$V_{OUTBST} = V_{BAT} + V_{OUT}$$

(EQ. 7)

After the IC starts up, the boost buck converters can keep working when the battery voltage drops extremely low because the IC's bias (VCC) LDO is powered by the boost output. For example, a 3.3V output application battery drops to 2V, and the VIN pin voltage is powered by the boost output voltage that is 5.2V (Equation 7), meaning that the VIN pin (buck input) still sees 5.2V to keep the IC working.

Note that in the previously mentioned case, the boost input current could be high because the input voltage is very low  $(V_{IN}*I_{IN}=V_{OUT}*I_{OUT}/Efficiency). \label{eq:continuous} If the design is to achieve the low input operation with full load, the inductor and MOSFET have to be selected with enough current ratings to handle the high current appearing at boost input. The boost inductor current are the same with the boost input current, which can be estimated as Equation 8, where <math display="inline">P_{OUT}$  is the output power,  $V_{BAT}$  is the boost input voltage, and EFF is the estimated efficiency of the whole boost and buck stages.

$$IL_{IN} = \frac{P_{OUT}}{V_{BAT} \cdot EFF}$$

(EQ. 8)

Based on the same concerns of the boost input current, the IC should be disabled before the boost input voltage rises above a certain level. PFM is not available in boost mode.

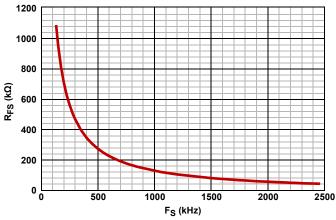

# **Oscillator and Synchronization**

The oscillator has a default frequency of 500kHz with the FS pin connected to VCC, or ground, or floating. The frequency can be programmed to any frequency between 200kHz and 2.2MHz with a resistor from FS pin to GND.

$$R_{FS}[k\Omega] = \frac{145000 - 16 \cdot FS[kHz]}{FS[kHz]}$$

(EQ. 9)

FIGURE 26. BOOST CONVERTER CONTROL

FIGURE 27. RFS vs FREQUENCY

The SYNC pin is bi-directional and it outputs the IC's default or programmed local clock signal when it's free running. The IC locks to an external clock injected to the SYNC pin (external clock frequency recommended to be 10% higher than the free running frequency). The delay from the rising edge of the external clock signal to the PHASE rising edge is half of the free running switching period pulse 220ns, (0.5Tsw+220ns). The maximum external clock frequency is recommended to be 1.6 of the free running frequency.

When the part enters PFM pulse skipping mode, the synchronization function is shut off and also no clock signal output in SYNC pin.

With the SYNC pins simply connected together, multiple ISL85402s can be synchronized. The slave ICs automatically have 180° phase shift with respective to the master IC.

# **Fault Protection**

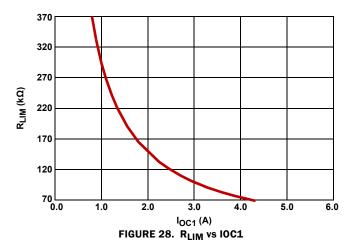

#### **Overcurrent Protection**

The overcurrent function protects against any overload condition and output short at worst case, by monitoring the current flowing through the upper MOSFET.

There are 2 current limiting thresholds. The first one  $I_{OC1}$  is to limit the high-side MOSFET peak current cycle-by-cycle. The current limit threshold is set to default at 3.6A with ILIMIT pin connected to GND or VCC, or left open. The current limit threshold can also be programmed by a resistor  $R_{LIM}$  at ILIMIT pin to ground. Use Equation 10 to calculate the resistor.

$$R_{LIM} = \frac{300000}{I_{OC}[A] + 0.018}$$

(EQ. 10)

Note that IOC1 is higher with lower R<sub>LIM</sub>. Considering the OC programming circuit tolerances over the temperature range -  $40\,^{\circ}$ C to  $105\,^{\circ}$ C, 71.5k is the lowest resistor value recommended to be used for R<sub>LIM</sub> to achieve the highest OC threshold. With 71.5k R<sub>LIM</sub>, the OC limit is 4.18A (TYP). A resistor lower than 71.5k would result in a default 3.6A OC1 threshold.

The second current protection threshold  $I_{0C2}$  is 15% higher than  $I_{0C1}$  mentioned previously. Instantly after the high-side MOSFET current reaches  $I_{0C2}$ , the PWM is shut off after 2-cycle delay and the IC enters hiccup mode. In hiccup mode, the PWM is disabled for

dummy soft-start duration equaling to 5 regular soft-start periods. After this dummy soft-start cycle, the true soft-start cycle is attempted again. The  $I_{\rm OC2}$  offers a robust and reliable protections against the worst case conditions.

The frequency foldback is implemented for the ISL85402. When overcurrent limiting, the switching frequency is reduced to be proportional to output voltage in order to keep the inductor current under limit threshold during overload condition. The low limit of frequency under frequency foldback operation is 40kHz.

## **Overvoltage Protection**

If the voltage detected on the FB pin is over 110% of reference, the high-side and low-side driver shuts down immediately and won't be allowed on until FB voltage drops to 0.8V. When the FB voltage drops to 0.8V, the drivers are released to ON. If the 120% overvoltage threshold is reached, the high-side and low-side driver shuts down immediately and the IC is latched off. The IC has to be reset for restart.

#### **Thermal Protection**

The ISL85402 PWM will be disabled if the junction temperature reaches +155 °C. A +15 °C hysteresis insures that the device will not restart until the junction temperature drops below +140 °C.

# **Component Selections**

The ISL85402 iSim model, which is available on the internet can be used to simulate the behaviors to, which will assist with the design.

#### **Output Capacitors**

An output capacitor is required to filter the inductor current. Output ripple voltage and transient response are 2 critical factors when considering output capacitance choice. The current mode control loop allows for the usage of low ESR ceramic capacitors and thus smaller board layout. Electrolytic and polymer capacitors may also be used.

Additional consideration applies to ceramic capacitors. While they offer excellent overall performance and reliability, the actual in-circuit capacitance must be considered. Ceramic capacitors are rated using large peak-to-peak voltage swings with no DC bias. In the DC/DC converter application, these conditions do not

reflect reality. As a result, the actual capacitance may be considerably lower than the advertised value. Consult the manufacturers data sheet to determine the actual in-application capacitance. Most manufacturers publish capacitance vs DC bias so that this effect can be easily accommodated. The effects of AC voltage are not frequently published, but an assumption of ~20% further reduction will generally suffice. The result of these considerations can easily result in an effective capacitance 50% lower than the rated value. Nonetheless, they are a very good choice in many applications due to their reliability and extremely low ESR.

The following equations allow calculation of the required capacitance to meet a desired ripple voltage level. Additional capacitance may be used.

For the ceramic capacitors (low ESR):

$$V_{OUTripple} = \frac{\Delta I}{8*F_{SW}*C_{OUT}}$$

(EQ. 11)

where  $\Delta I$  is the inductor's peak to peak ripple current,  $F_{SW}$  is the switching frequency and  $C_{OUT}$  is the output capacitor.

If using electrolytic capacitors then:

$$V_{OUTripple} = \Delta I * ESR$$

(EQ. 12)

Regarding transient response needs, a good starting point is to determine the allowable overshoot in  $V_{OUT}$  if the load is suddenly removed. In this case, energy stored in the inductor will be transferred to  $C_{OUT}$  causing its voltage to rise. After calculating capacitance required for both ripple and transient needs, choose the larger of the calculated values. The following equation determines the required output capacitor value in order to achieve a desired overshoot relative to the regulated voltage.

$$c_{OUT} = \frac{I_{OUT}^{2} * L}{V_{OUT}^{2} * (V_{OUTMAX} / V_{OUT})^{2} - 1)}$$

(EQ. 13)

where V<sub>OUTMAX</sub>/V<sub>OUT</sub> is the relative maximum overshoot allowed during the removal of the load.

## **Input Capacitors**

Depending on the system input power rail conditions, the aluminum electrolytic type capacitor is normally needed to provide the stable input voltage. Thus, restrict the switching frequency pulse current in a small area over the input traces for better EMC performance. The input capacitor should be able to handle the RMS current from the switching power devices.

Ceramic capacitors must be used at VIN pin of the IC and multiple capacitors including 1µF and 0.1µF are recommended. Place these capacitors as closely as possible to the IC.

#### **Buck Output Inductor**

The inductor value determines the converter's ripple current. Choosing an inductor current requires a somewhat arbitrary choice of ripple current,  $\Delta I$ . A reasonable starting point is 30% to 40% of total load current. The inductor value can then be calculated using Equation 14:

$$L = \frac{V_{IN} - V_{OUT}}{F_S \times \Delta I} \times \frac{V_{OUT}}{V_{IN}}$$

(EQ. 14)

Increasing the value of inductance reduces the ripple current and thus ripple voltage. However, the larger inductance value may reduce the converter's response time to a load transient. The inductor current rating should be such that it will not saturate in overcurrent conditions.

#### **Low-Side Power MOSFET**

In synchronous buck application, a power N MOSFET is needed as the synchronous low side MOSFET and a good one should have low Qgd, low  $r_{DS(ON)}$  and small Rg (Rg\_typ < 1.5 $\Omega$  recommended). Vgth\_min is recommended to be higher than 1.2V. A good example is SQS462EN.

## **Output Voltage Feedback Resistor Divider**

The output voltage can be programmed down to 0.8V by a resistor divider from  $V_{OUT}$  to FB according to Equation 15.

$$V_{OUT} = 0.8 \cdot \left(1 + \frac{R_{UP}}{R_{LOW}}\right)$$

(EQ. 15)

In an application requiring least input quiescent current, large resistors should be used for the divider. 232k is recommended for the upper resistor.

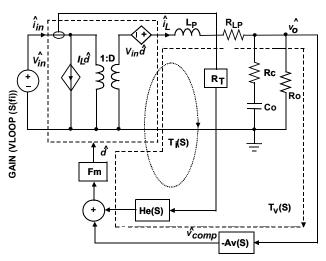

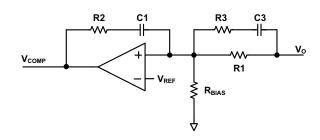

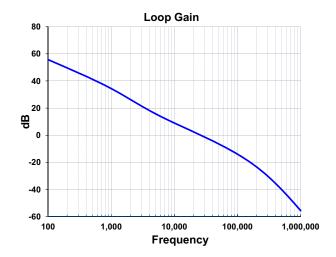

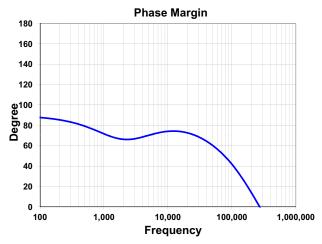

## **Loop Compensation Design**

The ISL85402 uses constant frequency peak current mode control architecture to achieve fast loop transient response. An accurate current sensing pilot device in parallel with the upper MOSFET is used for peak current control signal and overcurrent protection. The inductor is not considered as a state variable since its peak current is constant, and the system becomes single order system. It is much easier to design the compensator to stabilize the loop compared with voltage mode control. Peak current mode control has inherent input voltage feed-forward function to achieve good line regulation. Figure 29 shows the small signal model of a buck regulator.

FIGURE 29. SMALL SIGNAL MODEL OF BUCK REGULATOR

## **PWM Comparator Gain F<sub>m</sub>:**

The PWM comparator gain Fm for peak current mode control is given by Equation 16:

$$F_{m} = \frac{\hat{d}}{\hat{v}_{comp}} = \frac{1}{(S_{e} + S_{n})T_{s}}$$

(EQ. 16)

Where,  $S_e$  is the slew rate of the slope compensation and  $S_n$  is given by Equation 17:

$$S_n = R_t \frac{V_{in} - V_0}{L_p}$$

(EQ. 17)

where, Rt is the gain of the current amplifier.

## CURRENT SAMPLING TRANSFER FUNCTION $H_E(S)$ :

In current loop, the current signal is sampled every switching cycle. It has the following transfer function in Equation 18:

$$\mathbf{H_e(S)} = \frac{\mathbf{S^2}}{\omega_n^2} + \frac{\mathbf{S}}{\omega_n \mathbf{Q}_n} + \mathbf{1} \tag{EQ. 18}$$

where,  $\textbf{Q}_n$  and  $\boldsymbol{\omega}_n$  are given by  $\quad \textbf{Q}_n = -\frac{2}{\pi}, \, \boldsymbol{\omega}_n = \, \pi \textbf{f}_s$

## **Power Stage Transfer Functions**

Transfer function F<sub>1</sub>(S) from control to output voltage is:

$$F_{1}(S) = \frac{\hat{v}_{0}}{\hat{d}} = V_{in} \frac{1 + \frac{S}{\omega_{esr}}}{\frac{S^{2}}{\omega_{a}} + \frac{S}{\omega_{0}Q_{p}} + 1}$$

(EQ. 19)

Where,

$$\omega_{\text{esr}} = \frac{1}{R_{\text{c}}C_{\text{o}}}, Q_{\text{p}} \approx R_{\text{o}} \sqrt{\frac{C_{\text{o}}}{L_{\text{p}}}}$$

,  $\omega_{\text{o}} = \frac{1}{\sqrt{L_{\text{p}}C_{\text{o}}}}$

Transfer function  $F_2(S)$  from control to inductor current is given by Equation 20:

$$F_{2}(S) = \frac{\hat{I}_{0}}{\hat{d}} = \frac{V_{in}}{R_{0} + R_{LP}} \frac{1 + \frac{S}{\omega_{z}}}{\frac{S^{2}}{\omega_{0}Q_{p}} + 1}$$

(EQ. 20)

where  $\omega_z = \frac{1}{R_o C_o}$ .

Current loop gain T<sub>i</sub>(S) is expressed as Equation 21:

$$T_{i}(S) = R_{t}F_{m}F_{2}(S)H_{e}(S)$$

(EQ. 21)