## **PCA8802**

# Smartcard RTC; ultra low power oscillator with integrated counter for initiating one time password generation

Rev. 5 — 5 March 2013

**Product data sheet**

### 1. General description

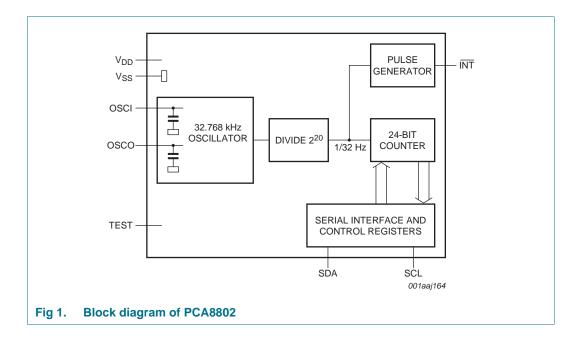

The PCA8802 is a CMOS integrated circuit for battery operation, typically supplied by button cells or flexible polymer batteries. Incorporated is a 32.768 kHz quartz crystal oscillator circuit including the two load capacitors. The circuit is optimized for a quartz with 6 pF load capacitance specification. Higher values can also be used with the addition of external load capacitors.

The main function of the oscillator is to generate a  $\frac{1}{32}$  Hz clock signal which is used to increment a 24 bit binary counter. The counter can be read over the serial interface and can also be set to any desired value. Control over the divider chain also allows for accurate starting of the counter. Incrementing of the counter value during read is prevented by freezing of the counter during access.

An interrupt signal is also available and is triggered coincident with the counter updating. This signal can be used as a wake-up for a microcontroller.

### 2. Features and benefits

- 32.768 kHz quartz oscillator, amplitude regulated with excellent frequency stability and high immunity to leakage currents

- Two integrated quartz crystal oscillator capacitors

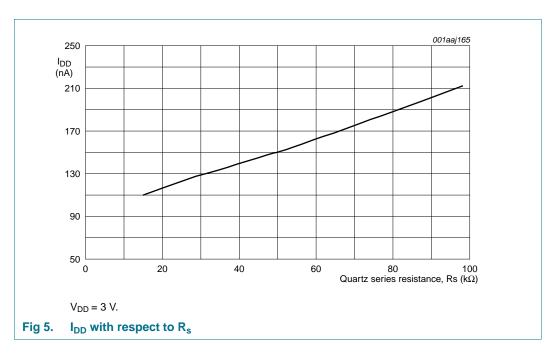

- Very low current consumption: typically 130 nA

- Two-wire serial interface (I<sup>2</sup>C-bus)

- Integrated 24-bit counter with auto increment every 32 seconds

- Interrupt output for processor wake-up

- Stop function for accurate time setting and current saving during shelf life

- User test modes for accelerated application testing and development

### 3. Applications

- One time password function generators

- Ultra low-power time keeper circuit

NXP Semiconductors PCA8802

Smartcard RTC

### 4. Ordering information

Table 1. Ordering information

| Type number | Package |                                        |           |  |

|-------------|---------|----------------------------------------|-----------|--|

|             | Name    | Description                            | Version   |  |

| PCA8802CX8  | WLCSP8  | wafer level chip-size package; 8 bumps | PCA8802CX |  |

| PCA8802U    | WLCSP8  | wafer level chip-size package; 8 bumps | PCA8802U  |  |

### 4.1 Ordering options

Table 2. Ordering options

| Product type number | Sales item (12NC) | Orderable part number | IC revision | Delivery form                          |

|---------------------|-------------------|-----------------------|-------------|----------------------------------------|

| PCA8802CX8/B/1      | 935288465027      | PCA8802CX8/B/1,027    | 1           | solder bumps; chips in tape and reel   |

| PCA8802U/12AA/1[1]  | 935297673005      | PCA8802U/12AA/1,00    | 1           | sawn wafer on Film Frame Carrier (FFC) |

| PCA8802U/2AA/1[1]   | 935288535026      | PCA8802U/2AA/1,026    | 1           | chips in tray                          |

| PCA8802UG/12KB/1[1] | 935299008005      | PCA8802UG/12KB/1,0    | 1           | sawn wafer on Film Frame Carrier (FFC) |

<sup>[1]</sup> Bump hardness see <u>Table 18</u>.

Table 3. PCA8802 wafer information

| Product type number | Wafer thickness | Wafer diameter | FFC for wafer size | Marking of bad die          |

|---------------------|-----------------|----------------|--------------------|-----------------------------|

| PCA8802U/12AA/1     | 200 μ <b>m</b>  | 6 inch         | 8 inch             | wafer mapping               |

| PCA8802UG/12KB/1    | 250 μ <b>m</b>  | 6 inch         | 8 inch             | inking and wafer<br>mapping |

For packing information, see Section 16 "Packing information" on page 28.

### 5. Marking

Table 4. Marking codes

| Product type number | Marking code |

|---------------------|--------------|

| PCA8802CX8/B/1      | PC8802-1     |

| PCA8802U/12AA/1     | PC8802-1     |

| PCA8802U/2AA/1      | PC8802-1     |

| PCA8802UG/12KB/1    | PC8802-1     |

| -                   |              |

### **Smartcard RTC**

### 6. Block diagram

**Smartcard RTC**

### 7. Pinning information

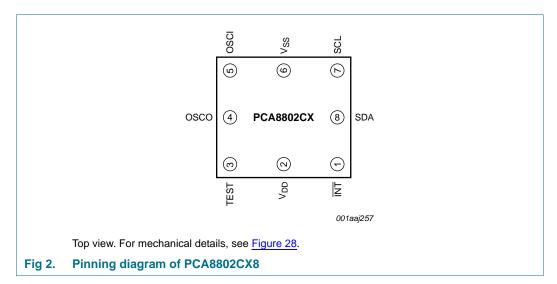

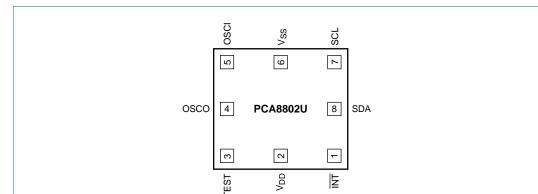

### 7.1 Pinning

001aaj151

Top view. For mechanical details, see Figure 29.

Fig 3. Pinning diagram of PCA8802U and PCA8802UG

### **Smartcard RTC**

### 7.2 Pin description

Table 5. Pin description for PCA8802

| Symbol          | Pin | Description                                          |

|-----------------|-----|------------------------------------------------------|

| INT             | 1   | interrupt and test mode output, push-pull            |

| $V_{DD}$        | 2   | supply voltage                                       |

| TEST            | 3   | test pin; must be connected to V <sub>SS</sub>       |

| OSCO            | 4   | oscillator output                                    |

| OSCI            | 5   | oscillator input                                     |

| V <sub>SS</sub> | 6   | ground                                               |

| SCL             | 7   | serial interface, clock                              |

| SDA             | 8   | serial interface, bidirectional data line; push-pull |

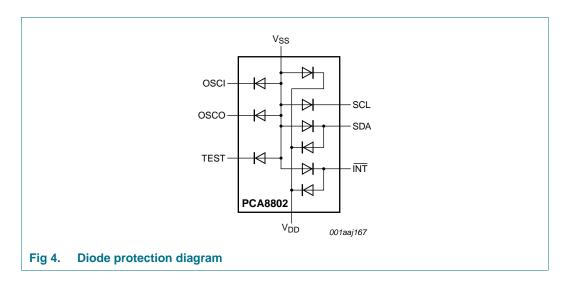

## 8. Device protection diagram

NXP Semiconductors PCA8802

Smartcard RTC

### 9. Functional description

The PCA8802 is an ultra low-power device for battery operations. The integrated oscillator circuit generates a  $\frac{1}{32}$  Hz clock signal to increment a 24-bit counter. The communication between the PCA8802 and other devices is made via point to point I<sup>2</sup>C-bus protocol.

The device is always running but for longer storage time it can be put in deep sleep and enabled again in case of delivery.

The functions of the device can be controlled with the following instruction set:

Table 6. Instruction set overview

| Instruction | Description                                   | Reference     |

|-------------|-----------------------------------------------|---------------|

| wrt_cmd     | device write access                           | Section 9.6.2 |

| dvs_cmd     | divider start or stop switch                  | Section 9.6.3 |

| pwd_cmd     | deep sleep mode switch                        | Section 9.6.4 |

| 32k_cmd     | 32.768 kHz clock signal on the pin INT switch | Section 9.6.5 |

| fst_cmd     | fast system development mode switch           | Section 9.6.6 |

| set_cmd     | set counter instruction                       | Section 9.6.7 |

| rd_cmd      | counter read instruction                      | Section 9.6.8 |

### 9.1 Oscillator

The 32.768 kHz oscillator includes two integrated load capacitors and an automatic gain control to ensure a reliable start-up.

For prototype development and system debugging, it is possible to output a 32.768 kHz square wave on the INT pin with the 32k\_cmd instruction.

### 9.1.1 Low-power operation

When the oscillator is running, a prime consideration for low power consumption is the series resistance  $R_s$  of the quartz used. The series resistance acts as a loss element. Low  $R_s$  reduces current consumption further.

**Smartcard RTC**

### 9.1.2 Deep sleep mode

With the deep sleep mode instruction (pwd\_cmd) the oscillator can be stopped and the device can be put into a deep sleep where power consumption is reduced to an absolute minimum. An example sequence can be found in <a href="Table 9">Table 9</a>. In deep sleep mode, the interface is still accessible.

### 9.2 Divider

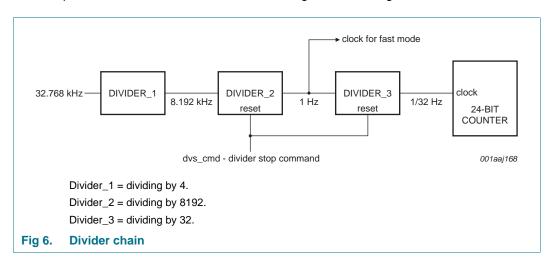

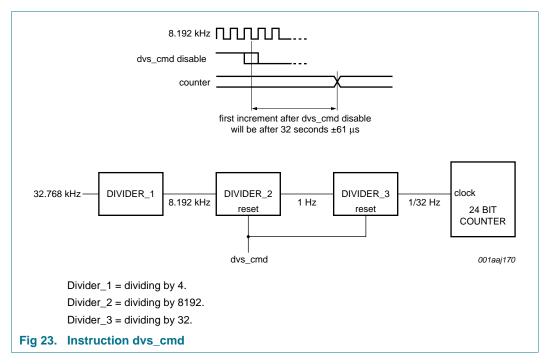

The divider chain is responsible for reducing the 32.768 kHz oscillator frequency down to  $1_{32}$  Hz.

The dividers (see Figure 6) divider\_2 and divider\_3 can be reset with the dvs\_cmd instruction. The 24-bit counter can be set when the dividers are held in reset, but this is not a requirement. This allows for accurate setting and restarting of the counter.

**Smartcard RTC**

The interface is asynchronous to the quartz oscillator and the state of divider\_1 cannot be known when the dvs\_cmd is enabled. The 8.192 kHz clock could have just occurred and hence a delay of  $\frac{1}{8192}$  seconds will occur before the next increment of the divider\_2, or the 8.192 kHz clock could be just about to occur and immediately increment the divider\_2.

As a consequence, an uncertainty of between zero and one 8192 Hz clock period (that is, a time uncertainty of about 0 s to 122  $\mu$ s) will be present when restarting the counter.

### 9.3 Binary counter

A 24-bit binary roll-over counter is implemented. The counter is reset at power-on.

The counter can be set to any value using the set\_cmd instruction. The set\_cmd instruction allows partial writing of data. Partial writing of the data parameters results in partial setting of the counter. For example, if data transfer is stopped after P1[23:16] (see Table 7) is transmitted, then only bit 23 to bit 16 will be updated. The counter will not increment while being set.

The counter can be halted by stopping the dividers using the dvs\_cmd instruction.

The counter can be read at any time and the counter value remains stable during reading. If the counter is due to increment during the read or write cycle, then the request to increment will be held off until after the read has concluded. For this reason, it is important to read the counter in bursts, ensuring that an interface STOP condition (see Section 9.5.4) is present between read accesses. Reading for periods of more than 32 seconds at a time results in loss of counts.

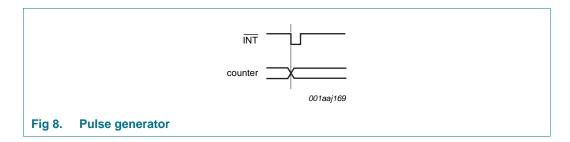

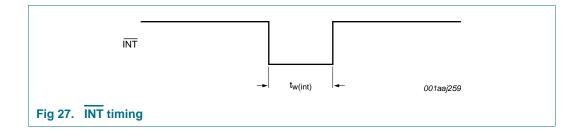

### 9.4 Pulse generator

An interrupt pulse is available at the  $\overline{\text{INT}}$  pin. This pulse is generated once every 32 seconds. It could be used to wake up a microcontroller to perform a periodic function, for example, to calculate and update an LCD display with a new one-time password.

A pulse is generated coincident with the increment of the counter. The new counter value is immediately available.

**Smartcard RTC**

### 9.5 I<sup>2</sup>C-bus interface

### 9.5.1 Interface protocol

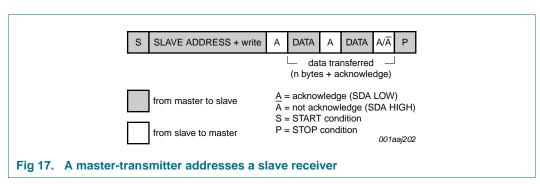

The serial interface is a point-to-point I<sup>2</sup>C-bus protocol. The I<sup>2</sup>C-bus protocol has the advantage of being robust in terms of immunity to electrical noise. Although the PCA8802 does not have the signal filters inside the interface pins, the slave address and acknowledge hand shaking is nevertheless implemented.

For power saving, the SDA output is a push-pull instead of the more traditional open-drain output. Push-pull prevents the need for power consuming pull-up resistors, but does limit the operation to point-to-point only.

The following slave addresses plus a write and read bit are reserved for the PCA8802:

write: 1010 0000read: 1010 0001

An incorrect slave address results in the device ignoring all bus data. A STOP or START condition (see Section 9.5.4) is required before a new transfer can be made.

### 9.5.1.1 The writing protocol

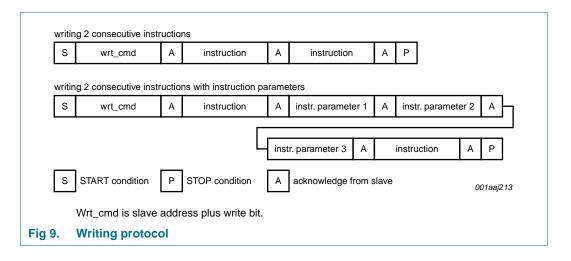

The writing protocol is shown in Figure 9.

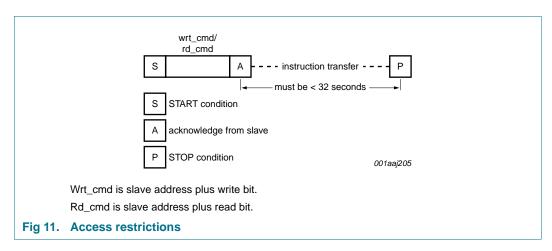

There is no restriction for the order of sending instructions. As many instructions as needed can be sent in one access. The total duration of one access must not exceed 32 seconds (see Figure 11).

**Smartcard RTC**

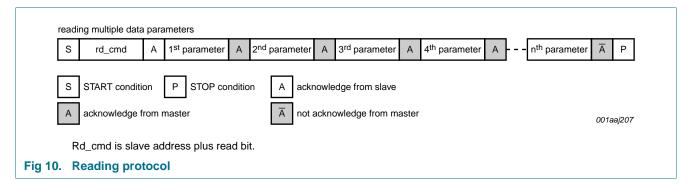

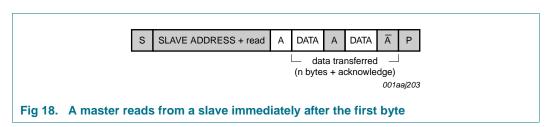

### 9.5.1.2 The reading protocol

The reading protocol is shown in Figure 10.

### 9.5.1.3 Reading and writing limitations

As the counter is frozen during interface accesses, all accesses must be completed within 32 seconds (see Figure 11). If this rule is not adhered to, then counts are dropped.

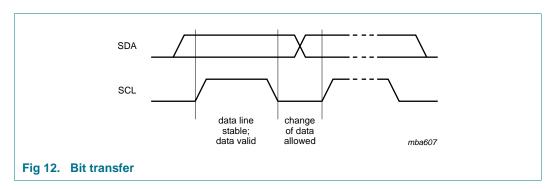

### 9.5.2 Bit transfer

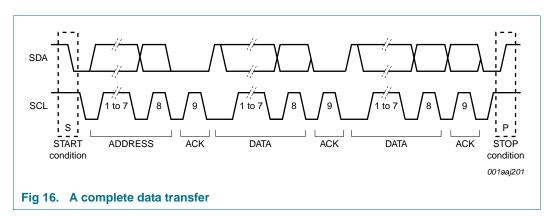

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time are interpreted as a control signal. Bit transfer is shown in Figure 12.

PCA8802

**Smartcard RTC**

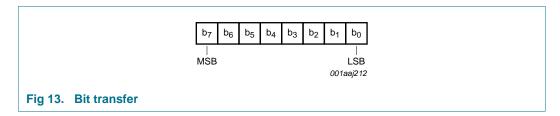

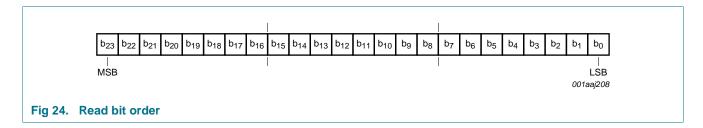

#### 9.5.3 Bit order

Data is transferred MSB first.

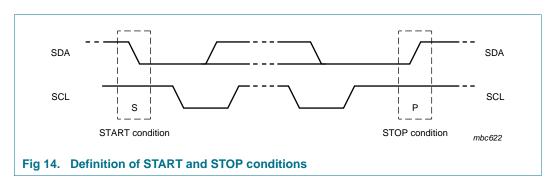

#### 9.5.4 START and STOP conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P). The START and STOP conditions are shown in Figure 14.

The data on SDA is sampled with the rising edge of SCL. Data is output to SDA on the falling edge of SCL.

### 9.5.5 System configuration

A device generating a message is a transmitter, a device receiving a message is the receiver. The device that controls the message is the master and the device which is controlled by the master is the slave.

### 9.5.6 Acknowledge

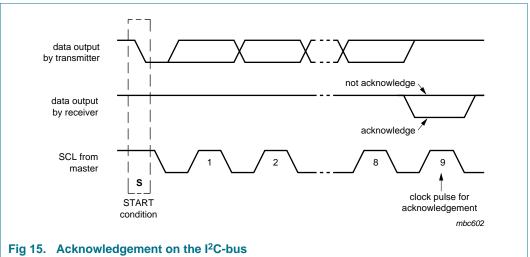

The number of data bytes transferred between the START and STOP conditions from transmitter to receiver is unlimited. But the duration of the access must not exceed 32 seconds. Each byte of 8 bits is followed by an acknowledge bit. The acknowledge bit is a HIGH level signal put on the bus by the transmitter during which time the master generates an extra acknowledge related clock pulse. A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master receiver must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges must pull-down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse (set-up and hold times must be considered). A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition. Acknowledgement is shown in Figure 15.

#### **Smartcard RTC**

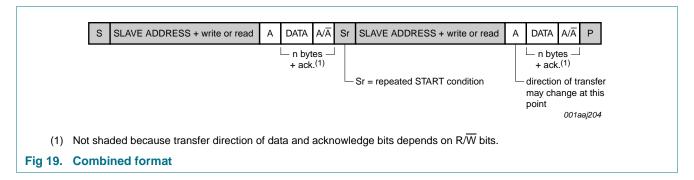

### 9.5.7 Data transfer

#### **Smartcard RTC**

### 9.5.7.1 Example data transfers

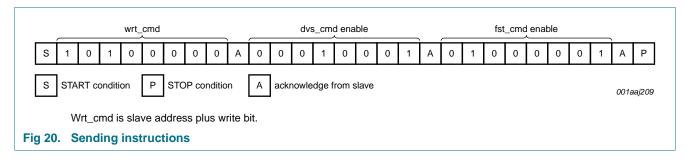

Example 1: Sending the instruction dvs\_cmd followed by fst\_cmd is shown in Figure 20.

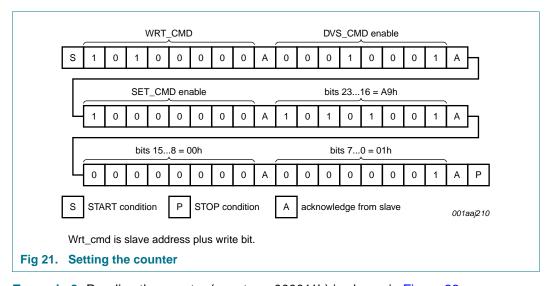

**Example 2:** Sending dvs\_cmd followed by setting the counter to A90001h is shown in Figure 21

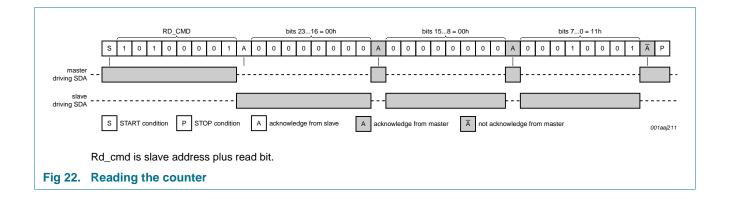

**Example 3:** Reading the counter (counter = 000011h) is shown in Figure 22.

### **Smartcard RTC**

NXP Semiconductors PCA8802

Smartcard RTC

### 9.6 Instructions

### 9.6.1 Instruction set

Table 7. Write instructions

The writing protocol is illustrated in Figure 9.

| First byte  |                  | Second byte |                  | Further bytes | Action                                                   |

|-------------|------------------|-------------|------------------|---------------|----------------------------------------------------------|

| Instruction | Instruction code | Instruction | Instruction code | Parameters    |                                                          |

| wrt_cmd     | 1010 0000        |             | '                | -             | device slave write address: slave address plus write bit |

|             |                  | dvs_cmd     | 0001 0001        | -             | stop and reset dividers                                  |

|             |                  |             | 0001 0000        | -             | start dividers                                           |

|             |                  | pwd_cmd     | 0010 0001        | -             | shut down the device                                     |

|             |                  |             | 0010 0000        | -             | enable the device                                        |

|             |                  | 32k_cmd     | 0011 0001        | -             | enable output of 32.768 kHz on pin INT                   |

|             |                  |             | 0011 0000        | -             | disable output of 32.768 kHz on pin INT                  |

|             |                  | fst_cmd     | 0100 0001        | -             | fast mode; increments counter every second               |

|             |                  |             | 0100 0000        | -             | fast mode disable                                        |

|             |                  | set_cmd     | 1000 0000        |               | set the counter value                                    |

|             |                  |             |                  | P1[23:16]     | parameter with counter values                            |

|             |                  |             |                  | P2[15:8]      |                                                          |

|             |                  |             |                  | P3[7:0]       |                                                          |

Table 8. Read instructions

The reading protocol is illustrated in Figure 10.

| First byte            |                  | Further bytes | Action                                                                                 |

|-----------------------|------------------|---------------|----------------------------------------------------------------------------------------|

| Instruction           | Instruction code | Parameters    |                                                                                        |

| rd_cmd <sup>[1]</sup> | 1010 0001        |               | device slave read address: slave address plus read bit                                 |

|                       |                  | P1[23:16]     | parameter with counter values;                                                         |

|                       |                  | P2[15:8]      | continues to read until no ACK is received;<br>counter is not updated during this time |

|                       |                  | P3[7:0]       | - counter is not apaated during this time                                              |

|                       |                  | P4[23:16]     |                                                                                        |

|                       |                  | :             |                                                                                        |

<sup>[1]</sup> Read of the counter is implicit with an interface read.

### 9.6.2 Instruction wrt\_cmd

The write instruction (wrt\_cmd) precedes each write sequence. Details of the writing protocol can be found in Section 9.5.1.1.

### 9.6.3 Instruction dvs\_cmd

The divider stop instruction (dvs\_cmd) can be used to freeze the divider chain and to put it in a defined state. The first 2 bits of the divider chain cannot be influenced. With this instruction, it is possible to control the time to the next increment of the counter. See Table 10.

PCA8802

**Smartcard RTC**

When the dividers are restarted, the first increment of the 24-bit counter will be after 32 seconds.

When the dividers are restarted, the 8192 Hz clock could have just occurred and hence a delay of  $\frac{1}{8192}$  seconds will occur before the next increment of the divider\_2. Or the 8192 Hz clock could be just about to occur and immediately increment the divider\_2. As a consequence, an uncertainty of one half clock period in the starting of the 24 bit counter is present when restarting (see Figure 23).

#### 9.6.4 Instruction pwd\_cmd

The power down instruction (pwd\_cmd) is intended to be used to put the system into a low-power mode for storage. Static leakage current will be the only power consumed. Storage at temperatures exceeding room temperature can increase leakage currents.

Entering deep sleep mode requires a specific sequence of events since under normal circumstances stopping the oscillator would result in a chip reset.

**Smartcard RTC**

Table 9. Deep sleep mode sequence

| Step  | Action                           | Code sequence   | Note                                                   |

|-------|----------------------------------|-----------------|--------------------------------------------------------|

| To en | ter deep sleep mode              |                 |                                                        |

| 1     | initiate transfer                | START condition | -                                                      |

| 2     | send wrt_cmd                     | 1010 0000       | -                                                      |

| 3     | enable dvs_cmd                   | 0001 0001       | stop the divider                                       |

| 4     | set counter with set_cmd         | 1000 0000       | set the counter = AAAAAAh                              |

|       |                                  | 1010 1010       | P1[23:16]                                              |

|       |                                  | 1010 1010       | P2[15:8]                                               |

|       |                                  | 1010 1010       | P3[7:0]                                                |

| 5     | enable pwd_cmd                   | 0010 0001       | stop the oscillator                                    |

| 6     | end transfer                     | STOP condition  | -                                                      |

| 7     | device is now in deep sleep mode | -               | -                                                      |

| То ех | it deep sleep mode               |                 |                                                        |

| 1     | initiate transfer                | START condition | -                                                      |

| 2     | send wrt_cmd                     | 1010 0000       | -                                                      |

| 3     | disable pwd_cmd                  | 0010 0000       | oscillator starts on the ACK cycle of this instruction |

| 4     | disable dvs_cmd                  | 0001 0000       | enable the divider again                               |

| 5     | end transfer                     | STOP condition  | -                                                      |

### 9.6.5 Instruction 32k\_cmd

The 32.768 kHz enable instruction (32k\_cmd) is intended to aid with oscillator characterization during system development. With this instruction, it is possible to obtain a 32.768 kHz clock on the INT pin which can be used for measurement.

This mode does not affect other operation of the chip except for the loss of interrupt output.

### 9.6.6 Instruction fst\_cmd

The fast mode instruction (fst\_cmd) is intended to enable faster system development. When enabled, the counter increments once every second instead of once every 32 seconds. Interrupt pulses are generated once every second as well.

When using fst\_cmd, data access to the device must be completed within 1 second, if not then counter increments are lost. The 1 second period is measured from the ACK cycle of a valid slave address to the next STOP or repeated START. A repeated START is sufficient to allow the counter to increment.

### 9.6.7 Instruction set\_cmd

The counter can be set to any value using the set instruction (set\_cmd). Partial writing of the data parameters results in partial setting of the counter. For example, if data transfer is stopped after P1[23:16] is transmitted, then only bit 23 to bit 16 will be updated.

This instruction takes only 3 parameters in one command. Data after the third parameter are interpreted as the next instruction.

**Smartcard RTC**

Accurate setting and start-up can be implemented using the dvs\_cmd instruction in cooperation with the set\_cmd instruction. An example is shown in Table 10.

Table 10. Example of accurate setting of the counter

| Step | Action                           | Code sequence   | Note                                                |

|------|----------------------------------|-----------------|-----------------------------------------------------|

| 1    | initiate transfer                | START condition | -                                                   |

| 2    | send wrt_cmd                     | 1010 0000       | -                                                   |

| 3    | enable dvs_cmd                   | 0001 0001       | -                                                   |

| 4    | set counter with set_cmd         | 1000 0000       | set the counter = 1                                 |

|      |                                  | 0000 0000       | P1[23:16]                                           |

|      |                                  | 0000 0000       | P2[15:8]                                            |

|      |                                  | 0000 0001       | P3[7:0]                                             |

| 5    | end transfer                     | STOP condition  | -                                                   |

| 6    | wait for an external time marker | -               | -                                                   |

| 7    | initiate transfer                | START condition | -                                                   |

| 8    | send wrt_cmd                     | 1010 0000       | -                                                   |

| 9    | disable dvs_cmd                  | 0001 0000       | counter starts on the ACK cycle of this instruction |

| 10   | end transfer                     | STOP condition  | -                                                   |

|      |                                  |                 |                                                     |

### 9.6.8 Instruction rd\_cmd

With the read instruction (rd\_cmd) the counter value can be read at any time. When the counter value is read, the counter is frozen so that there are no changes during the read back. After a read is terminated, the counter will be allowed to increment again. Any increment that was scheduled during the frozen period will then be effected.

Reading the counter is cyclic, that is, the device repeatedly returns the present counter value until the read is terminated. Reading the counter more than once can be useful in the case that the application is subject to a strong Electromagnetic Interference (EMI) environment, so that read-back values can be compared.

Read back must be terminated within 32 seconds else a count will be dropped.

#### **Smartcard RTC**

#### 9.7 Power-on reset

At initial power-on a reset is generated. The reset lasts not longer than 10 ms. During this time, the serial interface will not respond when accessed. The state of the device after power-on reset is shown in Table 11.

Table 11. Reset state

| Instruction name | State after reset |

|------------------|-------------------|

| dvs_cmd          | disabled          |

| pwd_cmd          | disabled          |

| 32k_cmd          | disabled          |

| fst_cmd          | disabled          |

| 24-bit counter   | 000000h           |

### 10. Application design-in information

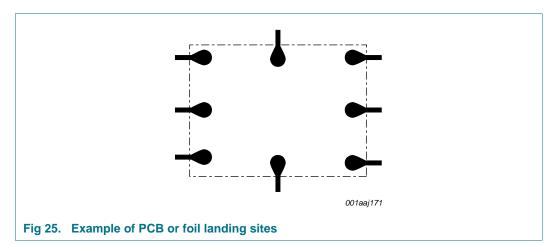

### 10.1 PCB or foil landing site

The layout of the landing sites is important. It is recommended to follow the following guidelines

- All landing sites should be the same size. When one site has a different size or shape, e.g. to indicate pad one, then the pull on the die produced by the surface tension of the solder will be different in one place. This variation can lead to the die not laying flat on the Printed-Circuit Board (PCB) or foil. This can also result in weak solder joints for some pins.

- It is recommended to use circular landing sites of the same diameter as the solder ball. This will help with self alignment. Solder bump dimensions can be found in Figure 28.

- 3. If no solder resist is used on the PCB or foil, then consideration should be given to the amount of run-off of the solder along the track connected to the landing site. Uneven run-off may result in similar problems as described in 1.

PCA8802

**Smartcard RTC**

### 11. Limiting values

Table 12. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                       | Conditions | Min            | Max   | Unit |

|------------------|---------------------------------|------------|----------------|-------|------|

| $V_{DD}$         | supply voltage                  |            | -0.5           | +6.5  | V    |

| $I_{DD}$         | supply current                  |            | -50            | +50   | mΑ   |

| $V_{I}$          | input voltage                   |            | -0.5           | +6.5  | V    |

| I                | input current                   |            | -10            | +10   | mΑ   |

| Vo               | output voltage                  |            | -0.5           | +6.5  | V    |

| Io               | output current                  |            | -10            | +10   | mA   |

| P <sub>tot</sub> | total power dissipation         |            | -              | 300   | mW   |

| V <sub>esd</sub> | electrostatic discharge voltage | HBM        | [1] -          | ±2500 | V    |

|                  |                                 | MM         | [2] _          | ±200  | V    |

| l <sub>lu</sub>  | latch-up current                |            | [3]            | 200   | mA   |

| T <sub>amb</sub> | ambient temperature             |            | -40            | +85   | °C   |

| T <sub>stg</sub> | storage temperature             |            | <u>[4]</u> –65 | +150  | °C   |

<sup>[1]</sup> Pass level; Human Body Model (HBM) according to JESD22-A114.

<sup>[2]</sup> Pass level; Machine Model (MM), according to JESD22-A115.

<sup>[3]</sup> Pass level; Latch-up testing, according to JESD78.

<sup>[4]</sup> According to the store and transport requirements (see Ref. 11 "UM10569") the devices have to be stored at a temperature of +8  $^{\circ}$ C to +45  $^{\circ}$ C and a humidity of 25  $^{\circ}$ 6 to 75  $^{\circ}$ 6.

**Smartcard RTC**

### 12. Static characteristics

Table 13. Static characteristics

$V_{DD}$  = 1.6 V to 5.5 V;  $V_{SS}$  = 0 V;  $f_{osc}$  = 32.768 kHz;  $T_{amb}$  = -40 °C to +85 °C; quartz crystal:  $R_s$  = 30 k $\Omega$ ,  $C_L$  = 6.0 pF; unless otherwise specified.

| Symbol               | Parameter                   | Conditions                                                                             |            | Min         | Тур  | Max                  | Unit |

|----------------------|-----------------------------|----------------------------------------------------------------------------------------|------------|-------------|------|----------------------|------|

| Supplies             |                             |                                                                                        |            |             |      |                      |      |

| $V_{DD}$             | supply voltage              |                                                                                        |            | 1.6         | -    | 5.5                  | V    |

|                      |                             | $T_{amb} = 25  ^{\circ}C;$<br>$f_{SCL} = 0  Hz$                                        |            | -           | 1.0  | -                    | V    |

| $\Delta V_{DD}$      | supply voltage variation    | $\Delta V/\Delta t = 1 V/\mu s$                                                        |            | -           | 0.25 | -                    | V    |

| I <sub>DD</sub>      | supply current              | deep sleep active                                                                      | <u>[1]</u> |             |      |                      |      |

|                      |                             | $T_{amb}$ = 25 °C;<br>$V_{DD}$ = 3 V;<br>$f_{SCL}$ = 0 Hz                              |            | -           | 3    | -                    | nA   |

|                      |                             | device running                                                                         |            |             |      |                      |      |

|                      |                             | f <sub>SCL</sub> = 0 Hz                                                                |            | -           | -    | 400                  | nA   |

|                      |                             | $T_{amb} = 25  ^{\circ}C;$<br>$V_{DD} = 3  V;$                                         |            | -           | 130  | -                    | nA   |

|                      |                             | $f_{SCL} = 0 Hz$                                                                       |            |             |      |                      |      |

|                      |                             | interface active                                                                       |            |             |      |                      |      |

|                      |                             | $f_{SCL} = 100 \text{ kHz}$                                                            |            | -           | 5    | 20                   | μΑ   |

|                      |                             | f <sub>SCL</sub> = 1 MHz                                                               |            | -           | 50   | 100                  | μΑ   |

| Oscillator           |                             |                                                                                        |            |             |      |                      |      |

| $V_{\text{start}}$   | start voltage               |                                                                                        |            | -           | 1.1  | -                    | V    |

| t <sub>startup</sub> | start-up time               |                                                                                        |            | -           | 0.2  | -                    | S    |

| C <sub>L(itg)</sub>  | integrated load capacitance |                                                                                        | [2]        | -           | 6.0  | -                    | pF   |

| Inputs               |                             |                                                                                        |            |             |      |                      |      |

| $V_{IL}$             | LOW-level input voltage     |                                                                                        |            | -           | -    | $0.3V_{DD}$          | V    |

| $V_{IH}$             | HIGH-level input voltage    |                                                                                        |            | $0.7V_{DD}$ | -    | -                    | V    |

| $V_{I}$              | input voltage               | on pins SCL, OSCI, TEST                                                                |            | -0.5        | -    | 5.5                  | V    |

|                      |                             | on pin SDA                                                                             |            | -0.5        | -    | $V_{DD} + 0.5$       | V    |

| I <sub>LI</sub>      | input leakage current       | $V_I = V_{DD}$ or $V_{SS}$ ; on pins SCL, SDA and TEST                                 |            | -200        | 0    | +200                 | nA   |

| Outputs              |                             |                                                                                        |            |             |      |                      |      |

| Vo                   | output voltage              |                                                                                        |            | -0.5        | -    | V <sub>DD</sub> +0.5 | V    |

| I <sub>OH</sub>      | HIGH-level output current   | $V_{OH} = 4.0 \text{ V};$<br>$V_{DD} = 5 \frac{\text{V};}{\text{ON pins INT}}$ and SDA |            | -           | 5    | 2                    | mA   |

|                      |                             | $V_{OH}$ = 1.28 V;<br>$V_{DD}$ = 1.6 V;<br>on pins $\overline{INT}$ and SDA            |            | -           | 0.5  | 0.2                  | mA   |

**Smartcard RTC**

Table 13. Static characteristics ... continued

$V_{DD}$  = 1.6 V to 5.5 V;  $V_{SS}$  = 0 V;  $f_{osc}$  = 32.768 kHz;  $T_{amb}$  = -40 °C to +85 °C; quartz crystal:  $R_s$  = 30 k $\Omega$ ,  $C_L$  = 6.0 pF; unless otherwise specified.

| Symbol          | Parameter                | Conditions                                                                                         | Min  | Тур       | Max  | Unit |

|-----------------|--------------------------|----------------------------------------------------------------------------------------------------|------|-----------|------|------|

| I <sub>OL</sub> | LOW-level output current | $V_{OL} = 1.0 \text{ V};$<br>$V_{DD} = 5 \text{ V};$<br>on pins $\overline{\text{INT}}$ and SDA    | -2   | <b>-7</b> | -    | mA   |

|                 |                          | $V_{OL} = 0.32 \text{ V};$<br>$V_{DD} = 1.6 \text{ V};$<br>on pins $\overline{\text{INT}}$ and SDA | -0.4 | <b>–1</b> | -    | mA   |

| I <sub>LO</sub> | output leakage current   | $V_O = V_{DD}$ or $V_{SS}$ ;<br>on pins SDA and $\overline{INT}$                                   | -200 | 0         | +200 | nA   |

[1] Unless otherwise defined,  $I_{DD}$  is measured with the reset state, see <u>Section 9.7</u>.

[2] Integrated load capacitance,  $C_{L(itg)}$ , is a calculation of  $C_{OSCI}$  and  $C_{OSCO}$  in series:  $C_{L(itg)} = \frac{(C_{OSCI} \cdot C_{OSCO})}{(C_{OSCI} + C_{OSCO})}$ .

**Smartcard RTC**

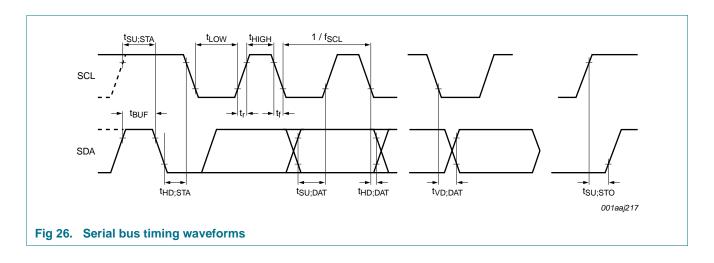

### 13. Dynamic characteristics

Table 14. Dynamic characteristics

$V_{DD}$  = 1.6 V to 5.5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 °C to +85 °C; unless otherwise specified. [1]

| Symbol              | Parameter                                        | Conditions |     | Min | Тур | Max | Unit |

|---------------------|--------------------------------------------------|------------|-----|-----|-----|-----|------|

| Timing cha          | aracteristics: serial bus                        |            |     |     |     |     |      |

| f <sub>SCL</sub>    | SCL clock frequency                              |            |     | -   | -   | 1   | MHz  |

| $t_{LOW}$           | LOW period of the SCL clock                      |            |     | 500 | -   | -   | ns   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                     |            |     | 260 | -   | -   | ns   |

| t <sub>BUF</sub>    | bus free time between a STOP and START condition |            |     | 500 | -   | -   | ns   |

| t <sub>HD;STA</sub> | hold time (repeated) START condition             |            |     | 260 | -   | -   | ns   |

| t <sub>SU;STA</sub> | set-up time for a repeated START condition       |            |     | 260 | -   | -   | ns   |

| t <sub>r</sub>      | rise time of both SDA and SCL signals            |            | [2] | -   | 10  | -   | ns   |

| t <sub>f</sub>      | fall time of both SDA and SCL signals            |            | [2] | -   | 10  | -   | ns   |

| t <sub>SU;DAT</sub> | data set-up time                                 |            |     | 50  | -   | -   | ns   |

| t <sub>HD;DAT</sub> | data hold time                                   |            |     | 0   | -   | -   | ns   |

| t <sub>SU;STO</sub> | set-up time for STOP condition                   |            |     | 260 | -   | -   | ns   |

| t <sub>VD;DAT</sub> | data valid time                                  |            |     | 75  | -   | 450 | ns   |

| C <sub>b</sub>      | capacitive load for each bus line                |            |     | -   | -   | 50  | pF   |

| Timing cha          | aracteristics: INT                               |            |     |     |     |     |      |

| t <sub>w(int)</sub> | interrupt pulse width                            |            |     | 20  | 40  | 80  | μS   |

<sup>[1]</sup> All timing values are valid within the operating supply voltage and ambient temperature range and are referenced to  $V_{IL}$  and  $V_{IH}$  with an input voltage swing of  $V_{SS}$  to  $V_{DD}$ .

<sup>[2]</sup> Rise and fall times are not limited. Fast edges can lead to system EMI problems, while slow edges are susceptible to noise.

### **Smartcard RTC**

**Smartcard RTC**

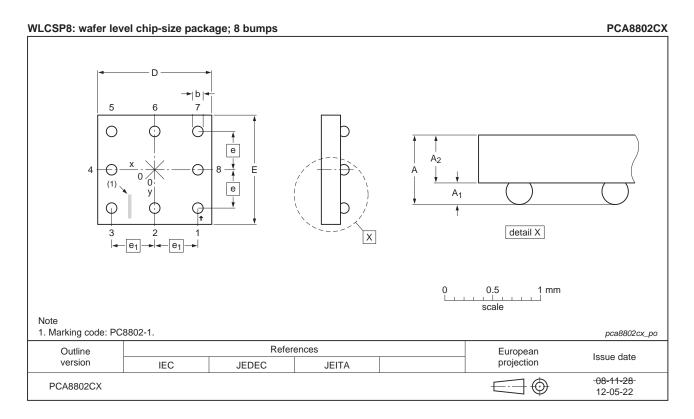

### 14. Bare die outline

Fig 28. Bare die outline PCA8802CX

Table 15. Dimensions of PCA8802CX

Original dimensions are in mm.

| Unit (mm) | Α    | $A_1$ | $A_2$ | b     | D    | E    | е   | <b>e</b> <sub>1</sub> | <b>e</b> <sub>D</sub> |

|-----------|------|-------|-------|-------|------|------|-----|-----------------------|-----------------------|

| max       | -    | 0.105 | -     | 0.136 | -    | -    | -   | -                     | -                     |

| nom       | 0.29 | 0.090 | 0.2   | 0.109 | 1.19 | 1.14 | 0.4 | 0.45                  | 0.96                  |

| min       | -    | 0.075 | -     | 0.082 | -    | -    | -   | -                     | -                     |

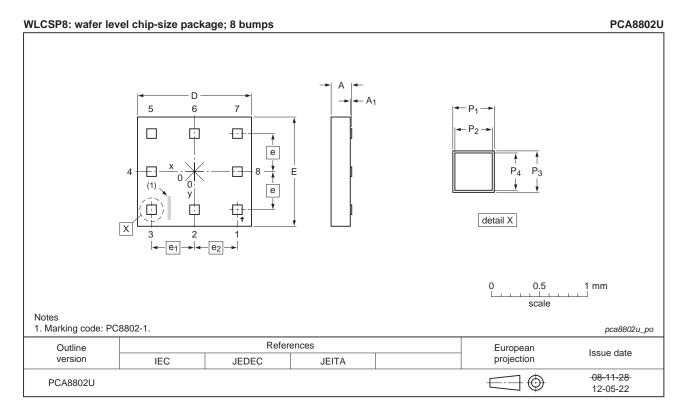

**Smartcard RTC**

Fig 29. Bare die outline PCA8802U

**Table 16. Dimensions of PCA8802U and PCA8802UG** *Original dimensions are in mm.*

| Unit (mm) | Α                                  | <b>A</b> <sub>1</sub> | D    | Е    | е     | <b>e</b> <sub>1</sub> | e <sub>2</sub> | P <sub>1</sub> [1] | P <sub>2</sub> [2] | P <sub>3</sub> [1] | P <sub>4</sub> [2] |

|-----------|------------------------------------|-----------------------|------|------|-------|-----------------------|----------------|--------------------|--------------------|--------------------|--------------------|

| PCA8802U/ | PCA8802U/2AA/1 and PCA8802U/12AA/1 |                       |      |      |       |                       |                |                    |                    |                    |                    |

| max       | -                                  | 0.018                 | -    | -    | -     | -                     | -              | -                  | 0.093              | -                  | 0.093              |

| nom       | 0.215                              | 0.015                 | 1.19 | 1.14 | 0.396 | 0.448                 | 0.449          | 0.099              | 0.090              | 0.099              | 0.090              |

| min       | -                                  | 0.012                 | -    | -    | -     | -                     | -              | -                  | 0.087              | -                  | 0.087              |

| PCA8802U  | G/12KB/                            | 1                     |      |      |       |                       |                |                    |                    |                    |                    |

| max       | -                                  | 0.018                 | -    | -    | -     | -                     | -              | -                  | 0.093              | -                  | 0.093              |

| nom       | 0.265                              | 0.015                 | 1.19 | 1.14 | 0.396 | 0.448                 | 0.449          | 0.099              | 0.090              | 0.099              | 0.090              |

| min       | -                                  | 0.012                 | -    | -    | -     | -                     | -              | -                  | 0.087              | -                  | 0.087              |

<sup>[1]</sup> Pad size.

<sup>[2]</sup> Bump size.

**Smartcard RTC**

Table 17. Bump and reference point locations of PCA8802U and PCA8802UG

| Symbol                    | Pad | Coordinates[1] |        |  |  |

|---------------------------|-----|----------------|--------|--|--|

|                           |     | x              | у      |  |  |

| INT                       | 1   | 437            | -396   |  |  |

| $V_{DD}$                  | 2   | -12            | -430   |  |  |

| TEST                      | 3   | -460           | -396   |  |  |

| OSCO                      | 4   | -460           | 1      |  |  |

| OSCI                      | 5   | -460           | 396    |  |  |

| V <sub>SS</sub> [2]       | 6   | -12            | 430    |  |  |

| SCL                       | 7   | 437            | 396    |  |  |

| SDA                       | 8   | 437            | 1      |  |  |

| pin 1 identifier          | -   | 474.7          | -472.0 |  |  |

| bottom left die corner[3] | -   | -594.8         | -568.2 |  |  |

| top right die corner[3]   | -   | 594.7          | 568.3  |  |  |

- [1] All coordinates are referenced, in  $\mu$ m, to the center of the die (see Figure 29).

- [2] The substrate (rear side of the die) is connected to V<sub>SS</sub> and should be electrically isolated.

- [3] Die size before dicing. Final dimensions will be 10  $\mu m$  to 20  $\mu m$  smaller.

Table 18. Gold bump hardness of PCA8802U and PCA8802UG

| Gold bump type | Min | Max | Unit <sup>[1]</sup> |

|----------------|-----|-----|---------------------|

| soft gold bump | 35  | 80  | HV                  |

<sup>[1]</sup> Pressure of diamond head: 10 g to 50 g.

### 15. Handling information

All input and output pins are protected against ElectroStatic Discharge (ESD) under normal handling. When handling Metal-Oxide Semiconductor (MOS) devices ensure that all normal precautions are taken as described in *JESD625-A*, *IEC 61340-5* or equivalent standards.

**Smartcard RTC**

### 16. Packing information

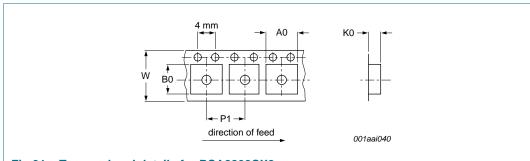

### 16.1 Tape and reel information for PCA8802CX8/B/1

Fig 31. Tape and reel details for PCA8802CX8

Table 19. Tape and reel dimensions [1]

| Dimension | Description   | Value  |

|-----------|---------------|--------|

| W         | tape width    | 8.0 mm |

| A0        | pocked length | 1.3 mm |

| B0        | pocket width  | 1.3 mm |

| K0        | pocket depth  | 0.5 mm |

| P1        | pocket pitch  | 4.0 mm |

[1] Die is placed in pocket bump side down.

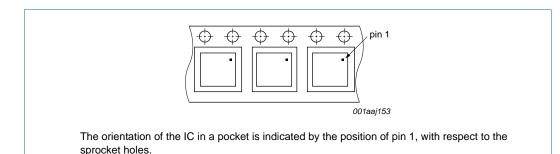

Fig 32. Pocket alignment for PCA8802CX8

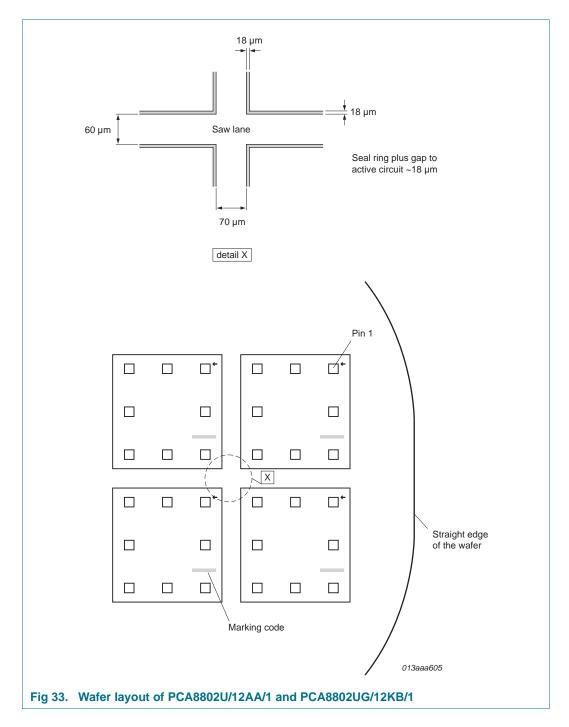

# 16.2 Wafer and Film Frame Carrier (FFC) information for PCA8802U/12AA/1 and PCA8802UG/12KB/1

**PCA8802 NXP Semiconductors**

### **Smartcard RTC**

**Smartcard RTC**

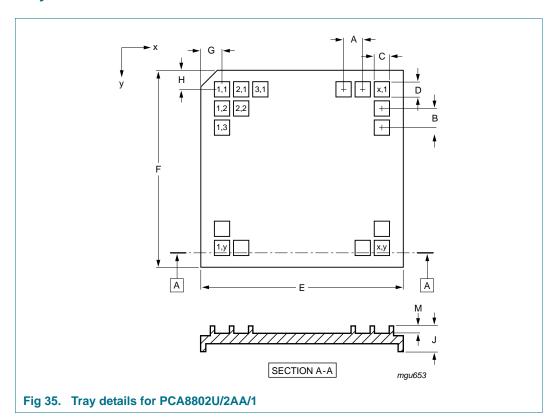

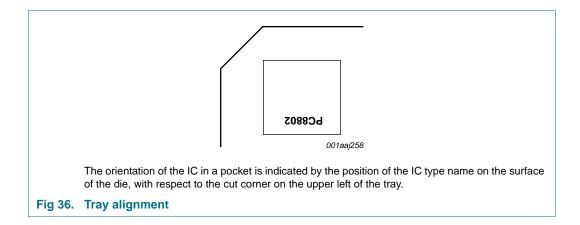

### 16.3 Tray information for PCA8802U/2AA/1

Table 20. Tray dimensions [1]

| Dimension | Description                                     | Value   |

|-----------|-------------------------------------------------|---------|

| Α         | pocket pitch; x direction                       | 3.1 mm  |

| В         | pocket pitch; y direction                       | 3.1 mm  |

| С         | pocket width; x direction                       | 1.29 mm |

| D         | pocket width; y direction                       | 1.24 mm |

| Е         | tray width; x direction                         | 50.8 mm |

| F         | tray width; y direction                         | 50.8 mm |

| G         | distance from cut corner to pocket (1,1) center | 5.25 mm |

| Н         | distance from cut corner to pocket (1,1) center | 5.25 mm |

| J         | tray thickness                                  | 3.96 mm |

| М         | pocket depth                                    | 0.5 mm  |

| x         | number of pockets in x direction                | 14      |

| у         | number of pockets in y direction                | 14      |

<sup>[1]</sup> Die is placed in pocket bump side up.

### **Smartcard RTC**

NXP Semiconductors PCA8802

Smartcard RTC

### 17. Soldering of WLCSP packages

### 17.1 Introduction to soldering WLCSP packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering WLCSP (Wafer Level Chip-Size Packages) can be found in application note AN10439 "Wafer Level Chip Scale Package" and in application note AN10365 "Surface mount reflow soldering description".

Wave soldering is not suitable for this package.

All NXP WLCSP packages are lead-free.

### 17.2 Board mounting

Board mounting of a WLCSP requires several steps:

- 1. Solder paste printing on the PCB

- 2. Component placement with a pick and place machine

- 3. The reflow soldering itself

### 17.3 Reflow soldering

Key characteristics in reflow soldering are:

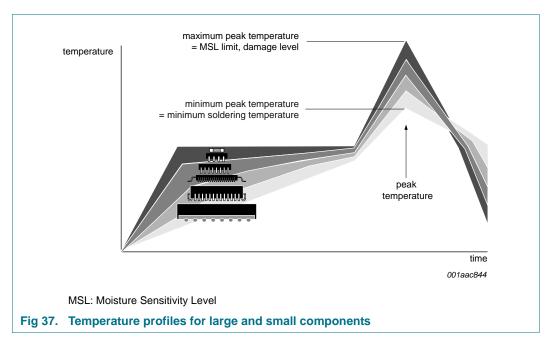

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 37</u>) than a PbSn process, thus reducing the process window

- Solder paste printing issues, such as smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature), and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic) while being low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 21.

Table 21. Lead-free process (from J-STD-020D)

| Package thickness (mm) | Package reflow to | nperature (°C) |        |  |  |  |  |

|------------------------|-------------------|----------------|--------|--|--|--|--|

|                        | Volume (mm³)      |                |        |  |  |  |  |

|                        | < 350             | 350 to 2000    | > 2000 |  |  |  |  |

| < 1.6                  | 260               | 260            | 260    |  |  |  |  |

| 1.6 to 2.5             | 260               | 250            | 245    |  |  |  |  |

| > 2.5                  | 250               | 245            | 245    |  |  |  |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 37.

**Smartcard RTC**

For further information on temperature profiles, refer to application note *AN10365* "Surface mount reflow soldering description".

#### 17.3.1 Stand off

The stand off between the substrate and the chip is determined by:

- The amount of printed solder on the substrate

- The size of the solder land on the substrate

- The bump height on the chip

The higher the stand off, the better the stresses are released due to TEC (Thermal Expansion Coefficient) differences between substrate and chip.

### 17.3.2 Quality of solder joint

A flip-chip joint is considered to be a good joint when the entire solder land has been wetted by the solder from the bump. The surface of the joint should be smooth and the shape symmetrical. The soldered joints on a chip should be uniform. Voids in the bumps after reflow can occur during the reflow process in bumps with high ratio of bump diameter to bump height, i.e. low bumps with large diameter. No failures have been found to be related to these voids. Solder joint inspection after reflow can be done with X-ray to monitor defects such as bridging, open circuits and voids.

#### 17.3.3 Rework

In general, rework is not recommended. By rework we mean the process of removing the chip from the substrate and replacing it with a new chip. If a chip is removed from the substrate, most solder balls of the chip will be damaged. In that case it is recommended not to re-use the chip again.

**Smartcard RTC**

Device removal can be done when the substrate is heated until it is certain that all solder joints are molten. The chip can then be carefully removed from the substrate without damaging the tracks and solder lands on the substrate. Removing the device must be done using plastic tweezers, because metal tweezers can damage the silicon. The surface of the substrate should be carefully cleaned and all solder and flux residues and/or underfill removed. When a new chip is placed on the substrate, use the flux process instead of solder on the solder lands. Apply flux on the bumps at the chip side as well as on the solder pads on the substrate. Place and align the new chip while viewing with a microscope. To reflow the solder, use the solder profile shown in application note *AN10365 "Surface mount reflow soldering description"*.

### 17.3.4 Cleaning

Cleaning can be done after reflow soldering.

### 18. Abbreviations

Table 22. Abbreviations

| Acronym | Description                             |

|---------|-----------------------------------------|

| CMOS    | Complementary Metal Oxide Semiconductor |

| EMI     | ElectroMagnetic Interference            |

| HBM     | Human Body Model                        |

| IC      | Integrated Circuit                      |

| LCD     | Liquid Crystal Display                  |

| LSB     | Least Significant Bit                   |

| MM      | Machine Model                           |

| MSB     | Most Significant Bit                    |

| PCB     | Printed-Circuit Board                   |

| RTC     | Real-Time Clock                         |

| WLCSP   | Wafer Level Chip-Size Package           |

### **Smartcard RTC**

### 19. References

- [1] AN10439 Wafer Level Chip Size Package

- [2] AN10706 Handling bare die

- [3] AN10853 ESD and EMC sensitivity of IC

- [4] IEC 60134 Rating systems for electronic tubes and valves and analogous semiconductor devices

- [5] IEC 61340-5 Protection of electronic devices from electrostatic phenomena

- [6] JESD22-A114 Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)

- [7] **JESD22-A115** Electrostatic Discharge (ESD) Sensitivity Testing Machine Model (MM)

- [8] JESD78 IC Latch-Up Test

- [9] JESD625-A Requirements for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices

- [10] UM10204 I<sup>2</sup>C-bus specification and user manual

- [11] UM10569 Store and transport requirements

36 of 42

NXP Semiconductors PCA8802

Smartcard RTC

### 20. Revision history

### Table 23. Revision history

| Document ID    | Release date                      | Data sheet status      | Change notice | Supersedes  |

|----------------|-----------------------------------|------------------------|---------------|-------------|

| PCA8802 v.5    | 20130305                          | Product data sheet     | -             | PCA8802 v.4 |

| Modifications: | <ul> <li>Adjusted prod</li> </ul> | duct types and related | d packing     |             |

| PCA8802 v.4    | 20120927                          | Product data sheet     | -             | PCA8802 v.3 |

| PCA8802 v.3    | 20120330                          | Product data sheet     | -             | PCA8802 v.2 |

| PCA8802 v.2    | 20120126                          | Product data sheet     | -             | PCA8802_1   |

| PCA8802_1      | 20090219                          | Product data sheet     | -             | -           |

NXP Semiconductors PCA8802

Smartcard RTC

### 21. Legal information

#### 21.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 21.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 21.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

PCA8802

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2013. All rights reserved.

#### **Smartcard RTC**

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Bare die — All die are tested on compliance with their related technical specifications as stated in this data sheet up to the point of wafer sawing and are handled in accordance with the NXP Semiconductors storage and transportation conditions. If there are data sheet limits not guaranteed, these will be separately indicated in the data sheet. There are no post-packing tests performed on individual die or wafers.

NXP Semiconductors has no control of third party procedures in the sawing, handling, packing or assembly of the die. Accordingly, NXP Semiconductors assumes no liability for device functionality or performance of the die or systems after third party sawing, handling, packing or assembly of the die. It is the responsibility of the customer to test and qualify their application in which the die is used.

All die sales are conditioned upon and subject to the customer entering into a written die sale agreement with NXP Semiconductors through its legal department.

#### 21.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

### 22. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

### **Smartcard RTC**

### 23. Tables

| Table 1.  | Ordering information                         | 2  |

|-----------|----------------------------------------------|----|

| Table 2.  | Ordering options                             |    |

| Table 3.  | PCA8802 wafer information                    |    |

| Table 4.  | Marking codes                                | 2  |

| Table 5.  | Pin description for PCA8802                  | 5  |

| Table 6.  | Instruction set overview                     | 6  |

| Table 7.  | Write instructions                           | 15 |

| Table 8.  | Read instructions                            | 15 |

| Table 9.  | Deep sleep mode sequence                     | 17 |

| Table 10. | Example of accurate setting of the counter . | 18 |

| Table 11. | Reset state                                  | 19 |

| Table 12. | Limiting values                              | 20 |

| Table 13. | Static characteristics                       | 21 |

|           | Dynamic characteristics                      |    |

| Table 15. | Dimensions of PCA8802CX                      | 25 |

| Table 16. | Dimensions of PCA8802U                       |    |

|           | and PCA8802UG                                | 26 |

| Table 17. | Bump and reference point locations           |    |

|           | of PCA8802U and PCA8802UG                    | 27 |

| Table 18. | Gold bump hardness of PCA8802U               |    |

|           | and PCA8802UG                                |    |

|           | Tape and reel dimensions [1]                 |    |

| Table 20. | Tray dimensions [1]                          | 31 |

|           | Lead-free process (from J-STD-020D)          |    |

| Table 22. | Abbreviations                                | 35 |

| Table 23. | Revision history                             | 37 |

### **Smartcard RTC**

## 24. Figures

| Fig 1.  | Block diagram of PCA8802                       |   |

|---------|------------------------------------------------|---|

| Fig 2.  | Pinning diagram of PCA8802CX8                  | 4 |

| Fig 3.  | Pinning diagram of PCA8802U                    |   |

|         | and PCA8802UG                                  | 4 |

| Fig 4.  | Diode protection diagram                       | 5 |

| Fig 5.  | I <sub>DD</sub> with respect to R <sub>s</sub> |   |

| Fig 6.  | Divider chain                                  |   |

| Fig 7.  | Counter behavior during read access            |   |

| Fig 8.  | Pulse generator                                |   |

| Fig 9.  | Writing protocol                               |   |

| Fig 10. | Reading protocol                               |   |

| Fig 11. | Access restrictions1                           |   |

| Fig 12. | Bit transfer                                   |   |

| Fig 13. | Bit transfer                                   |   |

| Fig 14. | Definition of START and STOP conditions 1      |   |

| Fig 15. | Acknowledgement on the I <sup>2</sup> C-bus    |   |

| Fig 16. | A complete data transfer                       | 2 |

| Fig 17. | A master-transmitter addresses                 |   |

|         | a slave receiver                               | 2 |

| Fig 18. | A master reads from a slave immediately        |   |

|         | after the first byte                           |   |

| Fig 19. | Combined format                                |   |

| Fig 20. | Sending instructions1                          |   |

| Fig 21. | Setting the counter1                           |   |

| Fig 22. | Reading the counter1                           |   |

| Fig 23. | Instruction dvs_cmd1                           |   |

| Fig 24. | Read bit order1                                |   |

| Fig 25. | Example of PCB or foil landing sites           |   |

| Fig 26. | Serial bus timing waveforms                    |   |

| Fig 27. | INT timing                                     |   |

| Fig 28. | Bare die outline PCA8802CX2                    |   |

| Fig 29. | Bare die outline PCA8802U2                     |   |

| Fig 30. | Pin 1 identifier                               |   |

| Fig 31. | Tape and reel details for PCA8802CX82          |   |

| Fig 32. | Pocket alignment for PCA8802CX82               | 8 |

| Fig 33. | Wafer layout of PCA8802U/12AA/1 and            | _ |

|         | PCA8802UG/12KB/1                               | 9 |

| Fig 34. | Film Frame Carrier (FFC) of PCA8802U/12AA/1    |   |

|         | and PCA8802UG/12KB/1                           |   |

| Fig 35. | Tray details for PCA8802U/2AA/1                |   |

| Fig 36. | Tray alignment                                 | 2 |

| Fig 37. | Temperature profiles for large and small       |   |

|         | components                                     | 4 |

### **Smartcard RTC**

### 25. Contents

| 1              | General description                                                                    | . 1 | 14     | Bare die outline                           | 25 |

|----------------|----------------------------------------------------------------------------------------|-----|--------|--------------------------------------------|----|

| 2              | Features and benefits                                                                  |     | 15     | Handling information                       | 27 |

| 3              | Applications                                                                           |     | 16     | Packing information                        |    |

| 4              | Ordering information                                                                   |     | 16.1   | Tape and reel information                  |    |

| <b>4</b> .1    | _                                                                                      |     | 10.1   | for PCA8802CX8/B/1                         | 28 |

|                | Ordering options                                                                       |     | 16.2   | Wafer and Film Frame Carrier (FFC)         | 20 |

| 5              | Marking                                                                                |     |        | information for PCA8802U/12AA/1 and        |    |

| 6              | Block diagram                                                                          |     |        |                                            | 29 |

| 7              | Pinning information                                                                    |     | 16.3   | Tray information for PCA8802U/2AA/1        | 31 |

| 7.1            | Pinning                                                                                |     | 17     | Soldering of WLCSP packages                | 33 |

| 7.2            | Pin description                                                                        | . 5 | 17.1   | Introduction to soldering WLCSP packages . |    |

| 8              | Device protection diagram                                                              | . 5 | 17.2   |                                            | 33 |

| 9              | Functional description                                                                 | . 6 | 17.3   | Reflow soldering                           | 33 |

| 9.1            | Oscillator                                                                             | . 6 | 17.3.1 | Stand off                                  |    |

| 9.1.1          | Low-power operation                                                                    |     | 17.3.2 | Quality of solder joint                    |    |

| 9.1.2          | Deep sleep mode                                                                        | . 7 | 17.3.3 | Rework                                     | 34 |

| 9.2            | Divider                                                                                | . 7 | 17.3.4 | Cleaning                                   | 35 |

| 9.3            | Binary counter                                                                         |     | 18     | Abbreviations                              | 35 |

| 9.4            | Pulse generator                                                                        |     | 19     | References                                 | 36 |

| 9.5            | I <sup>2</sup> C-bus interface                                                         |     | 20     | Revision history                           | 37 |

| 9.5.1          | Interface protocol                                                                     |     | 21     | Legal information                          |    |

| 9.5.1.1        | The writing protocol                                                                   |     | 21.1   | Data sheet status                          |    |

| 9.5.1.2        | The reading protocol                                                                   |     | 21.1   | Definitions                                |    |

| 9.5.1.3        | Reading and writing limitations                                                        |     | 21.2   | Disclaimers                                |    |

| 9.5.2<br>9.5.3 | Bit transfer                                                                           |     | 21.4   | Trademarks                                 |    |

| 9.5.4          | START and STOP conditions                                                              |     | 22     | Contact information                        |    |

| 9.5.5          | System configuration                                                                   |     |        | Tables                                     |    |

| 9.5.6          | Acknowledge                                                                            |     | 23     |                                            |    |

| 9.5.7          | Data transfer                                                                          |     | 24     | Figures                                    |    |

| 9.5.7.1        | Example data transfers                                                                 |     | 25     | Contents                                   | 42 |

| 9.6            | Instructions                                                                           |     |        |                                            |    |

| 9.6.1          | Instruction set                                                                        | 15  |        |                                            |    |

| 9.6.2          | Instruction wrt_cmd                                                                    | 15  |        |                                            |    |

| 9.6.3          | Instruction dvs_cmd                                                                    | 15  |        |                                            |    |

| 9.6.4          | Instruction pwd_cmd                                                                    | 16  |        |                                            |    |

| 9.6.5          | Instruction 32k_cmd                                                                    | 17  |        |                                            |    |