# R1LV3216R Series

## 32Mb Advanced LPSRAM (2M word x 16bit / 4M word x 8bit)

REJ03C0367-0100 Rev.1.00 2009.05.07

#### Description

The R1LV3216R Series is a family of low voltage 32-Mbit static RAMs organized as 2,097,152-word by 16-bit, fabricated by Renesas's high-performance 0.15um CMOS and TFT technologies.

The R1LV3216R Series is suitable for memory applications where a simple interfacing, battery operating and battery backup are the important design objectives.

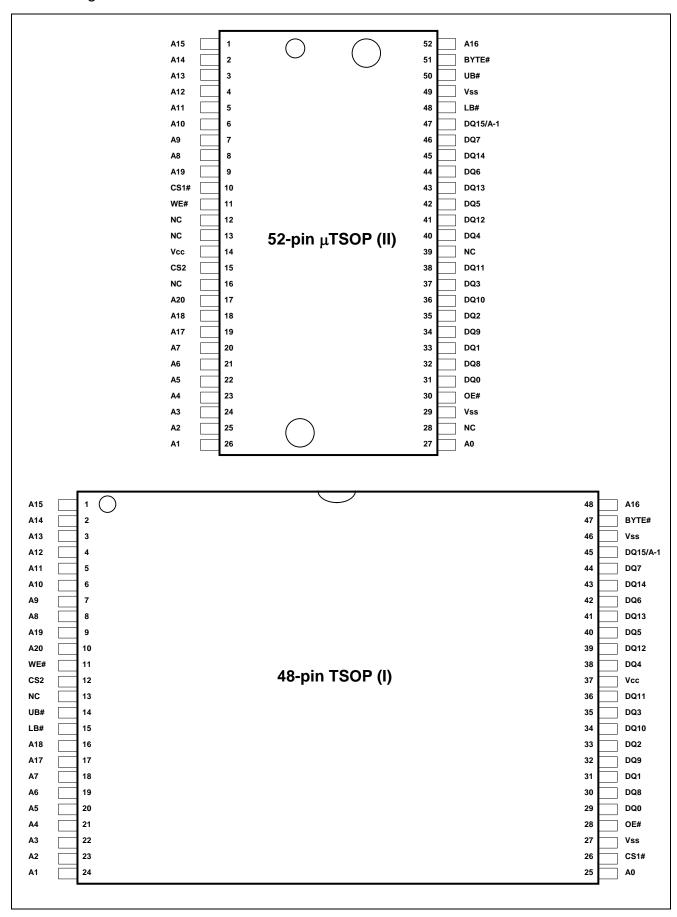

The R1LV3216R Series is provided in 48-pin thin small outline package [TSOP (I): 12mm x 20mm with pin pitch of 0.5mm] and 52-pin micro thin small outline package [µTSOP (II): 10.79mm x 10.49mm with pin pitch of 0.4mm]. It gives the best solution for compaction of mounting area as well as flexibility of wiring pattern of printed circuit boards.

#### **Features**

- Single 2.7~3.6V power supply

- Small stand-by current: 4 µA (3.0V, typical)

- No clocks, No refresh

- All inputs and outputs are TTL compatible.

- Easy memory expansion by CS1#, CS2, LB# and UB#

- Common Data I/O

- Three-state outputs: OR-tie Capability

- OE# prevents data contention on the I/O bus

#### Ordering Information

| Type No.        | Access time | Package                             |

|-----------------|-------------|-------------------------------------|

| R1LV3216RSA-5S% | 55 ns       | 12mm x 20mm 48-pin plastic TSOP (I) |

| R1LV3216RSA-7S% | 70 ns       | (normal-bend type) (48P3R)          |

| R1LV3216RSD-5S% | 55 ns       | 350 mil 52-pin plastic μ-TSOP (II)  |

| R1LV3216RSD-7S% | 70 ns       | (normal-bend type) (52PTG)          |

% - Temperature version; see table below

| % | Temperature Range |

|---|-------------------|

| R | 0 ~ +70 °C        |

| I | -40 ~ +85 °C      |

#### Pin Arrangement

# Pin Description

| Pin name    | Function                  |

|-------------|---------------------------|

| Vcc         | Power supply              |

| Vss         | Ground                    |

| A0 to A20   | Address input (word mode) |

| A-1 to A20  | Address input (byte mode) |

| DQ0 to DQ15 | Data input/output         |

| CS1#        | Chip select 1             |

| CS2         | Chip select 2             |

| WE#         | Write enable              |

| OE#         | Output enable             |

| LB#         | Lower byte enable         |

| UB#         | Upper byte enable         |

| BYTE#       | Byte control mode enable  |

| NC          | Non connection            |

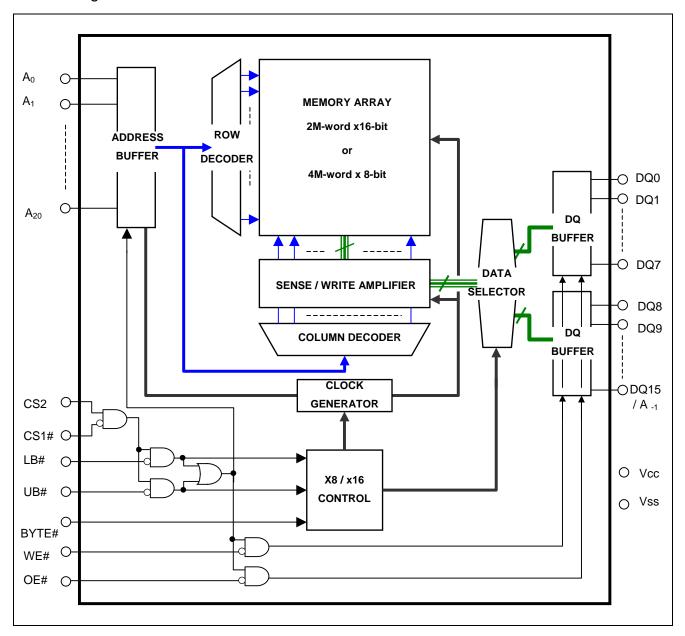

## **Block Diagram**

## Operation Table

| CS1# | CS2 | BYTE# | LB# | UB# | WE# | OE# | DQ0~7  | DQ8~14 | DQ15   | Operation           |

|------|-----|-------|-----|-----|-----|-----|--------|--------|--------|---------------------|

| Н    | Χ   | Χ     | Х   | Х   | Х   | Х   | High-Z | High-Z | High-Z | Stand-by            |

| Х    | L   | Х     | X   | Х   | Х   | Х   | High-Z | High-Z | High-Z | Stand-by            |

| Х    | Χ   | Н     | Н   | Н   | Х   | Х   | High-Z | High-Z | High-Z | Stand-by            |

| L    | Н   | Н     | L   | Н   | L   | Х   | Din    | High-Z | High-Z | Write in lower byte |

| L    | Н   | Н     | L   | Н   | Н   | L   | Dout   | High-Z | High-Z | Read in lower byte  |

| L    | Н   | Н     | L   | Η   | Η   | Н   | High-Z | High-Z | High-Z | Output disable      |

| L    | Н   | Н     | Н   | L   | L   | Х   | High-Z | Din    | Din    | Write in upper byte |

| L    | Н   | Н     | Н   | L   | Н   | L   | High-Z | Dout   | Dout   | Read in upper byte  |

| L    | Н   | Н     | Η   | L   | Η   | Н   | High-Z | High-Z | High-Z | Output disable      |

| L    | Н   | Н     | L   | L   | L   | Х   | Din    | Din    | Din    | Word write          |

| L    | Н   | Н     | L   | L   | Η   | L   | Dout   | Dout   | Dout   | Word read           |

| L    | Н   | Н     | L   | L   | Н   | Н   | High-Z | High-Z | High-Z | Output disable      |

| L    | Н   | L     | L   | L   | L   | Χ   | Din    | High-Z | A-1    | Byte write          |

| L    | Н   | Ĺ     | Ĺ   | Ĺ   | Н   | Ĺ   | Dout   | High-Z | A-1    | Byte read           |

| L    | Н   | L     | L   | L   | Н   | Н   | High-Z | High-Z | A-1    | Output disable      |

Note 1. H:  $V_{IH}$  L: $V_{IL}$  X:  $V_{IH}$  or  $V_{IL}$

### **Absolute Maximum Ratings**

| Parameter                                   | Symbol         |        | Value                                       | unit |  |

|---------------------------------------------|----------------|--------|---------------------------------------------|------|--|

| Power supply voltage relative to Vss        | Vcc            |        | -0.5 to +4.6                                |      |  |

| Terminal voltage on any pin relative to Vss | V <sub>T</sub> |        | -0.5 <sup>*1</sup> to Vcc+0.3 <sup>*2</sup> |      |  |

| Power dissipation                           | P <sub>T</sub> |        | 0.7                                         | W    |  |

| Operation temperature                       | Topr*3         | R ver. | 0 to +70                                    | °C   |  |

| Operation temperature                       | ТОРГ           | I ver. | -40 to +85                                  | °C   |  |

| Storage temperature range                   | Tstg           |        | -65 to 150                                  | °C   |  |

| Storage temperature range under him         | Tbias*3        | R ver. | 0 to +70                                    | °C   |  |

| Storage temperature range under bias        | ibias          | I ver. | -40 to +85                                  | °C   |  |

Note 1. -2.0V in case of AC (Pulse width ≤30ns)

- 2. Maximum voltage is +4.6V.

- 3. Ambient temperature range depends on R/I-version. Please see table on page 1.

<sup>2.</sup> When apply BYTE# ="L", please assign LB#=UB#="L".

## **Recommended Operating Conditions**

| Parameter                 |        | Symbol   | Min. | Тур. | Max.    | Unit     | Note |

|---------------------------|--------|----------|------|------|---------|----------|------|

| Supply voltage            |        | Vcc      | 2.7  | 3.0  | 3.6     | V        |      |

|                           |        | Vss      | 0    | 0    | 0       | <b>V</b> |      |

| Input high voltage        |        | $V_{IH}$ | 2.4  | -    | Vcc+0.2 | V        |      |

| Input low voltage         |        | $V_{IL}$ | -0.2 | 1    | 0.4     | V        | 1    |

| Ambient temperature range |        | Ta       | 0    | -    | +70     | °C       | 2    |

| Ambient temperature range | I ver. | Ia       | -40  | 1    | +85     | °C       | 2    |

Note 1. -2.0V in case of AC (Pulse width  $\leq 30$ ns)

#### **DC** Characteristics

| Parameter                 | Symbol           | Min. | Тур.             | Max. | Unit | Test conditions                                                                                                                                                                                                             |  |  |

|---------------------------|------------------|------|------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Input leakage current     | I <sub>LI</sub>  | -    | -                | 1    | μΑ   | Vin = Vss to Vcc                                                                                                                                                                                                            |  |  |

| Output leakage current    | I <sub>LO</sub>  | •    | -                | 1    | μΑ   | BYTE# $\geq$ Vcc -0.2V or BYTE# $\leq$ 0.2V<br>CS1# =V <sub>IH</sub> or CS2 =V <sub>IL</sub> or<br>OE# =V <sub>IH</sub> or WE# =V <sub>IL</sub> or<br>LB# = UB# =V <sub>IH</sub> , VI/O =Vss to Vcc                         |  |  |

| Average operating current | I <sub>CC1</sub> | -    | 40 <sup>*1</sup> | 55   | mA   | Min. cycle, duty =100%, II/O = 0mA<br>BYTE# ≥ Vcc -0.2V or BYTE# ≤ 0.2V<br>CS1# =V <sub>IL</sub> , CS2 =V <sub>IH</sub> , Others = V <sub>IH</sub> /V <sub>IL</sub>                                                         |  |  |

|                           | I <sub>CC2</sub> | -    | 3 <sup>*1</sup>  | 8    | mA   | Cycle =1 $\mu$ s, duty =100%, II/O = 0mA<br>BYTE# $\geq$ Vcc -0.2V or BYTE# $\leq$ 0.2V<br>CS1# $\leq$ 0.2V, CS2 $\geq$ V <sub>CC</sub> -0.2V,<br>V <sub>IH</sub> $\geq$ V <sub>CC</sub> -0.2V, V <sub>IL</sub> $\leq$ 0.2V |  |  |

| Standby current           | I <sub>SB</sub>  | -    | 0.1*1            | 0.3  | mA   | BYTE# ≥ Vcc -0.2V or BYTE# ≤ 0.2V<br>CS2 =V <sub>IL</sub>                                                                                                                                                                   |  |  |

| Standby current           |                  | -    | 4 <sup>*1</sup>  | 12   | μΑ   | ~+25°C                                                                                                                                                                                                                      |  |  |

|                           | I <sub>SB1</sub> | -    | 7*2              | 24   | μА   | 8YTE# ≤ 0.2V<br>(1) 0V ≤ CS2 ≤ 0.2V or<br>(2) CS1# ≥ V <sub>CC</sub> -0.2V,                                                                                                                                                 |  |  |

|                           | ISB1             | -    | -                | 50   | μΑ   | $\sim +70^{\circ}\text{C}$ (2) CS1# $\geq$ V <sub>CC</sub> -0.2V,<br>CS2 $\geq$ V <sub>CC</sub> -0.2V or<br>(3) LB# = UB# $\geq$ V <sub>CC</sub> -0.2V,                                                                     |  |  |

|                           |                  | ı    | -                | 80   | μΑ   | ~+85°C                                                                                                                                                                                                                      |  |  |

| Output high voltage       | V <sub>OH</sub>  | 2.4  | -                | -    | V    | BYTE# $\geq$ Vcc -0.2V or BYTE# $\leq$ 0.2V $I_{OH} = -0.5$ mA                                                                                                                                                              |  |  |

| Output low voltage        | V <sub>OL</sub>  | -    | -                | 0.4  | V    | BYTE# ≥ Vcc -0.2V or BYTE# ≤ 0.2V<br>I <sub>OL</sub> = 2mA                                                                                                                                                                  |  |  |

Note 1. Typical parameter indicates the value for the center of distribution at 3.0V ( $Ta=25^{\circ}C$ ), and not 100% tested.

<sup>2.</sup> Ambient temperature range depends on R/I-version. Please see table on page 1.

<sup>2.</sup> Typical parameter indicates the value for the center of distribution at 3.0V ( $Ta=40^{\circ}C$ ), and not 100% tested.

#### Capacitance

(Ta = $25^{\circ}$ C, f =1MHz)

| Parameter                  | Symbol           | Min. | Тур. | Max. | Unit | Test conditions      | Note |

|----------------------------|------------------|------|------|------|------|----------------------|------|

| Input capacitance          | C in             | -    | -    | 10   | pF   | Vin =0V              | 1    |

| Input / output capacitance | C <sub>I/O</sub> | -    | -    | 10   | pF   | V <sub>I/O</sub> =0V | 1    |

Note1. This parameter is sampled and not 100% tested.

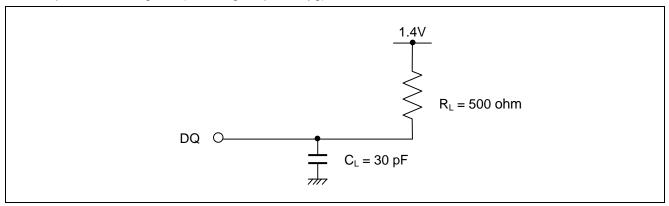

### **AC Characteristics**

Test Conditions (Vcc =  $2.7V \sim 3.6V$ , Ta =  $0 \sim +70^{\circ}C / -40 \sim +85^{\circ}C^{*1}$ )

- Input pulse levels:  $V_{IL} = 0.4V$ ,  $V_{IH} = 2.4V$

- Input rise and fall time: 5ns

- Input and output timing reference level: 1.4V

- Output load: See figures (Including scope and jig)

Note1. Ambient temperature range depends on R/I-version. Please see table on page 1.

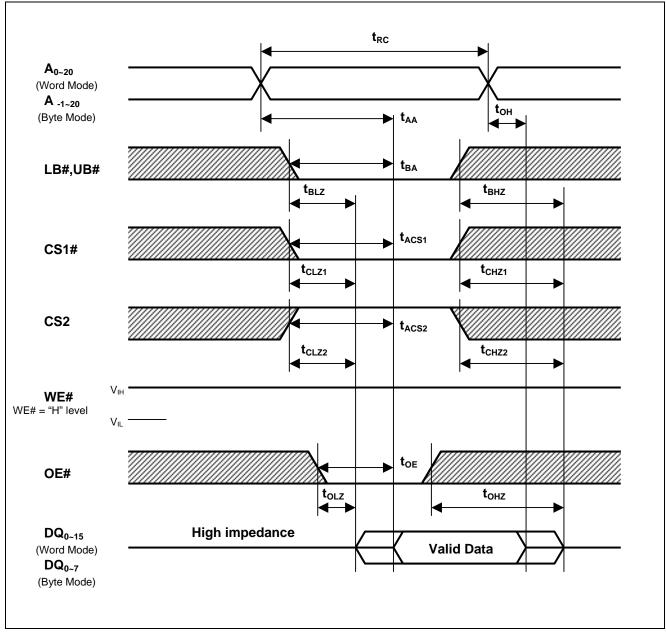

## Read Cycle

| Parameter                          | Symbol            | R1LV32 | 16R**-5S | R1LV32 | 16R**-7S | Unit  | Note  |

|------------------------------------|-------------------|--------|----------|--------|----------|-------|-------|

| Farameter                          | Symbol            | Min.   | Max.     | Min.   | Max.     | Offic | Note  |

| Read cycle time                    | t <sub>RC</sub>   | 55     | -        | 70     | -        | ns    |       |

| Address access time                | t <sub>AA</sub>   | -      | 55       | -      | 70       | ns    |       |

| Chin pologt gagge time             | t <sub>ACS1</sub> | -      | 55       | -      | 70       | ns    |       |

| Chip select access time            | t <sub>ACS2</sub> | -      | 55       | -      | 70       | ns    |       |

| Output enable to output valid      | t <sub>OE</sub>   | -      | 25       | -      | 35       | ns    |       |

| Output hold from address change    | tон               | 10     | -        | 10     | -        | ns    |       |

| LB#, UB# access time               | t <sub>BA</sub>   | -      | 55       | -      | 70       | ns    |       |

| Chin coloct to output in low 7     | t <sub>CLZ1</sub> | 10     | -        | 10     | -        | ns    | 2,3   |

| Chip select to output in low-Z     | t <sub>CLZ2</sub> | 10     | -        | 10     | -        | ns    | 2,3   |

| LB#, UB# enable to low-Z           | t <sub>BLZ</sub>  | 5      | -        | 5      | -        | ns    | 2,3   |

| Output enable to output in low-Z   | t <sub>OLZ</sub>  | 5      | -        | 5      | -        | ns    | 2,3   |

| Chin decelest to suspect in high 7 | t <sub>CHZ1</sub> | 0      | 20       | 0      | 25       | ns    | 1,2,3 |

| Chip deselect to output in high-Z  | t <sub>CHZ2</sub> | 0      | 20       | 0      | 25       | ns    | 1,2,3 |

| LB#, UB# disable to high-Z         | t <sub>BHZ</sub>  | 0      | 20       | 0      | 25       | ns    | 1,2,3 |

| Output disable to output in high-Z | tonz              | 0      | 20       | 0      | 25       | ns    | 1,2,3 |

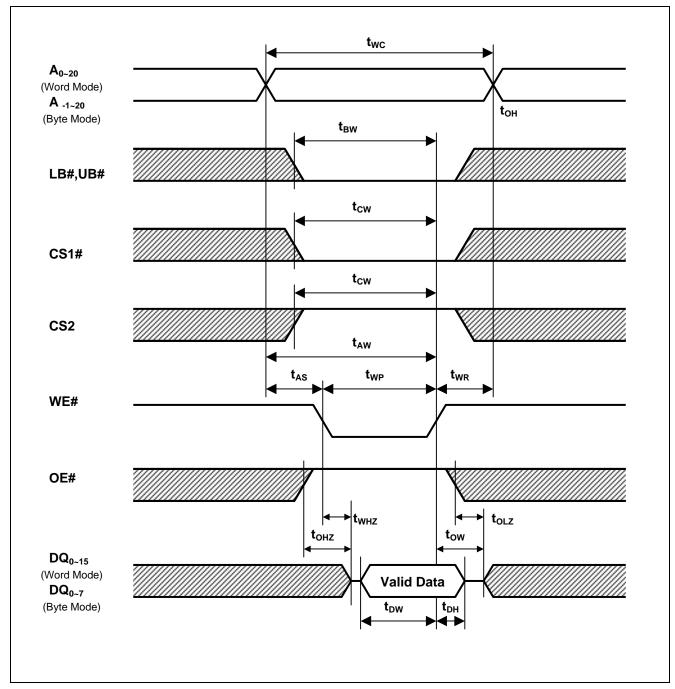

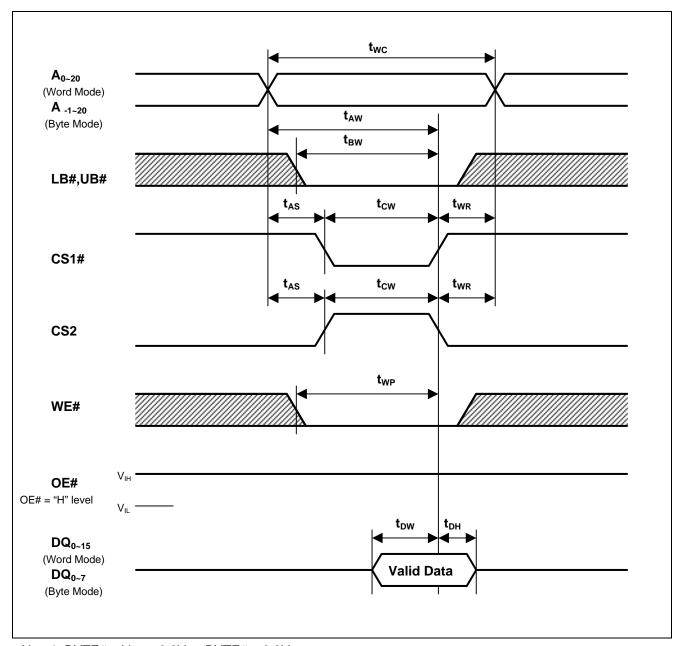

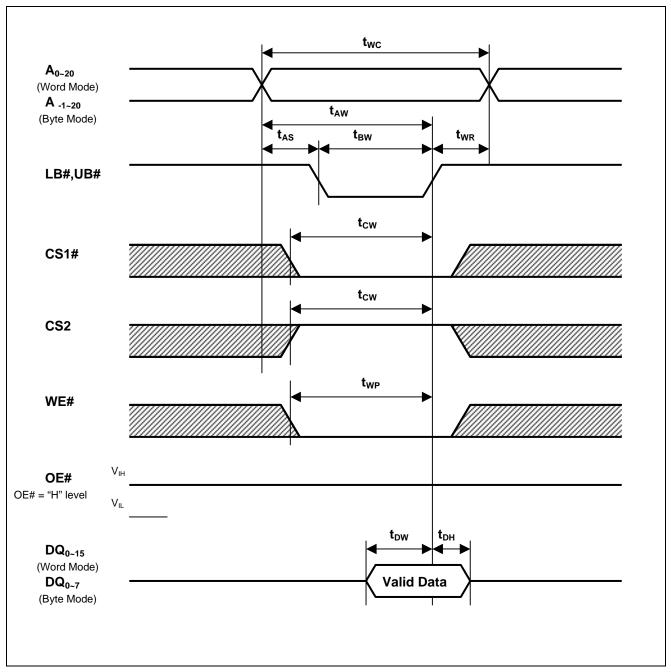

#### Write Cycle

| Parameter                          | Symbol           | R1LV32 | 16R**-5S | R1LV32 | I6R**-7S | Unit  | Note |

|------------------------------------|------------------|--------|----------|--------|----------|-------|------|

| Farameter                          | Symbol           | Min.   | Max.     | Min.   | Max.     | Offic | Note |

| Write cycle time                   | twc              | 55     | -        | 70     | ı        | ns    |      |

| Address valid to end of write      | t <sub>AW</sub>  | 50     | -        | 65     | ı        | ns    |      |

| Chip select to end of write        | t <sub>CW</sub>  | 50     | -        | 65     | ı        | ns    | 5    |

| Write pulse width                  | t <sub>WP</sub>  | 40     | -        | 55     | ı        | ns    | 4    |

| LB#, UB# valid to end of write     | t <sub>BW</sub>  | 50     | -        | 65     | ı        | ns    |      |

| Address setup time                 | t <sub>AS</sub>  | 0      | -        | 0      | ı        | ns    | 6    |

| Write recovery time                | t <sub>WR</sub>  | 0      | -        | 0      | ı        | ns    | 7    |

| Data to write time overlap         | t <sub>DW</sub>  | 25     | -        | 35     | ı        | ns    |      |

| Data hold from write time          | t <sub>DH</sub>  | 0      | -        | 0      | -        | ns    |      |

| Output enable from end of write    | tow              | 5      | -        | 5      | -        | ns    | 2    |

| Output disable to output in high-Z | t <sub>OHZ</sub> | 0      | 20       | 0      | 25       | ns    | 1,2  |

| Write to output in high-Z          | t <sub>WHZ</sub> | 0      | 20       | 0      | 25       | ns    | 1,2  |

Note1. t<sub>CHZ</sub>, t<sub>OHZ</sub>, t<sub>WHZ</sub> and t<sub>BHZ</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referred to output voltage levels.

- 2. This parameter is sampled and not 100% tested.

- 3. At any given temperature and voltage condition,  $t_{HZ}$  max is less than  $t_{LZ}$  min both for a given device and from device to device.

- 4. A write occurs during the overlap of a low CS1#, a high CS2, a low WE# and a low LB# or a low UB#.

A write begins at the latest transition among CS1# going low, CS2 going high, WE# going low and LB# going low or UB# going low .

A write ends at the earliest transition among CS1# going high, CS2 going low, WE# going high and LB# going high or UB# going high. t<sub>WP</sub> is measured from the beginning of write to the end of write.

- 5.  $t_{\text{CW}}$  is measured from the later of CS1# going low or CS2 going high to end of write.

- 6. t<sub>AS</sub> is measured the address valid to the beginning of write.

- 7. twR is measured from the earliest of CS1# or WE# going high or CS2 going low to the end of write cycle.

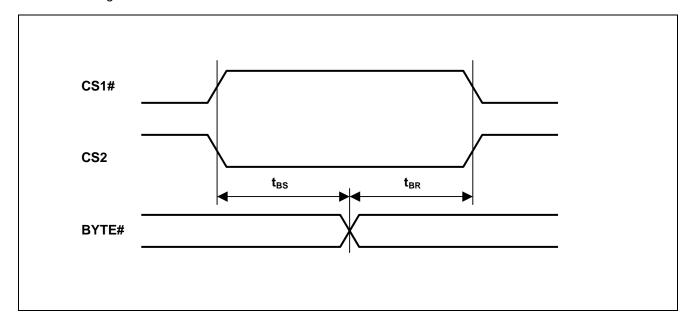

## BYTE# Timing Conditions

| Parameter          | Symbol          | R1LV32 | 16R**-5S | R1LV32 | 16R**-7S | Unit  | Note |

|--------------------|-----------------|--------|----------|--------|----------|-------|------|

| i arameter         | Symbol          | Min.   | Max.     | Min.   | Max.     | Offic |      |

| Byte setup time    | t <sub>BS</sub> | 5      | -        | 5      | -        | ms    |      |

| Byte recovery time | t <sub>BR</sub> | 5      | -        | 5      | -        | ms    |      |

#### BYTE# Timing Waveforms

## **Timing Waveforms**

## Read Cycle\*1

Note1. BYTE# ≥ Vcc – 0.2V or BYTE# ≤ 0.2V

## Write Cycle (1)\*1 (WE# CLOCK)

Note1. BYTE# ≥ Vcc – 0.2V or BYTE# ≤ 0.2V

## Write Cycle (2)\*1 (CS1#, CS2 CLOCK)

Note1. BYTE#  $\geq$  Vcc - 0.2V or BYTE#  $\leq$  0.2V

## Write Cycle (3)\*1 (LB#, UB# CLOCK)

Note1. BYTE# ≥ Vcc – 0.2V or BYTE# ≤ 0.2V

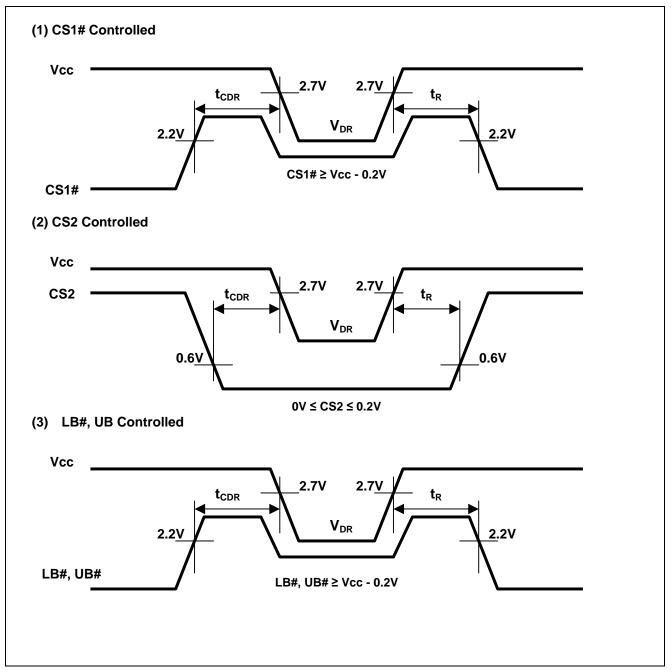

#### Low Vcc Data Retention Characteristics

| Parameter                          | Symbol           | Min. | Тур. | Max. | Unit |                                                        | Test conditions*3                                                                                                                            |  |

|------------------------------------|------------------|------|------|------|------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>CC</sub> for data retention | $V_{DR}$         | 2.0  | -    | 3.6  | V    | (1) 0V ≤ 0<br>(2) CS1#<br>CS2 ≥<br>(3) LB# =<br>CS1# ≤ | Vcc -0.2V or BYTE# ≤ 0.2V<br>CS2 ≤ 0.2V or<br>≥ $V_{CC}$ -0.2V,<br>$V_{CC}$ -0.2V or<br>: UB# ≥ $V_{CC}$ -0.2V,<br>≤ 0.2V,<br>$V_{CC}$ -0.2V |  |

|                                    |                  | -    | 4*1  | 12   | μΑ   | ~+25°C                                                 | Vin ≥ 0V<br>BYTE# ≥ Vcc -0.2V or                                                                                                             |  |

| Data retention current             |                  | -    | 7*2  | 24   | μΑ   | ~+40°C                                                 | BYTE# $\leq$ 0.2V<br>(1) 0V $\leq$ CS2 $\leq$ 0.2V or                                                                                        |  |

| Data retention current             | ICCDR            | -    | -    | 50   | μΑ   | ~+70°C                                                 | (2) CS1# $\geq$ V <sub>CC</sub> -0.2V,<br>CS2 $\geq$ V <sub>CC</sub> -0.2V or<br>(3) LB# = UB# $\geq$ V <sub>CC</sub> -0.2V,                 |  |

|                                    |                  | -    | -    | 80   | μА   | ~+85°C                                                 | CS1# ≤ 0.2V,<br>CS2 ≥ V <sub>CC</sub> -0.2V                                                                                                  |  |

| Chip select to data retention time | t <sub>CDR</sub> | 0    | -    | -    | ns   | See retention waveform.                                |                                                                                                                                              |  |

| Operation recovery time            | t <sub>R</sub>   | 5    | -    | -    | ms   |                                                        |                                                                                                                                              |  |

Note 1. Typical parameter indicates the value for the center of distribution at 3.0V (Ta= 25°C), and not 100% tested.

- 2. Typical parameter indicates the value for the center of distribution at 3.0V (Ta= 40°C), and not 100% tested.

- 3. CS2 also controls address buffer, WE# buffer ,CS1# buffer ,OE# buffer ,LB# ,UB# buffer and Din buffer. If CS2 controls data retention mode, Vin levels (address, WE# ,OE#,CS1#,LB#,UB#,I/O) can be in the high impedance state. If CS1# controls data retention mode, CS2 must be CS2 ≥ Vcc-0.2V or0V ≤ CS2 ≤ 0.2V. The other input levels (address, WE# ,OE#,CS1#,LB#,UB#,I/O) can be in the high impedance state.

Low Vcc Data Retention Timing Waveforms\*1

Note1. BYTE# ≥ Vcc - 0.2V or BYTE# ≤ 0.2V

# Revision History

## R1LV3216R Series Data Sheet

|      |              | Contents of Revision |                                                                                       |  |

|------|--------------|----------------------|---------------------------------------------------------------------------------------|--|

| Rev. | Date         | Page                 | Description                                                                           |  |

| 0.01 | Mar.24, 2008 | -                    | Initial issue: Preliminary Data Sheet                                                 |  |

| 1.00 | May 07, 2009 | -                    | Finalized                                                                             |  |

|      |              | 5                    | Operation Table corrected                                                             |  |

|      |              | 6                    | Error corrected: I <sub>SB</sub> Test condition CS2=V <sub>IH</sub> ->V <sub>IL</sub> |  |

Renesas Technology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warrantes or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property girbs to any other rights of representations with respect to the information in this document in this document of the purpose of the respect of the information in this document in the product data, diagrams, charts, programs, algorithms, and application critical expensions of the purpose of any other military use. When exporting the products or technology described in this document for the purpose of military applications, and procedures required by such laws and regulations, and procedures required to the date this document in the such and the procedure of the procedure o

#### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510