The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# SH7616 Hardware Manual

ardware Manua

64

Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family/SH7600 Series SH7616 HD6417616

Rev. 2.00 Revision Date: Mar 09, 2006

RenesasTechnology www.renesas.com

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

# Preface

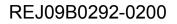

The SH7616 is a microprocessor that integrates peripheral functions necessary for system configuration with a 32-bit internal architecture SH2-DSP CPU as its core.

The SH7616's on-chip peripheral functions include a cache memory, an interrupt controller, timers, an ethernet controller (EtherC), DSP, a serial communication interface with FIFO (SCIF), a USB function module, a user break controller (UBC), a bus state controller (BSC), a direct memory access cntroller (DMAC), and I/O ports, making it ideal for use as a microcomputer in electronic devices that require high speed together with low power consumption.

Intended Readership: This manual is intended for users undertaking the design of an application system using the SH7616. Readers using this manual require a basic knowledge of electrical circuits, logic circuits, and microcomputers.

Purpose: The purpose of this manual is to give users an understanding of the hardware functions and electrical characteristics of the SH7616. Details of execution instructions can be found in the SH-1, SH-2, SH-DSP Programming Manual, which should be read in conjunction with the present manual.

Using this Manual:

- For an overall understanding of the SH7616's functions Follow the Table of Contents. This manual is broadly divided into sections on the CPU, system control functions, peripheral functions, and electrical characteristics.

- For a detailed understanding of CPU functions Refer to the separate publication SH-1, SH-2, SH-DSP Programming Manual. Note on bit notation: Bits are shown in high-to-low order from left to right.

Related Material: The latest information is available at our Web Site. Please make sure that you have the most up-to-date information available. http://www.renesas.com/

Rev. 2.00 Mar 09, 2006 page iii of xxvi

#### Renesas

User's Manuals on the SH7616:

| Manual Title                      | ADE No.          |

|-----------------------------------|------------------|

| SH7616 Hardware Manual            | This manual      |

| SH-1/ SH-2/SH-DSP Software Manual | REJ09B0171-0500O |

Users manuals for development tools:

| Manual Title                                                      | ADE No.         |

|-------------------------------------------------------------------|-----------------|

| C/C++ Complier, Assembler, Optimized Linkage Editor User's Manual | REJ10B0152-0101 |

| Simulator Debugger Users Manual                                   | REJ10B0210-0200 |

| High-performance Embedded Workshop Users Manual                   | REJ10J0886-0300 |

#### Application Note:

| Manual Title   | ADE No.         |

|----------------|-----------------|

| C/C++ Complier | REJ05B0463-0300 |

Rev. 2.00 Mar 09, 2006 page iv of xxvi

# Main Revisions in This Edition

| Item                                                                   | Page          | Revision (See Manual for Details)                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

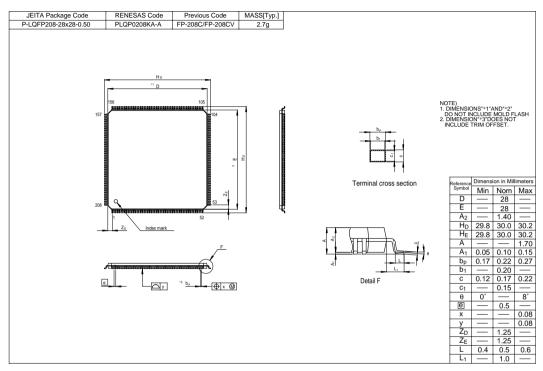

| All                                                                    | 37            | <ul> <li>Company name amended<br/>Hitachi, Ltd. → Renesas Technology Corp.</li> <li>Amendments made due to change in package code<br/>FP-208C → PRQP0208KA-A</li> <li>Description added</li> </ul>                                                                                                           |

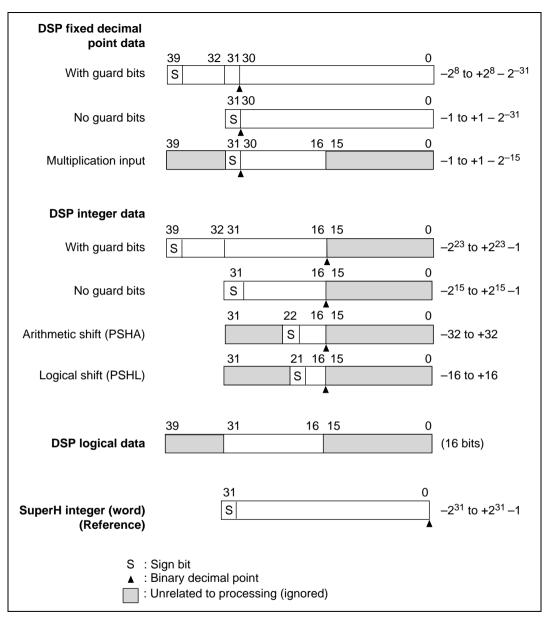

| C C                                                                    |               | Figure 2.4 shows the DSP registers. The DSR register bit functions are shown in table 2.2. Registers A0, X0, X1, Y0, Y1, and DSR are handled as system registers by CPU core instructions.                                                                                                                   |

| 7.1.5 Address Map                                                      | 255           | Table amended                                                                                                                                                                                                                                                                                                |

| Table 7.3 Address<br>Map                                               |               | AddressSpaceMemorySizeH'1000E000-H'1000EFFFOn-chip X RAM area4 kbytesH'1001E000-H'1001EFFFOn-chip Y RAM area4 kbytes                                                                                                                                                                                         |

|                                                                        | 269 to<br>274 | Description replaced                                                                                                                                                                                                                                                                                         |

| 7.5.11 64 Mbit<br>Synchronous DRAM<br>(2 Mword × 32-bit)<br>Connection | 323           | Description amended<br><b>Synchronous DRAM Mode Settings:</b> To make mode settings for<br>the synchronous DRAM, write to address X+H'FFFF6000 or<br>X+H'FFFF8000 from the CPU. (X represents the setting value.)<br>Whether to use X+H'FFFF6000 or X+H'FFFF8000 determines on<br>the synchronous DRAM used. |

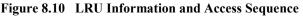

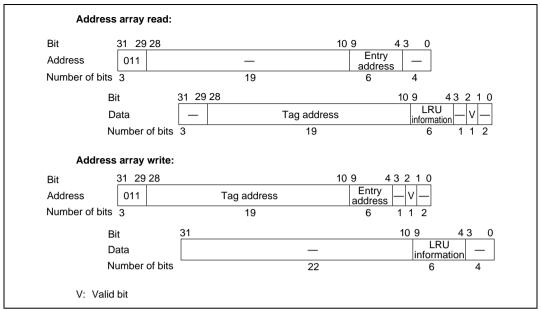

| 8.4.7 Associative 3<br>Purges<br>Figure 8.11                           | 369           | Figure amended Associative purge: Bit 31 2928 10 9 4 3 0                                                                                                                                                                                                                                                     |

#### **Revision (See Manual for Details)** Page

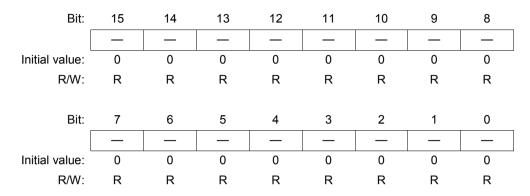

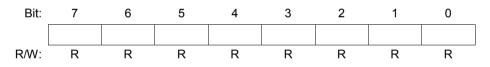

| 10.2.8             |

|--------------------|

| Transmit/Receive   |

| Status Copy Enable |

Register (TRSCER)

Item

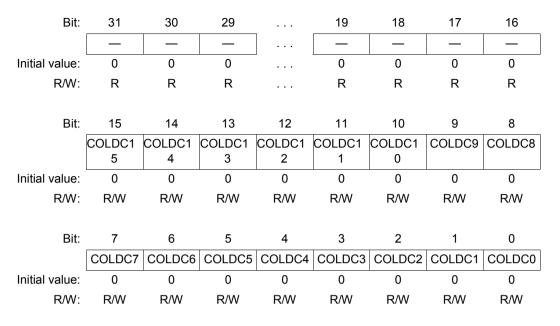

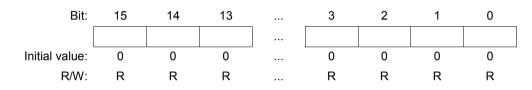

#### Description amended

437

| •              |        |    |    |    |    |    |    |    |

|----------------|--------|----|----|----|----|----|----|----|

| Bit:           | 31     | 30 | 29 |    | 19 | 18 | 17 | 16 |

|                | —      | _  | _  |    | _  | _  | _  | —  |

| Initial value: | 0      | 0  | 0  |    | 0  | 0  | 0  | 0  |

| R/W:           | R      | R  | R  |    | R  | R  | R  | R  |

|                |        |    |    |    |    |    |    |    |

| Bit:           | 15     | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|                | —      | _  | _  | —  | —  | —  | —  | —  |

| Initial value: | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| R/W:           | R      | R  | R  | R  | R  | R  | R  | R  |

|                |        |    |    |    |    |    |    |    |

| Bit:           | 7      | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|                | RMAFCE | —  | —  | —  | —  | —  | —  | —  |

| Initial value: | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| R/W:           | R/W    | R  | R  | R  | R  | R  | R  | R  |

|                |        |    |    |    |    |    |    |    |

Bits 31 to 8-Reserved These bits are always read as 0. The write value should always be 0.

Bit 7-Multicast Address Frame Receive (RMAF): Bit Copy Enable (RMAFCE)

| Bit 7: RMAFCE | Description                                                                                            |

|---------------|--------------------------------------------------------------------------------------------------------|

| 0             | Enables the RMAF bit status to be indicated in the RFS7 bit in the receive descriptor.                 |

| 1             | Disables occurrence of corresponding source to be indicated in the RFS7 bit in the receive descriptor. |

Bits 6 to 0-Reserved: These bits are always read as 0. The write value should always be 0.

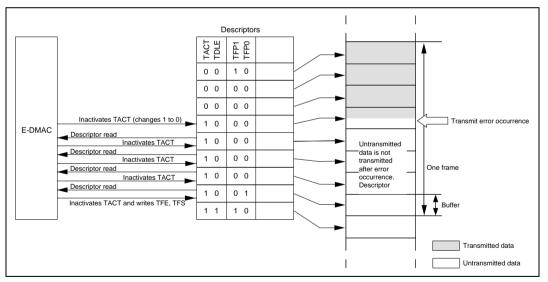

10.3.1 Descriptor 450 List and Data Buffers

#### Description amended

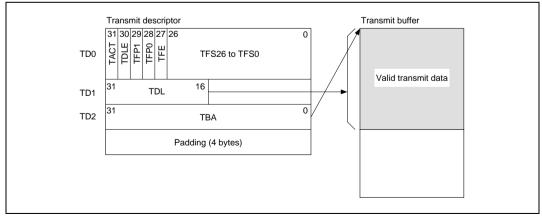

Bit 27-Transmit Frame Error (TFE): Indicates that one or other bit of the transmit frame status indicated by bits 26 to 0 is set.

Transmit Descriptor 0 (TD0)

#### Bit 27: TFE Description 0

| 1 An error of some kind eccurred during transmission (see hits 26 to 0) | 0 | No error during transmission                                          |  |

|-------------------------------------------------------------------------|---|-----------------------------------------------------------------------|--|

|                                                                         | 1 | An error of some kind occurred during transmission (see bits 26 to 0) |  |

Bits 26 to 0-Transmit Frame Status 26 to 0 (TFS26 to TFS0): These bits indicate the error status during frame transmission.

- TFS26 to TFS9-Reserved

- TFS8—Teransmit Abort Detect

- Note: This bit is set to 1 wh any of Transmit Frame Status bits 4 to 0 is set. When this bit is set, the Transmit Frame Error bit (bit 27: TFE) is set to 1.

- TFS7 to TFS5—Reserved

| Item                                                      | Page  | Revis  | ior      | ı (S | See               | M           | an  | ual for De | etails)        |   |   |

|-----------------------------------------------------------|-------|--------|----------|------|-------------------|-------------|-----|------------|----------------|---|---|

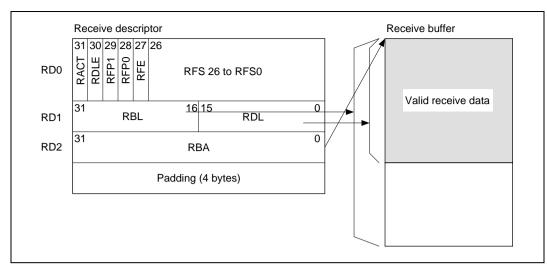

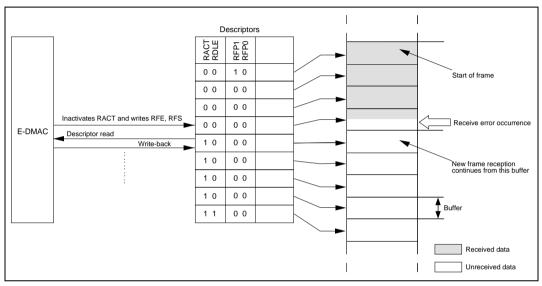

| 10.3.1 Descriptor<br>List and Data Buffers                | 451   | Figure |          |      |                   |             |     |            |                |   | 1 |

| Receive Descriptor                                        |       |        | Re<br>31 |      | ve c<br>29        |             |     |            |                |   |   |

| Figure 10.3<br>Relationship between<br>Receive Descriptor | ween  | RD0    | RACT     | RDLE | RFP1              | <b>RFPO</b> | RFE | RF         | RFS 26 to RFS0 |   |   |

| and Receive Buffer                                        | uffer |        |          |      |                   | RE          | 3L  | 16         | 15<br>RDL      | 0 |   |

|                                                           |       | RD2    | 31       |      |                   |             |     | RE         | 3A             | 0 |   |

|                                                           |       |        |          |      | Padding (4 bytes) |             |     |            |                |   |   |

| _                                                         |       |        |          |      |                   |             |     |            |                |   |   |

Rev. 2.00 Mar 09, 2006 page vii of xxvi

| ltem                                                   | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                           |                                                                                       |  |  |  |  |

|--------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| 10.3.1 Descriptor                                      | 453  | Description amended                                                                                                                                                                                                                                                                                                         |                                                                                       |  |  |  |  |

| List and Data Buffers<br>Receive Descriptor 0<br>(TD0) |      | Bit 27—Receive Frame Error (RFE): Indicates that one or other bit of the receive frame status indicated by bits 26 to 0 is set. Whether or not the multicast address frame receive information which is part of the frame status, is copied into this bit is specified by the transmit/receive status copy enable register. |                                                                                       |  |  |  |  |

|                                                        |      | Bit 27: RFE Description                                                                                                                                                                                                                                                                                                     |                                                                                       |  |  |  |  |

|                                                        |      | 0 No error during reception (Initial value)                                                                                                                                                                                                                                                                                 |                                                                                       |  |  |  |  |

|                                                        |      | 1 An error of some kind occurred during reception (see bits 26 to 0)                                                                                                                                                                                                                                                        |                                                                                       |  |  |  |  |

|                                                        | •    | • Bits 26 to 0—Receive Frame Status 26 to 0 (RFS26 to RFS0):<br>These bits indicate the error status during frame reception.                                                                                                                                                                                                |                                                                                       |  |  |  |  |

|                                                        |      | RFS26 to RFS10—Reserved                                                                                                                                                                                                                                                                                                     |                                                                                       |  |  |  |  |

|                                                        |      | <ul> <li>RFS9—Receive FIFO Overflow (corresponds to RFOF bit in EESR)</li> </ul>                                                                                                                                                                                                                                            |                                                                                       |  |  |  |  |

|                                                        | •    | RFS8—Reserve Abort Detect                                                                                                                                                                                                                                                                                                   |                                                                                       |  |  |  |  |

|                                                        |      | Note: This bit is set to 1 when any of Receive Frame Status<br>bit 9, bit 7, bits 4 to 0 is set. When this bit is set, the<br>Receive Frame Error bit (bit 27: RFE) is set to 1.                                                                                                                                            |                                                                                       |  |  |  |  |

|                                                        |      | <ul> <li>RFS7— Receive Multicast Address Frame (corresponds to<br/>RMAF bit in EESR)</li> </ul>                                                                                                                                                                                                                             |                                                                                       |  |  |  |  |

|                                                        |      | RFS6—Reserved <sup>*1</sup>                                                                                                                                                                                                                                                                                                 |                                                                                       |  |  |  |  |

|                                                        |      | <ul> <li>RSF5— Receive Frame Discard Request Assertion<br/>(corresponds to RFAR bit in EESR)<sup>*1</sup></li> </ul>                                                                                                                                                                                                        |                                                                                       |  |  |  |  |

|                                                        | •    | RFS4—Receive Residual-Bit Frame (corresponds to RRF bit in EESR)                                                                                                                                                                                                                                                            |                                                                                       |  |  |  |  |

|                                                        |      | •                                                                                                                                                                                                                                                                                                                           | <ul> <li>RFS3—Receive Too-Long Frame (corresponds to RTLF bit in<br/>EESR)</li> </ul> |  |  |  |  |

|                                                        |      | <ul> <li>RFS2—Receive Too-Short Frame (corresponds to RTSF bit in<br/>EESR)</li> </ul>                                                                                                                                                                                                                                      |                                                                                       |  |  |  |  |

|                                                        |      | <ul> <li>RFS1—PHY-LSI Receive Error (corresponds to PRE bit in<br/>EESR)</li> </ul>                                                                                                                                                                                                                                         |                                                                                       |  |  |  |  |

|                                                        |      | • RFS0—CRC Error on Received Frame (corresponds to CERF bit in EESR)                                                                                                                                                                                                                                                        |                                                                                       |  |  |  |  |

|                                                        |      | Note: 1. Only HD6417616 is effective. HD6417615 is Reserved bit.                                                                                                                                                                                                                                                            |                                                                                       |  |  |  |  |

| Item                                             | Page   | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|--------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

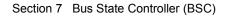

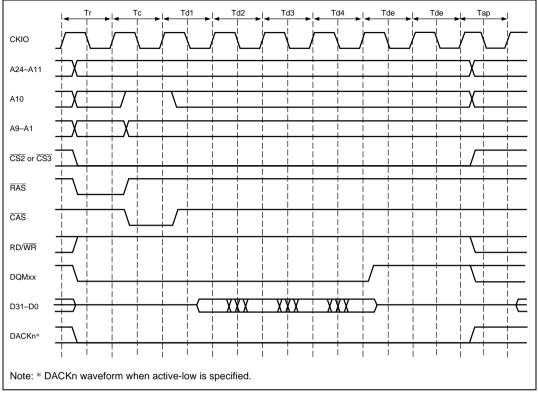

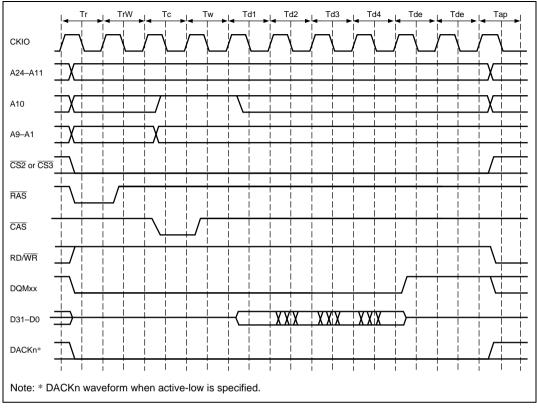

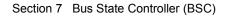

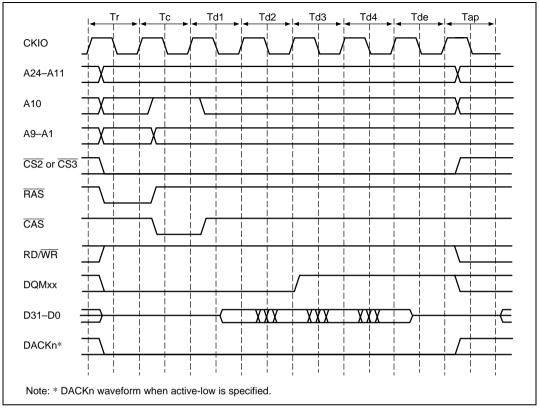

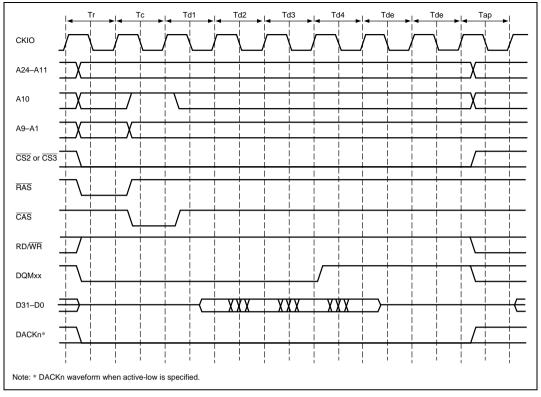

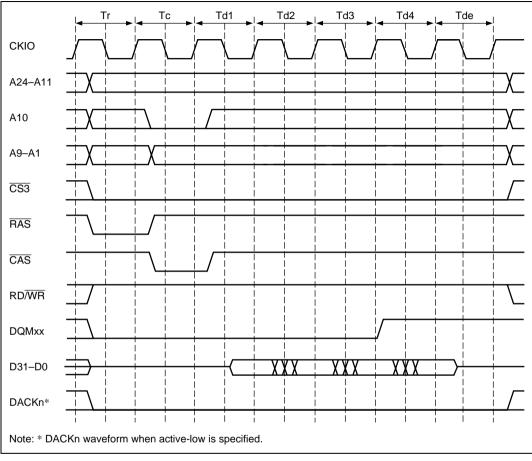

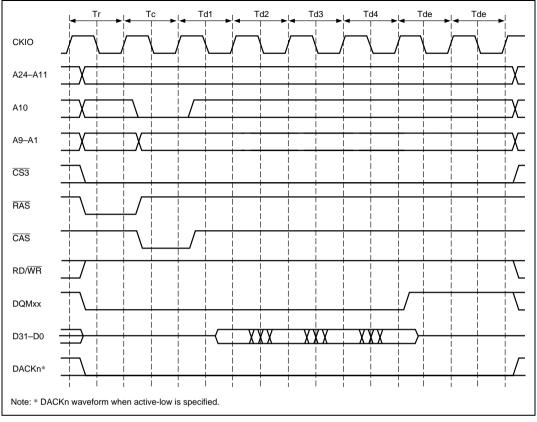

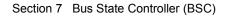

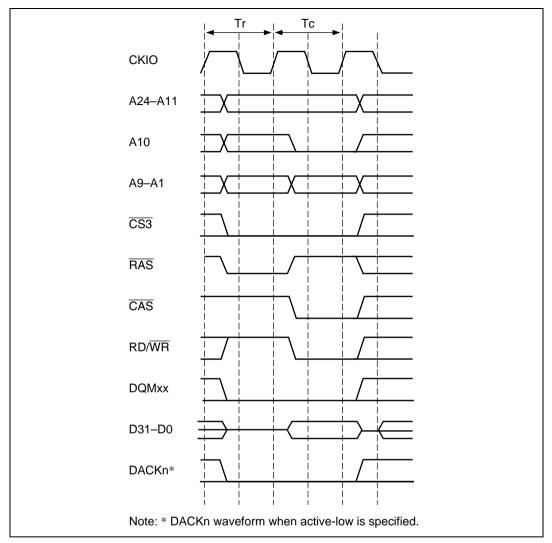

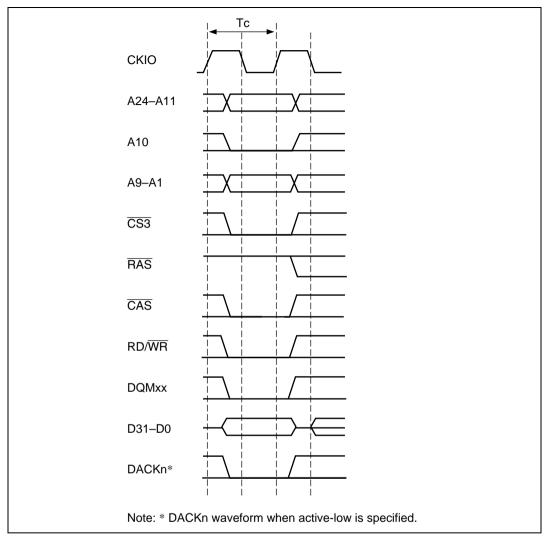

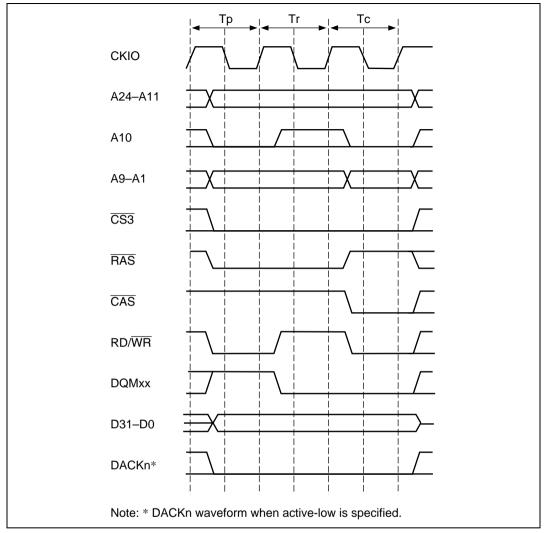

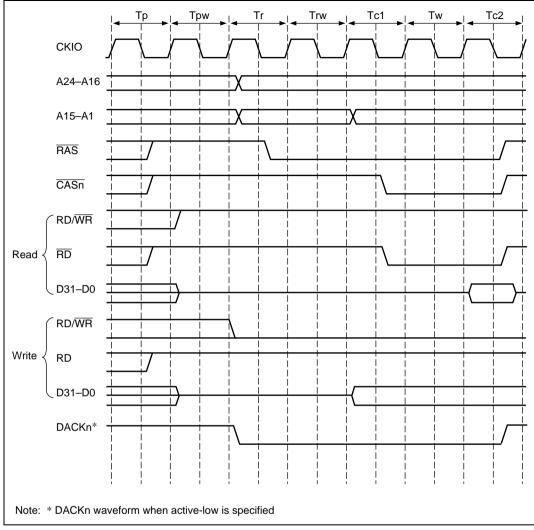

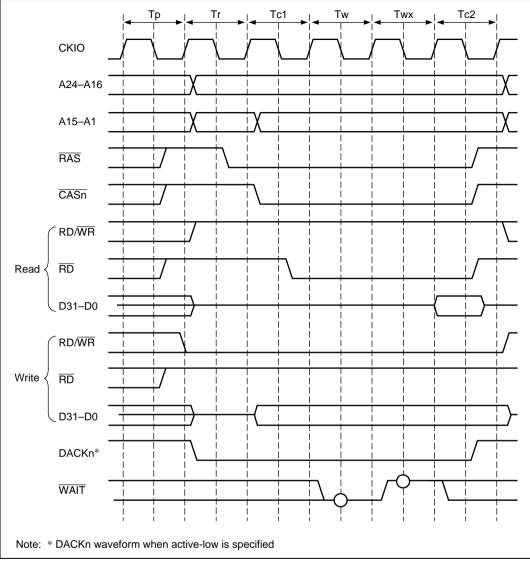

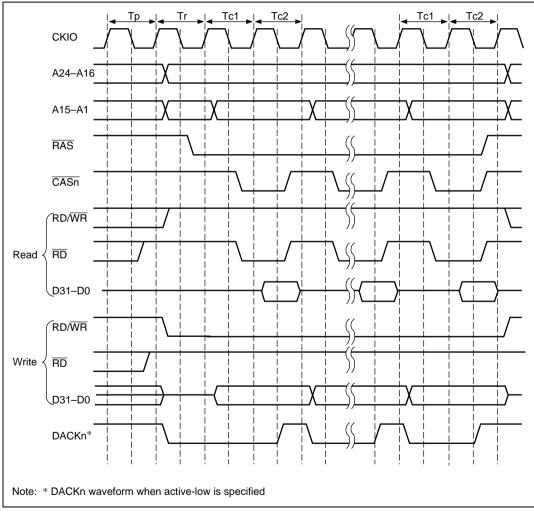

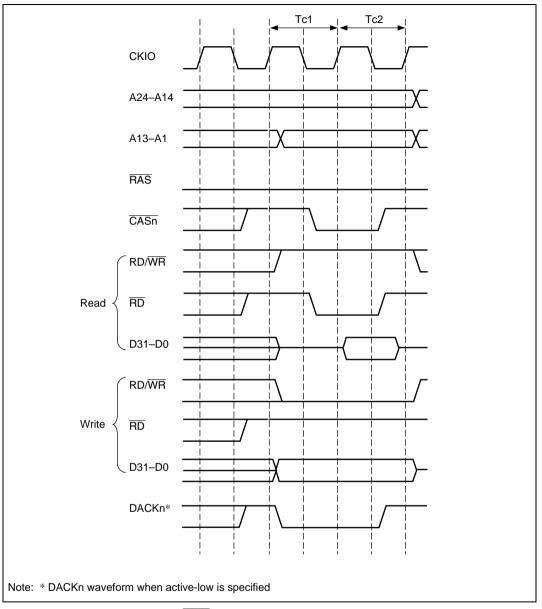

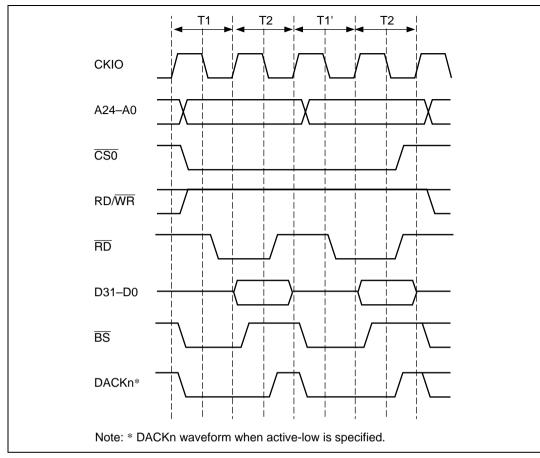

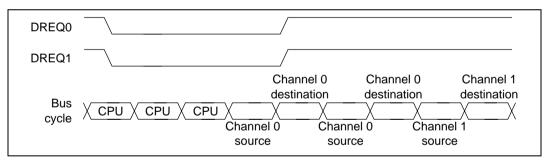

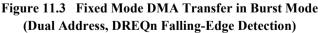

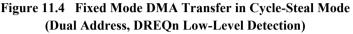

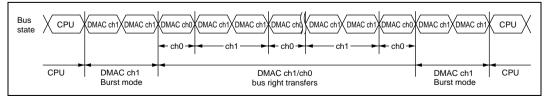

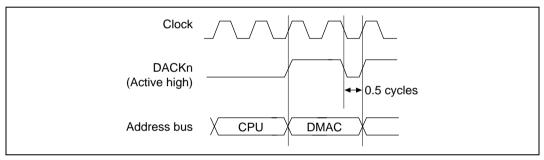

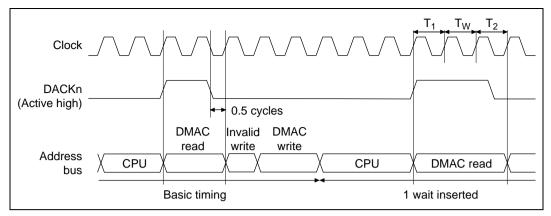

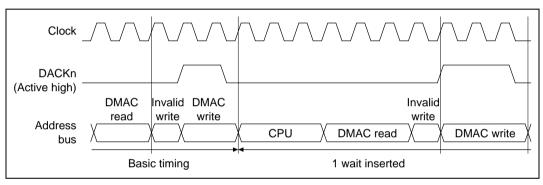

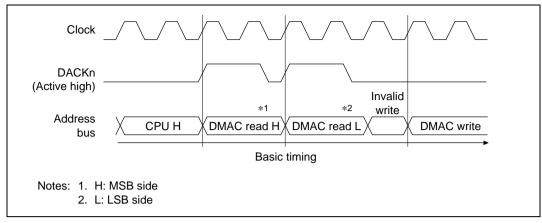

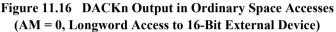

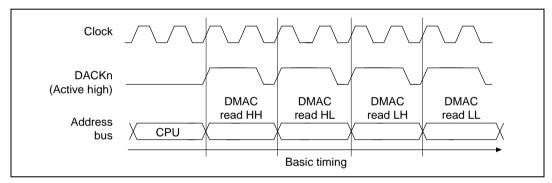

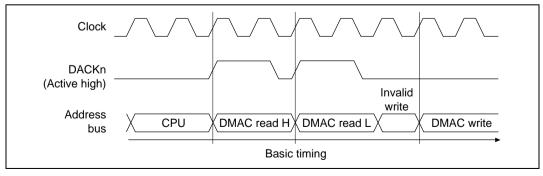

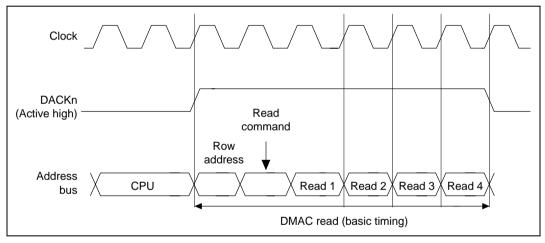

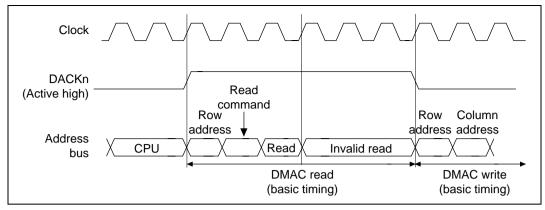

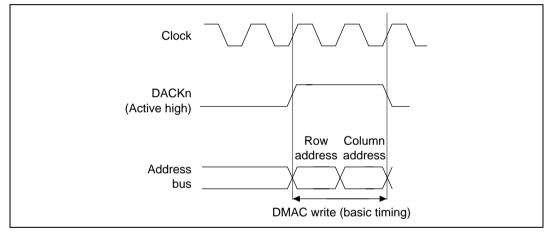

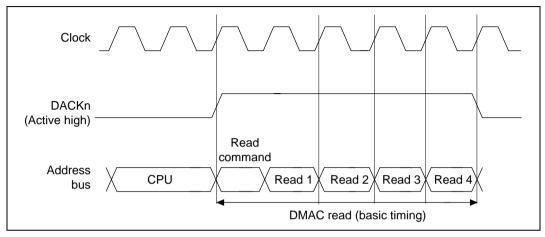

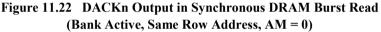

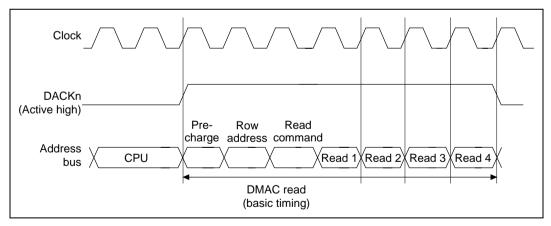

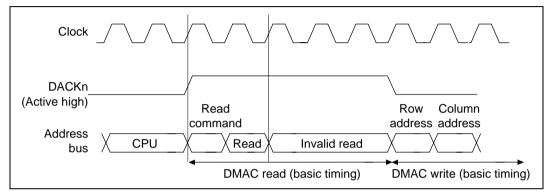

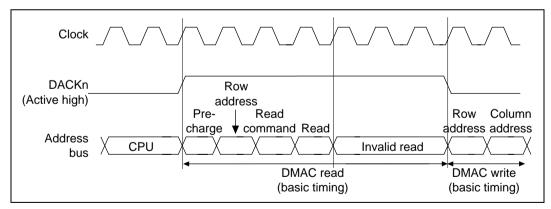

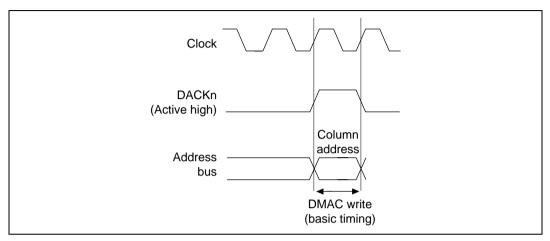

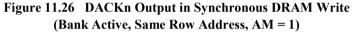

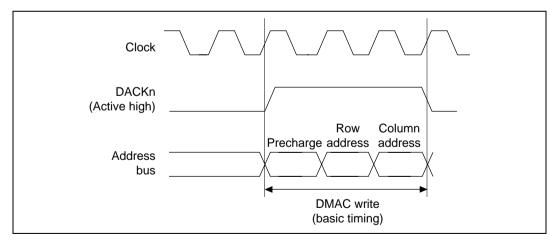

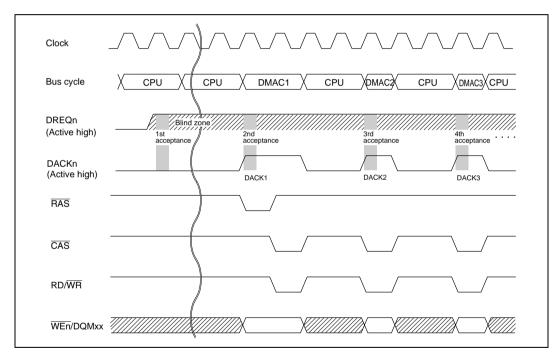

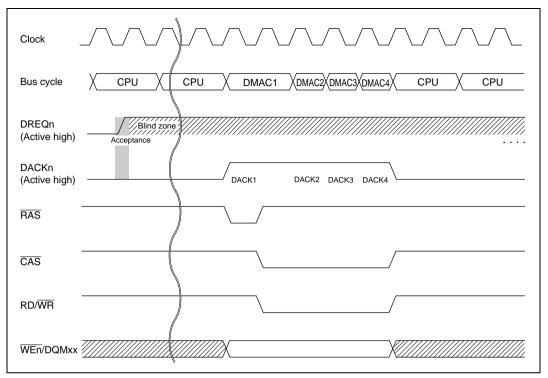

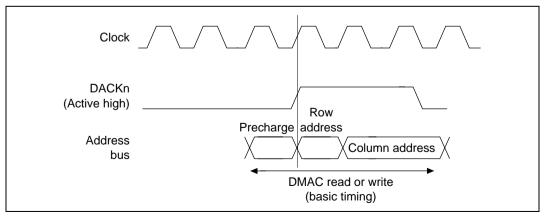

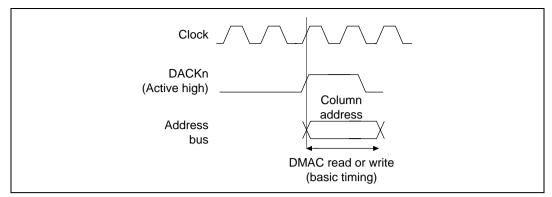

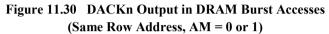

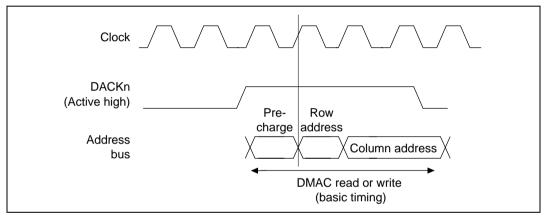

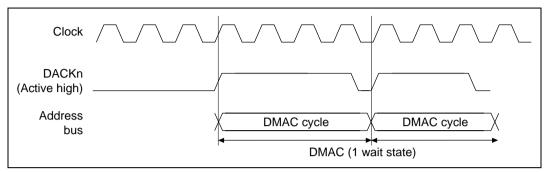

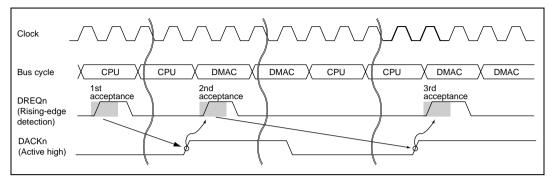

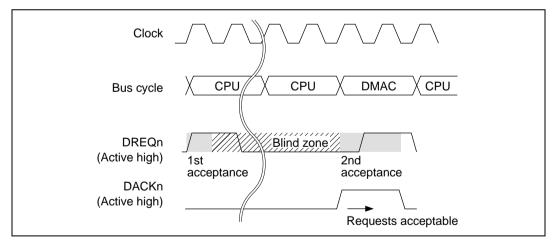

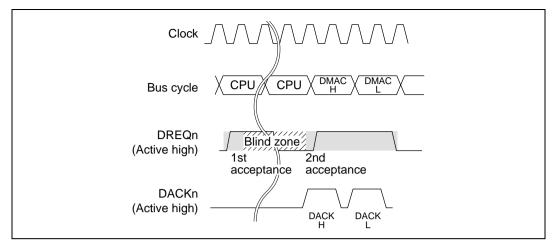

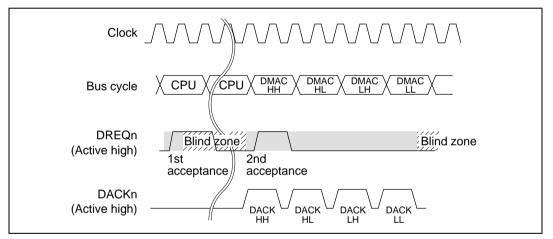

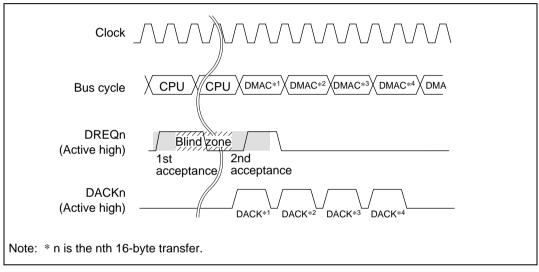

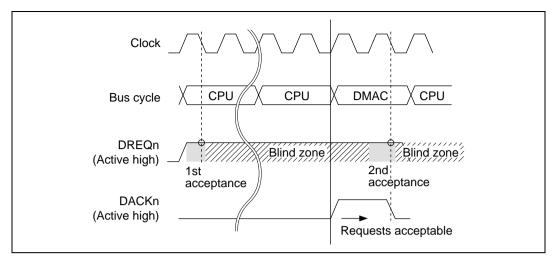

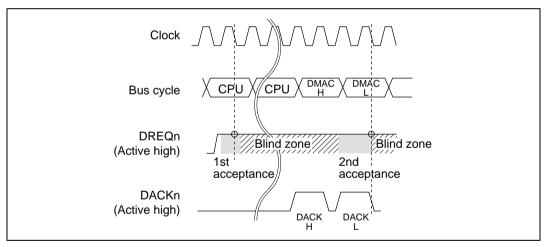

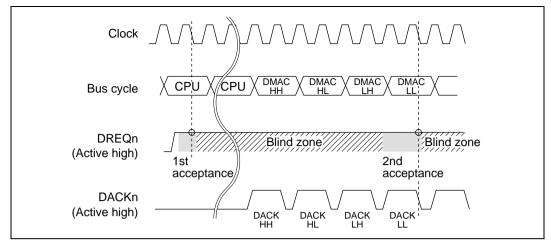

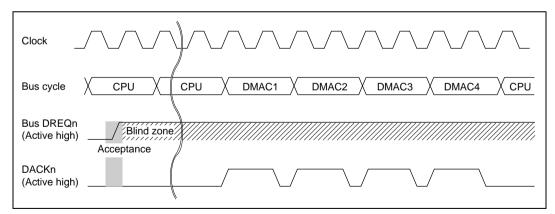

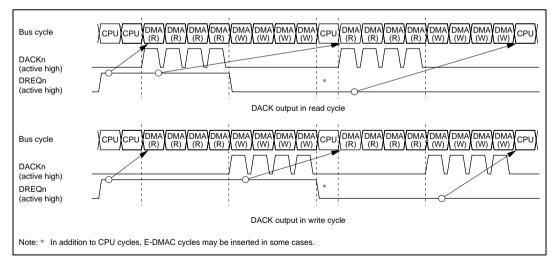

| 11.3.6 DMA Transfe                               | er 496 | Figure replaced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Request<br>Acknowledge Signal<br>Output Timing   |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Figure 11.13 Exampl<br>of DACKn Output<br>Timing | e      | DACKn<br>(Active high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                                                  |        | Address bus CPU DMAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

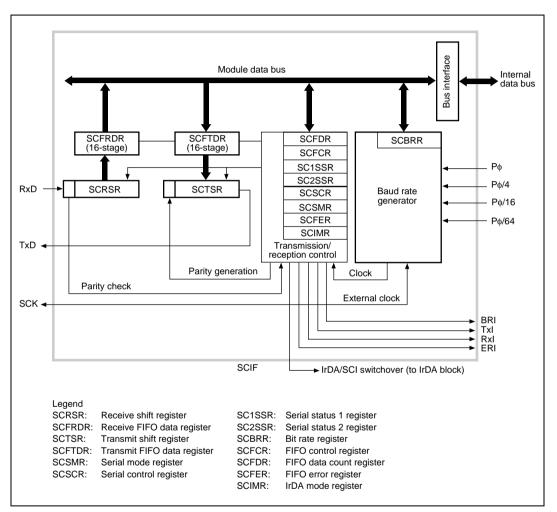

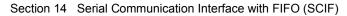

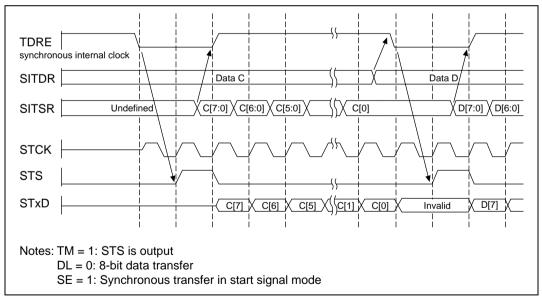

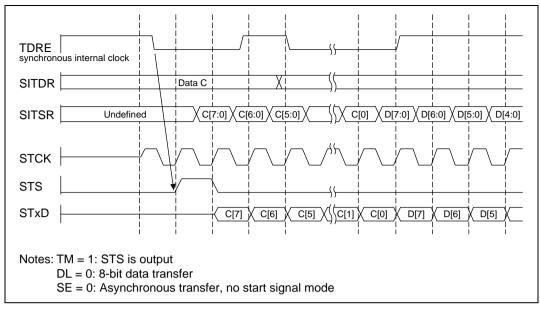

| 14.3.4 Operation in                              | 613    | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

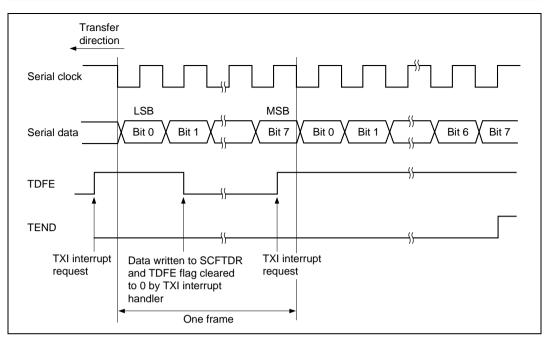

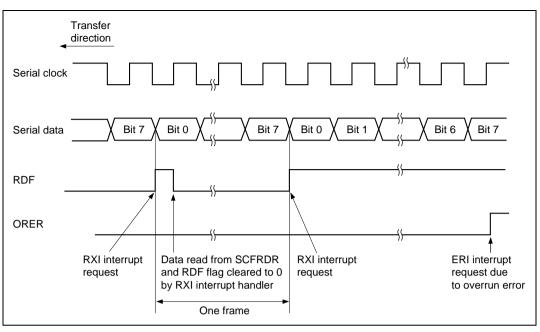

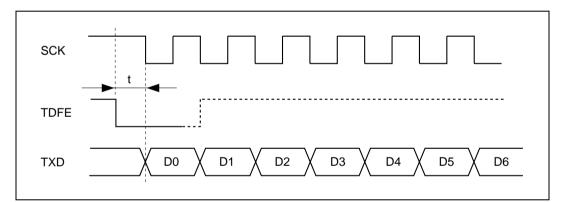

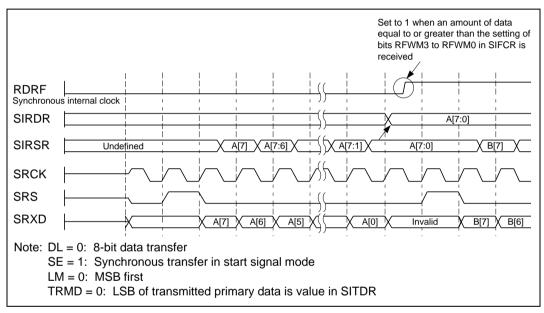

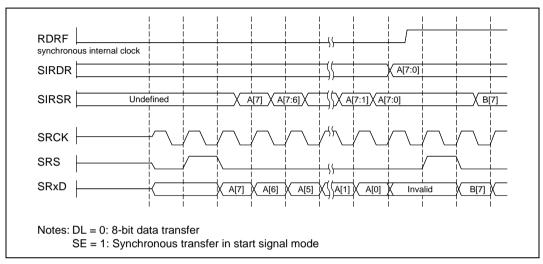

| Synchronous Mode                                 |        | In synchronous mode, the SCIF receives data in synchronization with the rise of the serial clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

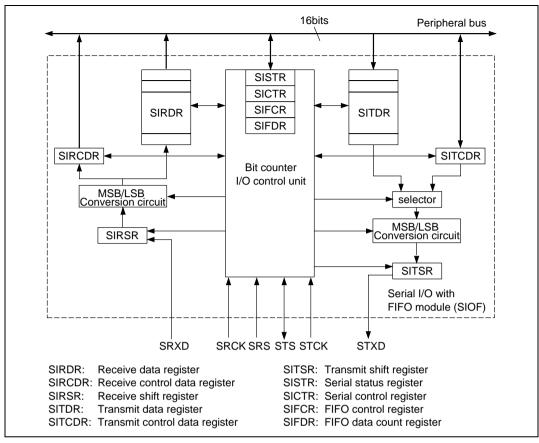

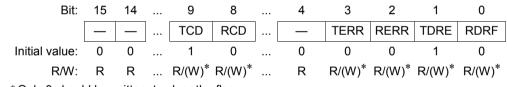

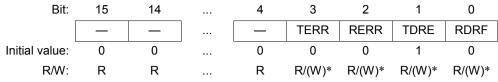

| 15.4 SIOF Interrupt<br>Sources and DMAC          | 663    | Description amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|                                                  |        | Each SIOF channel has four interrupt sources: the receive-overrun-<br>error interrupt (RERI0) request, transmit-underrun-error interrupt<br>(TERI0) request, receive-data-full interrupt/receive-control-data-<br>register-full interrupt (RDFI0) request, and transmit-data-empty<br>interrupt/transmit-control-data-register-empty interrupt (TDEI0)<br>request. Table 15.3 shows the interrupt sources and their relative<br>priorities. The RDFI0 and TDEI0 interrupts are enabled by the RIE,<br>RCIE, TIE, and TCIE bits, respectively, in SICTR. The RERI0 and<br>TERI0 interrupts cannot be disabled. |  |  |  |  |  |  |  |  |

| Table 15.3 SIOF                                  | 664    | Table amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Interrupt Sources                                |        | Interrupt DMAC<br>Source Description Activation Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                                                  |        | RERIO Receive overrun error (RERR) Not possible High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|                                                  |        | TERI0         Transmit underrun error (TERR)         Not possible         ↑                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|                                                  |        | RDFI0 Receive data register full (RDRF)/ Possible*<br>Receive Control Data Register Full (RCD) ↓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|                                                  |        | TDEI0 Transmit data register empty (TDRE)/ Possible* Low<br>Transmit Control Data Register Empty (TCD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Appendix C                                       | 904    | Table amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Table C.1 SH7616<br>Product Lineup               |        | Operating<br>Abbreviation Voltage Frequency Mark Code Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| -                                                |        | SH7616 3.3 V 62.5 MHz HD6417616SF PLQP0208KA-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|                                                  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

# Contents

| Secti | on 1                  | Overview                                                     | 1   |  |  |  |  |  |  |

|-------|-----------------------|--------------------------------------------------------------|-----|--|--|--|--|--|--|

| 1.1   | Featur                | res of SuperH Microcomputer with On-Chip Ethernet Controller | 1   |  |  |  |  |  |  |

| 1.2   | Block Diagram         |                                                              |     |  |  |  |  |  |  |

| 1.3   | Pin D                 | escription                                                   |     |  |  |  |  |  |  |

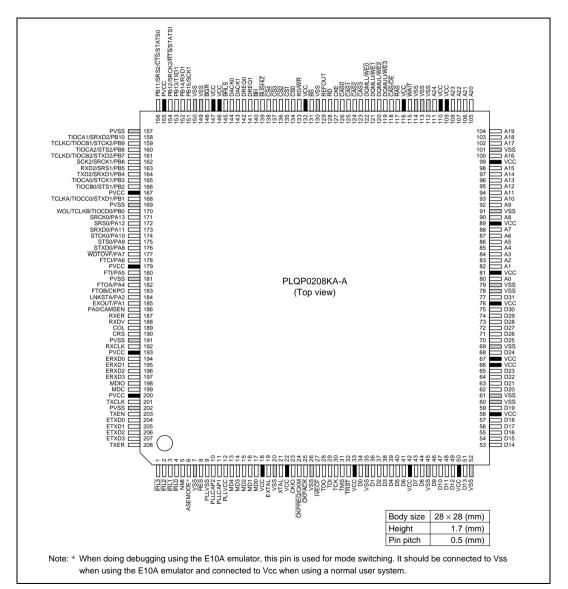

|       | 1.3.1 Pin Arrangement |                                                              |     |  |  |  |  |  |  |

|       | 1.3.2                 | Pin Functions                                                | 15  |  |  |  |  |  |  |

|       | 1.3.3                 | Pin Multiplexing                                             | 21  |  |  |  |  |  |  |

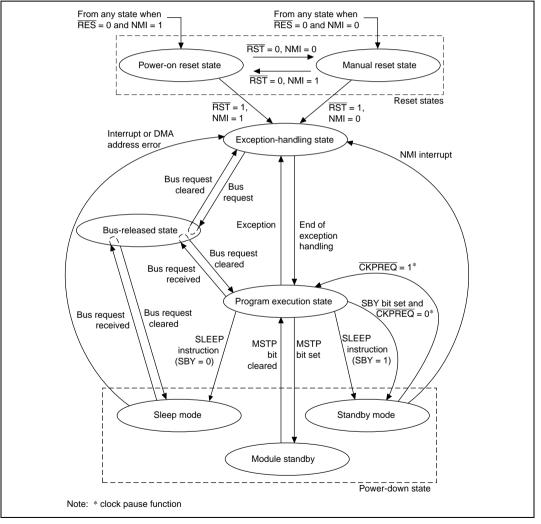

| 1.4   | Proce                 | ssing States                                                 | 27  |  |  |  |  |  |  |

| Secti | on 2                  | CPU                                                          | 31  |  |  |  |  |  |  |

| 2.1   |                       | ter Configuration                                            | 31  |  |  |  |  |  |  |

|       | 2.1.1                 | General Registers                                            | 31  |  |  |  |  |  |  |

|       | 2.1.2                 | Control Registers                                            | 33  |  |  |  |  |  |  |

|       | 2.1.3                 | System Registers                                             | 36  |  |  |  |  |  |  |

|       | 2.1.4                 | DSP Registers                                                | 37  |  |  |  |  |  |  |

|       | 2.1.5                 | Notes on Guard Bits and Overflow Treatment                   | 40  |  |  |  |  |  |  |

|       | 2.1.6                 | Initial Values of Registers                                  | 40  |  |  |  |  |  |  |

| 2.2   | Data Formats          |                                                              |     |  |  |  |  |  |  |

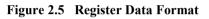

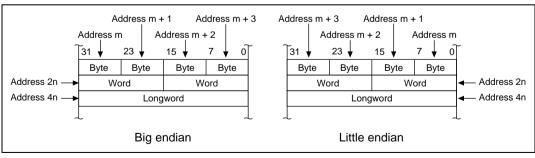

|       | 2.2.1                 | Data Format in Registers                                     | 41  |  |  |  |  |  |  |

|       | 2.2.2                 | Data Formats in Memory                                       | 41  |  |  |  |  |  |  |

|       | 2.2.3                 | Immediate Data Format                                        | 42  |  |  |  |  |  |  |

|       | 2.2.4                 | DSP Type Data Formats                                        | 42  |  |  |  |  |  |  |

|       | 2.2.5                 | DSP Type Instructions and Data Formats                       | 44  |  |  |  |  |  |  |

| 2.3   | CPU (                 | Core Instruction Features                                    | 48  |  |  |  |  |  |  |

| 2.4   | Instru                | ction Formats                                                | 52  |  |  |  |  |  |  |

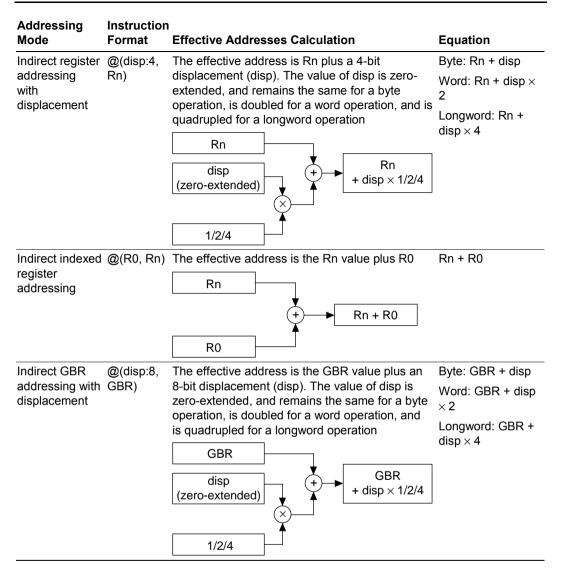

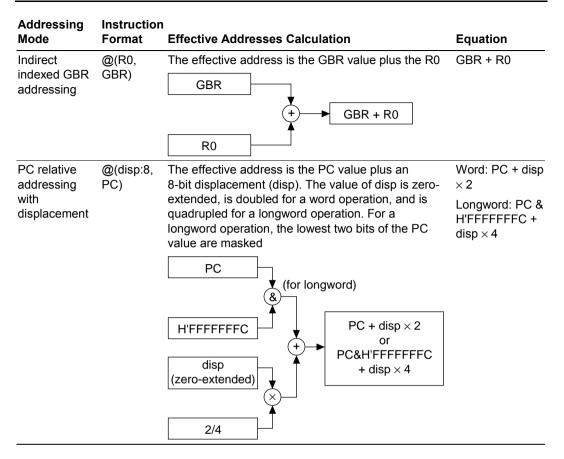

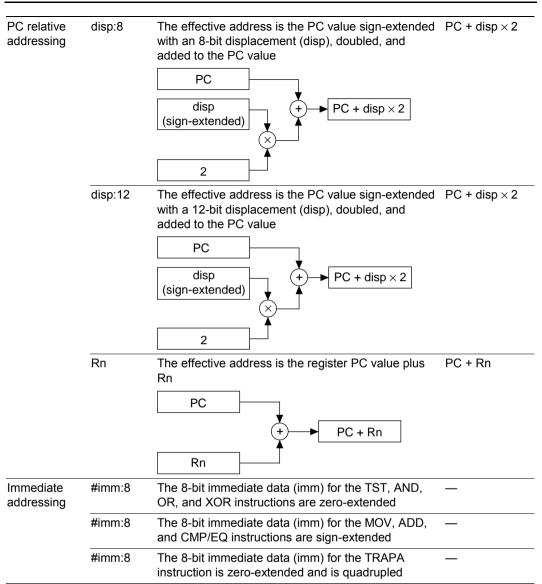

|       | 2.4.1                 | CPU Instruction Addressing Modes                             | 52  |  |  |  |  |  |  |

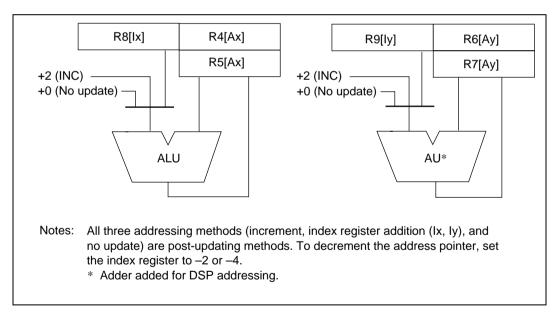

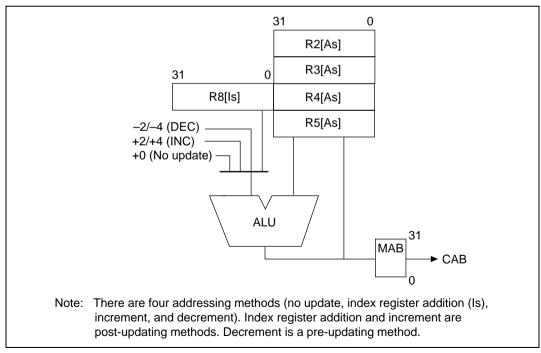

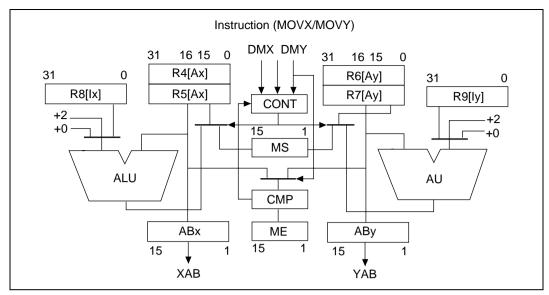

|       | 2.4.2                 | DSP Data Addressing                                          | 56  |  |  |  |  |  |  |

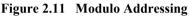

|       | 2.4.3                 | Instruction Formats for CPU Instructions                     | 62  |  |  |  |  |  |  |

|       | 2.4.4                 | Instruction Formats for DSP Instructions                     | 66  |  |  |  |  |  |  |

| 2.5   | Instru                | ction Set                                                    | 72  |  |  |  |  |  |  |

|       | 2.5.1                 | CPU Instruction Set                                          | 73  |  |  |  |  |  |  |

|       | 2.5.2                 | DSP Data Transfer Instruction Set                            | 89  |  |  |  |  |  |  |

|       | 2.5.3                 | DSP Operation Instruction Set                                | 93  |  |  |  |  |  |  |

|       | 2.5.4                 | Various Operation Instructions                               | 96  |  |  |  |  |  |  |

| 2.6   | Usage                 | Notes                                                        | 105 |  |  |  |  |  |  |

|       | 2.6.1                 | When not using DSP instructions                              | 105 |  |  |  |  |  |  |

Rev. 2.00 Mar 09, 2006 page xi of xxvi

|       | 2.6.2   | When executing a combination of double-precision multiplication or |     |

|-------|---------|--------------------------------------------------------------------|-----|

|       |         | double-precision product-sum operation (CPU instruction) and DSP   |     |

|       |         | computing instruction                                              | 105 |

| Secti | ion 3   | Oscillator Circuits and Operating Modes                            | 107 |

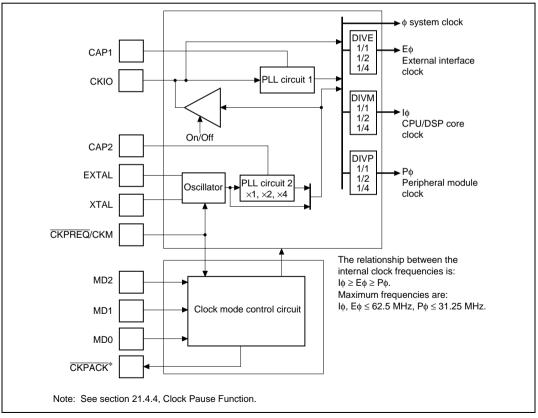

| 3.1   |         | iew                                                                |     |

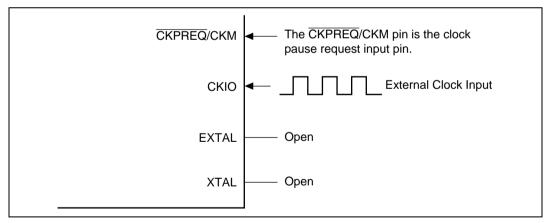

| 3.2   | On-Cl   | nip Clock Pulse Generator and Operating Modes                      | 107 |

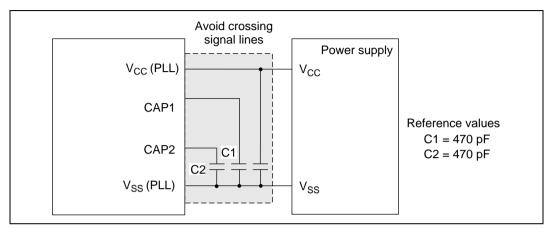

|       | 3.2.1   | Clock Pulse Generator                                              | 107 |

|       | 3.2.2   | Clock Operating Mode Settings                                      | 109 |

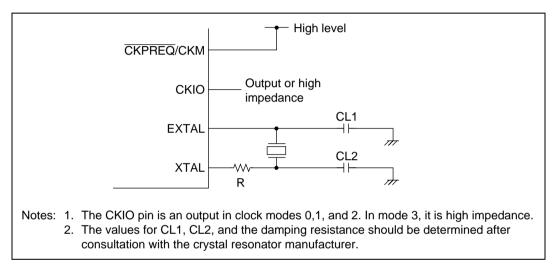

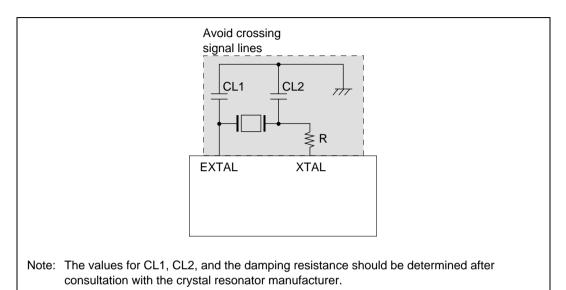

|       | 3.2.3   | Connecting a Crystal Resonator                                     | 112 |

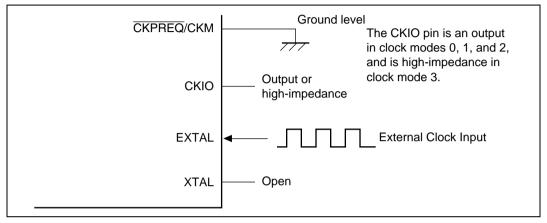

|       | 3.2.4   | External Clock Input                                               | 113 |

|       | 3.2.5   | Operating Frequency Selection by Register                          | 114 |

|       | 3.2.6   | Clock Modes and Frequency Ranges                                   | 122 |

|       | 3.2.7   | Notes on Board Design                                              | 123 |

| 3.3   | Bus W   | Vidth of the CS0 Area                                              | 124 |

| Secti | ion 4   | Exception Handling                                                 | 125 |

| 4.1   |         | iew                                                                |     |

|       | 4.1.1   | Types of Exception Handling and Priority Order                     | 125 |

|       | 4.1.2   | Exception Handling Operations                                      |     |

|       | 4.1.3   | Exception Vector Table                                             | 128 |

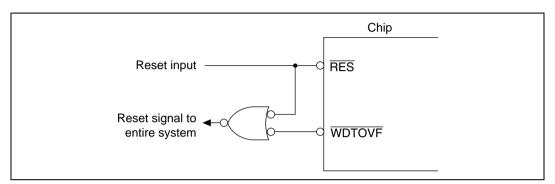

| 4.2   | Resets  |                                                                    | 131 |

|       | 4.2.1   | Types of Resets                                                    | 131 |

|       | 4.2.2   | Power-On Reset                                                     | 131 |

|       | 4.2.3   | Manual Reset                                                       | 132 |

| 4.3   | Addre   | ss Errors                                                          | 132 |

|       | 4.3.1   | Sources of Address Errors                                          | 132 |

|       | 4.3.2   | Address Error Exception Handling                                   | 134 |

| 4.4   | Interru | 1pts                                                               |     |

|       | 4.4.1   | Interrupt Sources                                                  | 135 |

|       | 4.4.2   | Interrupt Priority Levels                                          | 136 |

|       | 4.4.3   | Interrupt Exception Handling                                       | 136 |

| 4.5   | Excep   | tions Triggered by Instructions                                    | 137 |

|       | 4.5.1   | Instruction-Triggered Exception Types                              | 137 |

|       | 4.5.2   | Trap Instructions                                                  | 137 |

|       | 4.5.3   | Illegal Slot Instructions                                          | 138 |

|       | 4.5.4   | General Illegal Instructions                                       | 138 |

| 4.6   | When    | Exception Sources Are Not Accepted                                 |     |

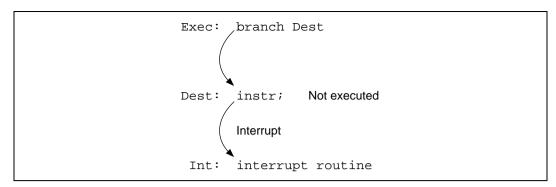

|       | 4.6.1   | Immediately after a Delayed Branch Instruction                     | 139 |

|       | 4.6.2   | Immediately after an Interrupt-Disabled Instruction                | 139 |

Rev. 2.00 Mar 09, 2006 page xii of xxvi

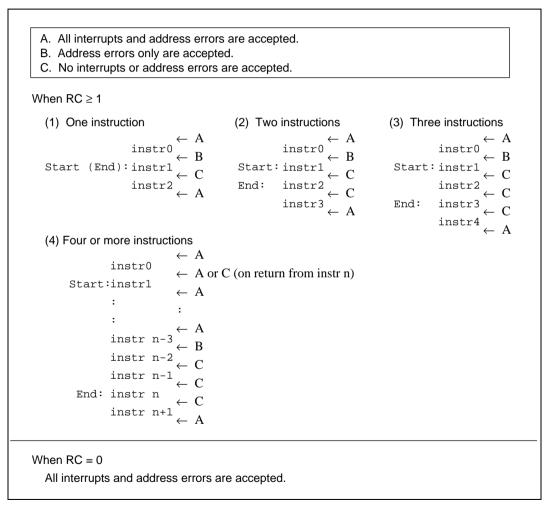

|       | 4.6.3   | Instructions in Repeat Loops                                          | 140 |

|-------|---------|-----------------------------------------------------------------------|-----|

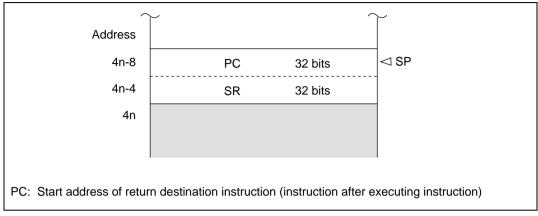

| 4.7   | Stack S | Status after Exception Handling                                       | 141 |

| 4.8   | Usage I | Notes                                                                 | 142 |

|       | 4.8.1   | Value of Stack Pointer (SP)                                           | 142 |

|       | 4.8.2   | Value of Vector Base Register (VBR)                                   | 142 |

|       | 4.8.3   | Address Errors Caused by Stacking of Address Error Exception Handling | 142 |

|       | 4.8.4   | Manual Reset during Register Access                                   | 142 |

|       |         |                                                                       |     |

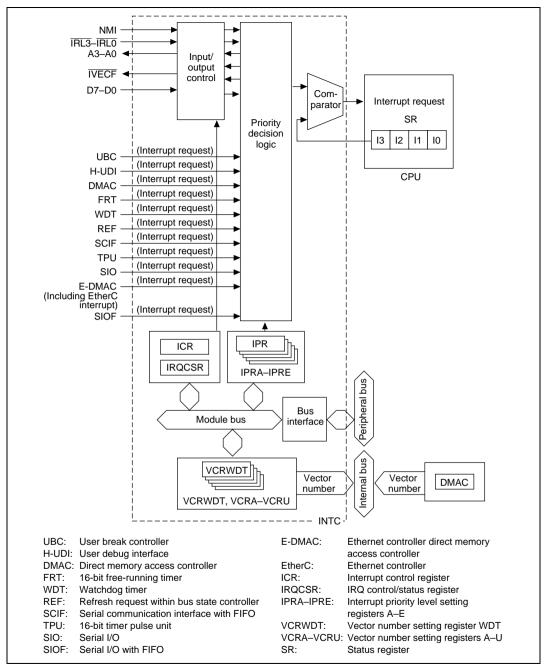

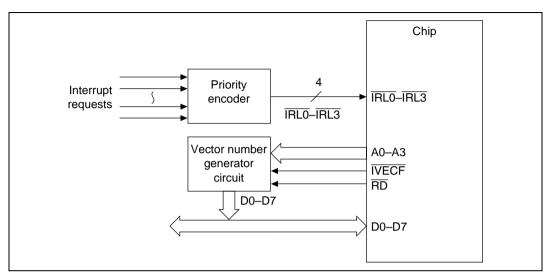

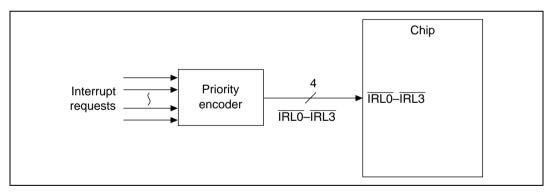

| Secti | on 5    | Interrupt Controller (INTC)                                           | 143 |

| 5.1   | Overvi  | ew                                                                    |     |

|       | 5.1.1   | Features                                                              |     |

|       | 5.1.2   | Block Diagram                                                         |     |

|       | 5.1.3   | Pin Configuration                                                     |     |

|       | 5.1.4   | Register Configuration                                                |     |

| 5.2   |         | pt Sources                                                            | 146 |

|       | 5.2.1   | NMI Interrupt                                                         |     |

|       | 5.2.2   | User Break Interrupt                                                  |     |

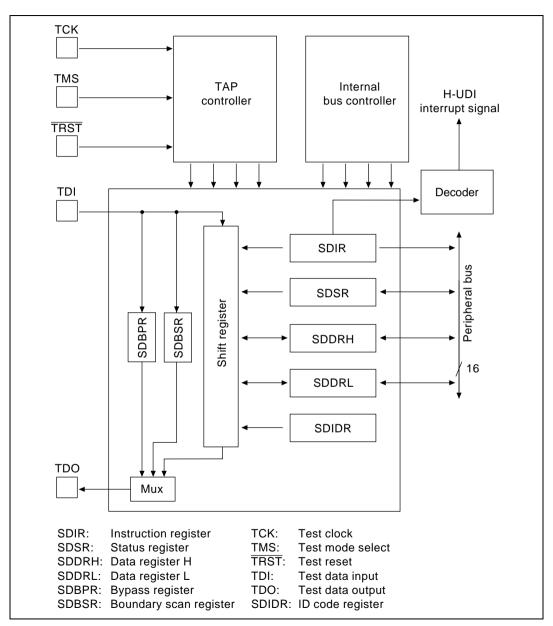

|       | 5.2.3   | H-UDI Interrupt                                                       |     |

|       | 5.2.4   | IRL Interrupts                                                        | 147 |

|       | 5.2.5   | IRQ Interrupts                                                        |     |

|       | 5.2.6   | On-chip Peripheral Module Interrupts                                  |     |

|       | 5.2.7   | Interrupt Exception Vectors and Priority Order                        |     |

| 5.3   | Registe | er Descriptions                                                       |     |

|       | 5.3.1   | Interrupt Priority Level Setting Register A (IPRA)                    |     |

|       | 5.3.2   | Interrupt Priority Level Setting Register B (IPRB)                    |     |

|       | 5.3.3   | Interrupt Priority Level Setting Register C (IPRC)                    |     |

|       | 5.3.4   | Interrupt Priority Level Setting Register D (IPRD)                    |     |

|       | 5.3.5   | Interrupt Priority Level Setting Register E (IPRE)                    |     |

|       | 5.3.6   | Vector Number Setting Register WDT (VCRWDT)                           |     |

|       | 5.3.7   | Vector Number Setting Register A (VCRA)                               |     |

|       | 5.3.8   | Vector Number Setting Register B (VCRB)                               |     |

|       | 5.3.9   | Vector Number Setting Register C (VCRC)                               | 166 |

|       | 5.3.10  | Vector Number Setting Register D (VCRD)                               |     |

|       | 5.3.11  | Vector Number Setting Register E (VCRE)                               |     |

|       | 5.3.12  | Vector Number Setting Register F (VCRF)                               | 169 |

|       | 5.3.13  | Vector Number Setting Register G (VCRG)                               |     |

|       | 5.3.14  | Vector Number Setting Register H (VCRH)                               |     |

|       | 5.3.15  | Vector Number Setting Register I (VCRI)                               |     |

|       |         | Vector Number Setting Register J (VCRJ)                               |     |

|       | 5.3.17  | Vector Number Setting Register K (VCRK)                               | 174 |

Rev. 2.00 Mar 09, 2006 page xiii of xxvi

|      | 5.3.18  | Vector Number Setting Register L (VCRL)                              | 175 |

|------|---------|----------------------------------------------------------------------|-----|

|      |         | Vector Number Setting Register M (VCRM)                              |     |

|      |         | Vector Number Setting Register N (VCRN)                              |     |

|      | 5.3.21  | Vector Number Setting Register O (VCRO)                              | 178 |

|      | 5.3.22  | Vector Number Setting Register P (VCRP)                              | 179 |

|      | 5.3.23  | Vector Number Setting Register Q (VCRQ)                              | 180 |

|      | 5.3.24  | Vector Number Setting Register R (VCRR)                              | 181 |

|      | 5.3.25  | Vector Number Setting Register S (VCRS)                              | 182 |

|      | 5.3.26  | Vector Number Setting Register T (VCRT)                              | 183 |

|      | 5.3.27  | Vector Number Setting Register U (VCRU)                              | 184 |

|      | 5.3.28  | Interrupt Control Register (ICR)                                     | 187 |

|      |         | IRQ Control/Status Register (IRQCSR)                                 |     |

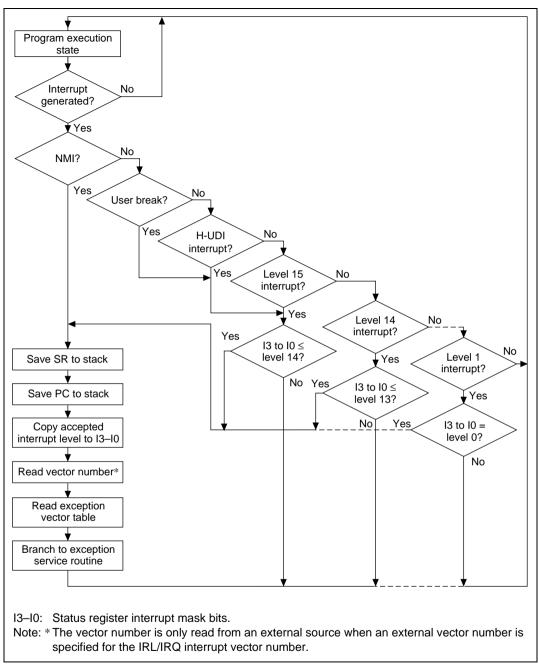

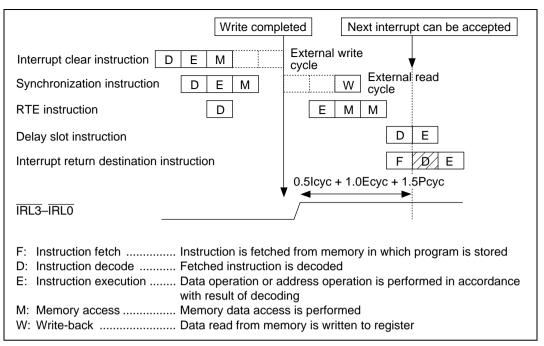

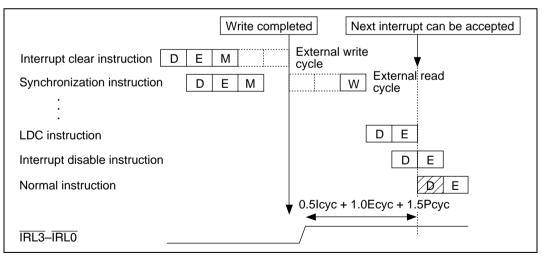

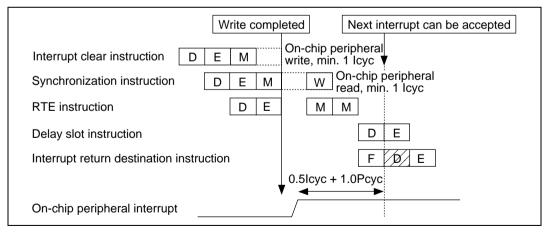

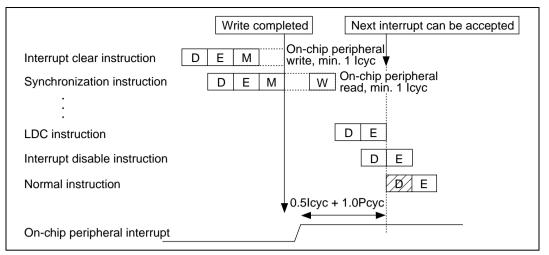

| 5.4  | Interru | pt Operation                                                         | 190 |

|      | 5.4.1   | Interrupt Sequence                                                   | 190 |

|      | 5.4.2   | Stack State after Interrupt Exception Handling                       | 192 |

| 5.5  | Interru | pt Response Time                                                     | 192 |

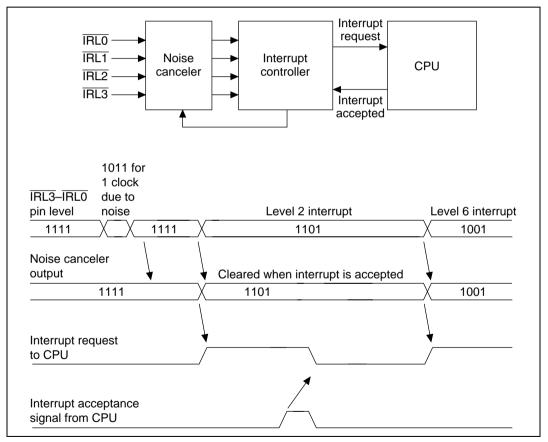

| 5.6  | Sampli  | ng of Pins IRL3–IRL0                                                 | 194 |

| 5.7  | Usage   | Notes                                                                | 195 |

|      |         |                                                                      |     |

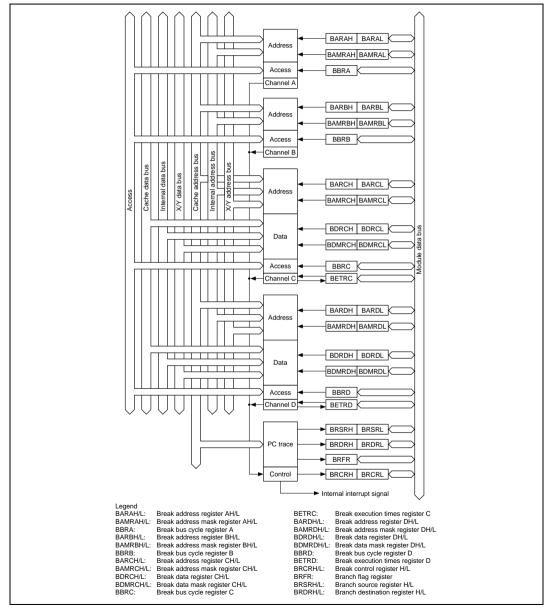

| Sect |         | User Break Controller (UBC)                                          |     |

| 6.1  | Overvi  | ew                                                                   |     |

|      | 6.1.1   | Features                                                             |     |

|      | 6.1.2   | Block Diagram                                                        |     |

|      | 6.1.3   | Register Configuration                                               |     |

| 6.2  | Registe | er Descriptions                                                      |     |

|      | 6.2.1   | Break Address Register A (BARA)                                      |     |

|      | 6.2.2   | Break Address Mask Register A (BAMRA)                                |     |

|      | 6.2.3   | Break Bus Cycle Register A (BBRA)                                    |     |

|      | 6.2.4   | Break Address Register B (BARB)                                      |     |

|      | 6.2.5   | Break Address Mask Register B (BAMRB)                                |     |

|      | 6.2.6   | Break Bus Cycle Register B (BBRB)                                    |     |

|      | 6.2.7   | Break Address Register C (BARC)                                      |     |

|      | 6.2.8   | Break Address Mask Register C (BAMRC)                                |     |

|      | 6.2.9   | Break Data Register C (BDRC)                                         |     |

|      | 6.2.10  | Break Data Mask Register C (BDMRC)                                   |     |

|      | 6.2.11  | Break Bus Cycle Register C (BBRC)                                    |     |

|      | 6.2.12  | Break Execution Times Register C (BETRC)                             |     |

|      |         | Dreads Addrease Desister D (DADD)                                    | 210 |

|      | 6.2.13  | Break Address Register D (BARD)                                      |     |

|      | 6.2.14  | Break Address Mask Register D (BARD)<br>Break Data Register D (BDRD) | 220 |

|       | 6.2.16  | Break Data Mask Register D (BDMRD)            | 223 |

|-------|---------|-----------------------------------------------|-----|

|       | 6.2.17  | Break Bus Cycle Register D (BBRD)             | 225 |

|       | 6.2.18  | Break Execution Times Register D (BETRD)      | 226 |

|       | 6.2.19  | Break Control Register (BRCR)                 | 227 |

|       | 6.2.20  | Branch Flag Registers (BRFR)                  | 233 |

|       | 6.2.21  | Branch Source Registers (BRSR)                |     |

|       | 6.2.22  | Branch Destination Registers (BRDR)           | 235 |

| 6.3   | Operati | on                                            | 236 |

|       | 6.3.1   | User Break Operation Sequence                 | 236 |

|       | 6.3.2   | Instruction Fetch Cycle Break                 | 237 |

|       | 6.3.3   | Data Access Cycle Break                       | 238 |

|       | 6.3.4   | Saved Program Counter (PC) Value              | 239 |

|       | 6.3.5   | X Memory Bus or Y Memory Bus Cycle Break      |     |

|       | 6.3.6   | Sequential Break                              |     |

|       | 6.3.7   | PC Traces                                     |     |

|       | 6.3.8   | Examples of Use                               | 243 |

|       | 6.3.9   | Usage Notes                                   |     |

|       |         |                                               |     |

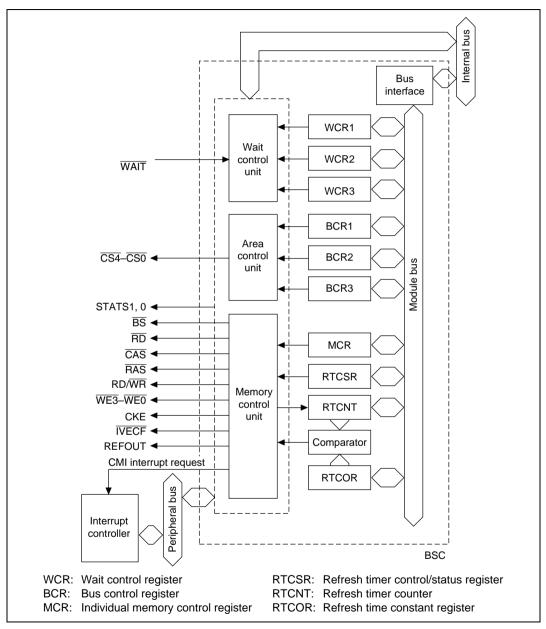

| Secti | ion 7 l | Bus State Controller (BSC)                    | 249 |

| 7.1   | Overvie | 2W                                            | 249 |

|       | 7.1.1   | Features                                      | 249 |

|       | 7.1.2   | Block Diagram                                 | 251 |

|       | 7.1.3   | Pin Configuration                             | 252 |

|       | 7.1.4   | Register Configuration                        |     |

|       | 7.1.5   | Address Map                                   | 255 |

| 7.2   | Registe | r Descriptions                                |     |

|       | 7.2.1   | Bus Control Register 1 (BCR1)                 |     |

|       | 7.2.2   | Bus Control Register 2 (BCR2)                 |     |

|       | 7.2.3   | Bus Control Register 3 (BCR3)                 | 261 |

|       | 7.2.4   | Wait Control Register 1 (WCR1)                |     |

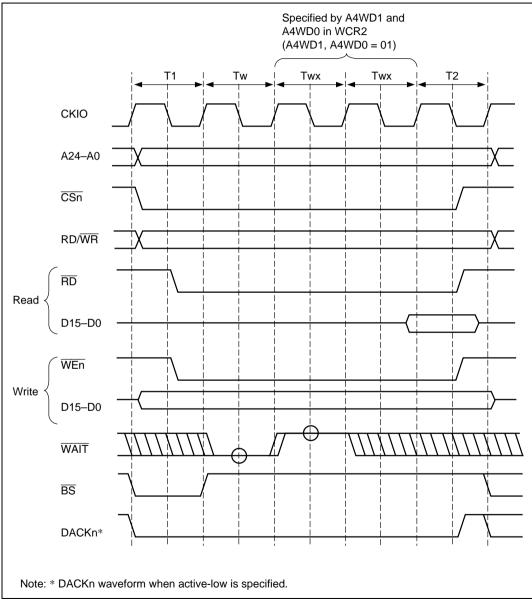

|       | 7.2.5   | Wait Control Register 2 (WCR2)                | 265 |

|       | 7.2.6   | Wait Control Register 3 (WCR3)                |     |

|       | 7.2.7   | Individual Memory Control Register (MCR)      | 268 |

|       | 7.2.8   | Refresh Timer Control/Status Register (RTCSR) | 276 |

|       | 7.2.9   | Refresh Timer Counter (RTCNT)                 | 278 |

|       | 7.2.10  | Refresh Time Constant Register (RTCOR)        |     |

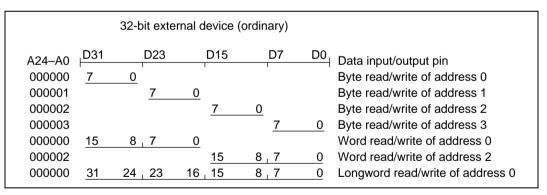

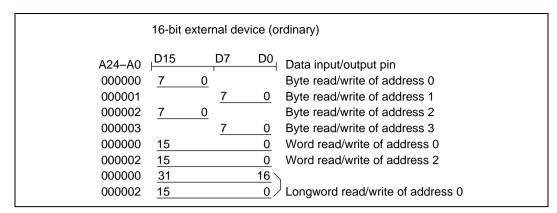

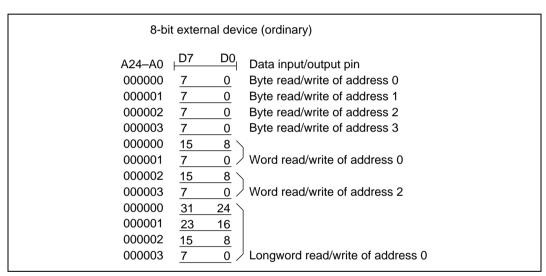

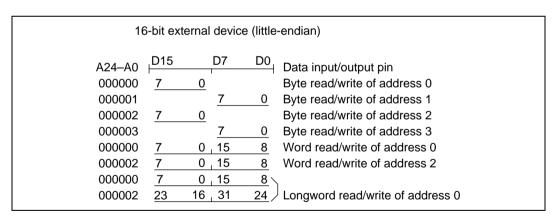

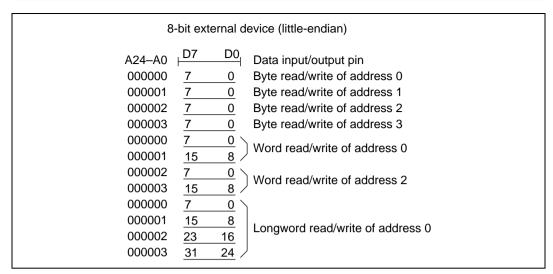

| 7.3   |         | Size and Data Alignment                       |     |

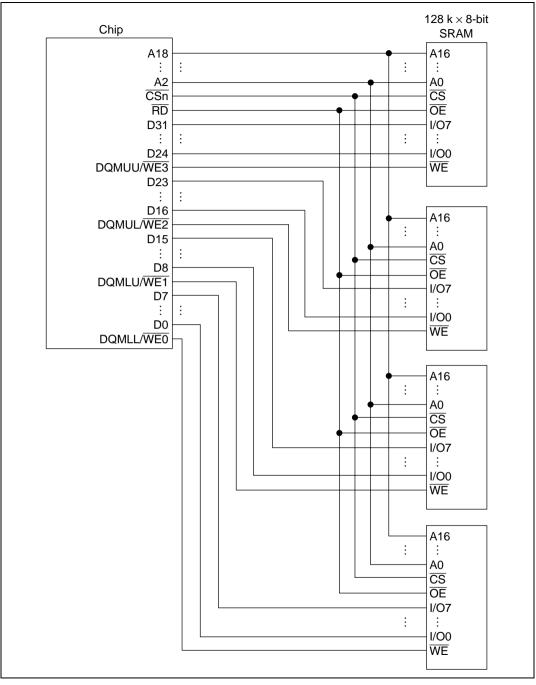

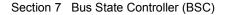

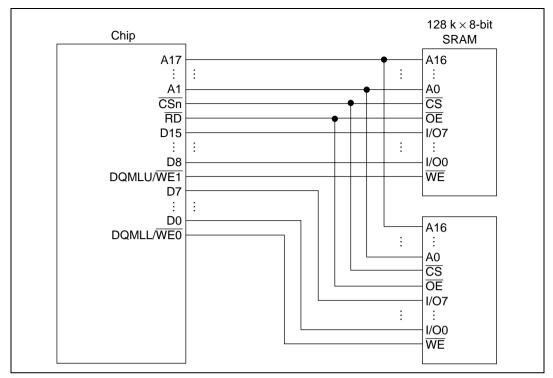

|       | 7.3.1   | Connection to Ordinary Devices                |     |

|       | 7.3.2   | Connection to Little-Endian Devices           | 280 |

| 7.4   | Access  | ing Ordinary Space                            |     |

|       |         |                                               |     |

Rev. 2.00 Mar 09, 2006 page xv of xxvi

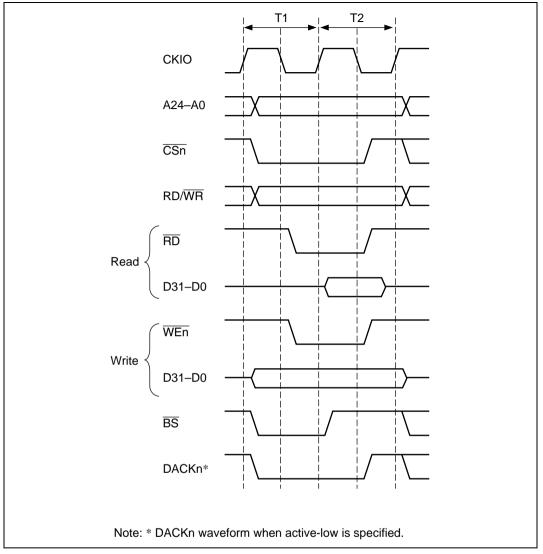

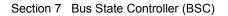

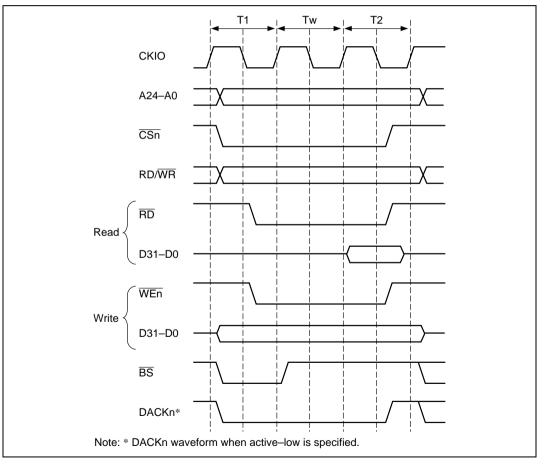

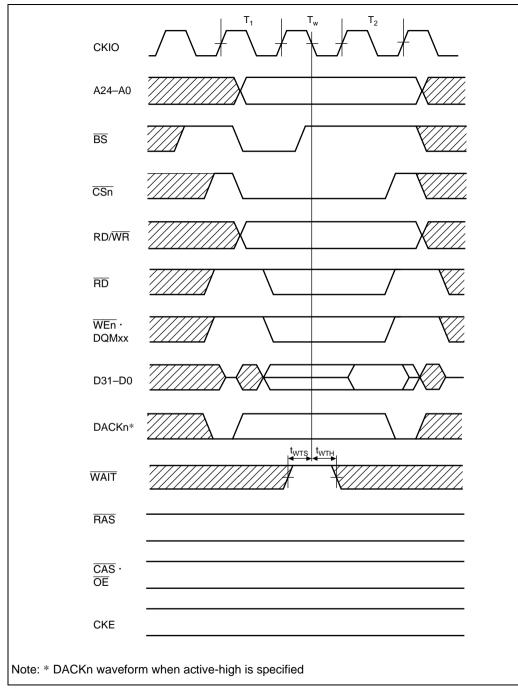

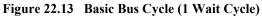

|      | 7.4.1    | Basic Timing                                                     | . 282 |

|------|----------|------------------------------------------------------------------|-------|

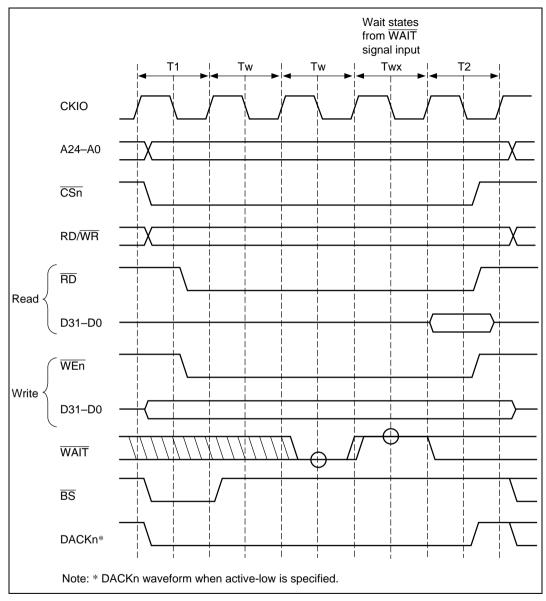

|      | 7.4.2    | Wait State Control.                                              | . 287 |

|      | 7.4.3    | CS Assertion Period Extension                                    | . 291 |

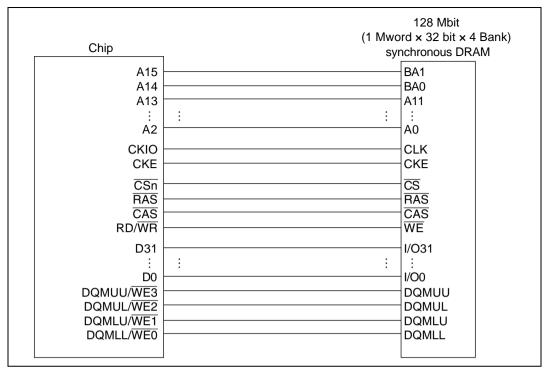

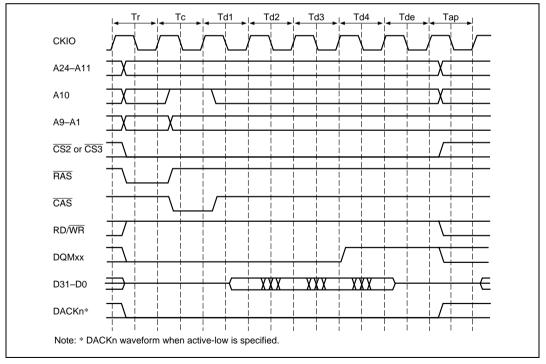

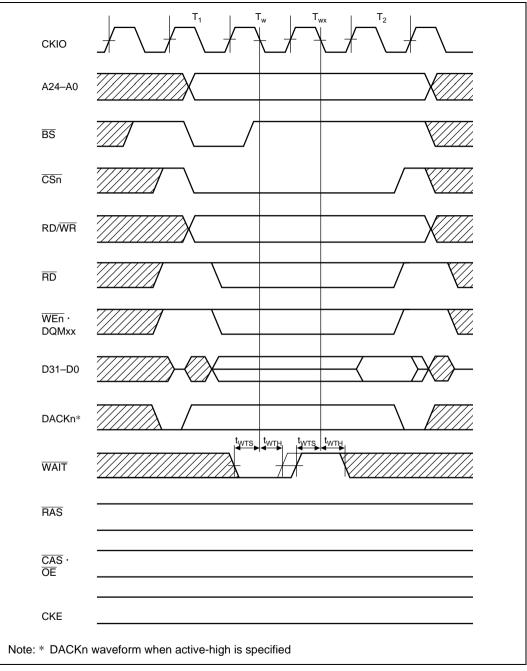

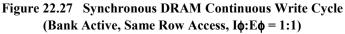

| 7.5  | Synchr   | onous DRAM Interface                                             | . 292 |

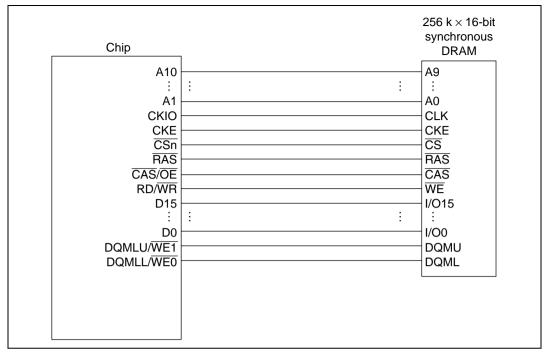

|      | 7.5.1    | Synchronous DRAM Direct Connection                               | . 292 |

|      | 7.5.2    | Address Multiplexing                                             | . 294 |

|      | 7.5.3    | Burst Reads                                                      | . 296 |

|      | 7.5.4    | Single Reads                                                     | . 301 |

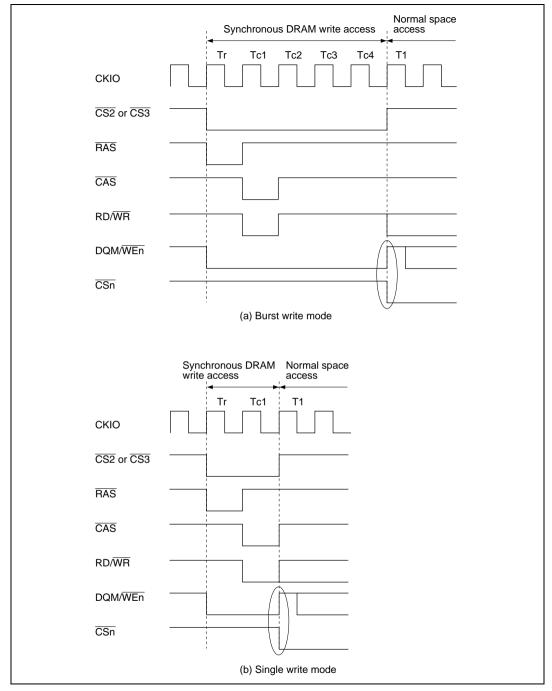

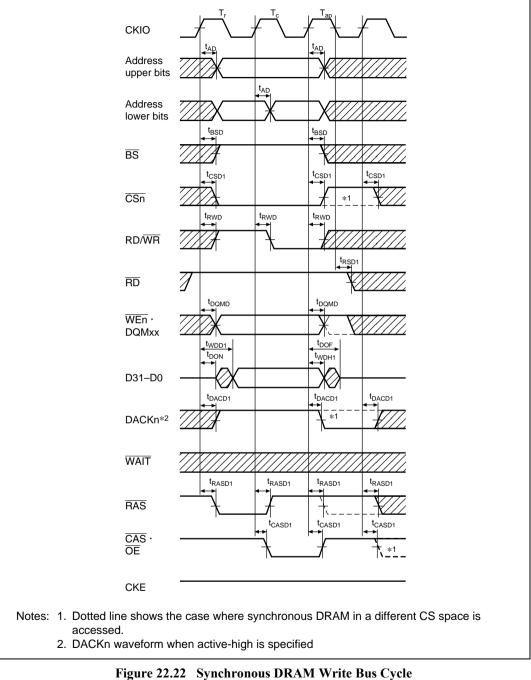

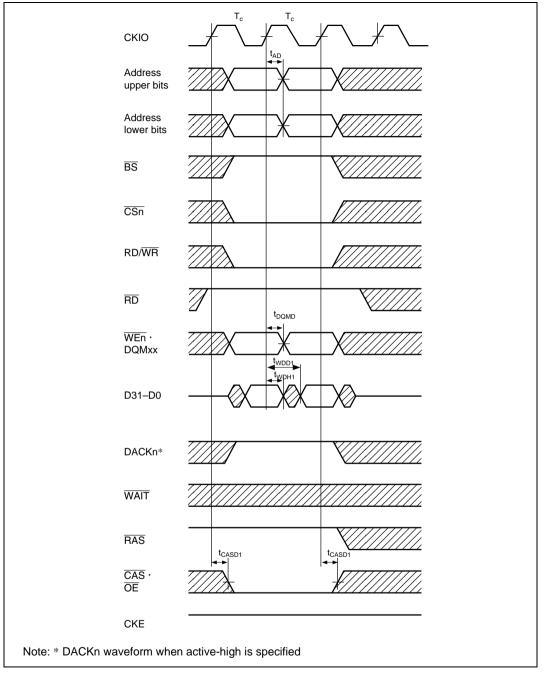

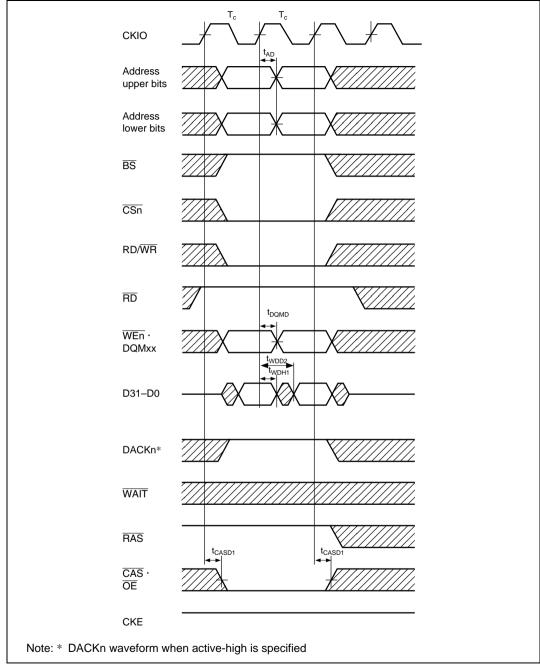

|      | 7.5.5    | Single Writes                                                    | . 303 |

|      | 7.5.6    | Burst Write Mode                                                 | . 304 |

|      | 7.5.7    | Bank Active Function                                             | . 306 |

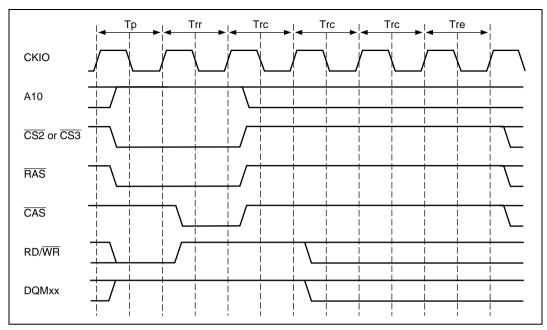

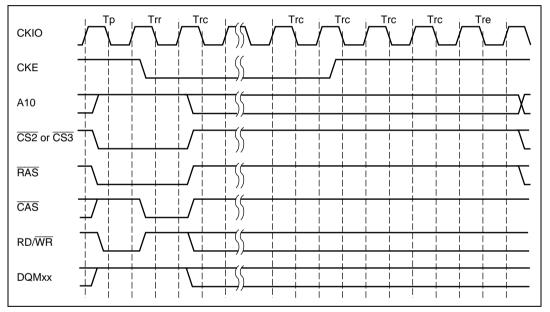

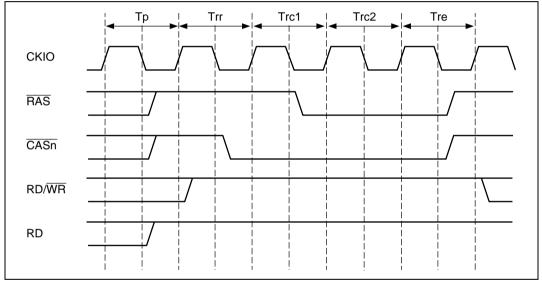

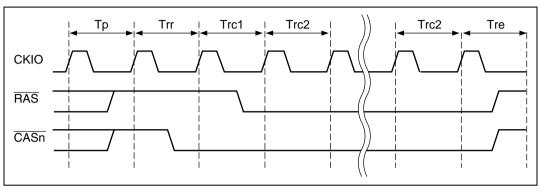

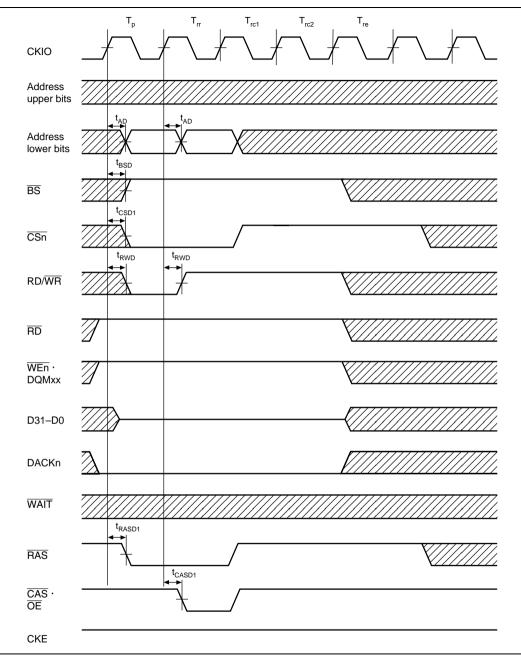

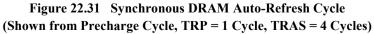

|      | 7.5.8    | Refreshes                                                        | . 317 |

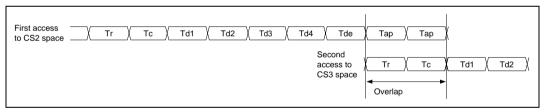

|      | 7.5.9    | Overlap Between Auto Precharge Cycle (Tap) and Next Access       | . 320 |

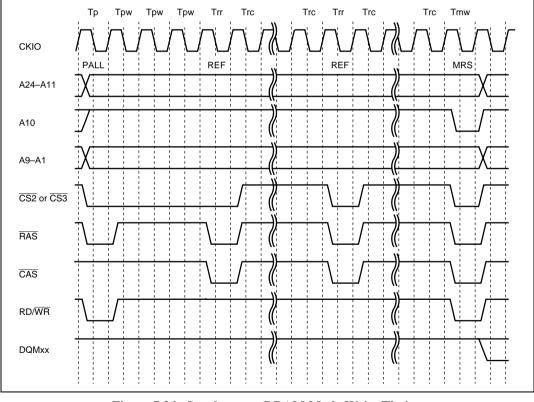

|      | 7.5.10   | Power-On Sequence                                                | . 321 |

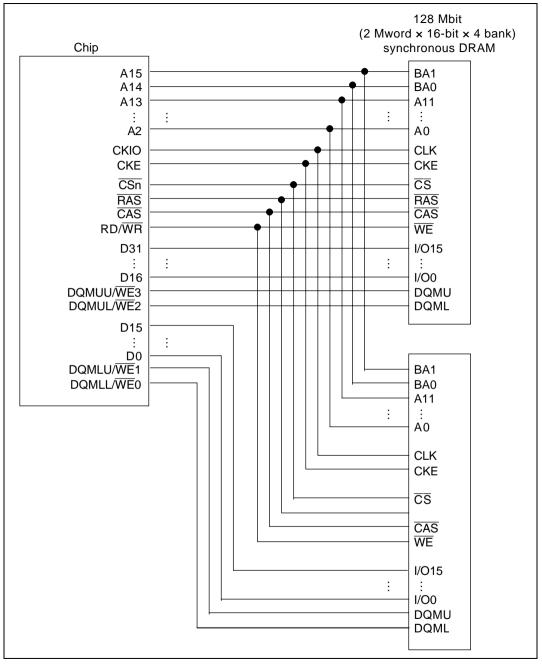

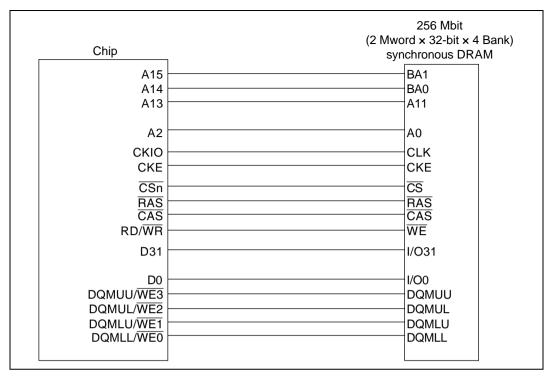

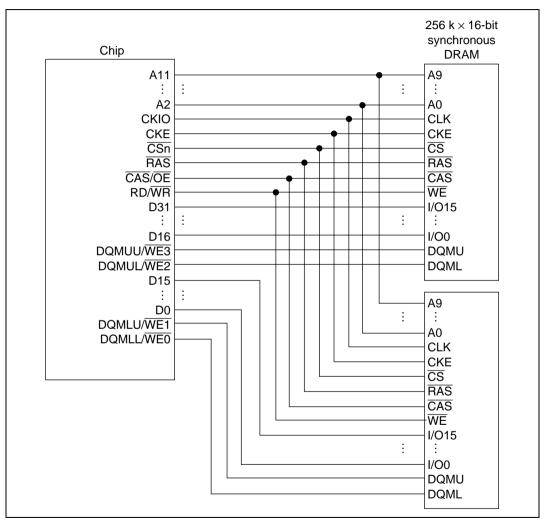

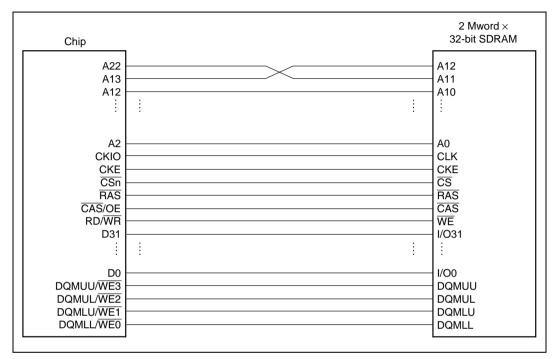

|      | 7.5.11   | 64 Mbit Synchronous DRAM (2 Mword × 32-bit) Connection           | . 323 |

| 7.6  | DRAM     | Interface                                                        | . 324 |

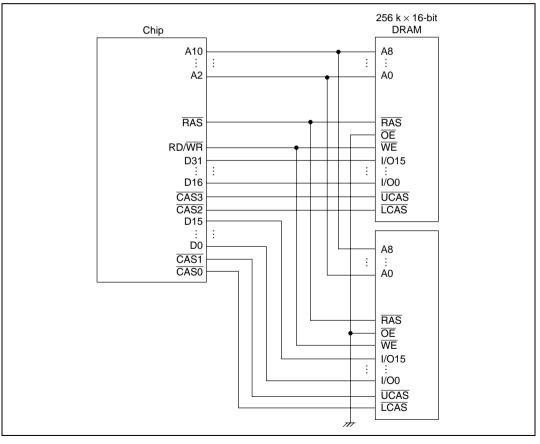

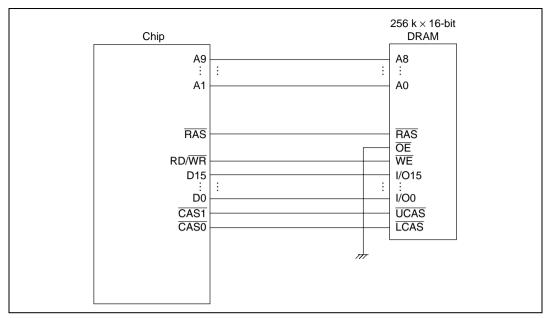

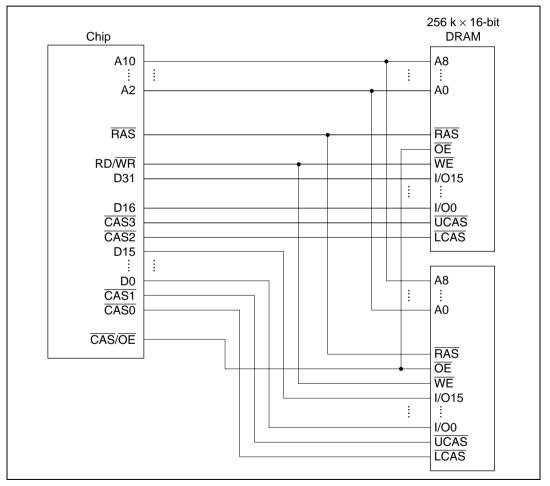

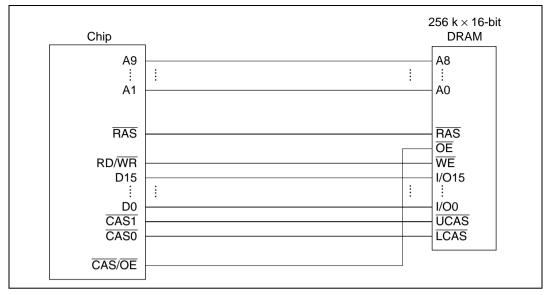

|      | 7.6.1    | DRAM Direct Connection                                           | . 324 |

|      | 7.6.2    | Address Multiplexing                                             | . 325 |

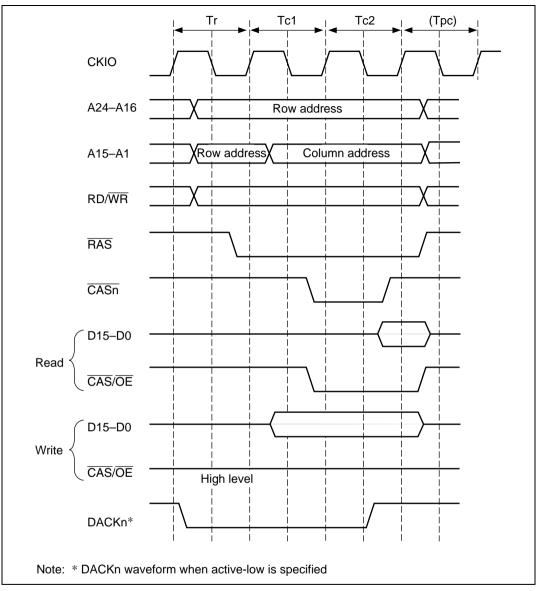

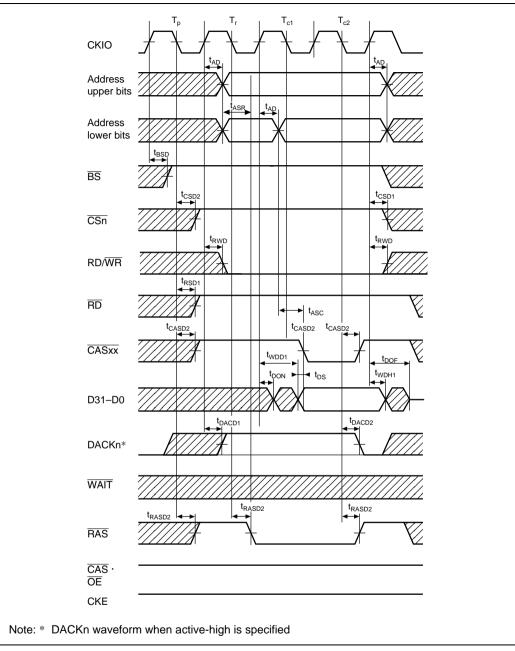

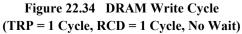

|      | 7.6.3    | Basic Timing                                                     | . 326 |

|      | 7.6.4    | Wait State Control                                               | . 327 |

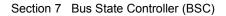

|      | 7.6.5    | Burst Access                                                     | . 329 |

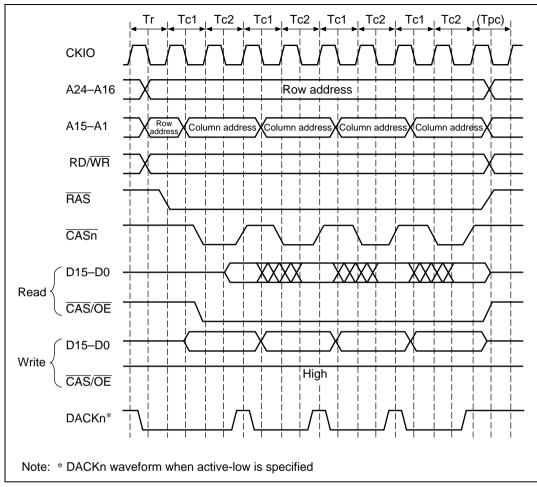

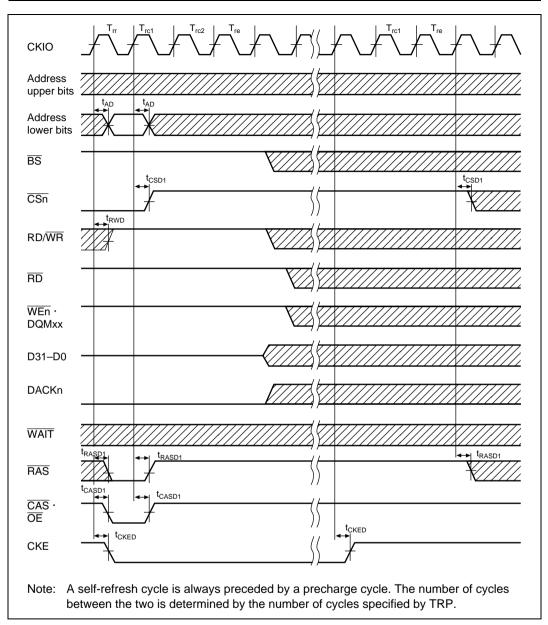

|      | 7.6.6    | EDO Mode                                                         | . 332 |

|      | 7.6.7    | DRAM Single Transfer                                             | . 336 |

|      | 7.6.8    | Refreshing                                                       | . 337 |

|      | 7.6.9    | Power-On Sequence                                                | . 339 |

| 7.7  | Burst F  | COM Interface                                                    | . 339 |

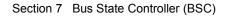

| 7.8  | Idles be | etween Cycles                                                    | . 343 |

| 7.9  | Bus Ar   | bitration                                                        | . 345 |

|      | 7.9.1    | Master Mode                                                      | . 349 |

| 7.10 | Additic  | onal Items                                                       | . 350 |

|      | 7.10.1   | Resets                                                           | . 350 |

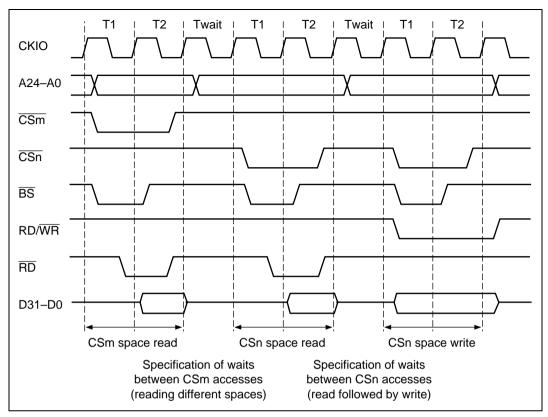

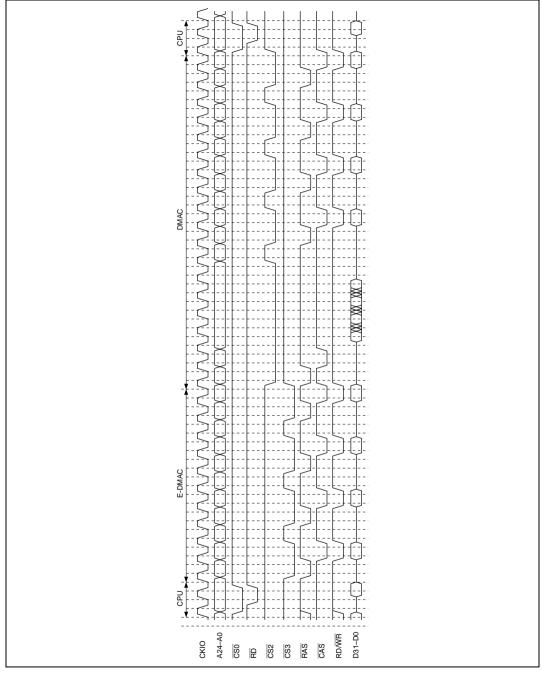

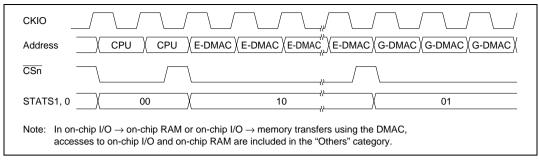

|      | 7.10.2   | Access as Viewed from CPU, DMAC or E-DMAC                        | . 351 |

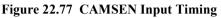

|      | 7.10.3   | STATS1 and STATS0 Pins                                           | . 352 |

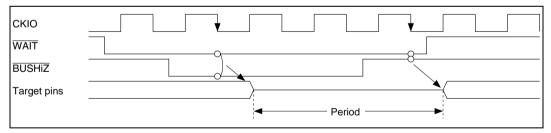

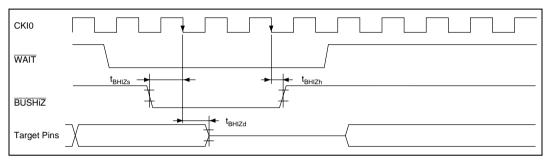

|      | 7.10.4   | BUSHiZ Specification                                             | . 353 |

| 7.11 | Usage    | Notes                                                            | . 354 |

|      | 7.11.1   | Normal Space Access after Synchronous DRAM Write when Using DMAC | . 354 |

|      | 7.11.2   |                                                                  |       |

|      |          | and External Wait Input                                          | . 356 |

|      | 7.11.3   | When connecting external device to synchronous DRAM              | . 356 |

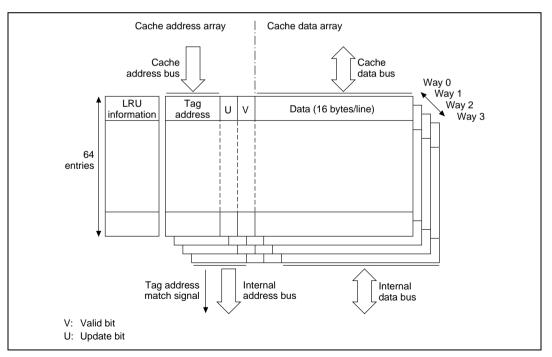

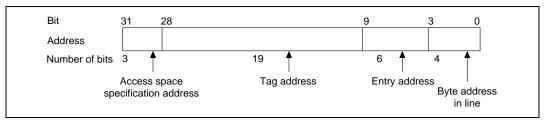

| Secti | on 8 (  | Cache                                         | 357 |

|-------|---------|-----------------------------------------------|-----|

| 8.1   | Introdu | ction                                         | 357 |

|       | 8.1.1   | Register Configuration                        | 358 |

| 8.2   | Registe | r Description                                 | 358 |

|       | 8.2.1   | Cache Control Register (CCR)                  | 358 |

| 8.3   | Address | s Space and the Cache                         | 360 |

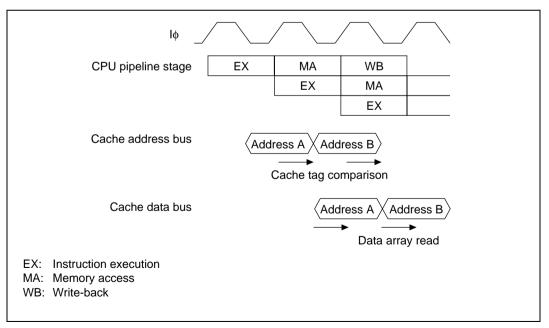

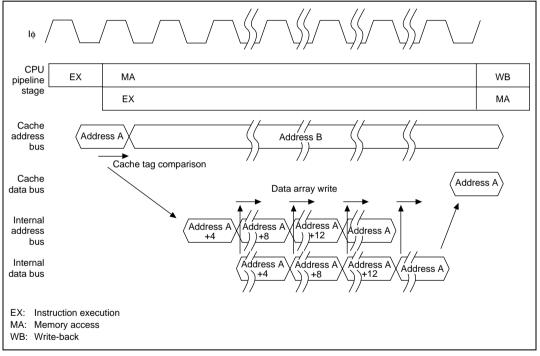

| 8.4   | Cache ( | Dperation                                     | 361 |

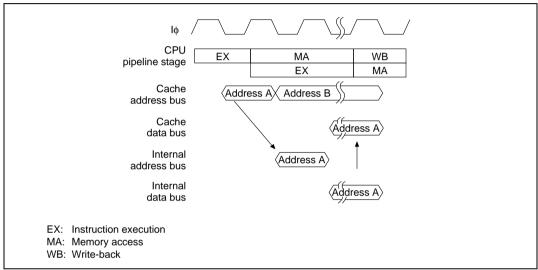

|       | 8.4.1   | Cache Reads                                   | 361 |

|       | 8.4.2   | Write Access                                  | 363 |

|       | 8.4.3   | Cache-Through Access                          | 366 |

|       | 8.4.4   | The TAS Instruction.                          | 366 |

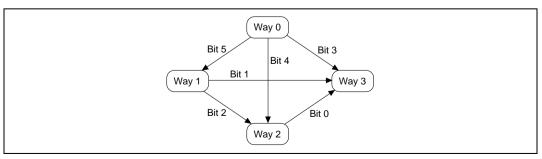

|       | 8.4.5   | Pseudo-LRU and Cache Replacement              | 366 |

|       | 8.4.6   | Cache Initialization                          | 368 |

|       | 8.4.7   | Associative Purges                            | 368 |

|       | 8.4.8   | Cache Flushing                                | 369 |

|       | 8.4.9   | Data Array Access                             | 369 |

|       | 8.4.10  | Address Array Access                          |     |

| 8.5   | Cache U | Jse                                           | 371 |

|       | 8.5.1   | Initialization                                | 371 |

|       | 8.5.2   | Purge of Specific Lines                       | 372 |

|       | 8.5.3   | Cache Data Coherency                          | 372 |

|       | 8.5.4   | Two-Way Cache Mode                            |     |

| 8.6   | Usage 1 | Notes                                         | 374 |

|       | 8.6.1   | Standby                                       | 374 |

|       | 8.6.2   | Cache Control Register                        |     |

|       |         |                                               |     |

| Secti | on 9 I  | Ethernet Controller (EtherC)                  | 375 |

| 9.1   |         | 2W                                            |     |

|       | 9.1.1   | Features                                      | 375 |

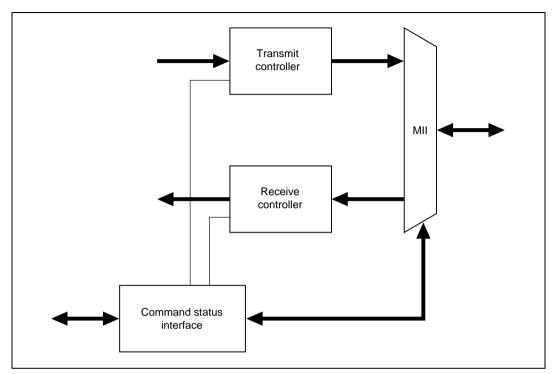

|       | 9.1.2   | Configuration                                 | 376 |

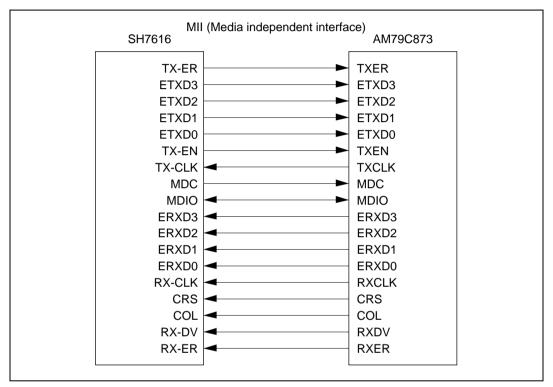

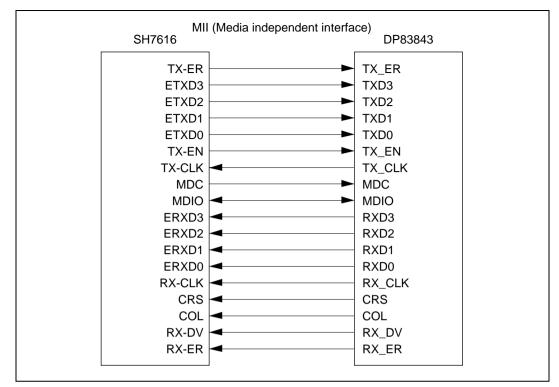

|       | 9.1.3   | Pin Configuration                             | 378 |

|       | 9.1.4   | Ethernet Controller Register Configuration    |     |

| 9.2   | Registe | r Descriptions                                | 380 |

|       | 9.2.1   | EtherC Mode Register (ECMR)                   | 380 |

|       | 9.2.2   | EtherC Status Register (ECSR)                 |     |

|       | 9.2.3   | EtherC Interrupt Permission Register (ECSIPR) | 384 |

|       | 9.2.4   | PHY Interface Register (PIR)                  |     |

|       | 9.2.5   | MAC Address High Register (MAHR)              |     |

|       | 9.2.6   | MAC Address Low Register (MALR)               |     |

|       | 9.2.7   | Receive Frame Length Register (RFLR)          |     |

Rev. 2.00 Mar 09, 2006 page xvii of xxvi

|       | 0.00    |                                                             | 200 |

|-------|---------|-------------------------------------------------------------|-----|

|       | 9.2.8   | PHY Interface Status Register (PSR)                         |     |

|       | 9.2.9   | Transmit Retry Over Counter Register (TROCR)                |     |

|       | 9.2.10  | Single Collision Detect Counter Register (SCDCR).           |     |

|       | 9.2.11  | Delay Collision Detect Counter Register (CDCR)              |     |

|       |         | Lost Carrier Counter Register (LCCR)                        |     |

|       | 9.2.13  | Carrier Not Detect Counter Register (CNDCR)                 |     |

|       |         | Illegal Frame Length Counter Register (IFLCR)               |     |

|       | 9.2.15  | CRC Error Frame Counter Register (CEFCR)                    |     |

|       | 9.2.16  | Frame Receive Error Counter Register (FRECR )               |     |

|       | 9.2.17  | Too-Short Frame Receive Counter Register (TSFRCR)           |     |

|       | 9.2.18  | Too-Long Frame Receive Counter Register (TLFRCR)            |     |

|       | 9.2.19  | Residual-Bit Frame Counter Register (RFCR)                  | 400 |

|       | 9.2.20  | Multicast Address Frame Counter Register (MAFCR)            | 401 |

| 9.3   | Operati | on                                                          | 402 |

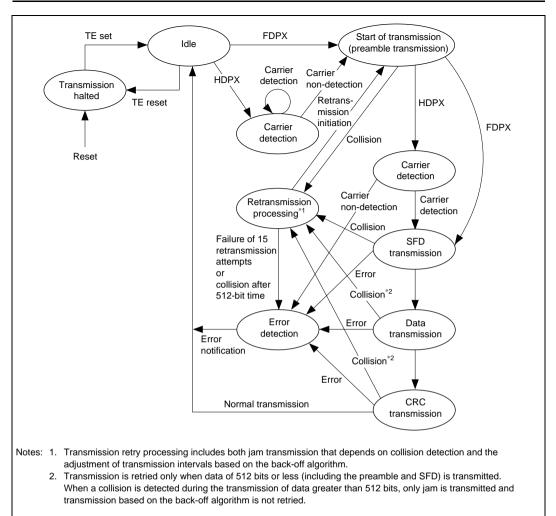

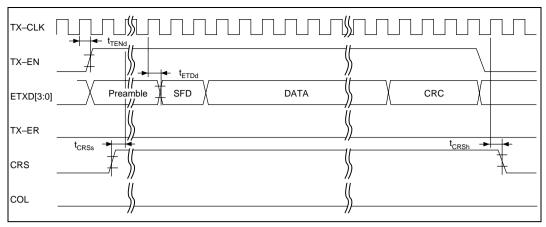

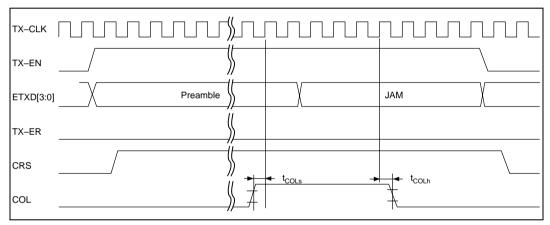

|       | 9.3.1   | Transmission                                                | 402 |

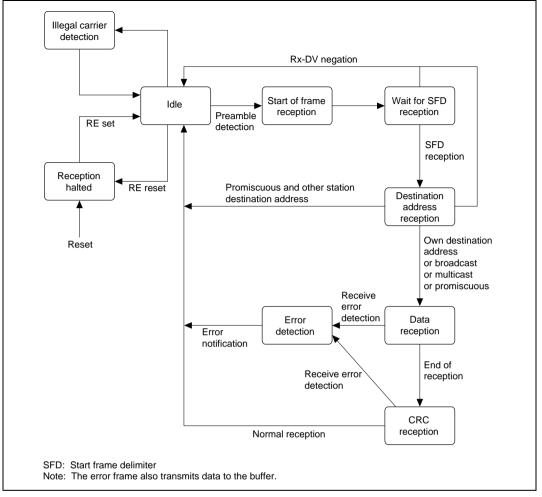

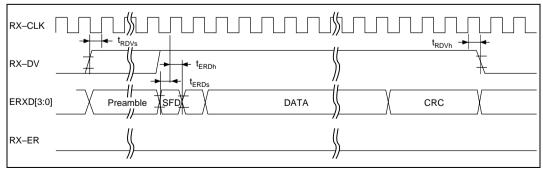

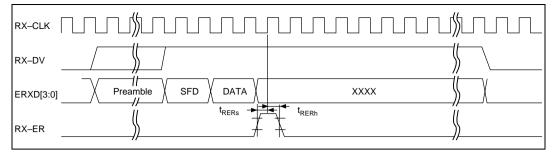

|       | 9.3.2   | Reception                                                   | 404 |

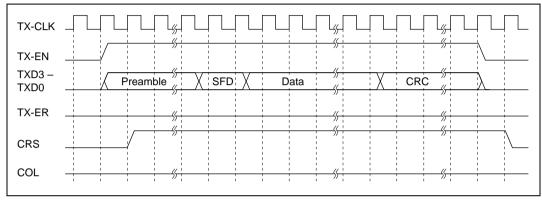

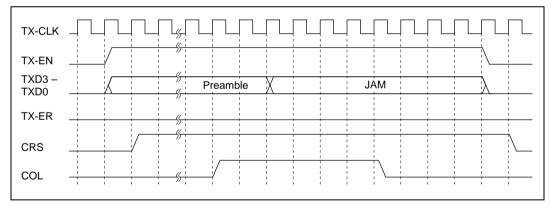

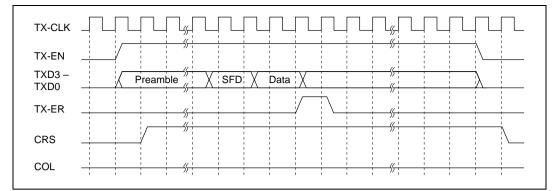

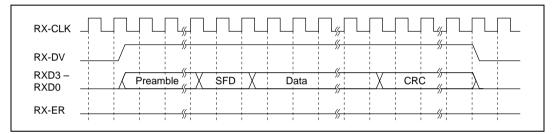

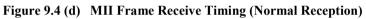

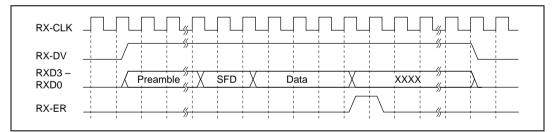

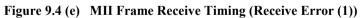

|       | 9.3.3   | MII Frame Timing                                            | 406 |

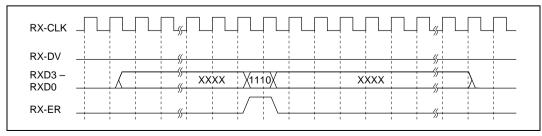

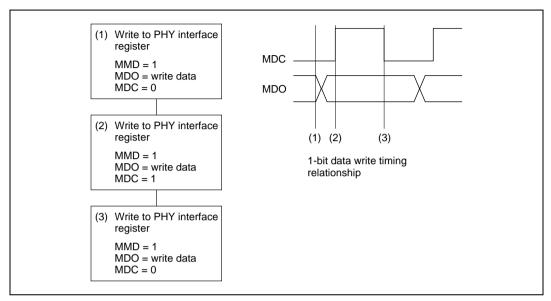

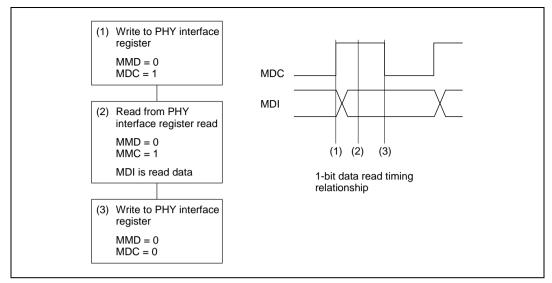

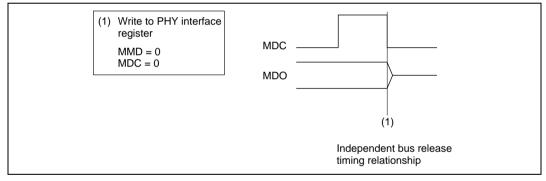

|       | 9.3.4   | Accessing MII Registers                                     | 408 |

|       | 9.3.5   | Magic Packet Detection                                      | 411 |

|       | 9.3.6   | CPU Operating Mode and Ethernet Controller Operation        |     |

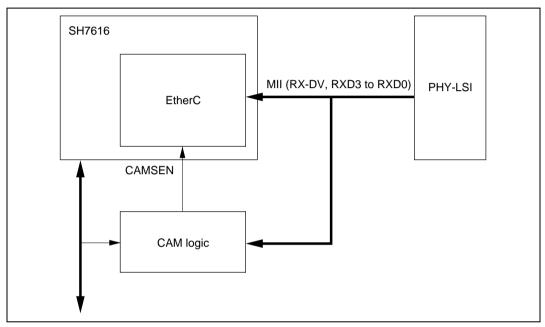

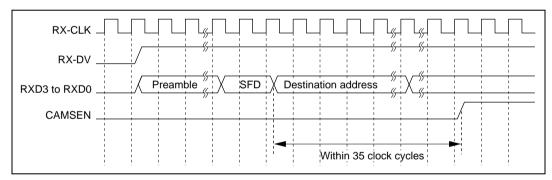

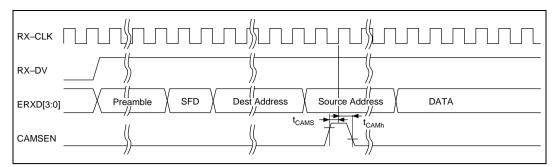

|       | 9.3.7   | CAM Match Signal Input Function                             |     |

| 9.4   | Connec  | tion to PHY-LSI                                             |     |

|       |         |                                                             |     |

| Secti | on 10   | Ethernet Controller Direct Memory Access Controller         |     |

|       |         | (E-DMAC)                                                    | 417 |

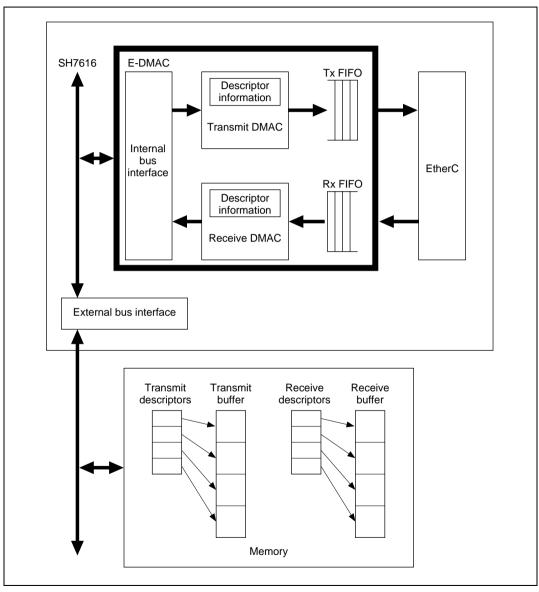

| 10.1  | Overvie | ew                                                          | 417 |

|       | 10.1.1  | Features                                                    | 417 |

|       | 10.1.2  | Configuration                                               | 418 |

|       |         | Descriptor Management System                                |     |

|       |         | Register Configuration                                      |     |

| 10.2  |         | r Descriptions                                              |     |

|       |         | E-DMAC Mode Register (EDMR)                                 |     |

|       |         | E-DMAC Transmit Request Register (EDTRR)                    |     |

|       |         | E-DMAC Receive Request Register (EDRRR)                     |     |

|       |         | Transmit Descriptor List Address Register (TDLAR)           |     |

|       |         | Receive Descriptor List Address Register (IDL/IIC)          |     |

|       |         | EtherC/E-DMAC Status Register (EESR)                        |     |

|       |         | EtherC/E-DMAC Status Interrupt Permission Register (EESIPR) |     |

|       |         | Transmit/Receive Status Copy Enable Register (TRSCER)       |     |

|       |         | Receive Missed-Frame Counter Register (RMFCR)               |     |

|       | 10.2.9  | Receive missed-maine Counter Register (RIMPCR)              | 400 |

Rev. 2.00 Mar 09, 2006 page xviii of xxvi

|      | 10.2.10 | ) Transmit FIFO Threshold Register (TFTR)                | 439 |

|------|---------|----------------------------------------------------------|-----|

|      | 10.2.1  | FIFO Depth Register (FDR)                                | 441 |

|      | 10.2.12 | 2 Receiver Control Register (RCR)                        | 442 |

|      | 10.2.13 | B E-DMAC Operation Control Register (EDOCR)              | 443 |

|      | 10.2.14 | Receiving-Buffer Write Address Register (RBWAR)          | 444 |

|      | 10.2.15 | 5 Receiving-Descriptor Fetch Address Register (RDFAR)    | 445 |

|      | 10.2.16 | 5 Transmission-Buffer Read Address Register (TBRAR)      | 446 |

|      | 10.2.17 | 7 Transmission-Descriptor Fetch Address Register (TDFAR) | 447 |

| 10.3 | Operat  | ion                                                      | 448 |

|      | 10.3.1  | Descriptor List and Data Buffers                         | 448 |

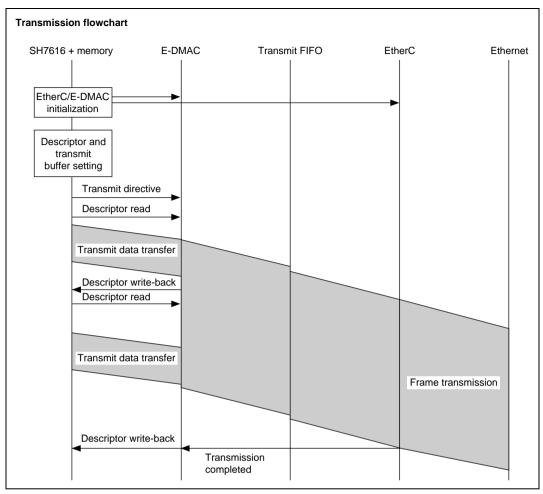

|      | 10.3.2  | Transmission                                             | 455 |

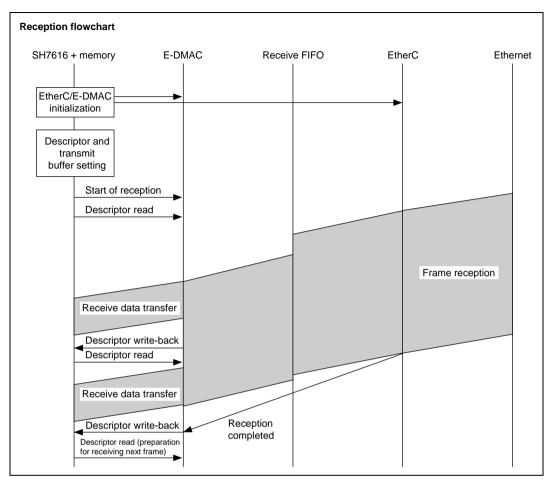

|      | 10.3.3  | Reception                                                | 457 |

|      | 10.3.4  | Multi-Buffer Frame Transmit/Receive Processing           | 459 |

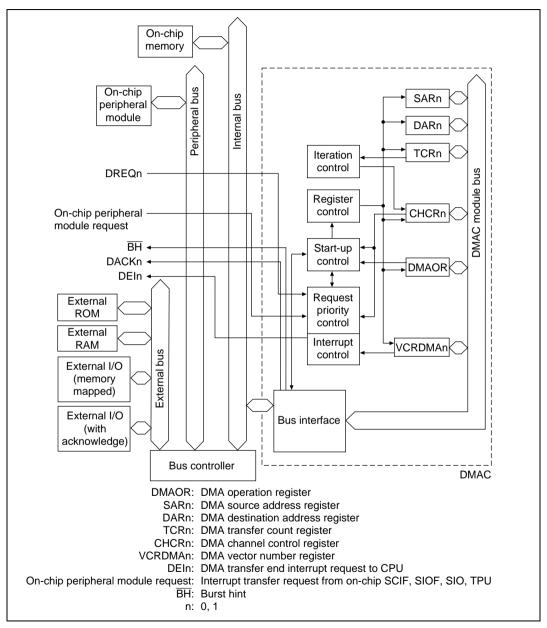

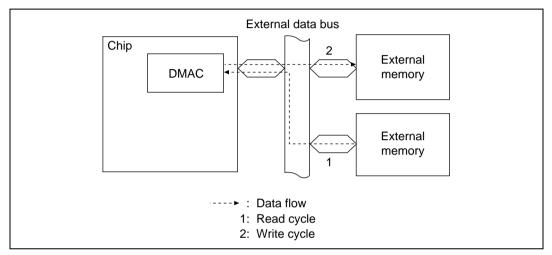

| Sect | ion 11  | Direct Memory Access Controller (DMAC)                   | 461 |

| 11.1 |         | ew                                                       |     |

|      | 11.1.1  | Features                                                 | 461 |

|      | 11.1.2  | Block Diagram                                            | 463 |

|      | 11.1.3  | Pin Configuration                                        | 464 |

|      | 11.1.4  | Register Configuration                                   | 465 |

| 11.2 | Registe | er Descriptions                                          | 466 |

|      | 11.2.1  | DMA Source Address Registers 0 and 1 (SAR0, SAR1)        | 466 |

|      | 11.2.2  | DMA Destination Address Registers 0 and 1 (DAR0, DAR1)   | 466 |

|      | 11.2.3  | DMA Transfer Count Registers 0 and 1 (TCR0, TCR1)        | 467 |

|      | 11.2.4  | DMA Channel Control Registers 0 and 1 (CHCR0, CHCR1)     | 467 |

|      | 11.2.5  | DMA Vector Number Registers 0 and 1 (VCRDMA0, VCRDMA1)   | 472 |

|      | 11.2.6  | DMA Request/Response Selection Control Registers 0 and 1 |     |

|      |         | (DRCR0, DRCR1)                                           | 473 |

|      | 11.2.7  | DMA Operation Register (DMAOR)                           | 475 |

| 11.3 | Operat  | ion                                                      | 477 |

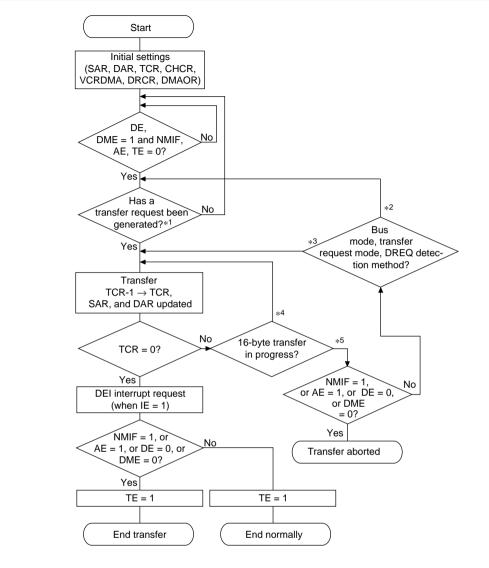

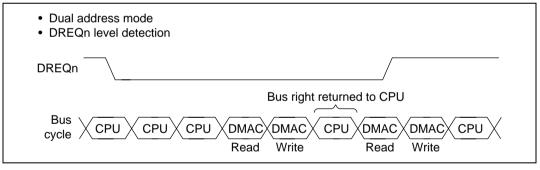

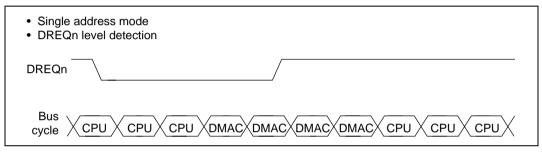

|      | 11.3.1  | DMA Transfer Flow                                        | 477 |

|      | 11.3.2  | DMA Transfer Requests                                    | 479 |

|      | 11.3.3  | Channel Priorities                                       | 483 |

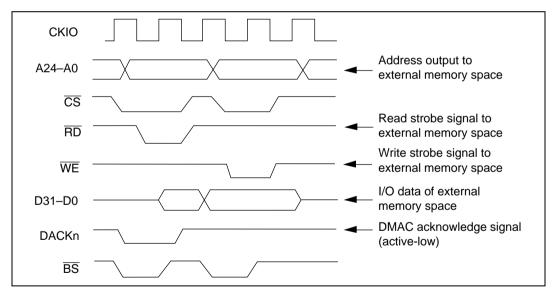

|      | 11.3.4  | DMA Transfer Types                                       | 486 |

|      | 11.3.5  | Number of Bus Cycles                                     | 496 |

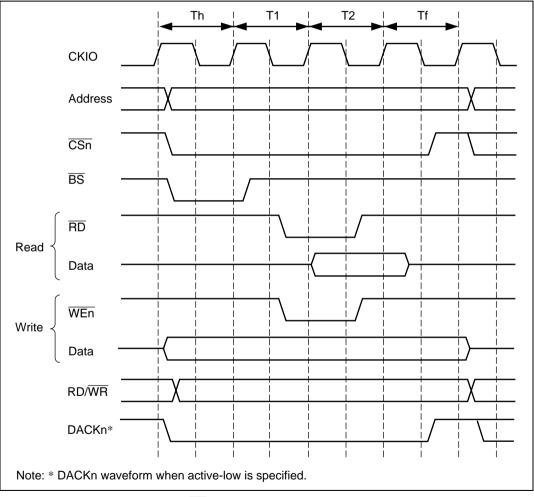

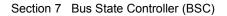

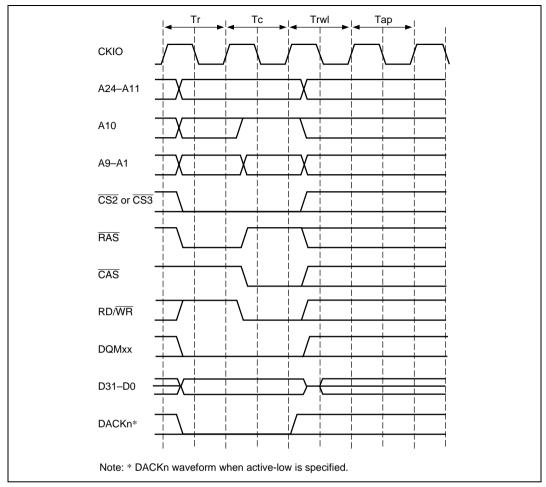

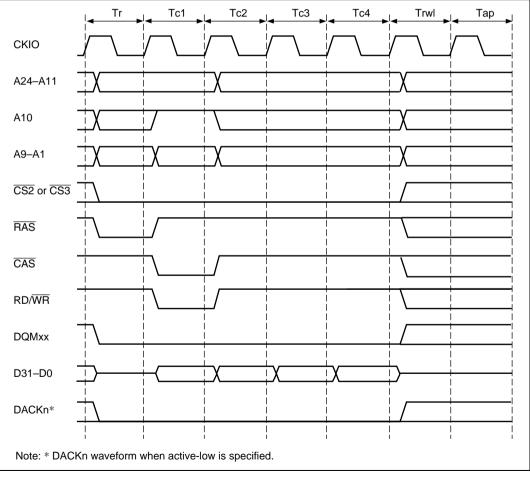

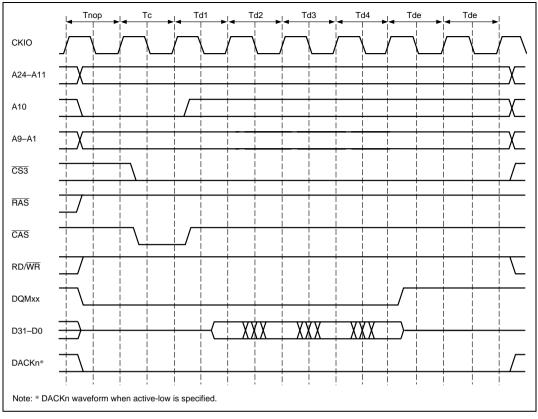

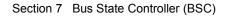

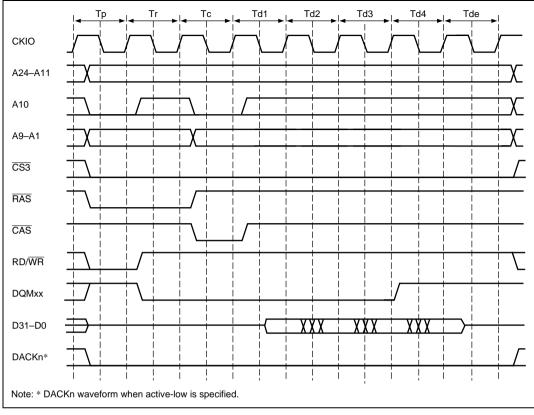

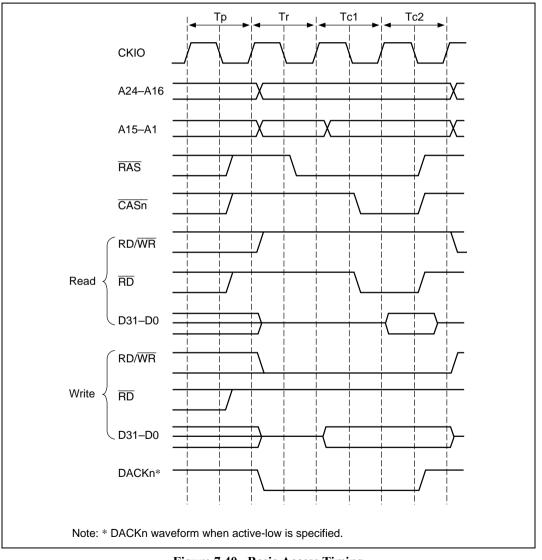

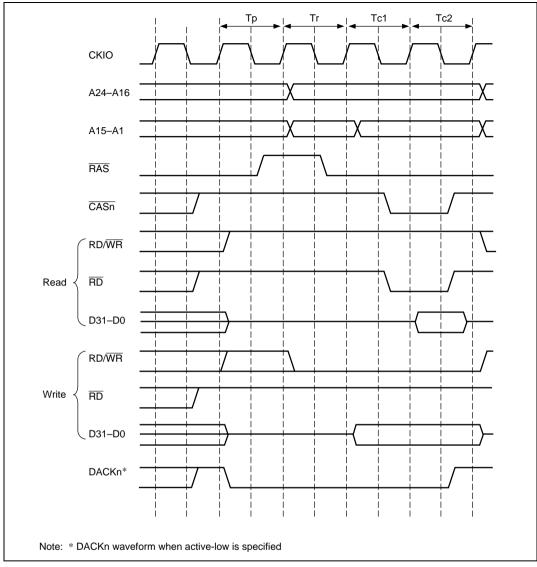

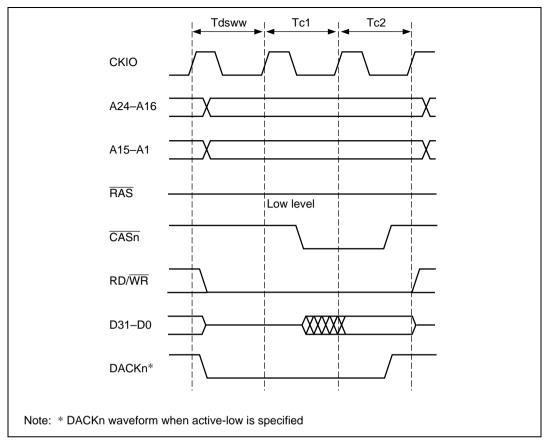

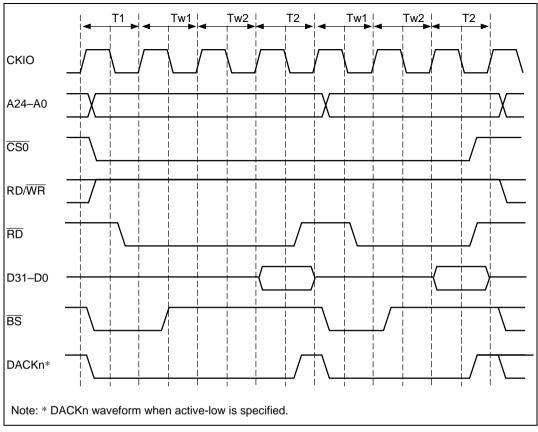

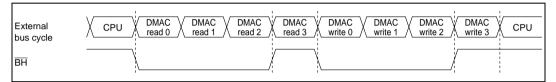

|      | 11.3.6  | DMA Transfer Request Acknowledge Signal Output Timing    | 496 |

|      | 11.3.7  |                                                          |     |

|      |         | DMA Transfer End                                         |     |

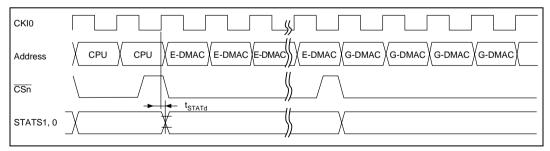

|      |         | BH Pin Output Timing                                     |     |

| 11.4 | Usage   | Examples                                                 | 516 |

Rev. 2.00 Mar 09, 2006 page xix of xxvi

|       | 11.4.1  | Example of DMA Data Transfer Between SCIF and External Memory | 516 |

|-------|---------|---------------------------------------------------------------|-----|

| 11.5  | Usage I | Notes                                                         | 516 |

|       |         |                                                               |     |

| Secti | on 12   | 16-Bit Free-Running Timer (FRT)                               | 519 |

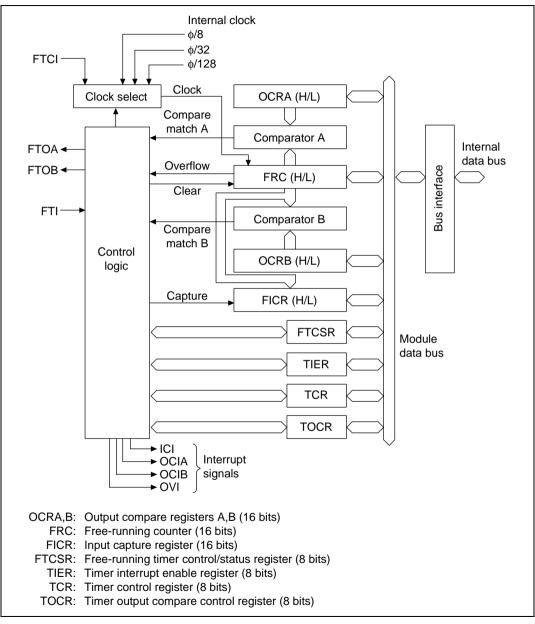

| 12.1  | Overvie | ew                                                            | 519 |

|       | 12.1.1  | Features                                                      | 519 |

|       | 12.1.2  | Block Diagram                                                 | 520 |

|       | 12.1.3  | Pin Configuration                                             | 521 |

|       | 12.1.4  | Register Configuration                                        | 521 |

| 12.2  | Registe | r Descriptions                                                | 522 |

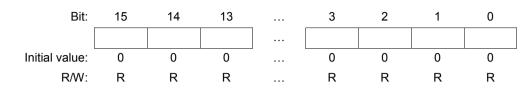

|       | 12.2.1  | Free-Running Counter (FRC)                                    | 522 |

|       | 12.2.2  | Output Compare Registers A and B (OCRA and OCRB)              | 522 |

|       | 12.2.3  | Input Capture Register (FICR)                                 | 523 |

|       | 12.2.4  | Timer Interrupt Enable Register (TIER)                        | 523 |

|       | 12.2.5  | Free-Running Timer Control/Status Register (FTCSR)            | 524 |

|       |         | Timer Control Register (TCR)                                  |     |

|       | 12.2.7  | Timer Output Compare Control Register (TOCR)                  | 527 |

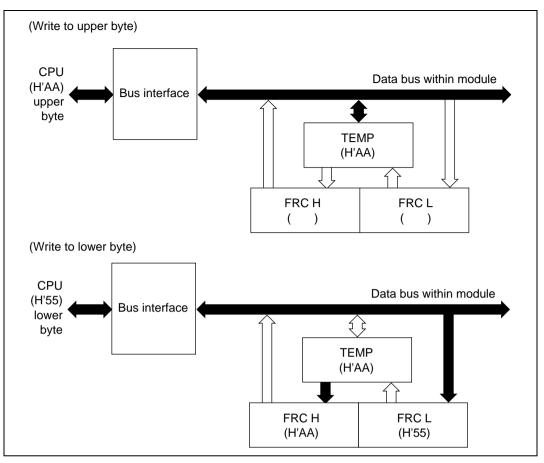

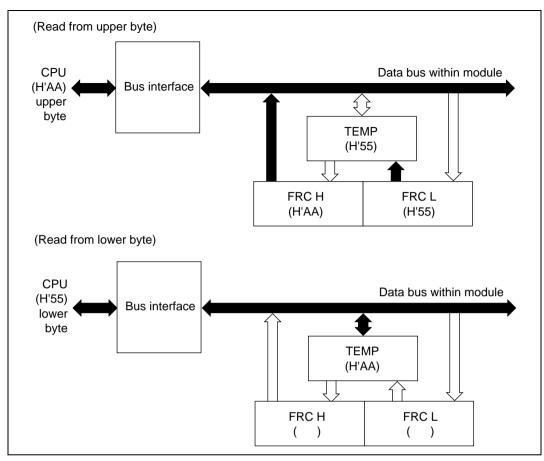

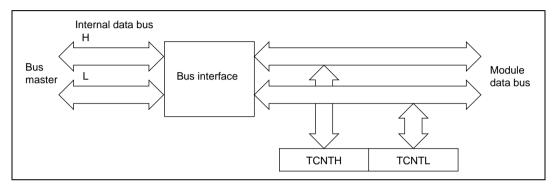

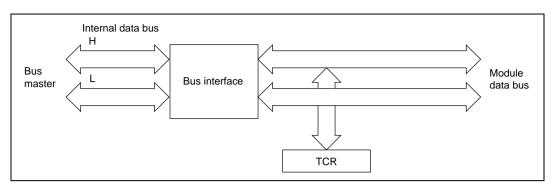

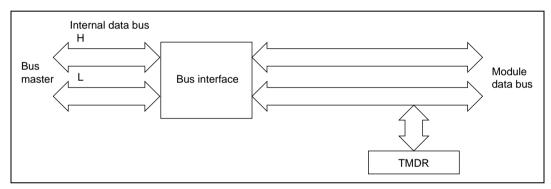

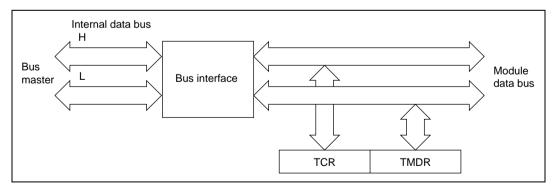

| 12.3  | CPU In  | iterface                                                      | 528 |

| 12.4  | Operati | on                                                            | 531 |

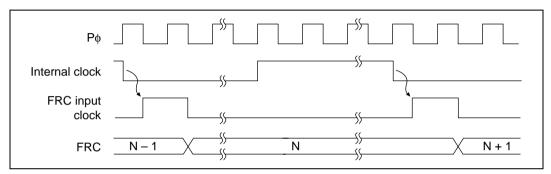

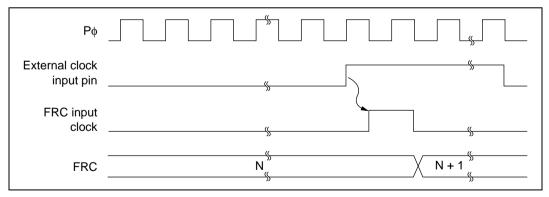

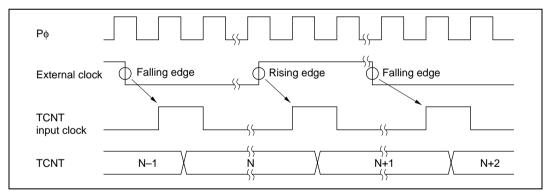

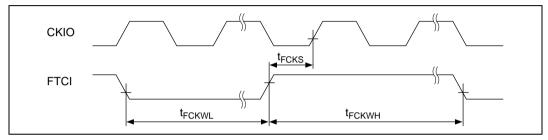

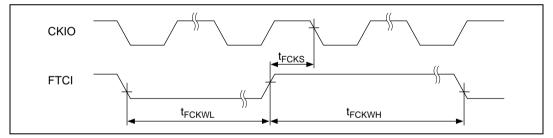

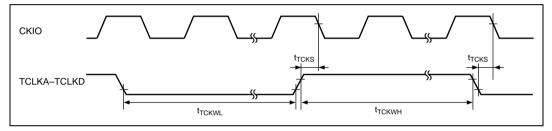

|       | 12.4.1  | FRC Count Timing                                              | 531 |

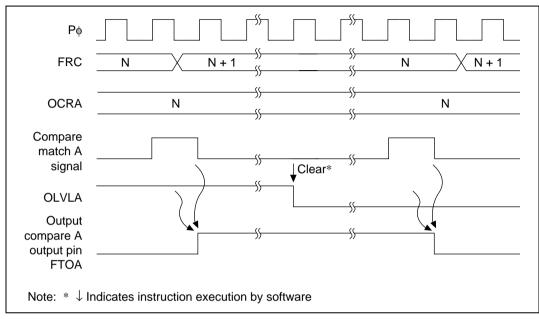

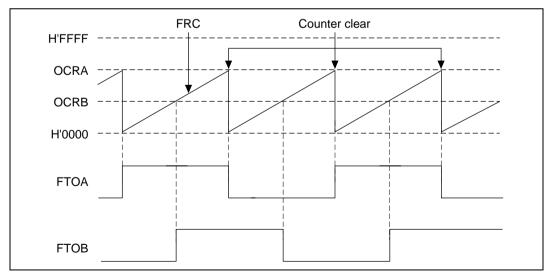

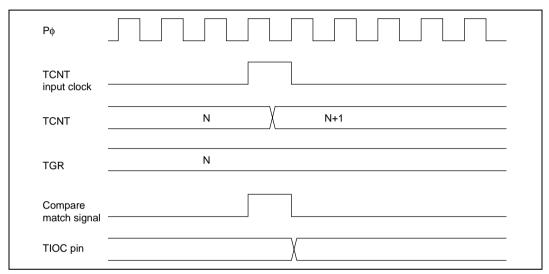

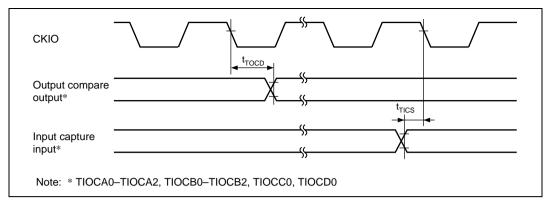

|       | 12.4.2  | Output Timing for Output Compare                              | 532 |

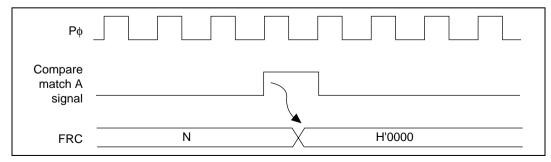

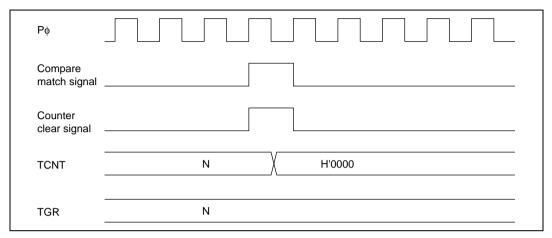

|       | 12.4.3  | FRC Clear Timing                                              | 532 |

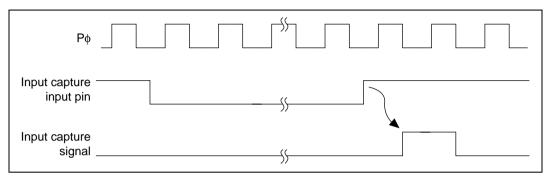

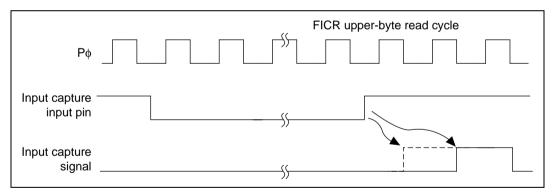

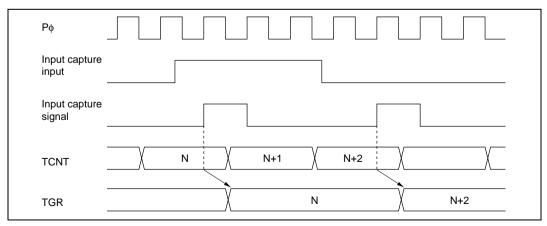

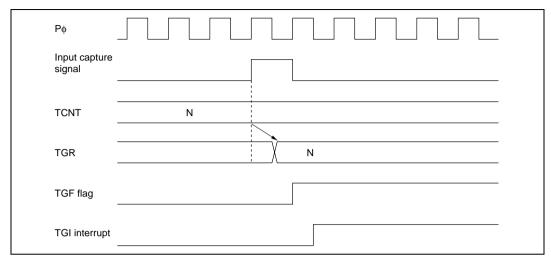

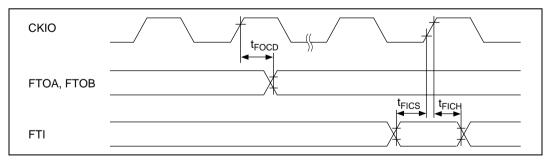

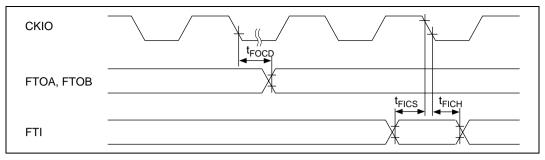

|       | 12.4.4  | Input Capture Input Timing                                    | 533 |

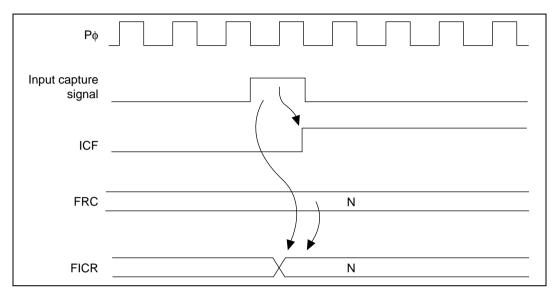

|       | 12.4.5  | Input Capture Flag (ICF) Setting Timing                       | 534 |

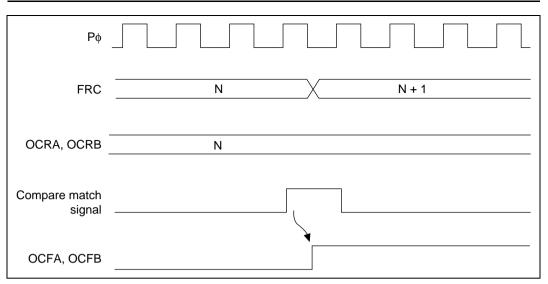

|       | 12.4.6  | Output Compare Flag (OCFA, OCFB) Setting Timing               | 534 |

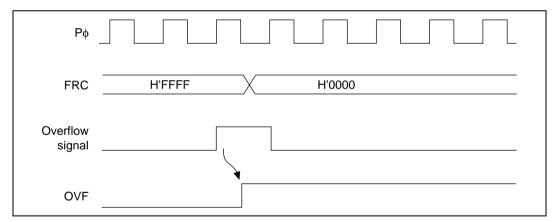

|       |         | Timer Overflow Flag (OVF) Setting Timing                      |     |

| 12.5  | Interru | ot Sources                                                    | 536 |

| 12.6  | Examp   | le of FRT Use                                                 | 536 |

| 12.7  | Usage 1 | Notes                                                         | 537 |

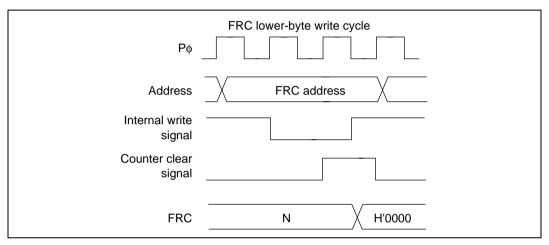

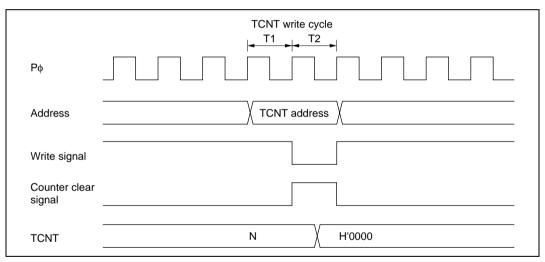

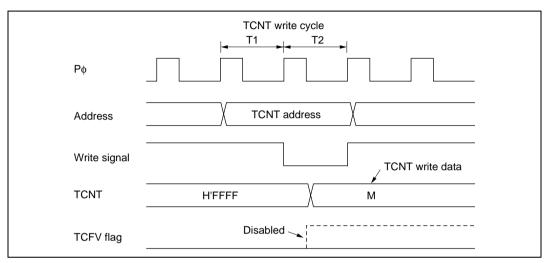

|       | 12.7.1  | Contention between FRC Write and Clear                        | 537 |

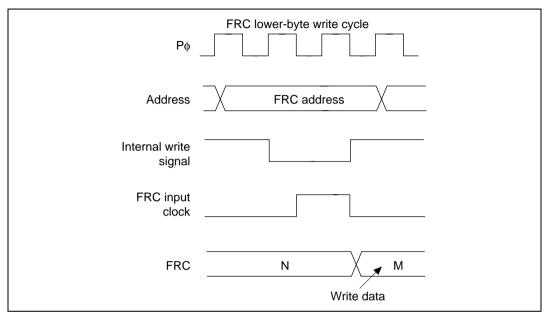

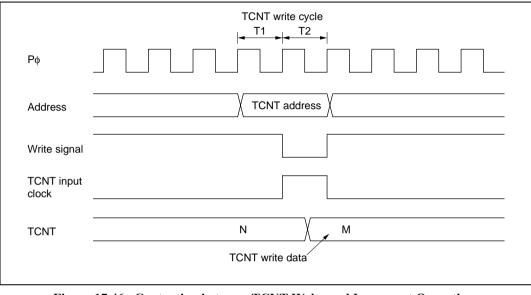

|       | 12.7.2  | Contention between FRC Write and Increment                    | 538 |

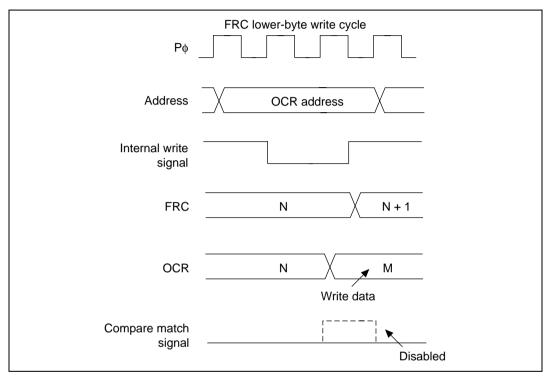

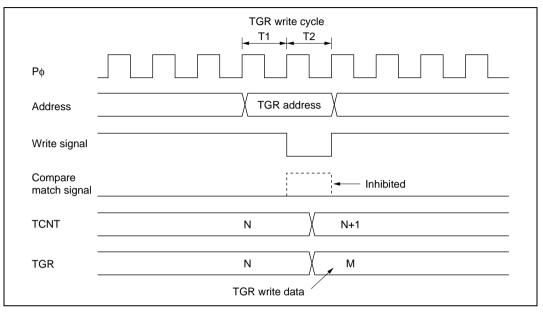

|       | 12.7.3  | Contention between OCR Write and Compare Match                | 539 |

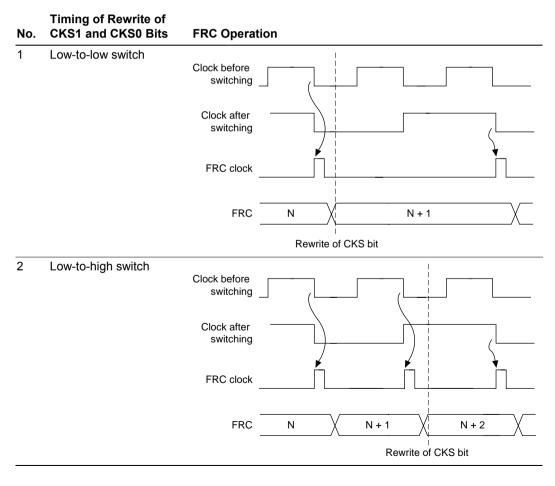

|       | 12.7.4  | Internal Clock Switching and Counter Operation                | 540 |

|       | 12.7.5  | Timer Output (FTOA, FTOB)                                     | 541 |

|       |         |                                                               |     |

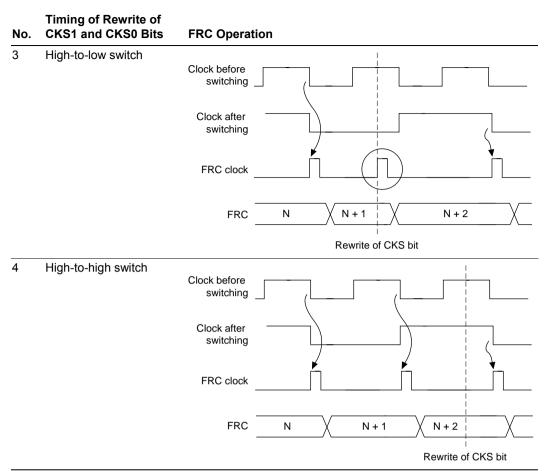

| Secti | on 13   | Watchdog Timer (WDT)                                          | 543 |

| 13.1  |         | ew                                                            |     |

|       |         | Features                                                      |     |

|       |         | Block Diagram                                                 |     |

|       |         | Pin Configuration                                             |     |

|       |         |                                                               |     |

|      | 13.1.4             | Register Configuration                                          | 545        |

|------|--------------------|-----------------------------------------------------------------|------------|

| 13.2 |                    | er Descriptions                                                 |            |

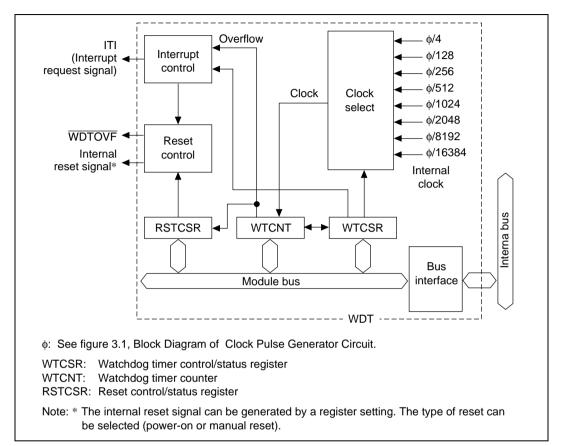

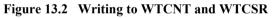

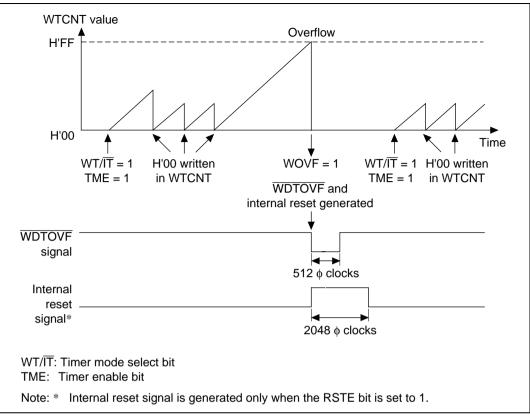

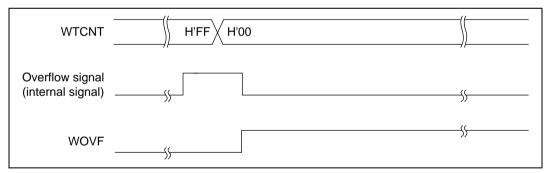

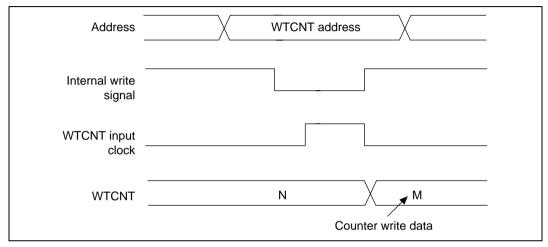

|      | 13.2.1             | Watchdog Timer Counter (WTCNT)                                  | 545        |

|      | 13.2.2             | Watchdog Timer Control/Status Register (WTCSR)                  | 546        |

|      | 13.2.3             | Reset Control/Status Register (RSTCSR)                          | 547        |