- Read and Write Clocks Can Be Asynchronous or Coincident

- Organization:

- SN74ACT72211L  $512 \times 9$

- SN74ACT72221L  $1024 \times 9$

- SN74ACT72231L 2048 × 9

- SN74ACT72241L  $4096 \times 9$

- Write and Read Cycle Times of 15 ns

- Bit-Width Expandable

- Empty and Full Flags

- Programmable Almost-Empty and Almost-Full Flags With Default Offsets of Empty+7 and Full-7, Respectively

- TTL-Compatible Inputs

- Fully Compatible With the IDT72211/72221/72231/72241

- Available in 32-Pin Plastic J-Leaded Chip Carrier (RJ)

#### description

The SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, and SN74ACT72241L are constructed with CMOS dual-port SRAM and are arranged as 512, 1024, 2048, and 4096 9-bit words, respectively. Internal write and read address counters provide data throughput on a first-in, first-out (FIFO) basis. Full and empty flags prevent memory overflow and underflow, and two programmable flags (almost full and almost empty) are provided.

The SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, and SN74ACT72241L are synchronous FIFOs, which means the data input port and data output port each employ synchronous control. Write-enable ( $\overline{WEN1}$ ,  $WEN2/\overline{LD}$ ) signals allow the low-to-high transition of the write clock (WCLK) to store data in memory, and read-enable ( $\overline{REN1}$ ,  $\overline{REN2}$ ) signals allow the low-to-high transition of the read clock (RCLK) to read data from memory. WCLK and RCLK are independent of one another and can operate asynchronously or be tied together for single-clock operation.

The empty-flag ( $\overline{EF}$ ) output is synchronized to RCLK and the full-flag ( $\overline{FF}$ ) output is synchronized to WCLK to indicate absolute boundary conditions. Write operations are prohibited when  $\overline{FF}$  is low, and read operations are prohibited when  $\overline{EF}$  is low. Two programmable flags, programmable almost empty ( $\overline{PAE}$ ) and programmable almost full ( $\overline{PAF}$ ), can both be programmed to indicate any measure of memory fill. After reset,  $\overline{PAE}$  defaults to empty+7 and  $\overline{PAF}$  defaults to full-7. Flag-offset programming control is similar to a memory write with the use of the load (WEN2/LD) signal.

These devices are suited for providing a data channel between two buses operating at asynchronous or synchronous rates. Applications include use as rate buffers for graphics systems and high-speed queues for communication systems. A 9-bit-wide data path is provided for the transmission of byte data plus a parity bit or packet-framing information.

The SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, and SN74ACT72241L are characterized for operation from 0°C to 70°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1993, Texas Instruments Incorporated

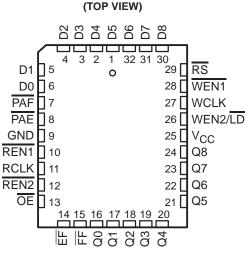

**RJ PACKAGE**

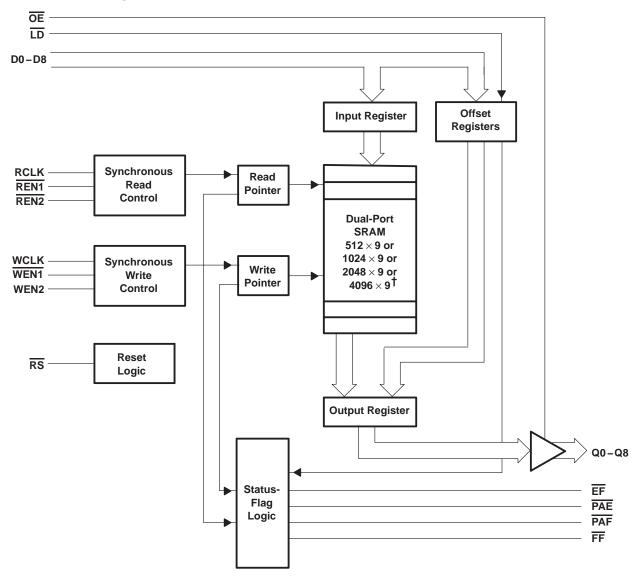

### functional block diagram

$+512 \times 9$  for the SN74ACT72211L; 1024  $\times$  9 for the SN74ACT72221L; 2048  $\times$  9 for the SN74ACT72231L; 4096  $\times$  9 for the SN74ACT72241L

## **Terminal Functions**

| NAME          | NO.           | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D8         | 6-1,<br>32-30 | I   | Data inputs                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EF            | 14            | 0   | Empty-flag. When memory is empty, $\overline{\text{EF}}$ is low and further data reads are ignored by the device. When $\overline{\text{EF}}$ is high, the memory is not empty and data reads are allowed. $\overline{\text{EF}}$ is synchronized to RCLK by one flip-flop.                                                                                                                                                            |

| FF            | 15            | 0   | Full-flag. When memory is full, $\overline{FF}$ is low and data writes are inhibited. $\overline{FF}$ is synchronized to WCLK by one flip-flop.                                                                                                                                                                                                                                                                                        |

| GND           | 9             |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OE            | 13            | Ι   | Output-enable. $Q0-Q8$ are in the high-impedance state when $\overline{OE}$ is high. $Q0-Q8$ are active when $\overline{OE}$ is low.                                                                                                                                                                                                                                                                                                   |

| PAE           | 8             | 0   | Programmable almost-empty-flag. PAE is low when the FIFO is almost empty based on the value in its offset register. The default value for the register is empty + 7. PAE is synchronized to RCLK by one flip-flop.                                                                                                                                                                                                                     |

| PAF           | 7             | 0   | Programmable almost-full-flag. PAF is low when the FIFO is almost full based on the value in its offset register.<br>The default value for the register is full –7. PAF is synchronized to WCLK by one flip-flop.                                                                                                                                                                                                                      |

| Q0-Q8         | 16-24         | 0   | Data outputs                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RCLK          | 11            | Ι   | Read-clock. A data read is performed by the low-to-high transition of RCLK when $\overline{\text{REN1}}$ and $\overline{\text{REN2}}$ are asserted and $\overline{\text{EF}}$ is high.                                                                                                                                                                                                                                                 |

| REN1,<br>REN2 | 10,<br>11     | I   | Read-enable. Data is read from the FIFO on a low-to-high transition of RCLK when $\overline{\text{REN1}}$ and $\overline{\text{REN2}}$ are low and $\overline{\text{EF}}$ is high.                                                                                                                                                                                                                                                     |

| RS            | 29            | I   | Reset. When $\overline{RS}$ is set low, the read and write pointers are initialized to the first RAM location and the FIFO is empty. $\overline{FF}$ and $\overline{PAF}$ are set high, and $\overline{EF}$ and $\overline{PAE}$ are set low. Each bit in the data output register is set low by a device reset. The FIFO must be reset after power up before data is written.                                                         |

| VCC           |               |     | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                         |

| WCLK          | 27            | I   | Write-clock. Data is written by the low-to-high transition of WCLK when WEN1 and WEN2/LD are asserted and FF is high.                                                                                                                                                                                                                                                                                                                  |

| WEN1          | 28            | I   | Write-enable 1. WEN1 is the only write enable terminal if the device is configured to have programmable flags. Data is written on a low-to-high transition of WCLK when WEN1 is low and FF is high. If the FIFO is not configured for programmable flags, data is written on a low-to-high transition of WCLK when WEN1 and WEN2 are asserted and FF is high.                                                                          |

| WEN2/LD       | 26            | I   | Write-enable 2/load. This is a dual-purpose input. The FIFO can have either two write enables or programmable flags. To use WEN2/LD as a WEN2, WEN2/LD must be held high at reset. When WEN2 and WEN1 are asserted and FF is high, a low-to-high transition of WCLK writes data. To use WEN2/LD as the LD terminal, it must be held low at reset. In this case, LD is asserted low to write or read the programmable offset registers. |

## SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, SN74ACT72241L 512 $\times$ 9, 1024 $\times$ 9, 2048 $\times$ 9, AND 4096 $\times$ 9 SYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES

SCAS222 - FEBRUARY 1993 - REVISED JUNE 1993

### detailed description

#### device reset

A reset is performed by taking the reset ( $\overline{RS}$ ) input low. This initializes both the write and read pointers to the first memory location. After a reset, the full flag ( $\overline{FF}$ ) and programmable almost-full flag ( $\overline{PAF}$ ) are high and the empty flag ( $\overline{EF}$ ) and programmable almost-empty flag ( $\overline{PAE}$ ) are low. Each bit in the data output register (Q0–Q8) is set low, and the flag offset registers are loaded with the default offset values. A FIFO must be reset after power up before a write cycle is allowed.

The logic level on the dual-purpose input write enable 2/load (WEN2/LD) during reset determines its function. If WEN2/LD is high when RS returns high at the end of the reset cycle, the input is a second write enable (see FIFO writes and reads) and the programmable flags (PAF, PAE) can only use the default values. If WEN2/LD is low when RS returns high at the end of the reset cycle, the input is the load (LD) enable for writing and reading flag offset registers (see flag programming).

#### **FIFO writes and reads**

Data is written to memory by a low-to-high transition of write clock (WCLK) when write enable 1 ( $\overline{WEN1}$ ) is low, WEN2/ $\overline{LD}$  is high, and  $\overline{FF}$  is high. This stores D0–D8 data in the dual-port SRAM and increments the write pointer.

If no reads are performed after reset ( $\overline{RS} = V_{IL}$ ),  $\overline{FF}$  is set low upon the completion of 512 writes to the SN74ACT72211, 1024 writes to the SN74ACT72221, 2048 writes to the SN74ACT72231, and 4096 writes to the SN74ACT72241. Attempted write cycles are ignored when  $\overline{FF}$  is low.  $\overline{FF}$  is set high by the first low-to-high transition of WCLK after data is read from a full FIFO.  $\overline{FF}$  and  $\overline{PAF}$  are each synchronized to the low-to-high transition of WCLK by one flip-flop.

If a device is configured to have two write enables (see device reset), data is read by the low-to-high transition of read clock (RCLK) when both read enables ( $\overline{REN1}$ ,  $\overline{REN2}$ ) are low and  $\overline{EF}$  is high. WEN2/LD must also be high if the device is configured to have programmable flags. A read from the FIFO puts RAM data on Q0–Q8 and increments the read pointer in the same sequence as the write pointer. New data is not shifted to the output register while either one or both of the read enables are high.

EF and PAE are each synchronized to the low-to-high transition of RCLK by one flip-flop. When the device is empty, the write and read pointers are equal and EF is set low. Attempted read cycles are ignored while EF is set low. EF is set high by the first low-to-high transition of RCLK after data is written to an empty FIFO.

WCLK and RCLK can be asynchronous or coincident to one another. Writing data to FIFO memory is independent of reading data from FIFO memory and vice versa.

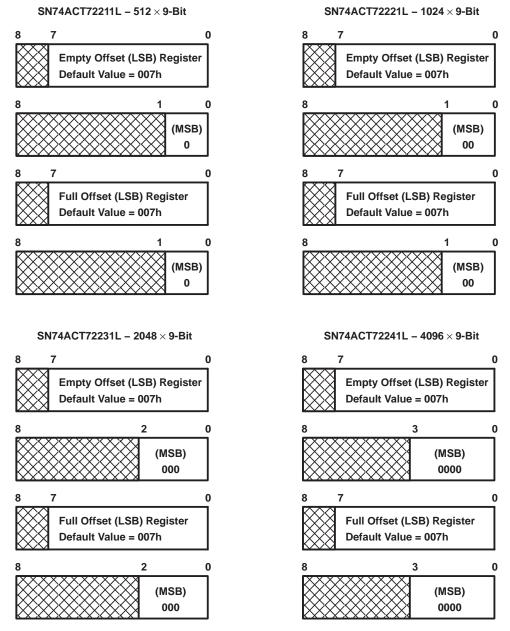

#### flag programming

When WEN2/ $\overline{\text{LD}}$  is held low during a device reset ( $\overline{\text{RS}} = V_{\text{IL}}$ ), the input is the load ( $\overline{\text{LD}}$ ) enable for flag offset programming. In this configuration, WEN2/ $\overline{\text{LD}}$  can be used to access the four 8-bit offset registers contained in the SN74ACT72211L/-72231L/-72231L/-72241L for writing or reading data.

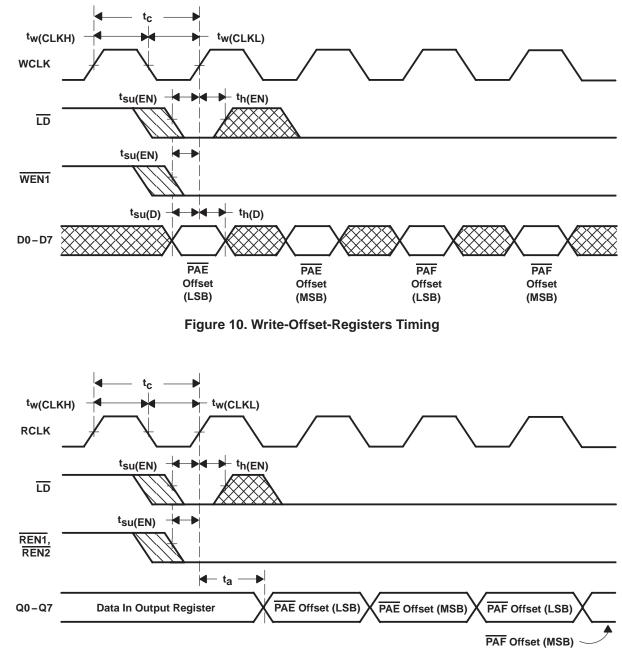

When the device is configured for programmable flags and both WEN2/LD and WEN1 are low, the first low-to-high transition of WCLK writes data from the data inputs to the empty offset least significant bit (LSB) register. The second, third, and fourth low-to-high transitions of WCLK store data in the empty offset most significant bit (MSB) register, full offset LSB register, and full offset MSB register, respectively, when WEN2/LD and WEN1 are low. The fifth low-to-high transition of WCLK while WEN2/LD and WEN1 are low writes data to the empty LSB register again. Figure 1 shows the register sizes and default values for the various device types.

It is not necessary to write to all the offset registers at one time. A subset of the offset registers can be written; then, by bringing the WEN2/ $\overline{\text{LD}}$  input high, the FIFO is returned to normal read and write operation. The next time WEN2/ $\overline{\text{LD}}$  is brought low, a write operation stores data in the next offset register in sequence.

#### flag programming (continued)

The contents of the offset registers can be read to the data outputs when WEN2/ $\overline{\text{LD}}$  is low and both  $\overline{\text{REN1}}$  and  $\overline{\text{REN2}}$  are low. Low-to-high transitions of RCLK read the register contents to the data outputs. Writes and reads should not be performed simultaneously on the offset registers (see Figure 1 and Table 1).

Figure 1. Offset Register Location and Default Values

#### flag programming (continued)

| LD | WEN1 | WCLK <sup>†</sup> | SELECTION                                                                          |

|----|------|-------------------|------------------------------------------------------------------------------------|

| 0  | 0    | Ť                 | Empty offset (LSB)<br>Empty offset (MSB)<br>Full offset (LSB)<br>Full offset (MSB) |

| 0  | 1    | $\uparrow$        | No operation                                                                       |

| 1  | 0    | $\uparrow$        | Write into FIFO                                                                    |

| 1  | 1    | $\uparrow$        | No operation                                                                       |

| +  |      | -                 |                                                                                    |

#### Table 1. Writing the Offset Registers

<sup>†</sup> The same selection sequence applies to reading from the registers. REN1 and REN2 are enabled and a read is performed on the low-to-high transition of RCLK.

### programmable flag (PAE, PAF) operation

Whether the flag offset registers are programmed as described in Table 1 or the default values are used, the programmable almost-empty flag ( $\overline{PAE}$ ) and programmable almost-full flag ( $\overline{PAF}$ ) states are determined by their corresponding offset registers and the difference between the read and write pointers.

The number formed by the empty offset least significant bit register and empty offset most significant bit register is referred to as *n* and determines the operation of  $\overrightarrow{PAE}$ .  $\overrightarrow{PAE}$  is synchronized to the low-to-high transition of RCLK by one flip-flop and is low when the FIFO contains n or fewer unread words.  $\overrightarrow{PAE}$  is set high by the low-to-high transition of RCLK when the FIFO contains (n + 1) or greater unread words.

The number formed by the full offset least significant bit register and full offset most significant bit register is referred to as *m* and determines the operation of  $\overrightarrow{PAF}$ .  $\overrightarrow{PAF}$  is synchronized to the low-to-high transition of WCLK by one flip-flop and is set low when the number of unread words in the FIFO is greater then or equal to (512 – m) for the SN74ACT72211L, (1024 – m) for the SN74ACT72221L, (2048 – m) for the SN74ACT72231L, and (4096 – m) for the SN74ACT72241L.  $\overrightarrow{PAF}$  is set high by the low-to-high transition of WCLK when the number of available memory locations is greater than m (see Table 2).

|                               | OUTPUTS                         |                                |                                |    |     |     |    |

|-------------------------------|---------------------------------|--------------------------------|--------------------------------|----|-----|-----|----|

| SN74ACT72211L                 | SN74ACT72221L                   | SN74ACT72231L                  | SN74ACT72241L                  | FF | PAF | PAE | EF |

| 0                             | 0                               | 0                              | 0                              | Н  | Н   | L   | L  |

| 1 to n <sup>†</sup>           | 1 to n <sup>†</sup>             | 1 to n <sup>†</sup>            | 1 to n†                        | Н  | Н   | L   | Н  |

| (n + 1) to<br>[512 – (m + 1)] | (n + 1) to<br>[1024 – (m + 1)]  | (n + 1) to<br>[2048 – (m + 1)] | (n + 1) to<br>[4096 – (m + 1)] | н  | Н   | Н   | н  |

| (512 – m)‡ to 511             | (1024 – m) <sup>‡</sup> to 1023 | (2048 – m)‡ to 2047            | (4096 – m)‡ to 4095            | Н  | L   | Н   | Н  |

| 512                           | 1024                            | 2048                           | 4096                           | L  | L   | Н   | Н  |

| Table | 2. | Status | Flags |

|-------|----|--------|-------|

|-------|----|--------|-------|

$\dagger$  n = empty offset (default value = 7)

$\ddagger$  m = full offset (default value = 7)

## SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, SN74ACT72241L 512 $\times$ 9, 1024 $\times$ 9, 2048 $\times$ 9, AND 4096 $\times$ 9 SYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES

SCAS222 - FEBRUARY 1993 - REVISED JUNE 1993

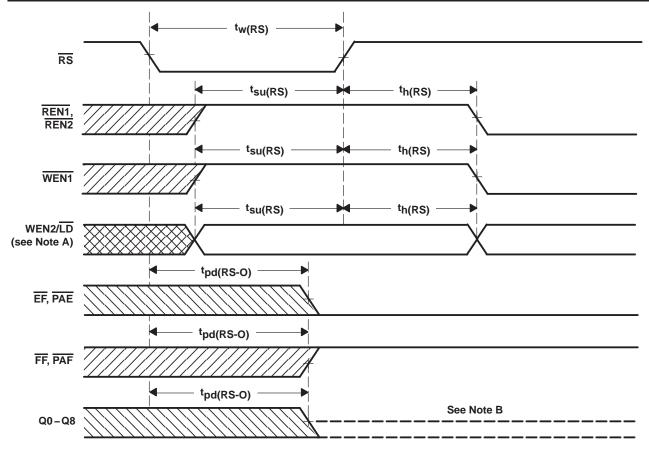

NOTES: A. Holding WEN2/LD high during reset makes it act as a second write enable. Holding WEN2/LD low during reset makes it act as a load enable for the programmable flag offset registers.

B. After reset, the outputs are low if OE is low and at the high-impedance level if OE is high.

C. The clocks (RCLK, WCLK) can be free running during reset.

Figure 2. Reset Timing

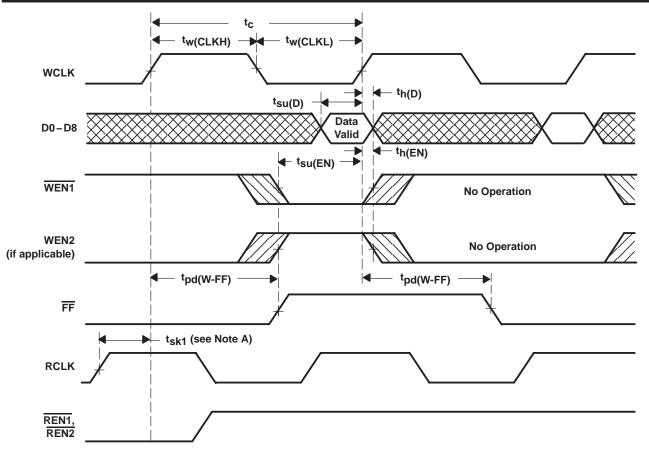

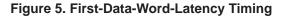

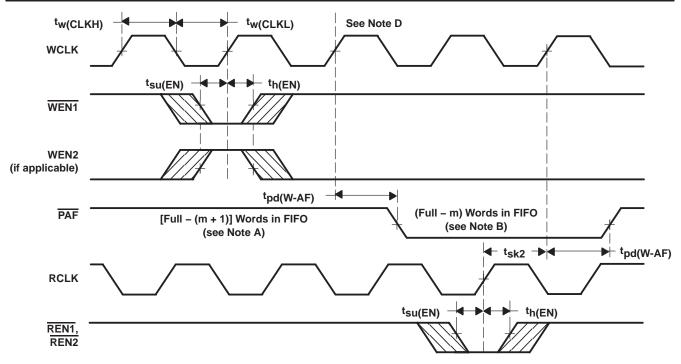

NOTE A: tsk1 is the minimum time between a rising RCLK edge and a subsequent rising WCLK edge for FF to change logic levels during the current clock cycle. If the time between the rising edge of RCLK and the subsequent rising edge of WCLK is less than t<sub>sk1</sub>, then FF may not change its logic level until the next WCLK rising edge.

#### Figure 3. Write-Cycle Timing

## SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, SN74ACT72241L 512 $\times$ 9, 1024 $\times$ 9, 2048 $\times$ 9, AND 4096 $\times$ 9 SYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES

SCAS222 - FEBRUARY 1993 - REVISED JUNE 1993

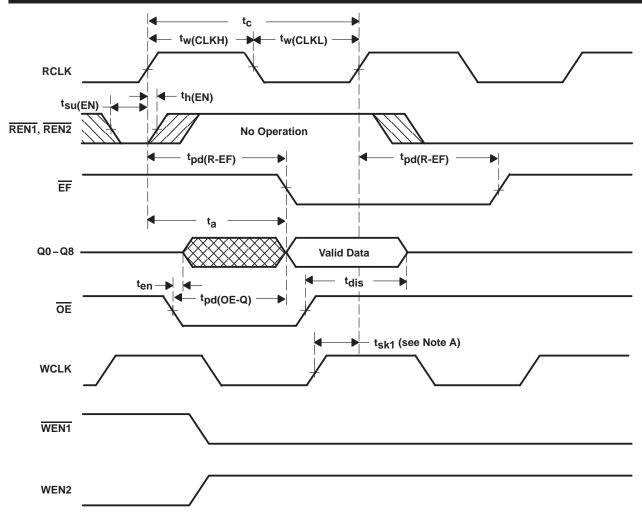

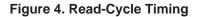

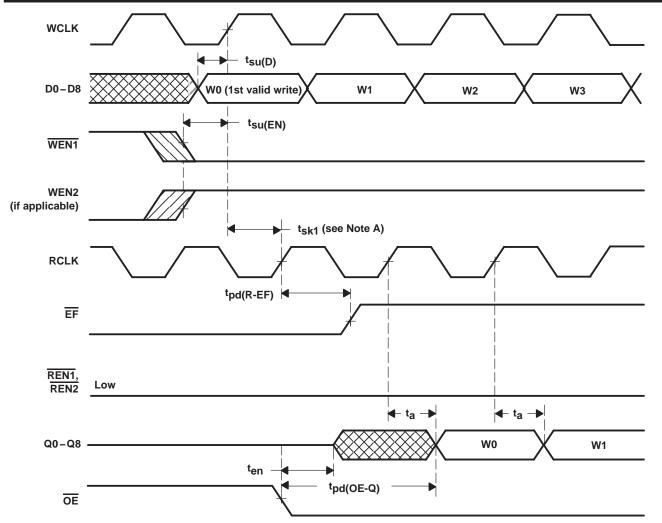

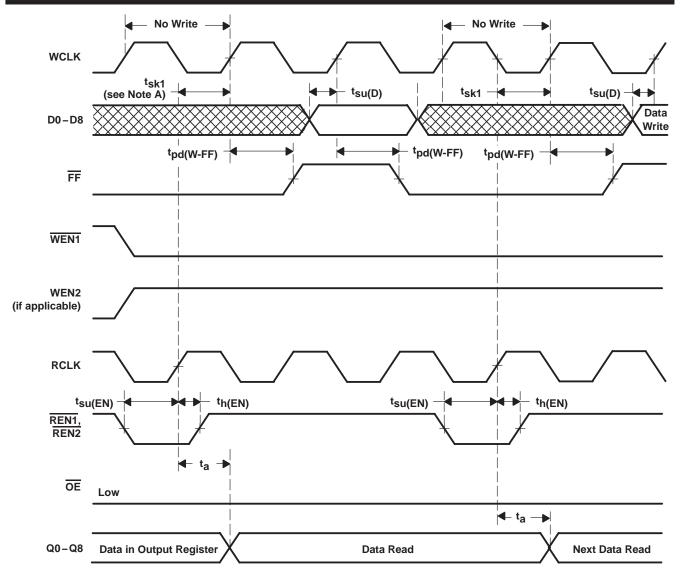

NOTE A: t<sub>sk1</sub> is the minimum time between a rising WCLK edge and a subsequent rising RCLK edge for EF to change logic levels during the current clock cycle. If the time between the rising edge of WCLK and the subsequent rising edge of RCLK is less than tsk1, then EF may not change its logic level until the next RCLK rising edge.

NOTE A: t<sub>sk1</sub> is the minimum time between a rising WCLK edge and a subsequent rising RCLK edge for EF to change during the current clock cycle. If the time between the rising edge of WCLK and the rising edge of RCLK is less than t<sub>sk1</sub>, then EF may not change state until the next RCLK edge.

NOTE A: tsk1 is the minimum time between a rising RCLK edge and a subsequent rising WCLK edge for FF to change logic levels during the current clock cycle. If the time between the rising edge of RCLK and the subsequent rising edge of WCLK is less than t<sub>sk1</sub>, then FF may not change its logic level until the next WCLK rising edge.

Figure 6. Full-Flag Timing

## SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, SN74ACT72241L 512 $\times$ 9, 1024 $\times$ 9, 2048 $\times$ 9, AND 4096 $\times$ 9 SYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES

SCAS222 - FEBRUARY 1993 - REVISED JUNE 1993

NOTE A: t<sub>sk1</sub> is the minimum time between a rising WCLK edge and a subsequent rising RCLK edge for EF to change logic levels during the current clock cycle. If the time between the rising edge of WCLK and the subsequent rising edge of RCLK is less than t<sub>sk1</sub>, then EF may not change its logic level until the next RCLK rising edge.

Figure 7. Empty-Flag Timing

## SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, SN74ACT72241L $512 \times 9$ , $1024 \times 9$ , $2048 \times 9$ , AND $4096 \times 9$ SYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES

SCAS222 - FEBRUARY 1993 - REVISED JUNE 1993

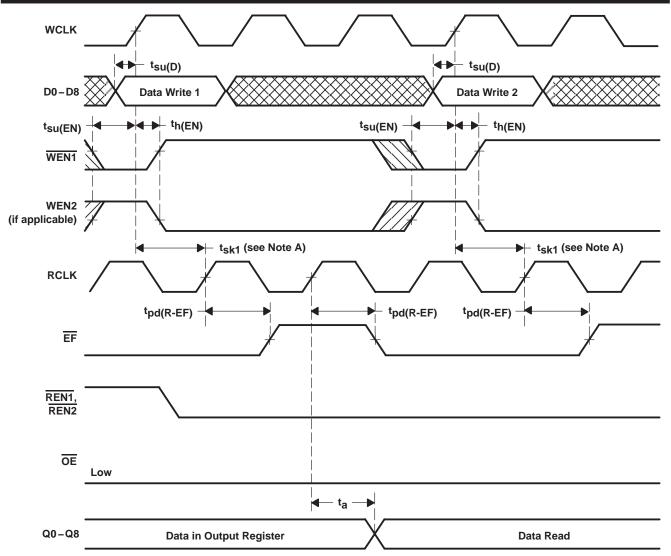

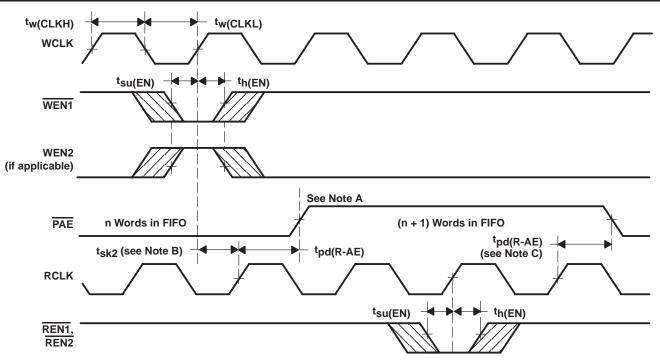

NOTES: A. PAF offset = m

B. (512 – m) words for SN74ACT72211L, (1024 – m) words for SN74ACT72221L, (2048 – m) words for SN74ACT72231L, (4096 – m) words for SN74ACT72241L

- C. t<sub>Sk2</sub> is the minimum time between a rising RCLK edge and the subsequent rising WCLK edge for PAF to change its logic level during that clock cycle. If the time between the rising edge of RCLK and the subsequent rising edge of WCLK is less than t<sub>sk2</sub>, then PAF may not change its logic level until the next WCLK rising edge.

- D. If a write is performed on this rising edge of the write clock, there will be [Full (m 1)] words in the FIFO when PAF goes low.

Figure 8. Programmable Almost-Full Flag Timing

- NOTES: A. PAE offset = n

- B. t<sub>sk2</sub> is the minimum time between a rising WCLK edge and the subsequent rising RCLK edge for PAE to change its logic level during that clock cycle. If the time between the rising edge of WCLK and the subsequent rising edge of RCLK is less than tsk2, then PAE may not change its logic level until the next RCLK rising edge.

- C. If a write is performed on this rising edge of the write clock, there will be [Empty + (n 1)] words in the FIFO when  $\overline{PAE}$  goes low.

Figure 9. Programmable Almost-Empty Flag Timing

## SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, SN74ACT72241L 512 $\times$ 9, 1024 $\times$ 9, 2048 $\times$ 9, AND 4096 $\times$ 9 SYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES

SCAS222 - FEBRUARY 1993 - REVISED JUNE 1993

Figure 11. Read-Offset-Registers Timing

## SN74ACT72211L, SN74ACT72221L, SN74ACT72231L, SN74ACT72241L 512 $\times$ 9, 1024 $\times$ 9, 2048 $\times$ 9, AND 4096 $\times$ 9 SYNCHRONOUS FIRST-IN, FIRST-OUT MEMORIES

SCAS222 – FEBRUARY 1993 – REVISED JUNE 1993

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub> (see Note 1)          | –0.5 V to 7 V  |

|-------------------------------------------------------------|----------------|

| Input voltage range, any input, V <sub>I</sub> (see Note 1) | –0.5 V to 7 V  |

| Continuous output current, I <sub>O</sub>                   | ±50 mA         |

| Voltage applied to a disabled 3-state output                | 5.5 V          |

| Operating free-air temperature range, T <sub>A</sub>        | 0°C to 70°C    |

| Storage temperature range under bias                        | –55°C to 125°C |

| Storage temperature range                                   | –55°C to 125°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to GND.

### recommended operating conditions

|          |                                | MIN | NOM | MAX | UNIT |

|----------|--------------------------------|-----|-----|-----|------|

| VCC      | Supply voltage                 | 4.5 | 5   | 5.5 | V    |

| VIH      | High-level input voltage       | 2   |     |     | V    |

| $V_{IL}$ | Low-level input voltage        |     |     | 0.8 | V    |

| IOH      | High-level output current      |     |     | -2  | mA   |

| IOL      | Low-level output current       |     |     | 8   | mA   |

| TA       | Operating free-air temperature | 0   |     | 70  | °C   |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                     |                             | MIN                                                                | MAX | UNIT             |    |

|------------------|-------------------------------|-----------------------------|--------------------------------------------------------------------|-----|------------------|----|

| VOH              | High-level output voltage     | $V_{CC} = 4.5 V,$           | I <sub>OH</sub> = – 2 mA                                           | 2.4 |                  | V  |

| VOL              | Low-level output voltage      | $V_{CC} = 4.5 V,$           | I <sub>OL</sub> = 8 mA                                             |     | 0.4              | V  |

| lj               | Input current                 | $V_{CC} = 5.5 V,$           | $V_{I} = V_{CC} \text{ or } 0 V$                                   |     | ±1               | μΑ |

| IOZ              | High-impedance output current | $V_{CC} = 5.5 V,$           | AO = ACC  or  0 A                                                  |     | ±10              | μΑ |

| C <sub>i</sub> ‡ | Input capacitance             | $V_{I} = 0,$                | f = 1 MHz                                                          |     | 10               | pF |

| Co‡              | Output capacitance            | $V_{O} = 0,$                | $f = 1 \text{ MHz}, \qquad \overline{\text{OE}} \ge V_{\text{IH}}$ |     | 10               | pF |

|                  |                               |                             | SN74ACT72211L                                                      |     | 140§             |    |

| Icc¶             | Active supply current         | f <sub>clock</sub> = 20 MHz | SN74ACT72221L, SN74ACT72231L,<br>SN74ACT72241L                     |     | 160 <sup>#</sup> | mA |

<sup>‡</sup> Specified by design but not tested

$I_{CC}$  measurements are made with outputs open (only capacitive loading). Typical I<sub>CC</sub> = 65 + (f<sub>clock</sub> × 1.1/MHz) + (f<sub>clock</sub> × C<sub>L</sub> × 0.03/MHz-pF) mA (C<sub>L</sub> = external capacitive load).

The I<sub>CC</sub> limits are valid for  $t_c = 15$ , 20, 25, and 50 ns.

<sup>#</sup> I<sub>CC</sub> measurements are made with outputs open (only capacitive loading). Typical I<sub>CC</sub> = 80 + ( $f_{clock} \times 2.1/MHz$ ) + ( $f_{clock} \times C_L \times 0.03/MHz$ -pF) mA ( $C_L$  = external capacitive load).

timing requirements over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Figures 2 through 13)

|                      |                                                                                                                                                  | 'ACT72211L-15<br>'ACT72221L-15<br>'ACT72231L-15<br>'ACT72241L-15 |   | 'ACT72211L-20<br>'ACT72221L-20<br>'ACT72231L-20<br>'ACT72241L-20 |     | 'ACT72211L-25<br>'ACT72221L-25<br>'ACT72231L-25<br>'ACT72241L-25 |     | 'ACT72211L-50<br>'ACT72221L-50<br>'ACT72231L-50<br>'ACT72241L-50 |     | UNIT |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---|------------------------------------------------------------------|-----|------------------------------------------------------------------|-----|------------------------------------------------------------------|-----|------|

|                      |                                                                                                                                                  | MIN MA                                                           | Х | MIN                                                              | MAX | MIN                                                              | MAX | MIN                                                              | MAX |      |

| fclock               | Clock frequency, RCLK or WCLK                                                                                                                    | 66.                                                              | 7 |                                                                  | 50  |                                                                  | 40  |                                                                  | 20  | MHz  |

| t <sub>C</sub>       | Clock cycle time, RCLK or WCLK                                                                                                                   | 15†                                                              |   | 20                                                               |     | 25                                                               |     | 50                                                               |     | ns   |

| <sup>t</sup> w(CLKH) | Pulse duration, RCLK or WCLK high                                                                                                                | 6                                                                |   | 8                                                                |     | 10                                                               |     | 20                                                               |     | ns   |

| <sup>t</sup> w(CLKL) | Pulse duration, RCLK or WCLK low                                                                                                                 | 6                                                                |   | 8                                                                |     | 10                                                               |     | 20                                                               |     | ns   |

| <sup>t</sup> w(RS)   | Pulse duration, RS low                                                                                                                           | 15                                                               |   | 20                                                               |     | 25                                                               |     | 50                                                               |     | ns   |

| <sup>t</sup> su(D)   | Setup time, D0-D8 before RCLK↑                                                                                                                   | 4                                                                |   | 5                                                                |     | 6                                                                |     | 10                                                               |     | ns   |

| <sup>t</sup> su(EN)  | Setup time, WEN1, WEN2 <sup>‡</sup> , and<br>LD§ before WCLK1; REN1, REN2,<br>and LD§ before RCLK1                                               | 4                                                                |   | 5                                                                |     | 6                                                                |     | 10                                                               |     | ns   |

| <sup>t</sup> su(RS)  | Setup time, <u>REN1</u> , <u>REN2</u> , <u>WEN1</u> ,<br>and WEN2/LD before RS high                                                              | 15                                                               |   | 20                                                               |     | 25                                                               |     | 50                                                               |     | ns   |

| <sup>t</sup> h(D)    | Hold time, D0-D8 after RCLK↑                                                                                                                     | 1                                                                |   | 1                                                                |     | 1                                                                |     | 2                                                                |     | ns   |

| <sup>t</sup> h(EN)   | Hold time, WEN1, WEN2 <sup>‡</sup> , and<br>LD <sup>§</sup> after WCLK <sup>↑</sup> ; REN1, REN2,<br>and LD <sup>§</sup> after RCLK <sup>↑</sup> | 1                                                                |   | 1                                                                |     | 1                                                                |     | 2                                                                |     | ns   |

| <sup>t</sup> h(RS)   | Hold time, REN1, REN2, WEN1, and WEN2/LD after RS high                                                                                           | 15                                                               |   | 20                                                               |     | 25                                                               |     | 50                                                               |     |      |

| <sup>t</sup> sk1     | Skew time between RCLK <sup>↑</sup> and<br>WCLK <sup>↑</sup> to allow EF or FF to<br>change logic levels during the<br>current clock cycle       | 6                                                                |   | 8                                                                |     | 10                                                               |     | 15                                                               |     | ns   |

| <sup>t</sup> sk2     | Skew time between RCLK <sup>↑</sup> and<br>WCLK <sup>↑</sup> to allow PAF or PAE to<br>change logic levels during the<br>current clock cycle     | 28                                                               |   | 35                                                               |     | 40                                                               |     | 45                                                               |     | ns   |

<sup>†</sup> Valid for PAE or PAF program values as follows:

$\leq$  63 bytes from the respective boundary for the SN74ACT72211L;

≤ 511 bytes from the respective boundary for the SN74ACT72221L/-72231L/-72241L;

minimum  $t_c$  is 20 ns for program values greater than those indicated above.

<sup>‡</sup> Applicable when the device is configured with two write-enable inputs (WEN2/ $\overline{LD}$  = WEN2).

§ Applicable when the device is configured to have programmable flags (WEN2/ $\overline{LD} = \overline{LD}$ ).

#### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Figures 2 through 13)

| -                     | •                                                                                               |                  | -                                        |                                    | -   |                                                                  |     |                                                                  |     |      |

|-----------------------|-------------------------------------------------------------------------------------------------|------------------|------------------------------------------|------------------------------------|-----|------------------------------------------------------------------|-----|------------------------------------------------------------------|-----|------|

| PARAMETER             |                                                                                                 | ´ΑCT72<br>´ΑCT72 | 211L-15<br>221L-15<br>231L-15<br>241L-15 | 5 'ACT72221L-20<br>5 'ACT72231L-20 |     | 'ACT72211L-25<br>'ACT72221L-25<br>'ACT72231L-25<br>'ACT72241L-25 |     | 'ACT72211L-50<br>'ACT72221L-50<br>'ACT72231L-50<br>'ACT72241L-50 |     | UNIT |

|                       |                                                                                                 | MIN              | MAX                                      | MIN                                | MAX | MIN                                                              | MAX | MIN                                                              | MAX |      |

| ta                    | Access time, RCLK↑ to Q0−Q8 valid                                                               | 2                | 10                                       | 2                                  | 12  | 3                                                                | 15  | 3                                                                | 25  | ns   |

| <sup>t</sup> pd(OE-Q) | Propagation delay time, $\overline{OE}$ low to $Q0 - Q8$ valid                                  | 3                | 8                                        | 3                                  | 10  | 3                                                                | 13  | 3                                                                | 28  | ns   |

| <sup>t</sup> pd(R-EF) | Propagation delay time, RCLK↑ to<br>EF low or high                                              |                  | 10                                       |                                    | 12  |                                                                  | 15  |                                                                  | 30  | ns   |

| <sup>t</sup> pd(W-FF) | Propagation delay time, WCLK↑ to<br>FF low or high                                              |                  | 10                                       |                                    | 12  |                                                                  | 15  |                                                                  | 30  | ns   |

| <sup>t</sup> pd(R-AE) | Propagation delay time, RCLK↑ to<br>PAE low or high                                             |                  | 10                                       |                                    | 12  |                                                                  | 15  |                                                                  | 30  | ns   |

| <sup>t</sup> pd(W-AF) | Propagation delay time, WCLK↑ to<br>PAF low or high                                             |                  | 10                                       |                                    | 12  |                                                                  | 15  |                                                                  | 30  | ns   |

| <sup>t</sup> pd(RS-O) | Propagation delay time, $\overline{RS}$ low to<br>FF and PAF high and EF, PAE, and<br>Q0-Q8 low |                  | 15                                       |                                    | 20  |                                                                  | 25  |                                                                  | 50  | ns   |

| t <sub>en</sub>       | Enable time, $\overline{OE}$ low to Q0–Q8 at the low-impedance level <sup>†</sup>               | 0                |                                          | 0                                  |     | 0                                                                |     | 0                                                                |     | ns   |

| <sup>t</sup> dis      | Disable time,                                                                                   | 3                | 8                                        | 3                                  | 10  | 3                                                                | 13  | 3                                                                | 28  | ns   |

<sup>†</sup> These values are characterized but not tested.

## APPLICATION INFORMATION

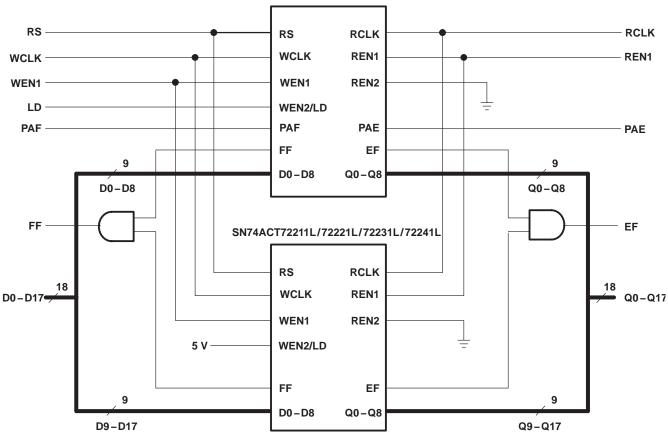

#### width-expansion configuration

Word width is increased by connecting the corresponding input control signals of multiple devices. Composite empty and full flags should be created by monitoring all devices in width expansion. Almost-full and almost-empty status can be obtained from any one device. Figure 12 shows an 18-bit-wide data path formed by using two SN74ACT72211L/72221L/72231L/72241L devices.

In Figure 12, read enable 2 (REN2) is grounded and read enable 1 (REN1) acts as the only read control. The write enable 2/load (WEN2/LD) input of only one device is set low at reset to configure the device for programmable flags and to have it act as a load control for reading and writing the programmable flag offset registers.

SN74ACT72211L/72221L/72231L/72241L

Figure 12. Word-Width Expansion for 512/1024/2048/4096  $\times$  18 FIFO

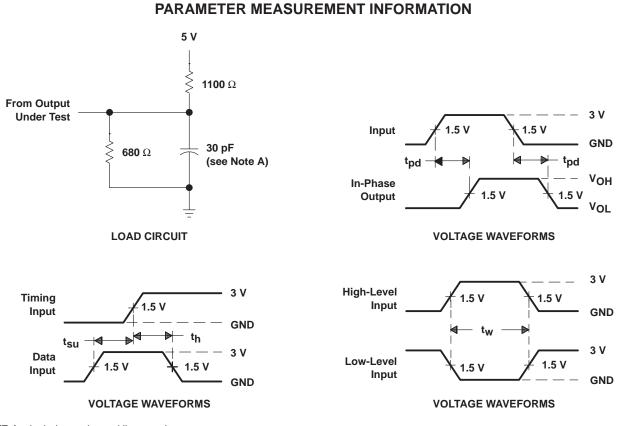

NOTE A: Includes probe and jig capacitance

Figure 13. Load Circuit and Voltage Waveforms

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                         | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Clocks and Timers           | www.ti.com/clocks      | Digital Control    | www.ti.com/digitalcontrol |

| Interface                   | interface.ti.com       | Medical            | www.ti.com/medical        |

| Logic                       | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt                  | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers            | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                        | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video & Imaging    | www.ti.com/video          |

|                             |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated