### Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

April 2014

# FSB127AH mWSaver™ Fairchild Power Switch (FPS™)

#### **Features**

### mWSaver™ Technology

- Achieves Low No-Load Power Consumption:

< 40 mW at 230 V<sub>AC</sub> (EMI Filter Loss Included)

- Meets 2013 ErP Standby Power Regulation (< 0.5 W Consumption with 0.25 W Load) for ATX Power and LCD TV Power

- Eliminates X-Cap Discharge Resistor Loss with Ax-CAP® Technology

- Linearly Decreases Switching Frequency at Light-Load Condition and Advanced Burst Mode Operation at No-Load Condition

- 700 V High-Voltage JFET Startup Circuit Eliminates Startup Resistor Loss

### **Highly Integrated with Rich Features**

- Internal Avalanche-Rugged 700 V SenseFET

- Built-in 5 ms Soft-Start

- Peak-Current-Mode Control

- Cycle-by-Cycle Current Limiting

- Leading-Edge Blanking (LEB)

- Synchronized Slope Compensation

- Proprietary Asynchronous Jitter to Reduce EMI

### **Advanced Protection**

- Internal Overload / Open-Loop Protection (OLP)

- V<sub>DD</sub> Under-Voltage Lockout (UVLO)

- V<sub>DD</sub> Over-Voltage Protection (OVP)

- Constant Power Limit (Full AC Input Range)

- Internal Auto-Restart Circuit (OLP, V<sub>DD</sub> OVP, OTP)

- Internal OTP Sensor with Hysteresis

- Adjustable Peak Current Limit

### Description

The FSB127AH next-generation, Green-Mode, Fairchild Power Switch (FPS™) incorporates Fairchild's innovative mWSaver™ technology, which dramatically reduces standby and no-load power consumption, enabling conformance to all worldwide Standby Mode efficiency guidelines. It integrates an advanced current-mode Pulse Width Modulator (PWM) and an avalancherugged 700 V SenseFET in a single package, allowing auxiliary power designs with higher standby energy efficiency, reduced size, improved reliability, and lower system cost than previous solutions.

Fairchild Semiconductor's mWSaver™ technology offers best-in-class minimum no-load and light-load power consumption. An innovative Ax-CAP® method, one of the five proprietary mWSaver™ technologies, minimizes losses in the EMI filter stage by eliminating the X-Cap discharge resistors while still meeting IEC61010-1 safety requirements. mWSaver™ Green Mode gradually decreases switching frequency as load decreases to minimize switching losses.

A new proprietary asynchronous jitter decreases EMI emission. Built-in synchronized slope compensation allows stable peak-current-mode control over a wide range of input voltage. The proprietary internal line compensation ensures constant-output power limit over the entire universal line voltage range.

Requiring minimum external components, FSB127AH provides a solid platform for cost-effective flyback converter design with low standby power consumption.

### **Applications**

General-purpose switched-mode power supplies (SMPS) and flyback power converters, including:

- Auxiliary Power Supply for PC, Server, LCD TV, and Game Console

- SMPS for VCR, SVR, STB, DVD, and DVCD Player, Printer, Facsimile, and Scanner

- General Adapter

- LCD Monitor Power / Open-Frame SMPS

### **Ordering Information**

| Part Number | SenseFET  | Operating<br>Temperature Range | Package                          | Packing Method |

|-------------|-----------|--------------------------------|----------------------------------|----------------|

| FSB127AHN   | 2 A 700 V | -40°C to +105°C                | 8-Pin, Dual Inline Package (DIP) | Tube           |

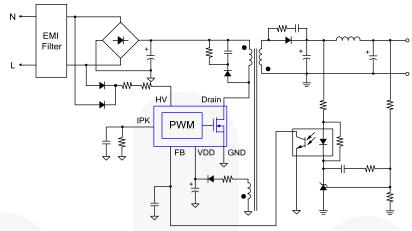

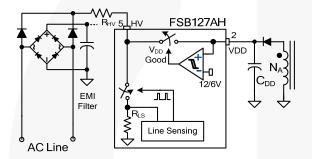

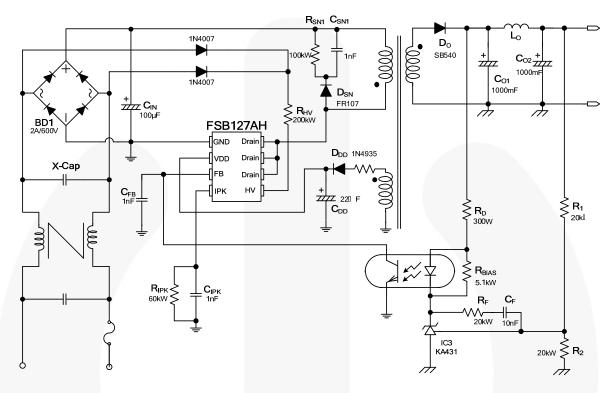

### **Application Diagram**

Figure 1. Typical Flyback Application

### Output Power Table(1)

| Draduat  | 230 V <sub>AC</sub> ±15% <sup>(2)</sup>             |      | 85-265 V <sub>AC</sub> |                           |  |

|----------|-----------------------------------------------------|------|------------------------|---------------------------|--|

| Product  | Adapter <sup>(3)</sup> Open-Frame <sup>(4)</sup> Ad |      | Adapter <sup>(3)</sup> | Open-Frame <sup>(4)</sup> |  |

| FSB127AH | 14 W                                                | 20 W | 11 W                   | 16 W                      |  |

#### Notes:

- 1. The maximum output power can be limited by junction temperature.

- 2. 230 V<sub>AC</sub> or 100/115 V<sub>AC</sub> with voltage doublers.

- 3. Typical continuous power in a non-ventilated enclosed adapter, with sufficient drain pattern of printed circuit board (PCB) as a heat sink, at 50°C ambient.

- 4. Maximum practical continuous power in an open-frame, design with sufficient drain pattern of printed circuit board (PCB) as a heat sink, at 50°C ambient.

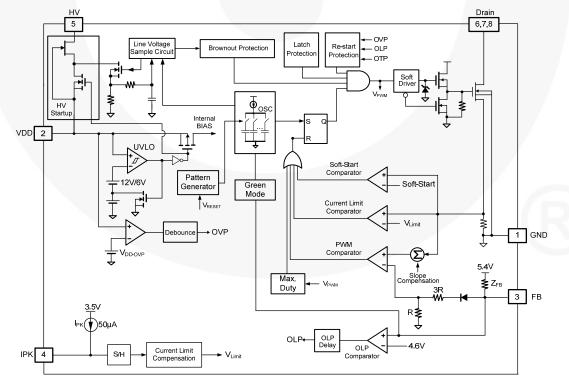

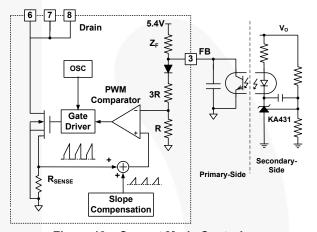

### **Block Diagram**

Figure 2. Internal Block Diagram

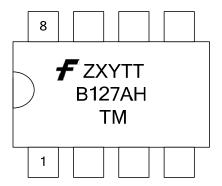

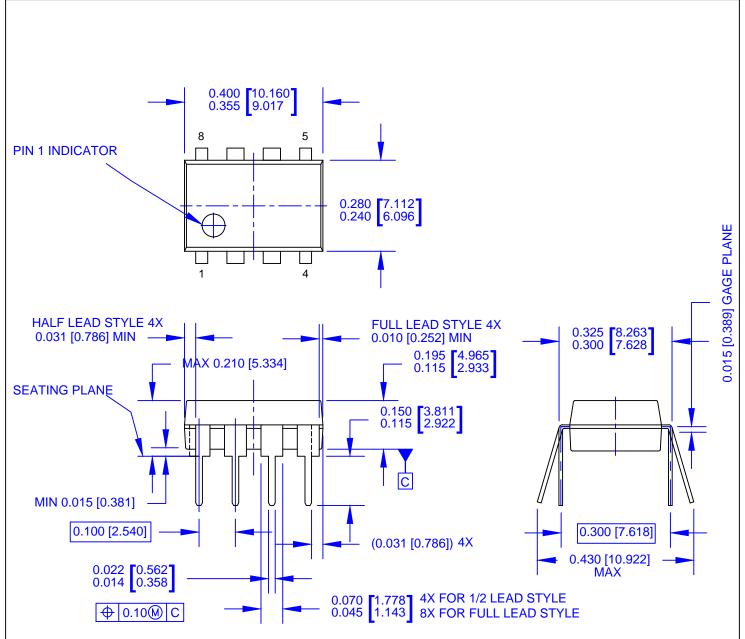

### **Pin Configuration**

F – Fairchild Logo

Z – Plant Code

X – 1-Digit Year Code

Y – 1-Digit Week Code

TT – 2-Digit Die Run Code

T – Package Type (N: DIP) M – Manufacture Flow Code

Figure 3. Pin Configuration

### **Pin Definitions**

| Pin# | Name  | Description                                                                                                                                                                                                                                                                                                                              |

|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | GND   | <b>Ground</b> . This pin internally connects to the SenseFET source and the signal ground of the PWM controller.                                                                                                                                                                                                                         |

| 2    | VDD   | <b>Supply Voltage of the IC</b> . Typically the hold-up capacitor connects from this pin to ground. A rectifier diode in series with the transformer auxiliary winding connects to this pin to supply bias during normal operation.                                                                                                      |

| 3    | FB    | <b>Feedback</b> . The signal from the external compensation circuit connects to this pin. The PWM duty cycle is determined by comparing the signal on this pin and the internal current-sense signal.                                                                                                                                    |

| 4    | IPK   | <b>Adjust Peak Current</b> . Typically a resistor connects from this pin to the GND pin to program the current-limit level. The internal current source (50 μA) introduces voltage drop across the resistor, which determines the current-limit level of pulse-by-pulse current limit.                                                   |

| 5    | HV    | <b>Startup</b> . Typically, resistors in series with diodes from the AC line connect to this pin to supply internal bias and to charge the external capacitor connected between the VDD pin and the GND pin during startup. This pin is also used to sense the line voltage for brownout protection and AC line disconnection detection. |

| 6    |       |                                                                                                                                                                                                                                                                                                                                          |

| 7    | Drain | SenseFET Drain. This pin is designed to directly drive the transformer.                                                                                                                                                                                                                                                                  |

| 8    |       |                                                                                                                                                                                                                                                                                                                                          |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol             | Parame                                        | eter                                 | Min.                                 | Max. | Unit |

|--------------------|-----------------------------------------------|--------------------------------------|--------------------------------------|------|------|

| V <sub>DRAIN</sub> | Drain Pin Voltage <sup>(5,6)</sup>            |                                      |                                      | 700  | V    |

| I <sub>DM</sub>    | Drain Current Pulsed <sup>(7)</sup>           |                                      |                                      | 8    | Α    |

| E <sub>AS</sub>    | Single Pulsed Avalanche Energy <sup>(8)</sup> |                                      | 140                                  | mJ   |      |

| $V_{DD}$           | DC Supply Voltage                             |                                      |                                      | 30   | V    |

| V <sub>FB</sub>    | FB Pin Input Voltage                          |                                      | -0.3                                 | 7.0  | V    |

| $V_{IPK}$          | IPK Pin Input Voltage                         |                                      | -0.3                                 | 7.0  | V    |

| V <sub>HV</sub>    | HV Pin Input Voltage                          |                                      |                                      | 700  | V    |

| P <sub>D</sub>     | Power Dissipation (T <sub>A</sub> < 50°C)     |                                      | 1.5                                  | W    |      |

| TJ                 | Operating Junction Temperature                | -40                                  | Internally<br>Limited <sup>(9)</sup> | °C   |      |

| T <sub>STG</sub>   | Storage Temperature Range                     |                                      | -55                                  | +150 | °C   |

| $T_L$              | Lead Soldering Temperature (Wave              | Soldering or IR, 10 Seconds)         |                                      | +260 | °C   |

|                    | Electrostatic Discharge Capability,           | Human Body Model:<br>JESD22-A114     | 5.50                                 |      |      |

| ECD                | All Pins Except HV Pin                        | Charged Device Model:<br>JESD22-C101 | 2.00                                 |      | 147  |

| ESD -              | Electrostatic Discharge Capability,           | Human Body Model:<br>JESD22-A114     | 3.00                                 |      | kV   |

|                    | All Pins Including HV Pin                     | Charged Device Model:<br>JESD22-C101 | 1.25                                 |      |      |

#### Notes:

- 5. All voltage values, except differential voltages, are given with respect to the network ground terminal.

- 6. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

- Non-repetitive rating: pulse width is limited by the maximum junction temperature.

- 8. L = 51 mH, starting T<sub>J</sub> = 25°C.

- 9. Internally limited by Over-Temperature Protection (OTP) (refer to  $T_{OTP}$ ).

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter                                                 | Min. | Max. | Unit |

|-----------------|-----------------------------------------------------------|------|------|------|

| R <sub>HV</sub> | Resistor Connect to HV Pin for Full Range Input Detection | 150  | 250  | kΩ   |

#### **Thermal Resistance Table**

| Symbol        | Parameter                                              | Тур. | Unit |

|---------------|--------------------------------------------------------|------|------|

| $\theta_{JA}$ | Junction-to-Air Thermal Resistance                     | 86   | °C/W |

| Ψлт           | Junction-to-Package Thermal Resistance <sup>(10)</sup> | 20   | °C/W |

#### Note:

10. Measured on the package top surface.

### **Electrical Characteristics**

$V_{DD}$ =15 V and  $T_A$ =25°C unless otherwise specified.

| Symbol                  | Parameter                                                                      | Condition                                                                        | Min. | Тур. | Max. | Unit |

|-------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|------|

| SenseFET                | Section <sup>(11)</sup>                                                        |                                                                                  |      |      |      |      |

| BV <sub>DSS</sub>       | Drain-Source Breakdown Voltage                                                 | V <sub>DS</sub> = 700 V, V <sub>GS</sub> = 0 V                                   | 700  |      |      | V    |

|                         |                                                                                | V <sub>DS</sub> = 700 V, V <sub>GS</sub> = 0 V                                   |      |      | 50   |      |

| $I_{DSS}$               | Zero-Gate-Voltage Drain Current                                                | $V_{DS} = 560 \text{ V}, V_{GS} = 0 \text{ V},$<br>$T_{C} = 125^{\circ}\text{C}$ |      |      | 200  | μA   |

| R <sub>DS(ON)</sub>     | Drain-Source On-State Resistance <sup>(11)</sup>                               | $V_{GS} = 10 \text{ V}, I_D = 0.5 \text{ A}$                                     |      | 6.0  | 7.2  | Ω    |

| C <sub>ISS</sub>        | Input Capacitance                                                              | $V_{GS} = 0V$ , $V_{DS} = 25 V$ , $f = 1 MHz$                                    |      | 550  | 715  | pF   |

| Coss                    | Output Capacitance                                                             | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 25 V,<br>f = 1 MHz                      |      | 38   | 50   | pF   |

| C <sub>RSS</sub>        | Reverse Transfer Capacitance                                                   | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 25 V,<br>f = 1 MHz                      |      | 17   | 26   | pF   |

| t <sub>d(on)</sub>      | Turn-On Delay                                                                  | $V_{DS} = 350 \text{ V}, I_{D} = 1.0 \text{ A}$                                  |      | 20   | 50   | ns   |

| t <sub>r</sub>          | Rise Time                                                                      | V <sub>DS</sub> = 350 V, I <sub>D</sub> = 1.0 A                                  |      | 15   | 40   | ns   |

| $t_{\text{d(off)}}$     | Turn-Off Delay                                                                 | $V_{DS} = 350 \text{ V}, I_{D} = 1.0 \text{ A}$                                  |      | 55   | 120  | ns   |

| t <sub>f</sub>          | Fall Time                                                                      | $V_{DS} = 350 \text{ V}, I_{D} = 1.0 \text{ A}$                                  |      | 25   | 60   | ns   |

| Control Sec             | ction                                                                          |                                                                                  |      |      |      |      |

| V <sub>DD</sub> Section | 1                                                                              |                                                                                  |      |      |      |      |

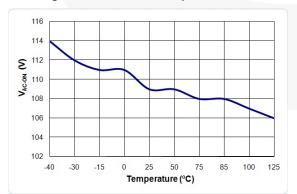

| $V_{DD\text{-}ON}$      | UVLO Start Threshold Voltage                                                   |                                                                                  | 11   | 12   | 13   | V    |

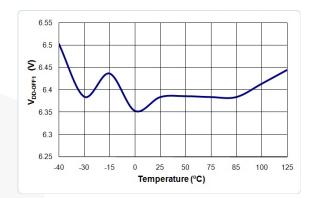

| V <sub>DD-OFF1</sub>    | UVLO Stop Threshold Voltage                                                    |                                                                                  | 5    | 6    | 7    | V    |

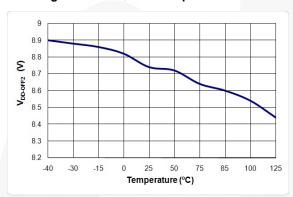

| $V_{\text{DD-OFF2}}$    | I <sub>DD-OLP</sub> Enable Threshold Voltage                                   |                                                                                  | 8    | 9    | 10   | V    |

| $V_{\text{DD-OLP}}$     | V <sub>DD</sub> Voltage Threshold for HV Startup<br>Turn-On at Protection Mode |                                                                                  | 5    | 6    | 7    | V    |

| I <sub>DD-ST</sub>      | Startup Supply Current                                                         | V <sub>DD-ON</sub> – 0.16 V                                                      |      |      | 30   | μΑ   |

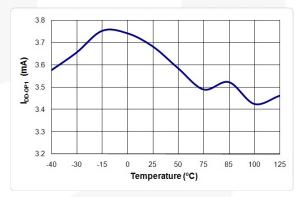

| I <sub>DD-OP1</sub>     | Operating Supply Current with Normal Switching Operation                       | V <sub>DD</sub> =15 V, V <sub>FB</sub> =3 V                                      |      |      | 3.8  | mA   |

| I <sub>DD-OP2</sub>     | Operating Supply Current without Switching Operation                           | V <sub>DD</sub> =15 V, V <sub>FB</sub> =1 V                                      |      |      | 1.8  | mA   |

| I <sub>DD-OLP</sub>     | Internal Sinking Current                                                       | V <sub>DD-OLP</sub> + 0.1 V                                                      | 30   | 60   | 90   | μA   |

| $V_{\text{DD-OVP}}$     | V <sub>DD</sub> Over-Voltage Protection                                        |                                                                                  | 27   | 28   | 29   | V    |

| t <sub>D-VDDOVP</sub>   | V <sub>DD</sub> Over-Voltage Protection<br>Debounce Time                       |                                                                                  | 70   | 140  | 210  | μs   |

| <b>HV Section</b>       |                                                                                |                                                                                  |      |      |      |      |

| $I_{HV}$                | Supply Current Drawn from HV Pin                                               | HV=120 $V_{DC}$ , $V_{DD}$ =0 $V$ with 10 $\mu F$                                | 1.5  |      | 5.0  | mA   |

| I <sub>HV-LC</sub>      | Leakage Current after Startup                                                  | HV=700 V, V <sub>DD</sub> =V <sub>DD</sub> -<br>OFF1+1 V                         |      |      | 10   | μA   |

| $V_{AC\text{-}ON}$      | Brown-in Threshold Level (V <sub>DC</sub> )                                    | DC Voltage Applied to                                                            | 110  | 114  | 118  | V    |

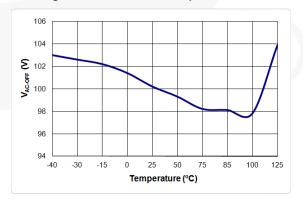

| $V_{AC\text{-}OFF}$     | Brownout Threshold Level (V <sub>DC</sub> )                                    | HV Pin Through 200 kΩ<br>Resistor                                                | 93   | 99   | 105  | V    |

| t <sub>UVP</sub>        | Brownout Protection Time                                                       |                                                                                  | 0.8  | 1.2  | 1.6  | s    |

Continued on the following page...

# **Electrical Characteristics** (Continued)

$V_{\text{DD}}\text{=}15~V$  and  $T_{\text{A}}\text{=}25^{\circ}\text{C}$  unless otherwise specified.

| Symbol                | Parameter                                                                            | Condition                                                 | Min.  | Тур.                           | Max.  | Unit   |

|-----------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------|-------|--------------------------------|-------|--------|

| Oscillator S          | ection                                                                               |                                                           |       |                                |       |        |

| £                     | Francisco Naminal Made                                                               | Center Frequency                                          | 94    | 100                            | 106   | La III |

| fosc                  | Frequency in Nominal Mode                                                            | Hopping Range                                             | ±4    | ±6                             | ±8    | kHz    |

| t <sub>HOP</sub>      | Hopping Period <sup>(11)</sup>                                                       |                                                           |       | 20                             |       | ms     |

| f <sub>OSC-G</sub>    | Green-Mode Frequency                                                                 |                                                           | 20    | 23                             | 26    | kHz    |

| $f_{DV}$              | Frequency Variation vs. V <sub>DD</sub><br>Deviation                                 | V <sub>DD</sub> =11 V to 22 V                             |       |                                | 5     | %      |

| f <sub>DT</sub>       | Frequency Variation vs. Temperature Deviation <sup>(11)</sup>                        | T <sub>A</sub> =-40 to 105°C                              |       |                                | 5     | %      |

| Feedback In           | put Section                                                                          |                                                           |       |                                |       |        |

| A <sub>V</sub>        | Internal Voltage Dividing Factor of FB Pin <sup>(11)</sup>                           |                                                           | 1/4.5 | 1/4.0                          | 1/3.5 | V/V    |

| Z <sub>FB</sub>       | Pull-Up Impedance of FB Pin                                                          |                                                           | 15    | 21                             | 27    | kΩ     |

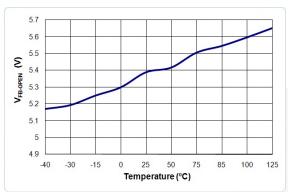

| V <sub>FB-OPEN</sub>  | FB Pin Pull-Up Voltage                                                               | FB Pin Open                                               | 5.2   | 5.4                            | 5.6   | V      |

| $V_{FB-OLP}$          | FB Voltage Threshold to Trigger Open-Loop Protection                                 |                                                           | 4.3   | 4.6                            | 4.9   | V      |

| t <sub>D-OLP</sub>    | Delay of FB Pin Open-Loop Protection                                                 |                                                           | 46    | 56                             | 66    | ms     |

| $V_{\text{FB-N}}$     | FB Voltage Threshold to Exit Green Mode                                              | V <sub>FB</sub> is Rising                                 | 2.4   | 2.6                            | 2.8   | V      |

| $V_{FB-G}$            | FB Voltage Threshold to Enter Green Mode                                             | V <sub>FB</sub> is Falling                                |       | V <sub>FB-N</sub> -<br>0.2     |       | V      |

| V <sub>FB-ZDC</sub>   | FB Voltage Threshold to Enter Zero-<br>Duty State                                    | V <sub>FB</sub> is Falling                                | 1.95  | 2.05                           | 2.15  | V      |

| V <sub>FB-ZDCR</sub>  | FB Voltage Threshold to Exit Zero-<br>Duty State                                     | V <sub>FB</sub> is Rising                                 |       | V <sub>FB-ZDC</sub><br>+0.1    |       | V      |

| IPK Pin Sec           | tion                                                                                 |                                                           |       |                                |       |        |

| V <sub>IPK-OPEN</sub> | IPK Pin Open Voltage                                                                 |                                                           | 3.0   | 3.5                            | 4.0   | V      |

| $V_{IPK-H}$           | Internal Upper Clamping Voltage of IPK Pin <sup>(11)</sup>                           |                                                           |       |                                | 3     | V      |

| V <sub>IPK-L</sub>    | Internal Lower Clamping Voltage of IPK Pin <sup>(11)</sup>                           |                                                           | 1.5   |                                |       | V      |

| I <sub>PK</sub>       | Internal Current Source of IPK Pin                                                   | T <sub>A</sub> =-40 to 105°C,<br>V <sub>IPK</sub> =2.25 V | 45    | 50                             | 55    | μA     |

| I <sub>LMT-FL-H</sub> | Flat Threshold Level of Current Limit for the Highest IPK Level                      | V <sub>IPK</sub> =3 V, Duty>40%                           | 0.90  | 1.00                           | 1.10  | Α      |

| I <sub>LMT-VA-H</sub> | Valley Threshold Level of Current<br>Limit for the Highest IPK Level <sup>(11)</sup> | V <sub>IPK</sub> =3 V, Duty=0%                            |       | I <sub>LMT-FL-Н</sub> -0.25    |       | Α      |

| I <sub>LMT-FL-L</sub> | Flat Threshold Level of Current Limit for the Lowest IPK Level                       | V <sub>IPK</sub> =1.5 V, Duty>40%                         | 0.45  | 0.50                           | 0.55  | Α      |

| I <sub>LMT-VA-L</sub> | Valley Threshold Level of Current<br>Limit for the Lowest IPK Level <sup>(11)</sup>  | V <sub>IPK</sub> =1.5 V, Duty=0%                          |       | I <sub>LMT-FL-L</sub><br>-0.12 |       | А      |

Continued on the following page...

### **Electrical Characteristics** (Continued)

$V_{DD}$ =15 V,  $T_A$ =25°C unless otherwise specified.

| Symbol             | Parameter                                           | Condition | Min. | Тур. | Max. | Unit |  |

|--------------------|-----------------------------------------------------|-----------|------|------|------|------|--|

| Current-Sen        | Current-Sense Section <sup>(12)</sup>               |           |      |      |      |      |  |

| t <sub>PD</sub>    | Current Limit Turn-Off Delay                        |           |      | 100  | 200  | ns   |  |

| t <sub>LEB</sub>   | Leading-Edge Blanking Time                          |           | 230  | 280  | 330  | ns   |  |

| t <sub>SS</sub>    | Soft-Start Time <sup>(11)</sup>                     |           |      | 5    |      | ms   |  |

| GATE Section       | on <sup>(12)</sup>                                  |           |      |      |      |      |  |

| DCY <sub>MAX</sub> | Maximum Duty Cycle                                  |           | 70   |      |      | %    |  |

| Over-Tempe         | rature Protection Section (OTP)                     |           | •    |      |      |      |  |

| T <sub>OTP</sub>   | Junction Temperature to trigger OTP <sup>(11)</sup> |           | 135  | 142  | 150  | °C   |  |

| $\Delta T_{OTP}$   | Hysteresis of OTP <sup>(11)</sup>                   |           |      | 25   |      | °C   |  |

- 11. Guaranteed by design; not 100% tested in production.

12. Pulse test: pulse width ≤ 300 μs, duty ≤ 2%.

13. These parameters, although guaranteed, are tested in wafer-sort process.

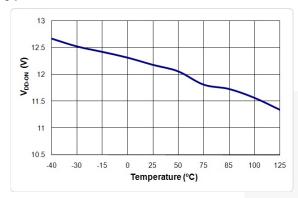

### **Typical Characteristics**

Figure 4. V<sub>DD-ON</sub> vs. Temperature

Figure 6. V<sub>DD-OFF2</sub> vs. Temperature

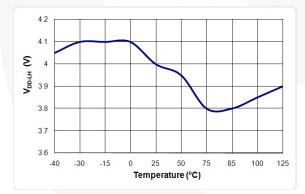

Figure 8. V<sub>DD-LH</sub> vs. Temperature

Figure 10. V<sub>AC-ON</sub> vs. Temperature

Figure 5. V<sub>DD-OFF1</sub> vs. Temperature

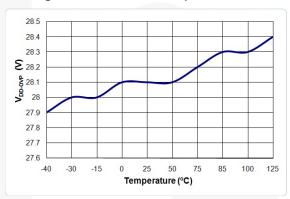

Figure 7. V<sub>DD-OVP</sub> vs. Temperature

Figure 9. IDD-OP1 vs. Temperature

Figure 11. V<sub>AC-OFF</sub> vs. Temperature

### **Typical Characteristics**

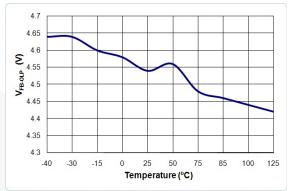

Figure 12. V<sub>FB-OPEN</sub> vs. Temperature

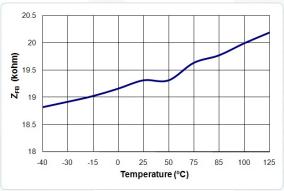

Figure 14. Z<sub>FB</sub> vs. Temperature

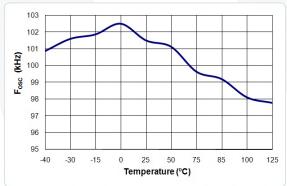

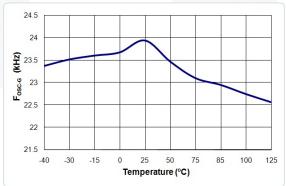

Figure 16. fosc vs. Temperature

Figure 13. V<sub>FB-OLP</sub> vs. Temperature

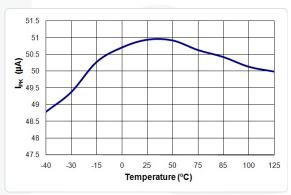

Figure 15. IPK vs. Temperature

Figure 17. f<sub>OSC-G</sub> vs. Temperature

### **Functional Description**

### **Startup Operation**

The HV pin is typically connected to the AC line input through two external diodes and one resistor ( $R_{HV}$ ), as shown in Figure 18. When the AC line voltage is applied, the  $V_{DD}$  hold-up capacitor is charged by the line voltage through the diodes and resistor. After  $V_{DD}$  voltage reaches the turn-on threshold voltage ( $V_{DD-ON}$ ), the startup circuit charging the  $V_{DD}$  capacitor is switched off and  $V_{DD}$  is supplied by the auxiliary winding of the transformer. Once the FSB127AH starts, it continues operation until  $V_{DD}$  drops below 6 V ( $V_{DD-OFF1}$ ). The IC startup time with a given AC line input voltage is:

$$t_{STARTUP} = R_{HV} \cdot C_{DD} \cdot \ln \frac{V_{AC-IN} \cdot \frac{2\sqrt{2}}{\pi}}{V_{AC-IN} \cdot \frac{2\sqrt{2}}{\pi} - V_{DD-ON}}$$

(1)

Figure 18. Startup Circuit

#### **Brown-in/out Function**

The HV pin can detect the AC line voltage using a switched voltage divider that consists of external resistor ( $R_{\text{HV}}$ ) and internal resistor ( $R_{\text{LS}}$ ), as shown in Figure 18. The internal line-sensing circuit detects the real RMS value of the line voltage using a sampling circuit and peak-detection circuit. Because the voltage divider causes power consumption when it is switched on, the switching is driven by a signal with a very narrow pulse width to minimize power loss. The sampling frequency is adaptively changed according to the load condition to minimize power consumption in light-load condition.

Based on the detected line voltage, brown-in and brownout thresholds are determined. Since the internal resistor ( $R_{LS}$ ) of the voltage divider is much smaller than  $R_{HV}$ , the thresholds are given as:

$$V_{BROWN-IN}(RMS) = \frac{R_{HV}}{200k} \cdot \frac{V_{AC-ON}}{\sqrt{2}}$$

(2)

$$V_{BROWN-OUT}(RMS) = \frac{R_{HV}}{200k} \cdot \frac{V_{AC-OFF}}{\sqrt{2}}$$

(3)

#### **PWM Control**

The FSB127AH employs current-mode control, as shown in Figure 19. An opto-coupler (such as the H11A817A) and shunt regulator (such as the KA431) are typically used to implement the feedback network. Comparing the feedback voltage with the voltage across the  $R_{\mathsf{SENSE}}$  resistor makes it possible to control the switching duty cycle. A synchronized positive slope is added to the SenseFET current information to guarantee stable current-mode control over a wide range of input voltage. The built-in slope compensation stabilizes the current loop and prevents sub-harmonic oscillation.

Figure 19. Current Mode Control

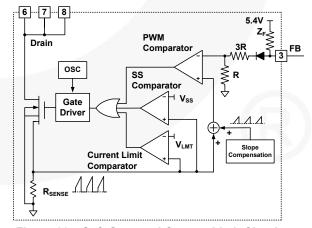

#### Soft-Start

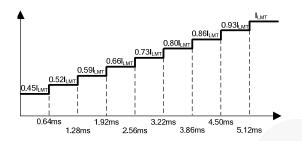

The internal soft-start circuit progressively increases the pulse-by-pulse current limit level of MOSFET during startup to establish the correct working conditions for transformers and capacitors, as shown in Figure 20. The current limit levels have nine steps, as shown in Figure 21. This prevents transformer saturation and reduces stress on the secondary diode during startup.

Figure 20. Soft-Start and Current-Limit Circuit

Figure 21. Current Limit Variation During Soft-Start

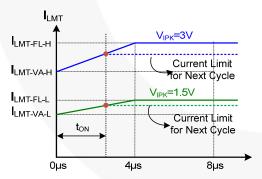

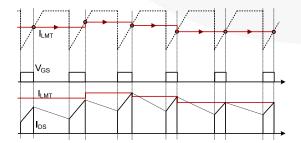

# Adjustable Peak Current Limit & H/L Line Compensation for Constant Power Limit

To make the limited output power constant, regardless of the line voltage condition, a special current-limit profile with sample and hold is used (as shown in Figure 22). The current-limit level is sampled and held at the falling edge of the gate drive signal, as shown in Figure 23. Then, the sampled current-limit level is used for the next switching cycle. The sample-and-hold function prevents sub-harmonic oscillation in current-mode control.

The current-limit level increases as the duty cycle increases, which reduces the current limit as duty cycle decreases. This allows a lower current-limit level for high-line voltage condition where the duty cycle is smaller than that of low line. Therefore, the limited maximum output power can remain constant even for a wide input voltage range.

The peak current limit is programmable using a resistor on the IPK pin. The internal 50  $\mu\text{A}$  current source for the IPK pin generates voltage drop across the resistor. The voltage of the IPK pin determines the current-limit level. Since the upper and lower clamping voltages of the IPK pin are 3 V and 1.5 V, respectively; the suggested resistor value is from 30 k $\Omega$  to 60 k $\Omega$ .

Figure 22. I<sub>LMT</sub> vs. PWM Turn-On Time

Figure 23. Current Limit Variation with Duty Cycle

### mWSaver™ Technology

### Ax-CAP® Elimination of X-Cap Discharge Resistors

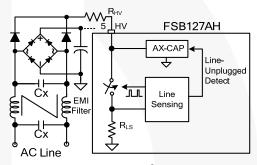

The EMI filter in the front end of the switched-mode power supply (SMPS) typically includes a capacitor across the AC line connector, as shown in Figure 24. Most of the safety regulations, such as UL 1950 and IEC61010-1, require the capacitor be discharged to a safe level within a given time after being unplugged from the power outlet. Typically a discharge resistor across the capacitor is used to ensure the capacitor is discharged naturally, which introduces power loss. As power level increases, the EMI filter capacitor tends to increase, requiring a smaller discharge resistor to maintain the same discharge time. This typically results in more power dissipation in high-power applications. The innovative Ax-CAP technology intelligently discharges the filter capacitor only when the power supply is unplugged from the power outlet. Since the Ax-CAP® discharge circuit is disabled in normal operation, the power loss in the EMI filter can be virtually removed.

Figure 24. Ax-CAP® Circuit

#### **Green Mode**

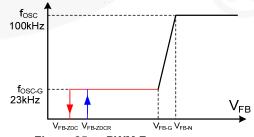

The FSB127AH modulates the PWM frequency as a function of FB voltage, as shown in Figure 25. Since the output power is proportional to the FB voltage in current-mode control, the switching frequency decreases as load decreases. In heavy-load conditions, the switching frequency is 100 kHz. Once  $V_{FB}$  decreases below  $V_{FB-N}$  (2.6 V), the PWM frequency linearly decreases from 100 kHz to 23 kHz to reduce switching losses at light-load condition. As  $V_{FB}$  decreases to  $V_{FB-G}$  (2.4 V), the switching frequency is fixed at 23 kHz.

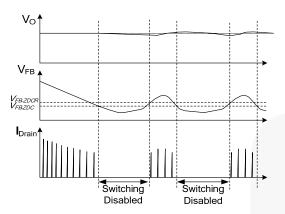

As  $V_{FB}$  falls below  $V_{FB-ZDC}$  (2.1 V), the FSB127AH enters Burst Mode, where PWM switching is disabled. Then the output voltage starts to drop, causing the feedback voltage to rise. Once  $V_{FB}$  rises above  $V_{FB-ZDCR}$ , switching resumes. Burst Mode alternately enables and disables switching, thereby reducing switching loss to reduce power consumption, as shown in Figure 26.

Figure 25. PWM Frequency

Figure 26. Burst-Mode Operation

#### **Protections**

Protection functions include Overload / Open-Loop Protection (OLP), Over-Voltage Protection (OVP), and Over-Temperature Protection (OTP). All the protections are implemented as Auto-Restart Mode. Once the fault condition is detected, switching is terminated and the SenseFET remains off. This causes  $V_{DD}$  to fall. When  $V_{DD}$  falls to 6 V, the protection is reset and HV startup circuit charges  $V_{DD}$  up to 12 V voltage, allowing restart.

#### Open-Loop / Overload Protection (OLP)

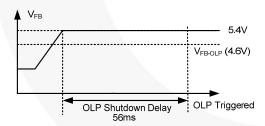

Because of the pulse-by-pulse current-limit capability, the maximum peak current through the SenseFET is limited and maximum input power is limited. If the output consumes more than the limited maximum power, the output voltage ( $V_O$ ) drops below the set voltage. Then the current through the opto-coupler LED and the transistor become virtually zero and FB voltage is pulled HIGH, as shown in Figure 27. If feedback voltage is above 4.6 V for longer than 56 ms, OLP is triggered. This protection is also triggered when the feedback loop is open due to a soldering defect.

Figure 27. OLP Operation

#### **V<sub>DD</sub> Over-Voltage Protection (OVP)**

If the secondary-side feedback circuit malfunctions or a solder defect causes an opening in the feedback path, the current through the opto-coupler transistor becomes virtually zero. Then feedback voltage climbs up in a similar manner to the overload situation, forcing the preset maximum current to be supplied to the SMPS until the overload protection triggers. Because more energy than required is provided to the output, the output voltage may exceed the rated voltage before the overload protection triggers, resulting in the breakdown of the devices in the secondary side. To prevent this situation, an OVP circuit is employed. Since VDD voltage is proportional to the output voltage by the transformer

coupling, the over voltage of output is indirectly detected using  $V_{DD}$  voltage. The OVP is triggered when  $V_{DD}$  voltage reaches 28 V. Debounce time (typically 150  $\mu$ s) is applied to prevent false triggering by switching noise.

#### **Over-Temperature Protection (OTP)**

The SenseFET and the control IC are integrated in one package. This makes it easier for the control IC to detect the abnormal over temperature of the SenseFET. If the temperature exceeds approximately 140°C, the OTP is triggered and the MOSFET remains off. When the junction temperature drops by 25°C from OTP temperature, normal operation resumes.

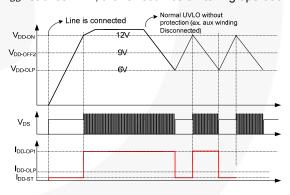

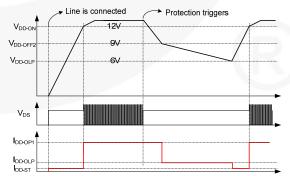

#### **Two-Level UVLO**

Since all the protections are auto-restart, the power supply repeats shutdown and restart until the fault condition is removed. Two-level UVLO is enabled when protection is triggered to delay the re-startup by slowing down V<sub>DD</sub> discharge. This effectively reduces the input power of the power supply during the fault condition, minimizing the voltage/current stress of the switching devices. Figure 28 shows the normal UVLO operation and two-step UVLO operation. When V<sub>DD</sub> drops to 6 V without triggering the protection, the PWM stops switching and V<sub>DD</sub> is charged by the HV startup circuit. Meanwhile, when the protection is triggered, the FSB127AH has a different V<sub>DD</sub> discharge profile. Once the protection is triggered, the IC stops switching and V<sub>DD</sub> drops. When V<sub>DD</sub> drops to 9 V, the operating current becomes very small and V<sub>DD</sub> is slowly discharged. When V<sub>DD</sub> is naturally discharged down to 6 V, the protection is reset and V<sub>DD</sub> is charged by the HV startup circuit. Once V<sub>DD</sub> reaches 12 V, the IC resumes switching operation.

Figure 28. Normal and Two-Level UVLO

### **Typical Application Circuit**

| Application             | Fairchild Device | Input Voltage Range                      | Output      |

|-------------------------|------------------|------------------------------------------|-------------|

| Standby Auxiliary Power | FSB127AH         | 85 V <sub>AC</sub> ~ 265 V <sub>AC</sub> | 5 V / 3.2 A |

Figure 29. Schematic of Typical Application Circuit

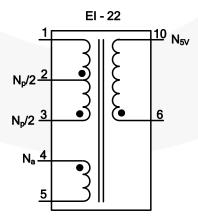

### **Transformer Specification**

Core: El 22Bobbin: El 22

Figure 30. Transformer Specification

## Typical Application Circuit (Continued)

|                                                  | $\textbf{Pin (S} \rightarrow \textbf{F)}$ | Wire       | Turns | Winding Method   |  |  |

|--------------------------------------------------|-------------------------------------------|------------|-------|------------------|--|--|

| Na                                               | 4 → 5                                     | 0.15φ×1    | 12    | Solenoid Winding |  |  |

| Insulation: Polyester Tape t = 0.025 mm, 1-Layer |                                           |            |       |                  |  |  |

| N <sub>p</sub> /2                                | 3 → 2                                     | 0.27φ×1    | 31    | Solenoid Winding |  |  |

| Insulation: F                                    | Polyester Tape t = 0.025 mm               | ı, 2-Layer |       |                  |  |  |

| N <sub>5V</sub>                                  | 6 → 10                                    | 0.55φ×2    | 5     | Solenoid Winding |  |  |

| Insulation: F                                    | Polyester Tape t = 0.025 mm               | ı, 2-Layer |       |                  |  |  |

| N <sub>p</sub> /2                                | 2 → 1                                     | 0.27φ×1    | 31    | Solenoid Winding |  |  |

| Insulation: Polyester Tape t = 0.025 mm, 2-Layer |                                           |            |       |                  |  |  |

|                                | Pin | Specification   | Remark               |

|--------------------------------|-----|-----------------|----------------------|

| Primary-Side Inductance        | 1-3 | 900 μH ±10%     | 100 kHz, 1 V         |

| Primary-Side Effective Leakage | 1-3 | < 30 µH Maximum | Short All Other Pins |

#### NOTES:

- A) THIS PACKAGE CONFORMS TO JEDEC MS-001 VARIATION BA WHICH DEFINES 2 VERSIONS OF THE PACKAGE TERMINAL STYLE WHICH ARE SHOWN HERE.

- B) CONTROLING DIMS ARE IN INCHES

- C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

- D) DIMENSIONS AND TOLERANCES PER ASME Y14.5M-2009

- E) DRAWING FILENAME AND REVSION: MKT-N08MREV2.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative