# **Data Sheet**

### **FEATURES**

Complete supervisory and sequencing solution for up to 10 supplies 10 supply fault detectors enable supervision of supplies to <0.5% accuracy at all voltages at 25°C <1.0% accuracy across all voltages and temperatures 5 selectable input attenuators allow supervision of supplies to 14.4 V on VH 6 V on VP1 to VP4 (VPx) 5 dual-function inputs, VX1 to VX5 (VXx) High impedance input to supply fault detector with thresholds between 0.573 V and 1.375 V General-purpose logic input 10 programmable driver outputs, PDO1 to PDO10 (PDOx) **Open-collector with external pull-up** Push/pull output, driven to VDDCAP or VPx Open collector with weak pull-up to VDDCAP or VPx Internally charge-pumped high drive for use with external N-FET (PDO1 to PDO6 only) Sequencing engine (SE) implements state machine control of **PDO outputs** State changes conditional on input events **Enables complex control of boards** Power-up and power-down sequence control Fault event handling Interrupt generation on warnings Watchdog function can be integrated in SE Program software control of sequencing through SMBus Open-loop margining solution for 6 voltage rails 6 voltage output 8-bit DACs (0.300 V to 1.551 V) allow voltage adjustment via dc-to-dc converter trim/feedback node Device powered by the highest of VPx, VH for improved redundancy User EEPROM: 256 bytes Industry-standard 2-wire bus interface (SMBus) Guaranteed PDO low with VH, VPx = 1.2 V Available in 40-lead, 6 mm × 6 mm LFCSP and 48-lead, 7 mm × 7 mm TQFP packages

### **APPLICATIONS**

**Central office systems** Servers/routers Multivoltage system line cards **DSP/FPGA** supply sequencing In-circuit testing of margined supplies

**Document Feedback**

Rev. E Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# Super Sequencer with **Open-Loop Margining DACs**

# **ADM1067**

### **GENERAL DESCRIPTION**

The ADM1067 Super Sequencer<sup>®</sup> is a configurable supervisory/ sequencing device that offers a single-chip solution for supply monitoring and sequencing in multiple supply systems. In addition to these functions, the ADM1067 integrates six 8-bit voltage output DACs. These circuits can be used to implement an openloop margining system that enables supply adjustment by altering either the feedback node or reference of a dc-to-dc converter using the DAC outputs.

For more information about the ADM1067 register map, refer to the AN-698 Application Note.

# ADM1067\* Product Page Quick Links

Last Content Update: 08/30/2016

# Comparable Parts

View a parametric search of comparable parts

# Evaluation Kits

• ADM1067 Evaluation Board

# Documentation 🖵

## **Application Notes**

- AN-0973: Erasing and Programming the Sequencing Engine EEPROM

- AN-0975: Automatic Generation of State Diagrams for the ADM1062 to ADM1069 Using Graphviz

- AN-0997: Ping-Pong Configuration Guide for ADM1062 to ADM1069 Devices

- AN-1001: Checksum Calculations

- AN-1009: Block Erasing, Reading and Writing to the ADM106x EEPROM

- AN-1086: Using an ADM106x in a Hot Swap Application

- AN-698: Configuration Registers of ADM1062/ADM1063/ ADM1064/ADM1065/ADM1066/ADM1067/ADM1166

- AN-722: Watchdog Detection Using the ADM106x

- AN-723: Interrupt Generation Using the ADM106x

- AN-780: Monitoring Negative Voltages with the ADM1062 to ADM1069 Super Sequencers

- AN-781: Monitoring Additional Supplies with the ADM1062-ADM1069 Super Sequencers™

- AN-782: Monitoring High Voltages with the ADM1062-ADM1069 Super Sequencers<sup>™</sup>

- AN-897: ADC Readback Code

### **Data Sheet**

• ADM1067: Super Sequencer<sup>™</sup> with Open Loop Margining DACs Data Sheet

## **User Guides**

- SuperSequencer Documentation

- UG-404: USB-SDP-CABLEZ Serial Interface Board

## Software and Systems Requirements

- ADMxxxx Common Run-Time

- SuperSequencer Software

## Reference Materials

## Informational

· Optical and High Speed Networking ICs

### **Product Selection Guide**

- Supervisory Devices Complementary Parts Guide for Altera FPGAs

- Supervisory Devices Complementary Parts Guide for Xilinx FPGAs

### **Solutions Bulletins & Brochures**

• Power Supply Sequencing Bulletin (2007)

### **Technical Articles**

· Temperature monitor measures three thermal zones

# Design Resources 🖵

- ADM1067 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

## Discussions 🖵

View all ADM1067 EngineerZone Discussions

# Sample and Buy

Visit the product page to see pricing options

# Technical Support

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# TABLE OF CONTENTS

| Features                                                |

|---------------------------------------------------------|

| Applications1                                           |

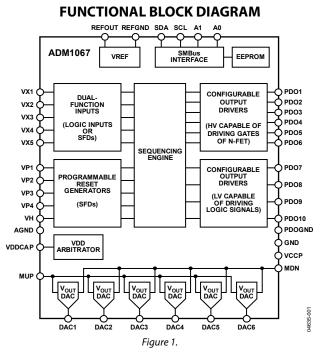

| Functional Block Diagram1                               |

| General Description                                     |

| Revision History                                        |

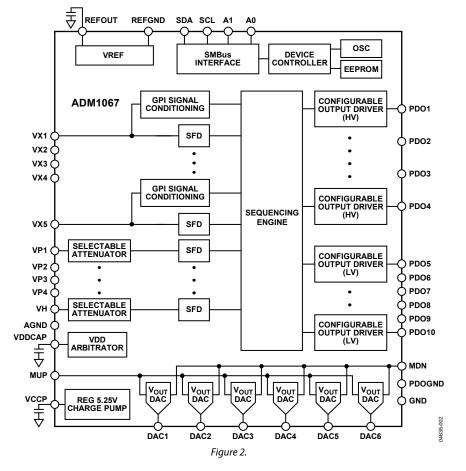

| Detailed Block Diagram 4                                |

| Specifications                                          |

| Absolute Maximum Ratings                                |

| Thermal Resistance                                      |

| ESD Caution                                             |

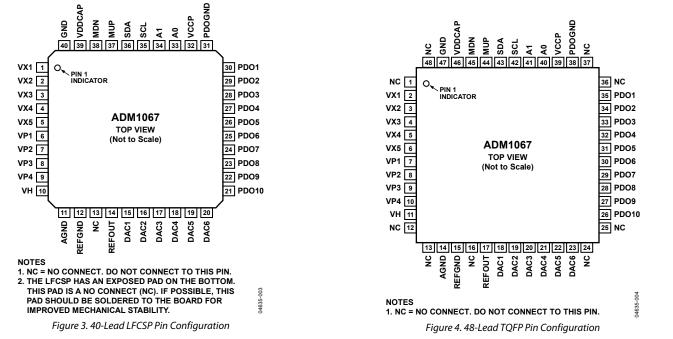

| Pin Configurations and Function Descriptions9           |

| Typical Performance Characteristics                     |

| Powering the ADM106714                                  |

| Slew Rate Consideration14                               |

| Inputs15                                                |

| Supply Supervision                                      |

| Programming the Supply Fault Detectors15                |

| Input Comparator Hysteresis15                           |

| Input Glitch Filtering16                                |

| Supply Supervision with VXx Inputs16                    |

| VXx Pins as Digital Inputs16                            |

| Outputs                                                 |

| Supply Sequencing Through Configurable Output Drivers17 |

| Default Output Configuration17                          |

| Sequencing Engine                                       |

| Overview                                      | 18 |

|-----------------------------------------------|----|

| Warnings                                      | 18 |

| SMBus Jump (Unconditional Jump)               | 18 |

| Sequencing Engine Application Example         | 19 |

| Fault and Status Reporting                    | 20 |

| Supply Margining                              | 21 |

| Overview                                      | 21 |

| Open-Loop Supply Margining                    | 21 |

| Writing to the DACs                           | 21 |

| Choosing the Size of the Attenuation Resistor | 22 |

| DAC Limiting and Other Safety Features        | 22 |

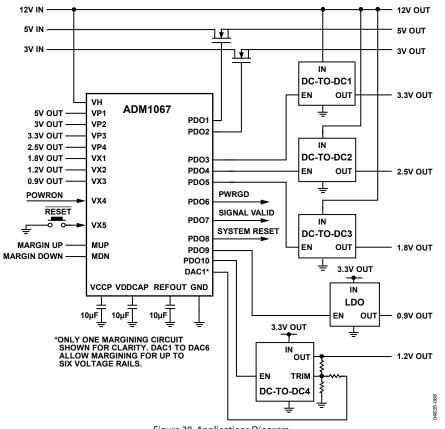

| Applications Diagram                          | 23 |

| Communicating with the ADM1067                | 24 |

| Configuration Download at Power-Up            | 24 |

| Updating the Configuration                    | 24 |

| Updating the Sequencing Engine                | 25 |

| Internal Registers                            | 25 |

| EEPROM                                        | 25 |

| Serial Bus Interface                          | 25 |

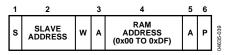

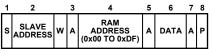

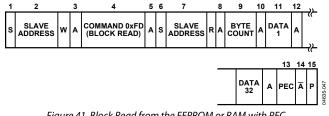

| SMBus Protocols for RAM and EEPROM            | 28 |

| Write Operations                              | 28 |

| Read Operations                               | 30 |

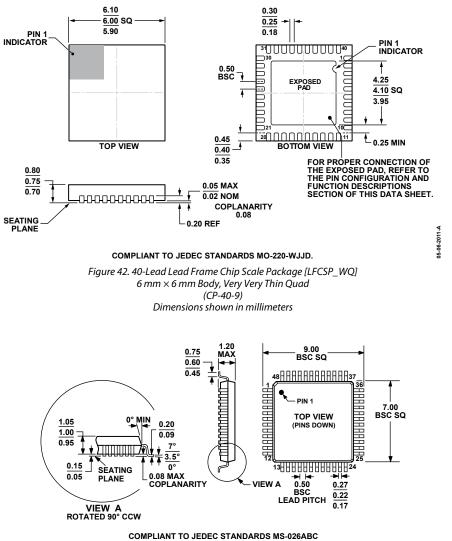

| Outline Dimensions                            | 31 |

| Ordering Guide                                | 31 |

|                                               |    |

## **REVISION HISTORY**

| 1/15—Rev. D to Rev. E                              |    |

|----------------------------------------------------|----|

| Changes to Figure 3, Figure 4, and Table 4         | 9  |

| Added Slew Rate Consideration Section              | 14 |

| Added SCL Held Low Timeout Section and False Start |    |

| Detection Section                                  | 26 |

| Updated Outline Dimensions                         | 31 |

| Changes to Ordering Guide                          | 31 |

### 6/11-Rev. C to Rev. D

| Changes to Serial Bus Timing Parameter in Table 1 | 5  |

|---------------------------------------------------|----|

| Change to Figure 3                                | 9  |

| Added Exposed Pad Notation to Outline Dimensions  | 31 |

| Changes to Ordering Guide                         | 31 |

|                                                   |    |

### 5/08—Rev. B to Rev. C

| Changes to Figure 1                                   | 1  |

|-------------------------------------------------------|----|

| Changes to Table 1                                    |    |

| Changes to Powering the ADM1067 Section               | 13 |

| Changes to Sequence Detector Section                  | 18 |

| Changes to Figure 27                                  | 20 |

| Changes to Configuration Download at Power-Up Section | 23 |

| Changes to Table 10                                   | 24 |

| Changes to Figure 40 and Error Correction Section     | 29 |

| Changes to Ordering Guide                             | 30 |

|                                                       |    |

#### 11/06—Rev. A to Rev. B

| Updated Format                                        | Universal |

|-------------------------------------------------------|-----------|

| Changes to Features                                   | 1         |

| Changes to Figure 2                                   | 3         |

| Changes to Table 1                                    | 4         |

| Changes to Table 2                                    | 7         |

| Changes to Absolute Maximum Ratings Section           | 9         |

| Changes to Programming the Supply Fault Detectors Sec | tion 14   |

| Changes to Table 6                                    | 14        |

| Added the Default Output Configuration Section        |           |

| Changes to Fault Reporting Section                    | 21        |

| Changes to Figure 28                                  | 24        |

| Changes to the Identifying the ADM1067                |           |

| on the SMBus Section                                  |           |

| Changes to Figure 30 and Figure 31                    |           |

| Changes to Ordering Guide                             |           |

### 1/05—Rev. 0 to Rev. A

| Changes to Figure 1                              | 1  |

|--------------------------------------------------|----|

| Changes to Absolute Maximum Ratings Section      |    |

| Change to Supply Sequencing through Configurable |    |

| Output Drivers Section                           | 16 |

| Changes to Figure 28                             | 22 |

| Change to Table 9                                | 25 |

10/04—Revision 0: Initial Version

Supply margining can be performed with a minimum of external components. The margining capability can be used for in-circuit testing of a board during production (for example, to verify board functionality at -5% of nominal supplies), or it can be used dynamically to accurately control the output voltage of a dc-to-dc converter.

The device also provides up to 10 programmable inputs for monitoring undervoltage faults, overvoltage faults, or out-ofwindow faults on up to 10 supplies. In addition, 10 programmable outputs can be used as logic enables. Six of these programmable outputs can also provide up to a 12 V output for driving the gate of an N-FET that can be placed in the path of a supply.

The logical core of the device is a sequencing engine. This statemachine-based construction provides up to 63 different states. This design enables very flexible sequencing of the outputs, based on the condition of the inputs.

The device is controlled via configuration data that can be programmed into an EEPROM. The entire configuration can be programmed using an intuitive GUI-based software package provided by Analog Devices, Inc.

## DETAILED BLOCK DIAGRAM

# **SPECIFICATIONS**

VH = 3.0 V to 14.4  $V^{\rm l},$  VPx = 3.0 V to 6.0  $V^{\rm l},$   $T_{\rm A}$  = -40°C to +85°C, unless otherwise noted.

## Table 1.

| Parameter                                          | Min   | Тур    | Max   | Unit | Test Conditions/Comments                                                                |

|----------------------------------------------------|-------|--------|-------|------|-----------------------------------------------------------------------------------------|

| POWER SUPPLY ARBITRATION                           |       |        |       |      |                                                                                         |

| VH, VPx                                            | 3.0   |        |       | V    | Minimum supply required on one of VH, VPx                                               |

| VPx                                                |       |        | 6.0   | V    | Maximum VDDCAP = 5.1 V, typical                                                         |

| VH                                                 |       |        | 14.4  | V    | VDDCAP = 4.75 V                                                                         |

| VDDCAP                                             | 2.7   | 4.75   | 5.4   | v    | Regulated LDO output                                                                    |

| CVDDCAP                                            | 10    |        |       | μF   | Minimum recommended decoupling capacitance                                              |

| POWER SUPPLY                                       |       |        |       |      |                                                                                         |

| Supply Current, I <sub>VH</sub> , I <sub>VPx</sub> |       | 4.2    | 6     | mA   | VDDCAP = 4.75 V, PDO1 to PDO10 off, DACs off, ADC off                                   |

| Additional Currents                                |       |        |       |      |                                                                                         |

| All PDO FET Drivers On                             |       | 1      |       | mA   | VDDCAP = 4.75 V, PDO1 to PDO6 loaded with 1 $\mu$ A each, PDO7 to PDO10 off             |

| Current Available from VDDCAP                      |       |        | 2     | mA   | Maximum additional load that can be drawn from all PDO pull-ups to VDDCAP               |

| DACs Supply Current                                |       | 2.2    |       | mA   | Six DACs on with 100 μA maximum load on each                                            |

| ADC Supply Current                                 |       | 1      |       | mA   | Running round-robin loop                                                                |

| EEPROM Erase Current                               |       | 10     |       | mA   | 1 ms duration only, VDDCAP = 3 V                                                        |

| SUPPLY FAULT DETECTORS                             |       |        |       |      |                                                                                         |

| VH Pin                                             |       |        |       |      |                                                                                         |

| Input Impedance                                    |       | 52     |       | kΩ   |                                                                                         |

| Input Attenuator Error                             |       | ±0.05  |       | %    | Midrange and high range                                                                 |

| Detection Ranges                                   |       |        |       |      |                                                                                         |

| High Range                                         | 6     |        | 14.4  | v    |                                                                                         |

| Midrange                                           | 2.5   |        | 6     | v    |                                                                                         |

| VPx Pins                                           |       |        |       |      |                                                                                         |

| Input Impedance                                    |       | 52     |       | kΩ   |                                                                                         |

| Input Attenuator Error                             |       | ±0.05  |       | %    | Low range and midrange                                                                  |

| Detection Ranges                                   |       |        |       |      |                                                                                         |

| Midrange                                           | 2.5   |        | 6     | v    |                                                                                         |

| Low Range                                          | 1.25  |        | 3     | v    |                                                                                         |

| Ultralow Range                                     | 0.573 |        | 1.375 | v    | No input attenuation error                                                              |

| VXx Pins                                           |       |        |       |      |                                                                                         |

| Input Impedance                                    | 1     |        |       | MΩ   |                                                                                         |

| Detection Ranges                                   |       |        |       |      |                                                                                         |

| Ultralow Range                                     | 0.573 |        | 1.375 | v    | No input attenuation error                                                              |

| Absolute Accuracy                                  |       |        | ±1    | %    | VREF error + DAC nonlinearity + comparator offset error + input attenuation error       |

| Threshold Resolution                               |       | 8      |       | Bits |                                                                                         |

| Digital Glitch Filter                              |       | 0      |       | μs   | Minimum programmable filter length                                                      |

|                                                    |       | 100    |       | μs   | Maximum programmable filter length                                                      |

| BUFFERED VOLTAGE OUTPUT DACs                       |       |        |       |      |                                                                                         |

| Resolution                                         |       | 8      |       | Bits |                                                                                         |

| Code 0x80 Output Voltage                           |       |        |       |      | Six DACs are individually selectable for centering on one of four output voltage ranges |

| Range 1                                            | 0.592 | 0.6    | 0.603 | V    |                                                                                         |

| Range 2                                            | 0.796 | 0.8    | 0.803 | V    |                                                                                         |

| Range 3                                            | 0.997 | 1      | 1.003 | V    |                                                                                         |

| Range 4                                            | 1.247 | 1.25   | 1.253 | V    |                                                                                         |

| Output Voltage Range                               |       | 601.25 |       | mV   | Same range, independent of center point                                                 |

| LSB Step Size                                      |       | 2.36   |       | mV   |                                                                                         |

| Parameter                                         | Min                 | Тур   | Max   | Unit     | Test Conditions/Comments                                                                                                                                   |

|---------------------------------------------------|---------------------|-------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INL                                               |                     |       | ±0.75 | LSB      | Endpoint corrected                                                                                                                                         |

| DNL                                               |                     |       | ±0.4  | LSB      |                                                                                                                                                            |

| Gain Error                                        |                     |       | 1     | %        |                                                                                                                                                            |

| Maximum Load Current (Source)                     |                     | 100   |       | μA       |                                                                                                                                                            |

| Maximum Load Current (Sink)                       |                     | 100   |       | μA       |                                                                                                                                                            |

| Maximum Load Capacitance                          |                     |       | 50    | pF       |                                                                                                                                                            |

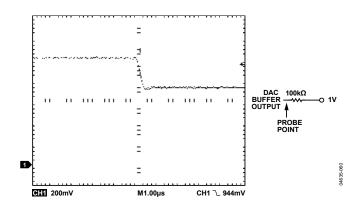

| Settling Time into 50 pF Load                     |                     |       | 2     | μs       |                                                                                                                                                            |

| Load Regulation                                   |                     | 2.5   | -     | mV       | Per mA                                                                                                                                                     |

| PSRR                                              |                     | 60    |       | dB       | DC                                                                                                                                                         |

|                                                   |                     | 40    |       | dB       | 100 mV step in 20 ns with 50 pF load                                                                                                                       |

| REFERENCE OUTPUT                                  |                     | 40    |       | ab       |                                                                                                                                                            |

| Reference Output Voltage                          | 2.043               | 2.048 | 2.053 | v        | No load                                                                                                                                                    |

| Load Regulation                                   | 2.045               | -0.25 | 2.055 | mV       | Sourcing current, $I_{DACXMAX} = -100 \mu\text{A}$                                                                                                         |

| Load Regulation                                   |                     | 0.25  |       | mV       | Sinking current, $I_{DACXMAX} = 100 \ \mu A$                                                                                                               |

| Minimum Load Canacitance                          | 1                   | 0.25  |       |          | Capacitor required for decoupling, stability                                                                                                               |

| Minimum Load Capacitance<br>PSRR                  | 1                   | 60    |       | μF<br>dB | DC                                                                                                                                                         |

| PROGRAMMABLE DRIVER OUTPUTS                       |                     | 00    |       | UD       |                                                                                                                                                            |

| High Voltage Charge Pump Mode<br>(PDO1 to PDO6)   |                     |       |       |          |                                                                                                                                                            |

| Output Impedance                                  |                     | 500   |       | kΩ       |                                                                                                                                                            |

|                                                   | 11                  |       | 14    |          |                                                                                                                                                            |

| V <sub>он</sub>                                   | 11                  | 12.5  | 14    | V        | $I_{OH} = 0 \mu A$                                                                                                                                         |

|                                                   | 10.5                | 12    | 13.5  | V        | $I_{OH} = 1 \mu A$                                                                                                                                         |

|                                                   |                     | 20    |       | μΑ       | $2 V < V_{OH} < 7 V$                                                                                                                                       |

| Standard (Digital Output) Mode<br>(PDO1 to PDO10) |                     |       |       |          |                                                                                                                                                            |

| V <sub>OH</sub>                                   | 2.4                 |       |       | V        | $V_{PU}$ (pull-up to VDDCAP or VPx) = 2.7 V, $I_{OH}$ = 0.5 mA                                                                                             |

|                                                   |                     |       | 4.5   | V        | $V_{PU}$ to $VPx = 6.0$ V, $I_{OH} = 0$ mA                                                                                                                 |

|                                                   | $V_{\text{PU}}-0.3$ |       |       | V        | $V_{PU} \leq 2.7 \text{ V}, I_{OH} = 0.5 \text{ mA}$                                                                                                       |

| V <sub>OL</sub>                                   | 0                   |       | 0.50  | V        | $I_{OL} = 20 \text{ mA}$                                                                                                                                   |

| I <sub>OL</sub> <sup>2</sup>                      |                     |       | 20    | mA       | Maximum sink current per PDOx pin                                                                                                                          |

| Isink <sup>2</sup>                                |                     |       | 60    | mA       | Maximum total sink for all PDOx pins                                                                                                                       |

| R <sub>PULL-UP</sub>                              | 16                  | 20    | 29    | kΩ       | Internal pull-up                                                                                                                                           |

| Isource (VPx) <sup>2</sup>                        |                     |       | 2     | mA       | Current load on any VPx pull-ups, that is, total source<br>current available through any number of PDO pull-up<br>switches configured onto any one VPx pin |

| Three-State Output Leakage Current                |                     |       | 10    | μΑ       | V <sub>PDO</sub> = 14.4 V                                                                                                                                  |

| Oscillator Frequency                              | 90                  | 100   | 110   | kHz      | All on-chip time delays derived from this clock                                                                                                            |

| DIGITAL INPUTS (VXx, A0, A1, MUP, MDN)            |                     |       |       |          |                                                                                                                                                            |

| Input High Voltage, V <sub>⊮</sub>                | 2.0                 |       |       | V        | Maximum $V_{IN} = 5.5 V$                                                                                                                                   |

| Input Low Voltage, V <sub>I</sub>                 |                     |       | 0.8   | V        | Maximum $V_{IN} = 5.5 V$                                                                                                                                   |

| Input High Current, I <sub>⊮</sub>                | -1                  |       |       | μA       | $V_{IN} = 5.5 V$                                                                                                                                           |

| Input Low Current, IL                             |                     |       | 1     | μA       | $V_{IN} = 0 V$                                                                                                                                             |

| Input Capacitance                                 |                     | 5     |       | pF       |                                                                                                                                                            |

| Programmable Pull-Down Current,                   |                     | 20    |       | μA       | VDDCAP = 4.75 V, $T_A$ = 25°C, if known logic state is require                                                                                             |

| IPULL-DOWN                                        |                     | -     |       |          |                                                                                                                                                            |

| SERIAL BUS DIGITAL INPUTS (SDA, SCL)              |                     |       |       |          |                                                                                                                                                            |

| Input High Voltage, V <sub>IH</sub>               | 2.0                 |       |       | V        |                                                                                                                                                            |

| Input Low Voltage, V <sub>L</sub>                 |                     |       | 0.8   | v        |                                                                                                                                                            |

| Output Low Voltage, $V_{OL}^2$                    |                     |       | 0.4   | V        | $I_{OUT} = -3.0 \text{ mA}$                                                                                                                                |

# **Data Sheet**

# ADM1067

| Parameter                            | Min | Тур | Max | Unit | Test Conditions/Comments |

|--------------------------------------|-----|-----|-----|------|--------------------------|

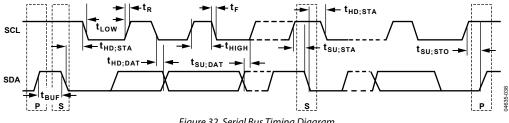

| SERIAL BUS TIMING <sup>3</sup>       |     |     |     |      |                          |

| Clock Frequency, fsclk               |     |     | 400 | kHz  |                          |

| Bus Free Time, tBUF                  | 1.3 |     |     | μs   |                          |

| Start Setup Time, tsu;sta            | 0.6 |     |     | μs   |                          |

| Stop Setup Time, tsu;sto             | 0.6 |     |     | μs   |                          |

| Start Hold Time, tHD;STA             | 0.6 |     |     | μs   |                          |

| SCL Low Time, t <sub>LOW</sub>       | 1.3 |     |     | μs   |                          |

| SCL High Time, thigh                 | 0.6 |     |     | μs   |                          |

| SCL, SDA Rise Time, t <sub>R</sub>   |     |     | 300 | ns   |                          |

| SCL, SDA Fall Time, t <sub>F</sub>   |     |     | 300 | ns   |                          |

| Data Setup Time, t <sub>su;DAT</sub> | 100 |     |     | ns   |                          |

| Data Hold Time, thd;dat              | 5   |     |     | ns   |                          |

| Input Low Current, I <sub>IL</sub>   |     |     | 1   | μΑ   | $V_{IN} = 0 V$           |

| SEQUENCING ENGINE TIMING             |     |     |     |      |                          |

| State Change Time                    |     | 10  |     | μs   |                          |

<sup>1</sup> At least one of the VH, VPx pins must be  $\geq$ 3.0 V to maintain the device supply on VDDCAP. <sup>2</sup> Specification is not production tested but is supported by characterization data at initial product release. <sup>3</sup> Timing specifications are guaranteed by design and supported by characterization data.

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                                 | Rating           |

|-------------------------------------------|------------------|

| Voltage on VH Pin                         | 16 V             |

| Voltage on VPx Pins                       | 7 V              |

| Voltage on VXx Pins                       | –0.3 V to +6.5 V |

| Voltage on A0, A1 Pins                    | –0.3 V to +7 V   |

| Voltage on REFOUT Pin                     | 5 V              |

| Voltage on VDDCAP, VCCP Pins              | 6.5 V            |

| Voltage on DACx Pins                      | 6.5 V            |

| Voltage on PDOx Pins                      | 16 V             |

| Voltage on SDA, SCL Pins                  | 7 V              |

| Voltage on GND, AGND, PDOGND, REFGND Pins | –0.3 V to +0.3 V |

| Voltage on MUP and MDN Pins               | VDDCAP + 0.6 V   |

| Input Current at Any Pin                  | ±5 mA            |

| Package Input Current                     | ±20 mA           |

| Maximum Junction Temperature (TJ max)     | 150°C            |

| Storage Temperature Range                 | –65°C to +150°C  |

| Lead Temperature,                         |                  |

| Soldering Vapor Phase, 60 sec             | 215°C            |

| ESD Rating, All Pins                      | 2000 V           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 3. Thermal Resistance

| Package Type  | Αιθ | Unit |

|---------------|-----|------|

| 40-Lead LFCSP | 25  | °C/W |

| 48-Lead TQFP  | 50  | °C/W |

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

#### **Table 4. Pin Function Descriptions**

| Pi               | n No.                                   | _                   |                                                                                                                                                                                                                                                                                                                             |

|------------------|-----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40-Lead<br>LFCSP | 48-Lead<br>TQFP                         | Mnemonic            | Description                                                                                                                                                                                                                                                                                                                 |

| 13               | 1, 12, 13, 16,<br>24, 25, 36,<br>37, 48 | NC                  | No Connect. Do not connect to this pin.                                                                                                                                                                                                                                                                                     |

| 1 to 5           | 2 to 6                                  | VX1 to VX5<br>(VXx) | High Impedance Inputs to Supply Fault Detectors. Fault thresholds can be set from 0.573 V to 1.375 V. Alternatively, these pins can be used as general-purpose digital inputs.                                                                                                                                              |

| 6 to 9           | 7 to 10                                 | VP1 to VP4<br>(VPx) | Low Voltage Inputs to Supply Fault Detectors. Three input ranges can be set by altering the input attenuation on a potential divider connected to these pins, the output of which connects to a supply fault detector. These pins allow thresholds from 2.5 V to 6.0 V, from 1.25 V to 3.00 V, and from 0.573 V to 1.375 V. |

| 10               | 11                                      | VH                  | High Voltage Input to Supply Fault Detectors. Two input ranges can be set by altering the input attenuation on a potential divider connected to this pin, the output of which connects to a supply fault detector. This pin allows thresholds from 6.0 V to 14.4 V and from 2.5 V to 6.0 V.                                 |

| 11               | 14                                      | AGND <sup>1</sup>   | Ground Return for Input Attenuators.                                                                                                                                                                                                                                                                                        |

| 12               | 15                                      | REFGND <sup>1</sup> | Ground Return for On-Chip Reference Circuits.                                                                                                                                                                                                                                                                               |

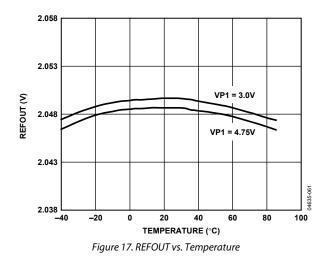

| 14               | 17                                      | REFOUT              | Reference Output, 2.048 V. Note that the capacitor must be connected between this pin and REFGND. A 10 $\mu$ F capacitor is recommended for this purpose.                                                                                                                                                                   |

| 15 to 20         | 18 to 23                                | DAC1 to<br>DAC6     | Voltage Output DACs. These pins default to high impedance at power-up.                                                                                                                                                                                                                                                      |

| 21 to 30         | 26 to 35                                | PDO10 to<br>PDO1    | Programmable Output Drivers.                                                                                                                                                                                                                                                                                                |

| 31               | 38                                      | PDOGND <sup>1</sup> | Ground Return for Output Drivers.                                                                                                                                                                                                                                                                                           |

| 32               | 39                                      | VCCP                | Central Charge-Pump Voltage of 5.25 V. A reservoir capacitor must be connected between this pin and GND. A 10 $\mu$ F capacitor is recommended for this purpose.                                                                                                                                                            |

| 33               | 40                                      | A0                  | Logic Input. This pin sets the seventh bit of the SMBus interface address.                                                                                                                                                                                                                                                  |

| 34               | 41                                      | A1                  | Logic Input. This pin sets the sixth bit of the SMBus interface address.                                                                                                                                                                                                                                                    |

| 35               | 42                                      | SCL                 | SMBus Clock Pin. Bidirectional open drain requires external resistive pull-up.                                                                                                                                                                                                                                              |

| 36               | 43                                      | SDA                 | SMBus Data Pin. Bidirectional open drain requires external resistive pull-up.                                                                                                                                                                                                                                               |

| 37               | 44                                      | MUP                 | Digital Input. Forces DACs to their lowest value, causing the voltage at the feedback node to drop. This is compensated for by an increase in the supply output voltage, thus margining up.                                                                                                                                 |

| Pin No.          |                  |                  |                                                                                                                                                                                                                                    |

|------------------|------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40-Lead<br>LFCSP | 48-Lead<br>TQFP  | Mnemonic         | Description                                                                                                                                                                                                                        |

| 38               | 45               | MDN              | Digital Input. Forces DACs to their highest value, causing the voltage at the feedback node to rise. This is compensated for by a decrease in the supply output voltage, thus margining down.                                      |

| 39               | 46               | VDDCAP           | Device Supply Voltage. Linearly regulated from the highest of the VPx, VH pins to a typical of 4.75 V. Note that the capacitor must be connected between this pin and GND. A 10 $\mu$ F capacitor is recommended for this purpose. |

| 40               | 47               | GND <sup>1</sup> | Supply Ground.                                                                                                                                                                                                                     |

|                  | N/A <sup>2</sup> | EPAD             | Exposed Pad. The LFCSP has an exposed pad on the bottom. This pad is a no connect (NC). If possible, this pad should be soldered to the board for improved mechanical stability.                                                   |

$^{\rm 1}$  In a typical application, all ground pins are connected together.  $^{\rm 2}$  N/A is not applicable

04635-053

04635-054

04635-055

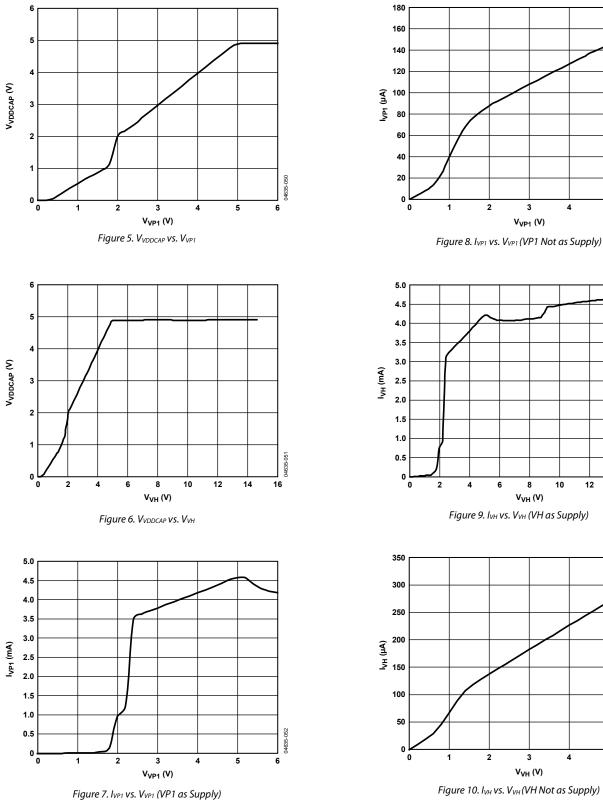

# **TYPICAL PERFORMANCE CHARACTERISTICS**

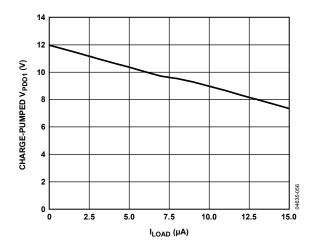

Figure 11. Charge-Pumped VPDO1 (FET Drive Mode) vs. ILOAD

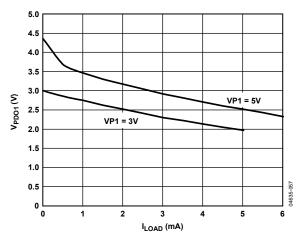

Figure 12. VPDO1 (Strong Pull-Up to VP) vs. ILOAD

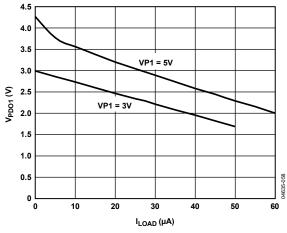

Figure 13. VPDO1 (Weak Pull-Up to VP) vs. ILOAD

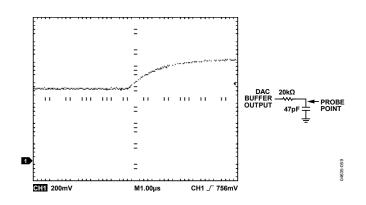

Figure 14. Transient Response of DAC Code Change into Typical Load

Figure 15. Transient Response of DAC to Turn-On from High-Z State

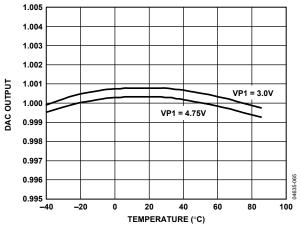

Figure 16. DAC Output vs. Temperature

# **POWERING THE ADM1067**

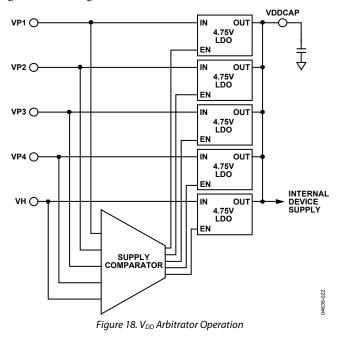

The ADM1067 is powered from the highest voltage input on either the positive-only supply inputs (VPx) or the high voltage supply input (VH). This technique offers improved redundancy because the device is not dependent on any particular voltage rail to keep it operational. The same pins are used for supply fault detection (see the Supply Supervision section). A V<sub>DD</sub> arbitrator on the device chooses which supply to use. The arbitrator can be considered an OR'ing of five low dropout regulators (LDOs) together. A supply comparator chooses the highest input to provide the on-chip supply. There is minimal switching loss with this architecture (~0.2 V), resulting in the ability to power the ADM1067 from a supply as low as 3.0 V. Note that the supply on the VXx pins cannot be used to power the device.

An external capacitor to GND is required to decouple the onchip supply from noise. This capacitor should be connected to the VDDCAP pin, as shown in Figure 18. The capacitor has another use during brownouts (momentary loss of power). Under these conditions, when the input supply (VPx or VH) dips transiently below V<sub>DD</sub>, the synchronous rectifier switch immediately turns off so that it does not pull V<sub>DD</sub> down. The V<sub>DD</sub> capacitor can then act as a reservoir to keep the device active until the next highest supply takes over the powering of the device. A 10  $\mu$ F capacitor is recommended for this reservoir/decoupling function.

The VH input pin can accommodate supplies up to 14.4 V, which allows the ADM1067 to be powered using a 12 V backplane supply. In cases where this 12 V supply is hot swapped, it is recommended that the ADM1067 not be connected directly to the supply. Suitable precautions, such as the use of a hot swap controller, should be taken to protect the device from transients that could cause damage during hot swap events.

When two or more supplies are within 100 mV of each other, the supply that first takes control of  $V_{DD}$  keeps control. For example, if VP1 is connected to a 3.3 V supply,  $V_{DD}$  powers up to approximately 3.1 V through VP1. If VP2 is then connected to another 3.3 V supply, VP1 still powers the device, unless VP2 goes 100 mV higher than VP1.

### **SLEW RATE CONSIDERATION**

When the ambient temperature of operation is less than approximately  $-20^{\circ}$ C, and in the event of a power loss where all supply inputs fail for less than a few hundreds of milliseconds (for example, due to a system supply brownout), it is recommended that the supply voltage recover with a ramp rate of at least 1.5 V/ms or less than 0.5 V/ms.

## INPUTS SUPPLY SUPERVISION

The ADM1067 has 10 programmable inputs. Five of these are dedicated supply fault detectors (SFDs). These dedicated inputs are called VH and VPx (VP1 to VP4) by default. The other five inputs are labeled VXx (VX1 to VX5) and have dual functionality. They can be used either as SFDs, with functionality similar to VH and VPx, or as CMOS-/TTL-compatible logic inputs to the device. Therefore, the ADM1067 can have up to 10 analog inputs, a minimum of five analog inputs and five digital inputs, or a combination thereof. If an input is used as an analog input, it cannot be used as a digital input. Therefore, a configuration requiring 10 analog inputs has no available digital inputs. Table 6 shows the details of each input.

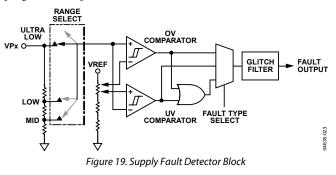

## **PROGRAMMING THE SUPPLY FAULT DETECTORS**

The ADM1067 can have up to 10 SFDs on its 10 input channels. These highly programmable reset generators enable the supervision of up to 10 supply voltages. The supplies can be as low as 0.573 V and as high as 14.4 V. The inputs can be configured to detect an undervoltage fault (the input voltage drops below a preprogrammed value), an overvoltage fault (the input voltage rises above a preprogrammed value), or an out-of-window fault (the input voltage is outside a preprogrammed range). The thresholds can be programmed to an 8-bit resolution in registers provided in the ADM1067. This translates to a voltage resolution that is dependent on the range selected.

The resolution is given by

*Step Size* = Threshold Range/255

Therefore, if the high range is selected on VH, the step size can be calculated as follows:

(14.4 V - 6.0 V)/255 = 32.9 mV

Table 5 lists the upper and lower limits of each available range, the bottom of each range ( $V_B$ ), and the range itself ( $V_R$ ).

| Table 5. | Voltage Rang | ge Limits |

|----------|--------------|-----------|

|----------|--------------|-----------|

| Voltage Range (V) | <b>V</b> <sub>B</sub> ( <b>V</b> ) | V <sub>R</sub> (V) |

|-------------------|------------------------------------|--------------------|

| 0.573 to 1.375    | 0.573                              | 0.802              |

| 1.25 to 3.00      | 1.25                               | 1.75               |

| 2.5 to 6.0        | 2.5                                | 3.5                |

| 6.0 to 14.4       | 6.0                                | 9.6                |

#### Table 6. Input Functions, Thresholds, and Ranges

The threshold value required is given by

$V_T = (V_R \times N)/255 + V_B$

where:

$V_T$  is the desired threshold voltage (undervoltage or overvoltage).  $V_R$  is the voltage range.

*N* is the decimal value of the 8-bit code.

$V_B$  is the bottom of the range.

Reversing the equation, the code for a desired threshold is given by

$N = 255 \times (V_T - V_B)/V_R$

For example, if the user wants to set a 5 V overvoltage threshold on VP1, the code to be programmed in the PS1OVTH register (as discussed in the AN-698 Application Note) is given by

$N = 255 \times (5 - 2.5)/3.5$

Therefore, N = 182 (1011 0110 or 0xB6).

### INPUT COMPARATOR HYSTERESIS

The UV and OV comparators shown in Figure 19 are always monitoring VPx. To avoid chatter (multiple transitions when the input is very close to the set threshold level), these comparators have digitally programmable hysteresis. The hysteresis can be programmed up to the values shown in Table 6.

The hysteresis is added after a supply voltage goes out of tolerance. Therefore, the user can program the amount above the undervoltage threshold to which the input must rise before an undervoltage fault is deasserted. Similarly, the user can program the amount below the overvoltage threshold to which an input must fall before an overvoltage fault is deasserted.

| Input | Function                  | Voltage Range (V) | Maximum Hysteresis | Voltage Resolution (mV) | Glitch Filter (µs) |

|-------|---------------------------|-------------------|--------------------|-------------------------|--------------------|

| VH    | High Voltage Analog Input | 2.5 to 6.0        | 425 mV             | 13.7                    | 0 to 100           |

|       |                           | 6.0 to 14.4       | 1.02 V             | 32.9                    | 0 to 100           |

| VPx   | Positive Analog Input     | 0.573 to 1.375    | 97.5 mV            | 3.14                    | 0 to 100           |

|       |                           | 1.25 to 3.00      | 212 mV             | 6.8                     | 0 to 100           |

|       |                           | 2.5 to 6.0        | 425 mV             | 13.7                    | 0 to 100           |

| VXx   | High-Z Analog Input       | 0.573 to 1.375    | 97.5 mV            | 3.14                    | 0 to 100           |

|       | Digital Input             | 0 to 5.0          | N/A                | N/A                     | 0 to 100           |

The hysteresis value is given by

$V_{HYST} = V_R \times N_{THRESH}/255$

where:

$V_{HYST}$  is the desired hysteresis voltage.  $N_{THRESH}$  is the decimal value of the 5-bit hysteresis code.

Note that  $N_{THRESH}$  has a maximum value of 31. The maximum hysteresis for the ranges is listed in Table 6.

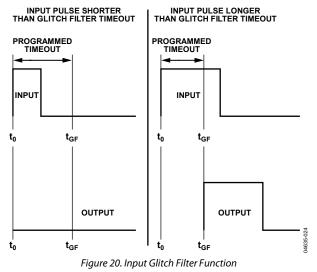

## **INPUT GLITCH FILTERING**

The final stage of the SFDs is a glitch filter. This block provides time-domain filtering on the output of the SFD comparators, which allows the user to remove any spurious transitions such as supply bounce at turn-on. The glitch filter function is in addition to the digitally programmable hysteresis of the SFD comparators. The glitch filter timeout is programmable up to 100  $\mu$ s.

For example, when the glitch filter timeout is 100  $\mu$ s, any pulse appearing on the input of the glitch filter block that is less than 100  $\mu$ s in duration is prevented from appearing on the output of the glitch filter block. Any input pulse that is longer than 100  $\mu$ s appears on the output of the glitch filter block. The output is delayed with respect to the input by 100  $\mu$ s. The filtering process is shown in Figure 20.

## SUPPLY SUPERVISION WITH VXx INPUTS

The VXx inputs have two functions. They can be used either as supply fault detectors or as digital logic inputs. When selected as analog (SFD) inputs, the VXx pins have functionality that is very similar to the VH and VPx pins. The primary difference is that the VXx pins have only one input range: 0.573 V to 1.375 V. Therefore, these inputs can directly supervise only the very low supplies. However, the input impedance of the VXx pins is high, allowing an external resistor divide network to be connected to the pin. Thus, potentially any supply can be divided down into the input range of the VXx pin and be supervised. This enables the ADM1067 to monitor other supplies, such as +24 V, +48 V, and -5 V.

An additional supply supervision function is available when the VXx pins are selected as digital inputs. In this case, the analog function is available as a second detector on each of the dedicated analog inputs, VPx and VH. The analog function of VX1 is mapped to VP1, VX2 is mapped to VP2, and so on. VX5 is mapped to VH. In this case, these SFDs can be viewed as secondary or warning SFDs.

The secondary SFDs are fixed to the same input range as the primary SFDs. They are used to indicate warning levels rather than failure levels. This allows faults and warnings to be generated on a single supply using only one pin. For example, if VP1 is set to output a fault when a 3.3 V supply drops to 3.0 V, VX1 can be set to output a warning at 3.1 V. Warning outputs are available for readback from the status registers. They are also OR'ed together and fed into the SE, allowing warnings to generate interrupts on the PDOs. Therefore, in this example, if the supply drops to 3.1 V, a warning is generated, and remedial action can be taken before the supply drops out of tolerance.

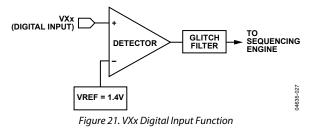

## **VXx PINS AS DIGITAL INPUTS**

As discussed in the Supply Supervision with VXx Inputs section, the VXx input pins on the ADM1067 have dual functionality. The second function is as a digital logic input to the device. Therefore, the ADM1067 can be configured for up to five digital inputs. These inputs are TTL-/CMOS-compatible. Standard logic signals can be applied to the pins: RESET from reset generators, PWRGD signals, fault flags, manual resets, and so on. These signals are available as inputs to the SE and, therefore, can be used to control the status of the PDOs. The inputs can be configured to detect either a change in level or an edge.

When configured for level detection, the output of the digital block is a buffered version of the input. When configured for edge detection, a pulse of programmable width is output from the digital block, once the logic transition is detected. The width is programmable from 0  $\mu$ s to 100  $\mu$ s.

The digital blocks feature the same glitch filter function that is available on the SFDs. This function enables the user to ignore spurious transitions on the inputs. For example, the filter can be used to debounce a manual reset switch.

When configured as digital inputs, each VXx pin has a weak (10  $\mu$ A) pull-down current source available for placing the input into a known condition, even if left floating. The current source, if selected, weakly pulls the input to GND.

## **OUTPUTS** SUPPLY SEQUENCING THROUGH CONFIGURABLE OUTPUT DRIVERS

Supply sequencing is achieved with the ADM1067 using the programmable driver outputs (PDOs) on the device as control signals for supplies. The output drivers can be used as logic enables or as FET drivers.

The sequence in which the PDOs are asserted (and, therefore, the supplies are turned on) is controlled by the sequencing engine (SE). The SE determines what action is taken with the PDOs, based on the condition of the ADM1067 inputs. Therefore, the PDOs can be set up to assert when the SFDs are in tolerance, the correct input signals are received on the VXx digital pins, no warnings are received from any of the inputs of the device, and at other times. The PDOs can be used for a variety of functions. The primary function is to provide enable signals for LDOs or dc-to-dc converters that generate supplies locally on a board. The PDOs can also be used to provide a PWRGD signal when all the SFDs are in tolerance or a RESET output if one of the SFDs goes out of specification (this can be used as a status signal for a DSP, FPGA, or other microcontroller).

The PDOs can be programmed to pull up to a number of different options. The outputs can be programmed as follows:

- Open drain (allowing the user to connect an external pullup resistor).

- Open drain with weak pull-up to V<sub>DD</sub>.

- Open drain with strong pull-up to V<sub>DD</sub>.

- Open drain with weak pull-up to VPx.

- Open drain with strong pull-up to VPx.

- Strong pull-down to GND.

- Internally charge-pumped high drive (12 V, PDO1 to PDO6 only).

The last option (available only on PDO1 to PDO6) allows the user to directly drive a voltage high enough to fully enhance an external N-FET, which is used to isolate, for example, a card-side voltage from a backplane supply (a PDO can sustain greater than 10.5 V into a 1  $\mu$ A load). The pull-down switches can also be used to drive status LEDs directly.

The data driving each of the PDOs can come from one of three sources. The source can be enabled in the PDOxCFG configuration register (see the AN-698 Application Note for details).

The data sources are as follows:

- Output from the SE.

- Directly from the SMBus. A PDO can be configured so that the SMBus has direct control over it. This enables software control of the PDOs. Therefore, a microcontroller can be used to initiate a software power-up/power-down sequence.

- On-chip clock. A 100 kHz clock is generated on the device. This clock can be made available on any of the PDOs. It can be used, for example, to clock an external device such as an LED.

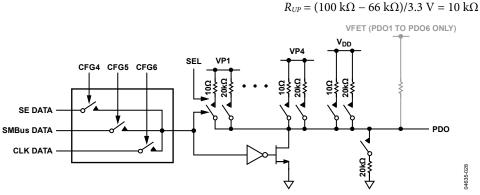

## **DEFAULT OUTPUT CONFIGURATION**

All of the internal registers in an unprogrammed ADM1067 device from the factory are set to 0. Because of this, the PDOx pins are pulled to GND by a weak ( $20 \text{ k}\Omega$ ) on-chip pull-down resistor.

As the input supply to the ADM1067 ramps up on VPx or VH, all PDOx pins behave as follows:

- Input supply = 0 V to 1.2 V. The PDOs are high impedance.

- Input supply = 1.2 V to 2.7 V. The PDOs are pulled to GND by a weak (20 kΩ) on-chip pull-down resistor.

- Supply > 2.7 V. Factory-programmed devices continue to pull all PDOs to GND by a weak (20 kΩ) on-chip pull-down resistor. Programmed devices download current EEPROM configuration data and the programmed setup is latched. The PDO then goes to the state demanded by the configuration, providing a known condition for the PDOs during power-up.

The internal pull-down can be overdriven with an external pull-up of suitable value tied from the PDOx pin to the required pull-up voltage. The 20 k $\Omega$  resistor must be accounted for in calculating a suitable value. For example, if PDOx must be pulled up to 3.3 V, and 5 V is available as an external supply, the pull-up resistor value is given by

$3.3~\mathrm{V} = 5~\mathrm{V} \times 20~\mathrm{k}\Omega/(R_{\rm UP}+20~\mathrm{k}\Omega)$

Therefore,

Figure 22. Programmable Driver Output

# SEQUENCING ENGINE overview

The ADM1067 sequencing engine (SE) provides the user with powerful and flexible control of sequencing. The SE implements a state machine control of the PDO outputs, with state changes conditional on input events. SE programs can enable complex control of boards such as power-up and power-down sequence control, fault event handling, and interrupt generation on warnings, among others. A watchdog function that verifies the continued operation of a processor clock can be integrated into the SE program. The SE can also be controlled via the SMBus, giving software or firmware control of the board sequencing.

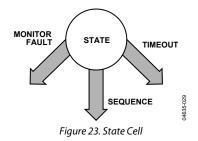

The SE state machine comprises 63 state cells. Each state has the following attributes:

- Monitors signals indicating the status of the 10 input pins, VP1 to VP4, VH, and VX1 to VX5.

- Can be entered from any other state.

- Three exit routes move the state machine onto a next state: sequence detection, fault monitoring, and timeout.

- Delay timers for the sequence and timeout blocks can be programmed independently and changed with each state change. The range of timeouts is from 0 ms to 400 ms.

- Output condition of the 10 PDO pins is defined and fixed within a state.

- Transition from one state to the next is made in less than 20 µs, which is the time needed to download a state definition from EEPROM to the SE.

The ADM1067 offers up to 63 state definitions. The signals monitored to indicate the status of the input pins are the outputs of the SFDs.

## WARNINGS

The SE also monitors warnings. These warnings can be generated when the ADC readings violate their limit register value or when the secondary voltage monitors on VPx and VH are triggered. The warnings are ORed together and available as a single warning input to each of the three blocks that enable exiting a state.

## SMBus JUMP (UNCONDITIONAL JUMP)

The SE can be forced to advance to the next state unconditionally. This enables the user to force the SE to advance. Examples of the use of this feature include moving to a margining state or debugging a sequence. The SMBus jump or go-to command can be seen as another input to sequence and timeout blocks to provide an exit from each state.

| State  | Sequence                                | Timeout                                             | Monitor                                             |

|--------|-----------------------------------------|-----------------------------------------------------|-----------------------------------------------------|

| IDLE1  | If VX1 is low, go to State IDLE2.       |                                                     |                                                     |

| IDLE2  | If VP1 is okay, go to State EN3V3.      |                                                     |                                                     |

| EN3V3  | If VP2 is okay, go to State EN2V5.      | If VP2 is not okay after 10 ms, go to State DIS3V3. | If VP1 is not okay, go to State IDLE1.              |

| DIS3V3 | If VX1 is high, go to State IDLE1.      |                                                     |                                                     |

| EN2V5  | If VP3 is okay, go to State PWRGD.      | If VP3 is not okay after 20 ms, go to State DIS2V5. | If VP1 or VP2 is not okay, go to State FSEL2.       |

| DIS2V5 | If VX1 is high, go to State IDLE1.      |                                                     |                                                     |

| FSEL1  | If VP3 is not okay, go to State DIS2V5. |                                                     | If VP1 or VP2 is not okay, go to State FSEL2.       |

| FSEL2  | If VP2 is not okay, go to State DIS3V3. |                                                     | If VP1 is not okay, go to State IDLE1.              |

| PWRGD  | If VX1 is high, go to State DIS2V5.     |                                                     | If VP1, VP2, or VP3 is not okay, go to State FSEL1. |

#### Table 7. Sample Sequence State Entries

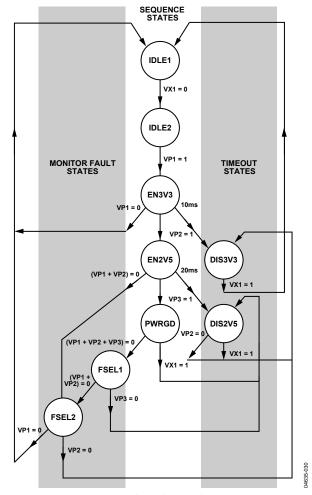

## SEQUENCING ENGINE APPLICATION EXAMPLE

The application in this section demonstrates the operation of the SE. Figure 25 shows how the simple building block of a single SE state can be used to build a power-up sequence for a threesupply system. Table 8 lists the PDO outputs for each state in the same SE implementation. In this system, a good 5 V supply on VP1 and the VX1 pin held low are the triggers required to start a power-up sequence. The sequence next turns on the 3.3 V supply, then the 2.5 V supply (assuming successful turn-on of the 3.3 V supply). When all three supplies have turned on correctly, the PWRGD state is entered, where the SE remains until a fault occurs on one of the three supplies or until it is instructed to go through a power-down sequence by VX1 going high.

Faults are dealt with throughout the power-up sequence on a case-by-case basis. The following three sections (the Sequence Detector section, the Monitoring Fault Detector section, and the Timeout Detector section) describe the individual blocks and use the sample application shown in Figure 25 to demonstrate the actions of the state machine.

#### **Sequence Detector**

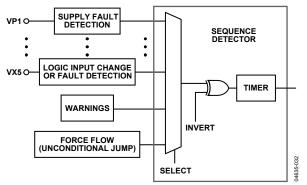

The sequence detector block is used to detect when a step in a sequence has been completed. It looks for one of the SE inputs to change state, and is most often used as the gate for successful progress through a power-up or power-down sequence. A timer block that is included in this detector can insert delays into a power-up or power-down sequence, if required. Timer delays can be set from 10  $\mu$ s to 400 ms. Figure 24 is a block diagram of the sequence detector.

Figure 24. Sequence Detector Block Diagram

If a timer delay is specified, the input to the sequence detector must remain in the defined state for the duration of the timer delay. If the input changes state during the delay, the timer is reset.

The sequence detector can also help to identify monitoring faults. In the sample application shown in Figure 25, the FSEL1 and FSEL2 states first identify which of the VP1, VP2, or VP3 pins has faulted, and then they take appropriate action.

Figure 25. Sample Application Flow Diagram

| PDO Outputs  | IDLE1 | IDLE2 | EN3V3 | EN2V5 | DIS3V3 | DIS2V5 | PWRGD | FSEL1 | FSEL2 |

|--------------|-------|-------|-------|-------|--------|--------|-------|-------|-------|

| PDO1 = 3V3ON | 0     | 0     | 1     | 1     | 0      | 1      | 1     | 1     | 1     |

| PDO2 = 2V5ON | 0     | 0     | 0     | 1     | 1      | 0      | 1     | 1     | 1     |

| PDO3 = FAULT | 0     | 0     | 0     | 0     | 1      | 1      | 0     | 1     | 1     |

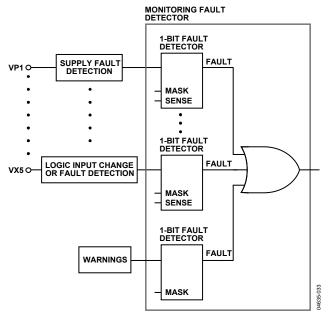

#### Monitoring Fault Detector

The monitoring fault detector block is used to detect a failure on an input. The logical function implementing this is a wide OR gate that can detect when an input deviates from its expected condition. The clearest demonstration of the use of this block is in the PWRGD state, where the monitor block indicates that a failure on one or more of the VP1, VP2, or VP3 inputs has occurred.

No programmable delay is available in this block because the triggering of a fault condition is likely to be caused by a supply falling out of tolerance. In this situation, the device needs to react as quickly as possible. Some latency occurs when moving out of this state because it takes a finite amount of time (~20  $\mu$ s) for the state configuration to download from the EEPROM into the SE. Figure 26 is a block diagram of the monitoring fault detector.

Figure 26. Monitoring Fault Detector Block Diagram

### **Timeout Detector**

The timeout detector allows the user to trap a failure to ensure proper progress through a power-up or power-down sequence.

In the sample application shown in Figure 25, the timeout nextstate transition is from the EN3V3 and EN2V5 states. For the EN3V3 state, the signal 3V3ON is asserted on the PDO1 output pin upon entry to this state to turn on a 3.3 V supply.

This supply rail is connected to the VP2 pin, and the sequence detector looks for the VP2 pin to go above its undervoltage threshold, which is set in the supply fault detector (SFD) attached to that pin.

The power-up sequence progresses when this change is detected. If, however, the supply fails (perhaps due to a short circuit overloading this supply), the timeout block traps the problem. In this example, if the 3.3 V supply fails within 10 ms, the SE moves to the DIS3V3 state and turns off this supply by bringing PDO1 low. It also indicates that a fault has occurred by taking PDO3 high. Timeout delays of 100  $\mu$ s to 400 ms can be programmed.

## FAULT AND STATUS REPORTING

The ADM1067 has a fault latch for recording faults. Two registers, FSTAT1 and FSTAT2, are set aside for this purpose. A single bit is assigned to each input of the device, and a fault on that input sets the relevant bit. The contents of the fault register can be read out over the SMBus to determine which input(s) faulted. The fault register can be enabled or disabled in each state. To latch data from one state, ensure that the fault latch is disabled in the following state. This ensures that only real faults are captured and not, for example, undervoltage conditions that may be present during a power-up or power-down sequence.

The ADM1067 also has a number of status registers. These include more detailed information, such as whether an undervoltage or overvoltage fault is present on a particular input. The status registers also include information on ADC limit faults. Note that the data in the status registers is not latched in any way and, therefore, is subject to change at any time.

See the AN-698 Application Note for full details about the ADM1067 registers.

# SUPPLY MARGINING overview

It is often necessary for the system designer to adjust supplies, either to optimize their level or force them away from nominal values to characterize the system performance under these conditions. This is a function typically performed during an incircuit test (ICT), such as when the manufacturer wants to guarantee that the product under test functions correctly at nominal supplies minus 10%.

## **OPEN-LOOP SUPPLY MARGINING**

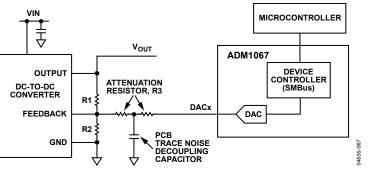

The simplest method of margining a supply is to implement an open-loop technique (see Figure 27). A popular way to do this is to switch extra resistors into the feedback node of a power module, such as a dc-to-dc converter or low dropout regulator (LDO). The extra resistor alters the voltage at the feedback or trim node and forces the output voltage to margin up or down by a certain amount.

The ADM1067 can perform open-loop margining for up to six supplies. The six on-board voltage DACs (DAC1 to DAC6) can drive into the feedback pins of the power modules to be margined. The simplest circuit to implement this function is an attenuation resistor that connects the DACx pin to the feedback node of a dc-to-dc converter. When the DACx output voltage is set equal to the feedback voltage, no current flows into the attenuation resistor, and the dc-to-dc converter output voltage does not change. Taking DACx above the feedback voltage forces current into the feedback node, and the output of the dc-to-dc converter is forced to fall to compensate for this. The dc-to-dc converter output can be forced high by setting the DACx output voltage lower than the feedback node voltage. The series resistor can be split in two, and the node between them can be decoupled with a capacitor to ground. This can help to decouple any noise picked up from the board. Decoupling to a ground local to the dc-todc converter is recommended.

The ADM1067 can be commanded to margin a supply up or down over the SMBus by updating the values on the relevant DAC output.

To implement open-loop margining

- 1. Disable the six DAC outputs.

- 2. Set the DAC output voltage equal to the voltage on the feedback node.

- 3. Enable the DAC.

- Assert MUP (drive logic high). The DAC voltage moves down to the value set in the DNLIM register (see the AN-698 Application Note). The output of the dc-to-dc converter rises to compensate for this, that is, margin up.

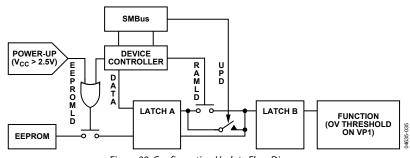

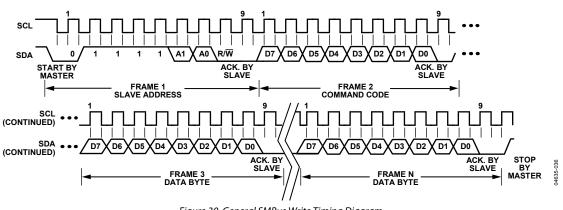

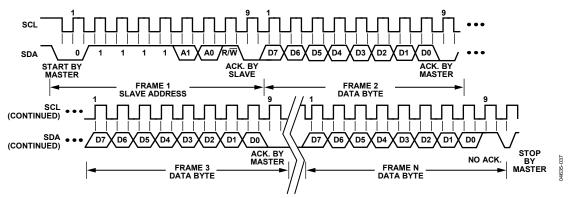

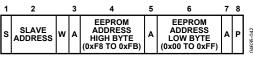

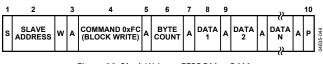

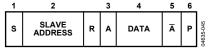

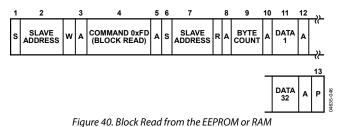

- Assert MDN (drive logic high). The DAC voltage moves down to the value set in the DPLIM register (see the AN-698 Application Note). The output of the dc-to-dc converter drops to compensate for this, that is, margin down.