HSON8-P-0505-1.27

Weight: 0.068 g (typ.)

**TOSHIBA CMOS Integrated Circuit Silicon Monolithic**

# **TCV7100F**

#### **Buck DC-DC Converter IC**

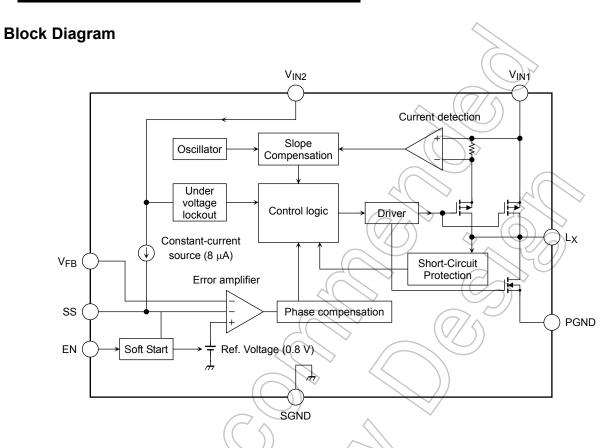

The TCV7100F is a single-chip buck DC-DC converter IC. The TCV7100F contains high-speed and low-on-resistance power MOSFETs for the main switch and synchronous rectifier to achieve high efficiency.

#### **Features**

- Enables up to 2.5 A of load current (IOUT) with a minimum of external components.

- High efficiency:  $\eta = 95\%$  (typ.)

$$(@V_{IN} = 5 \text{ V}, V_{OUT} = 3.3 \text{ V}, I_{OUT} = 1 \text{ A})$$

- Operating voltage range:  $V_{IN} = 2.7$  to 5.5 V

- Low ON-resistance: RDS (ON) =  $0.12 \Omega$  (high side) /  $0.12 \Omega$  (low-side) typical (@V<sub>IN</sub> = 5 V, T<sub>i</sub> = 25°C)

- High oscillation frequency: fosc = 800 kHz (typ.)

- Feedback voltage:  $V_{FB} = 0.8 \text{ V} \pm 1\% \text{ (@T_i = 25^{\circ}C)}$

- Uses internal phase compensation to achieve high efficiency with a minimum of external components.

- Allows the use of a small surface-mount ceramic capacitor as an output filter capacitor.

- Housed in a small surface-mount package (SOP Advance) with a low thermal resistance.

- Soft-start time adjustable by an external capacitor

# **Part Marking Pin Assignment** SS $V_{\mathsf{FB}}$ Part Number (or abbreviation code) Lot No: **TCV** 7100F 2 1 3 The dot (•) on the top surface indicates pin 1.

\*: The lot number consists of three digits. The first digit represents the last digit of the year of manufacture, and the following two digits indicates the week of manufacture between 01 and either 52 or 53.

PGND

$V_{IN1}$

This product has a MOS structure and is sensitive to electrostatic discharge. Handle with care.

The product(s) in this document ("Product") contain functions intended to protect the Product from temporary small overloads such as minor short-term overcurrent, or overheating. The protective functions do not necessarily protect Product under all circumstances. When incorporating Product into your system, please design the system (1) to avoid such overloads upon the Product, and (2) to shut down or otherwise relieve the Product of such overload conditions immediately upon occurrence. For details, please refer to the notes appearing below in this document and other documents referenced in this document.

2010-02-24

# **Ordering Information**

| Part Number         | Shipping                            |

|---------------------|-------------------------------------|

| TCV7100F (TE12L, Q) | Embossed tape (3000 units per reel) |

# **Pin Description**

| Pin No. | Symbol           | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PGND             | Ground pin for the output section                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2       | V <sub>IN1</sub> | Input pin for the output section This pin is placed in the standby state if $V_{EN}$ = low. Standby current is 10 $\mu$ A or less.                                                                                                                                                                                                                                                                                                     |

| 3       | VIN2             | Input pin for the control section This pin is placed in the standby state if $V_{EN}$ = low. Standby current is 10 $\mu$ A or less.                                                                                                                                                                                                                                                                                                    |

| 4       | SGND             | Ground pin for the control section                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5       | VFB              | Feedback pin This input is fed into an internal error amplifier with a reference voltage of 0.8 V (typ.).                                                                                                                                                                                                                                                                                                                              |

| 6       | ss               | Soft-start pin When the SS input is left open, the soft-start time is 1 ms (typ.). The soft-start time can be adjusted with an external capacitor. The external capacitor is charged from a $8-\mu A$ (typ.) constant-current source, and the reference voltage of the error amplifier is regulated between 0 V and 0.8 V. The external capacitor is discharged when EN = low and in case of undervoltage lockout or thermal shutdown. |

| 7       | EN               | Enable pin When EN $\geq$ 1.5 V (@ V <sub>IN</sub> = 5 V), the internal circuitry is allowed to operate and thus enable the switching operation of the output section. When EN $\leq$ 0.5 V (@ V <sub>IN</sub> = 5 V), the internal circuitry is disabled, putting the TCV7100F in Standby mode. This pin has an internal pull-down resistor of approx. 500 k $\Omega$ .                                                               |

| 8       | L <sub>X</sub>   | Switch pin This pin is connected to high-side P-channel MOSFET and low-side N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                          |

# Absolute Maximum Ratings (Ta = 25°C)

| Characteristics                                       |               | Symbol                            | Rating               | Unit |

|-------------------------------------------------------|---------------|-----------------------------------|----------------------|------|

| Input pin voltage for the output section              |               | V <sub>IN1</sub>                  | -0.3 to 6            | V    |

| Input pin voltage for the co                          | ntrol section | V <sub>IN2</sub>                  | √2 −0.3 to 6         |      |

| Feedback pin voltage                                  |               | V <sub>FB</sub>                   | -0.3 to 6            | V    |

| Soft-start pin voltage                                |               | V <sub>SS</sub>                   | -0.3 to 6            | V    |

| Enable pin voltage                                    |               | V <sub>EN</sub>                   | -0.3 to 6            | V    |

| V <sub>EN</sub> – V <sub>IN2</sub> voltage difference |               | V <sub>EN</sub> -V <sub>IN2</sub> | $V_{EN}-V_{IN2}<0.3$ | ٧    |

| Switch pin voltage                                    | (Note 1)      | $V_{LX}$                          | -0.3 to 6            | V    |

| Switch pin current                                    |               | $I_{LX}$                          | ±3.0                 | A C  |

| Power dissipation                                     | (Note 2)      | $P_{D}$                           | 2.2                  | W    |

| Operating junction temperature                        |               | T <sub>jopr</sub>                 | -40 to125            | (°C) |

| Junction temperature                                  | (Note 3)      | Tj                                | 150                  | \%C  |

| Storage temperature                                   |               | T <sub>stg</sub>                  | -55 to150            | )\o  |

Note: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings and the operating ranges.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook ("Handling Precautions"/"Derating Concept and Methods") and individual reliability data (i.e. reliability test report and estimated failure rate, etc)

Note 1: The switch pin voltage ( $V_{LX}$ ) doesn't include the peak voltage generated by TCV7100F's switching. A negative voltage generated in dead time is permitted among the switch pin current ( $I_{LX}$ ).

# Thermal Resistance Characteristics

| Characteristics                         | Symbol                | Max              | Unit |

|-----------------------------------------|-----------------------|------------------|------|

| Thermal resistance, junction to ambient | R <sub>th (j-a)</sub> | 44.6<br>(Note 2) | °C/W |

| Thermal resistance, junction to case    | R <sub>th (j-c)</sub> | 4.17             | °C/W |

Single-pulse measurement: pulse width t=10(s)

Note 3: The TCV7100F may into thermal shutdown at the rated maximum junction temperature. Thermal design is required to ensure that the rated maximum operating junction temperature, T<sub>jopr</sub>, will not be exceeded.

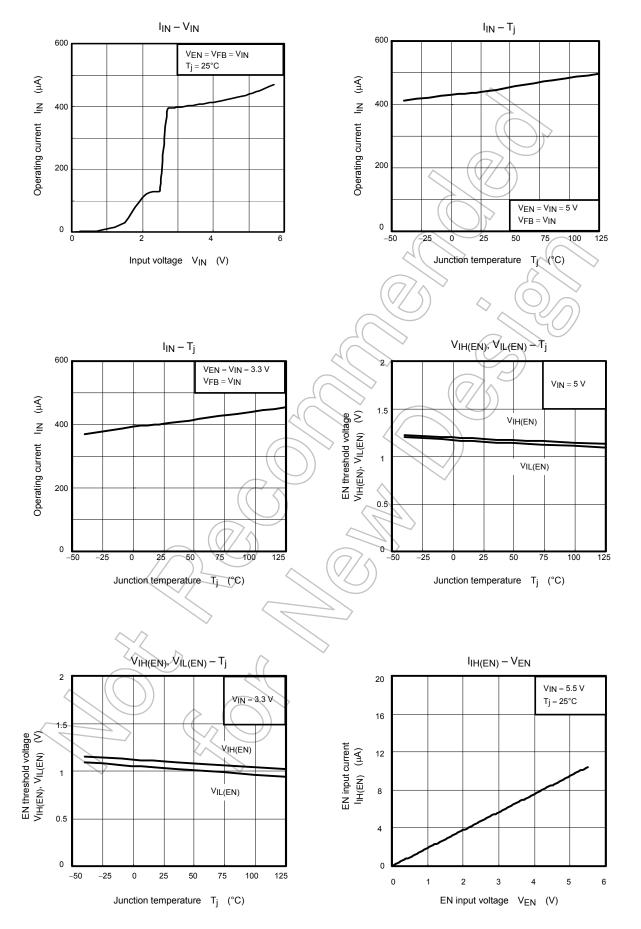

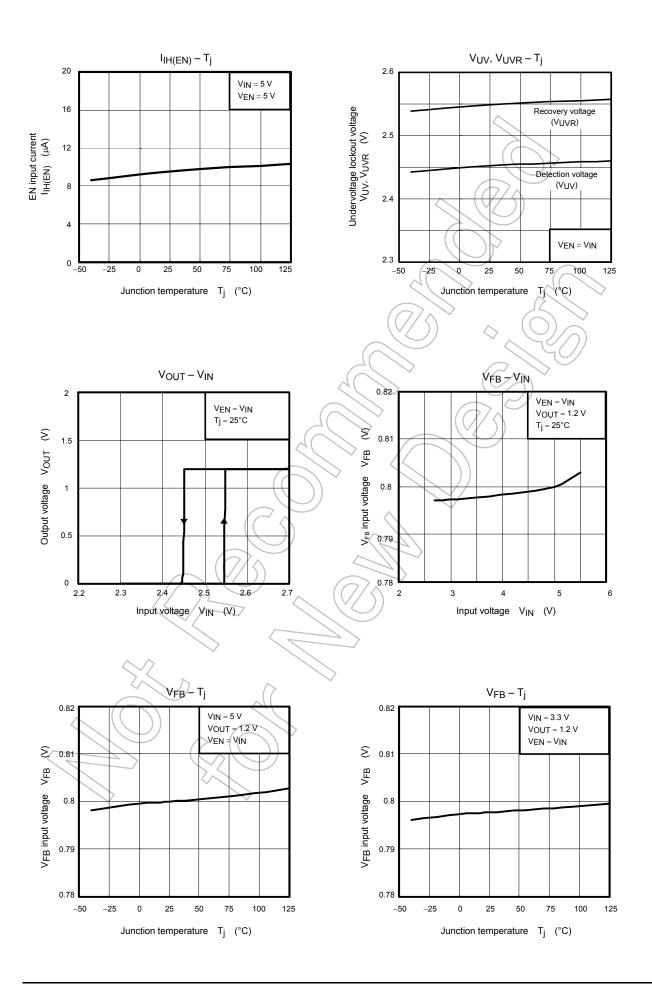

# Electrical Characteristics (T $_{j}$ = 25 $^{\circ}\text{C},~V_{IN1}$ = $V_{IN2}$ = 2.7 to 5.5 V, unless otherwise specified)

| Characteristics                     |                       | Symbol                     | Test Condition                                                                                                                    |       | Тур.    | Max   | Unit |  |

|-------------------------------------|-----------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|------|--|

| Operating input voltage             |                       | V <sub>IN (OPR)</sub>      |                                                                                                                                   |       | _       | 5.5   | V    |  |

| Operating current                   |                       | I <sub>IN</sub>            | V <sub>IN1</sub> = V <sub>IN2</sub> = V <sub>EN</sub> = V <sub>FB</sub> = 5 V                                                     | _     | 450     | 600   | μΑ   |  |

| Output voltage range                |                       | V <sub>OUT</sub> (OPR)     | V <sub>EN</sub> = V <sub>IN1</sub> = V <sub>IN2</sub>                                                                             |       | _       | _     | V    |  |

| Standby current                     |                       | IN (STBY) 1                | $V_{IN1} = V_{IN2} = 5 \text{ V}, V_{EN} = 0 \text{ V}$<br>$V_{FB} = 0.8 \text{ V}$                                               |       | 7       | 10    | μА   |  |

| Standby Current                     |                       | IN (STBY) 2                | V <sub>IN1</sub> = V <sub>IN2</sub> = 3.3 V, V <sub>EN</sub> = 0 V<br>V <sub>FB</sub> = 0.8 V                                     |       | )<br> - | 10    |      |  |

| High-side switch le                 | eakage current        | I <sub>LEAK</sub> (H)      | V <sub>IN1</sub> = V <sub>IN2</sub> = 5 V, V <sub>EN</sub> = 0 V<br>V <sub>FB</sub> = 0.8 V, V <sub>LX</sub> = 0 V                | )     | -       | 10    | μА   |  |

|                                     |                       | V <sub>IH</sub> (EN) 1     | V <sub>IN1</sub> = V <sub>IN2</sub> = 5 V                                                                                         | 1.5   | _       | _     |      |  |

| EN threshold volta                  | 190                   | V <sub>IH</sub> (EN) 2     | V <sub>IN1</sub> = V <sub>IN2</sub> = 3.3 V                                                                                       | 1.5   | ))      |       | \/   |  |

| LIN tillesiloid voita               | ige                   | V <sub>IL</sub> (EN) 1     | V <sub>IN1</sub> = V <sub>IN2</sub> = 5 V                                                                                         | _     | 4       | 0.5   | V    |  |

|                                     |                       | V <sub>IL (EN) 2</sub>     | V <sub>IN1</sub> = V <sub>IN2</sub> = 3.3 V                                                                                       | -/    | 7/      | 0.5   |      |  |

| EN input current                    |                       | I <sub>IH</sub> (EN) 1     | V <sub>IN1</sub> = V <sub>IN2</sub> = 5 V, V <sub>EN</sub> = 5 V                                                                  | 6 13  |         | 13    | ^    |  |

| LIV IIIpat carrent                  |                       | I <sub>IH</sub> (EN) 2     | $V_{IN1} = V_{IN2} = 3.3 \text{ V}, V_{EN} = 3.3 \text{ V}$                                                                       | 4     | 4       | 9     | μА   |  |

| V <sub>FB</sub> input voltage       |                       | V <sub>FB1</sub>           | V <sub>IN</sub> = 5 V, V <sub>EN</sub> = 5 V<br>Tj = 0 to 85°C                                                                    | 0.792 | 0.8     | 0.808 |      |  |

|                                     |                       | V <sub>FB2</sub>           | V <sub>IN</sub> = 3.3 V, V <sub>EN</sub> = 3.3 V<br>Tj = 0 to 85°C                                                                |       | 0.8     | 0.808 | V    |  |

| V <sub>FB</sub> input current       |                       | I <sub>FB</sub>            | V <sub>IN1</sub> = V <sub>IN2</sub> = 2.7 to 5.5 V<br>V <sub>FB</sub> = V <sub>IN2</sub>                                          |       | _       | 1     | μА   |  |

| High-side switch o                  | on-state resistance   | R <sub>DS</sub> (ON) (H) 1 | $V_{IN1} = V_{IN2} = 5 \text{ V}, V_{EN} = 5 \text{ V}$<br>$I_{LX} = -1 \text{ A}$                                                |       | 0.12    |       |      |  |

| Trigit-side switch o                | m-state resistance    | R <sub>DS</sub> (ON) (H) 2 | $V_{IN1} = V_{IN2} = 3.3 \text{ V}, V_{EN} = 3.3 \text{ V}$<br>$I_{LX} = -1 \text{ A}$                                            |       | 0.13    | _     | 32   |  |

| Low-side switch on-state resistance |                       | RDS (ON) (L) 1             | $V_{IN1} = V_{IN2} = 5 \text{ V}, V_{EN} = 5 \text{ V}$<br>$I_{LX} = 1 \text{ A}$                                                 | _     | 0.12    | _     | Ω    |  |

|                                     |                       | RDS (ON) (L) 2             | $V_{IN1} = V_{IN2} = 3.3 \text{ V}, V_{EN} = 3.3 \text{ V}$<br>$I_{LX} = 1 \text{ A}$                                             |       | 0.13    | _     | 22   |  |

| Oscillation frequer                 | ncy                   | fosc                       | $V_{IN1} = V_{IN2} = V_{EN} = 5 \text{ V}$                                                                                        |       | 800     | 960   | kHz  |  |

| Internal soft-start time            |                       | tss                        | V <sub>IN1</sub> = V <sub>IN2</sub> = 5 V, I <sub>OUT</sub> = 0 A,<br>Measured between 0% and 90% points<br>at V <sub>OUT</sub> . |       | 1       | 1.5   | ms   |  |

| External soft-start charge current  |                       | I <sub>SS</sub>            | V <sub>IN1</sub> = V <sub>IN2</sub> = 5 V, V <sub>EN</sub> = 5 V                                                                  |       | -8      | -11   | μΑ   |  |

| High-side switch duty cycle         |                       | Dmax                       | V <sub>IN1</sub> = V <sub>IN2</sub> = 2.7 to 5.5 V                                                                                | _     | _       | 100   | %    |  |

| Thermal                             | Detection temperature | TSD                        | V <sub>IN1</sub> = V <sub>IN2</sub> = 5 V                                                                                         | _     | 150     | _     | °C   |  |

| shutdown (TSD)                      | Hysteresis            | ΔT <sub>SD</sub>           | V <sub>IN1</sub> = V <sub>IN2</sub> = 5 V                                                                                         | _     | 15      | _     |      |  |

|                                     | Detection voltage     | V <sub>UV</sub>            | $V_{EN} = V_{IN1} = V_{IN2}$                                                                                                      | 2.35  | 2.45    | 2.6   | V    |  |

| Undervoltage<br>lockout (UVLO)      | Recovery voltage      | V <sub>UVR</sub>           | $V_{EN} = V_{IN1} = V_{IN2}$                                                                                                      | 2.45  | 2.55    | 2.7   |      |  |

|                                     | Hysteresis            | $\Delta V_{UV}$            | $V_{EN} = V_{IN1} = V_{IN2}$                                                                                                      |       | 0.1     | _     |      |  |

| L <sub>X</sub> current limit        |                       | I <sub>LIM</sub>           | V <sub>IN1</sub> = V <sub>IN2</sub> = 5 V, V <sub>OUT</sub> = 2 V                                                                 | 2.9   | 4.2     | _     | Α    |  |

4 2010-02-24

#### **Note on Electrical Characteristics**

The test condition  $T_j = 25$  °C means a state where any drifts in electrical characteristics incurred by an increase in the chip's junction temperature can be ignored during pulse testing.

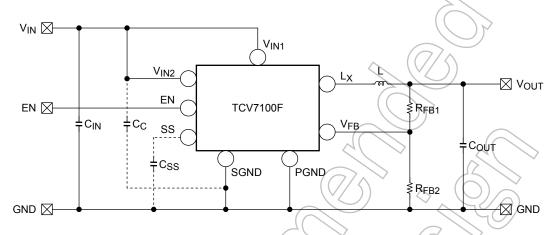

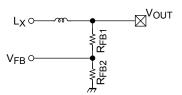

## **Application Circuit Example**

Figure 1 shows a typical application circuit using a low-ESR electrolytic or ceramic capacitor for COUT.

Figure 1 TCV7100F Application Circuit Example

Component values (reference value@  $V_{IN} = 5 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $T_{a} = 25$ °C)

$C_{IN}$ : Input filter capacitor = 10  $\mu F$

(ceramic capacitor: GRM21BB30J106K manufactured by Murata Manufacturing Co., Ltd.)

COUT: Output filter capacitor = 47 µF/

(ceramic capacitor: GRM31CB30J476M manufactured by Murata Manufacturing Co., Ltd.)

RFB1: Output voltage setting resistor =  $7.5 \text{ k}\Omega$

RFB2: Output voltage setting resistor =  $2.4 \text{ k}\Omega$

L: Inductor =  $2.2 \mu H$  (RLF7030T-2R2M5R4 manufactured by TDK-EPC Corporation)

CSS is a capacitor for adjusting the soft-start time.

CC is a decoupling capacitor of Input pin for the control section.

(Connect it when the circuit operation is unstable due to the board layout or a feature of the CIN.)

Examples of Component Values (For Reference Only)

| Output Voltage Setting Vout | Inductance<br>L | Input Capacitance<br>C <sub>IN</sub> | Output Capacitance<br>C <sub>OUT</sub> | Feedback Resistor<br>R <sub>FB1</sub> | Feedback Resistor<br>R <sub>FB2</sub> |

|-----------------------------|-----------------|--------------------------------------|----------------------------------------|---------------------------------------|---------------------------------------|

| 1.2 V                       | 2.2 μΗ          | 10 μF                                | 68 μF                                  | 7.5 kΩ                                | 15 kΩ                                 |

| 1.51 V                      | 2.2 μH          | 10 μF                                | 68 μF                                  | 16 kΩ                                 | 18 kΩ                                 |

| 1.8 V                       | 2.2 μH          | 10 μF                                | 68 μF                                  | 15 kΩ                                 | 12 kΩ                                 |

| 2.5 V                       | 2.2 μΗ          | 10 μF                                | 47 μF                                  | 5.1 kΩ                                | 2.4 kΩ                                |

| 3.3 V                       | 2.2 μΗ          | 10 μF                                | 47 μF                                  | 7.5 kΩ                                | 2.4 kΩ                                |

Component values need to be adjusted, depending on the TCV7100F's I/O conditions and the board layout.

5

# **Application Notes**

#### **Inductor Selection**

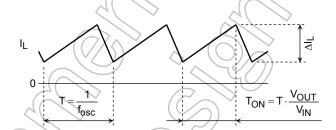

The inductance required for inductor L can be calculated as follows:

$$L = \frac{V_{IN} - V_{OUT}}{f_{osc} \cdot \Delta I_L} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \cdots \cdots (1)$$

V<sub>IN</sub>: Input voltage (V) V<sub>OUT</sub>: Output voltage (V)

f<sub>osc</sub>: Oscillation frequency = 800 kHz (typ.)

ΔIL: Inductor ripple current (A)

\*: Generally,  $\Delta I_L$  should be set to approximately 30% of the maximum output current. Since the maximum output current of the TCV7100F is 2.5 A,  $\Delta I_L$  should be 0.75 A or so. The inductor should have a current rating greater than the peak output current of 2.9 A. If the inductor current rating is exceeded, the inductor becomes saturated, leading to an unstable DC-DC converter operation.

When  $V_{IN} = 5$  V and  $V_{OUT} = 3.3$  V, the required inductance can be calculated as follows. Be sure to select an appropriate inductor, taking the input voltage range into account.

$$\begin{split} L &= \frac{V_{IN} - V_{OUT}}{f_{osc} \cdot \Delta I_L} \cdot \frac{V_{OUT}}{V_{IN}} \\ &= \frac{5 \text{ V} - 3.3 \text{ V}}{800 \text{kHz} \cdot 0.75 \text{A}} \cdot \frac{3.3 \text{ V}}{5 \text{ V}} \quad \cdots \cdots (2) \\ &= 1.87 \; \mu \text{H} \end{split}$$

Figure 2 Inductor Current Waveform

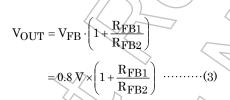

# **Setting the Output Voltage**

A resistive voltage divider is connected as shown in Figure 3 to set the output voltage; it is given by Equation 3 based on the reference voltage of the error amplifier (0.8 V typ.), which is connected to the Feedback pin, VFB. RFB1 should be up to  $30~k\Omega$  or so, because an extremely large-value RFB1 incurs a delay due to parasitic capacitance at the VFB pin. It is recommended that resistors with a precision of  $\pm 1\%$  or higher be used for RFB1 and RFB2.

6

Figure 3 Output Voltage Setting Resistors

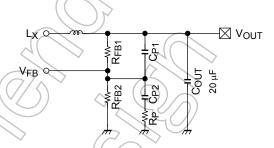

## **Output Filter Capacitor Selection**

Use a low-ESR electrolytic or ceramic capacitor as the output filter capacitor. Since a capacitor is generally sensitive to temperature, choose one with excellent temperature characteristics. As a rule of thumb, its capacitance should be 30  $\mu F$  or greater for applications where  $V_{OUT} \geq 2$  V, and 60  $\mu F$  or greater for applications where  $V_{OUT} < 2$  V. The capacitance should be set to an optimal value that meets the system's ripple voltage requirement and transient load response characteristics. The phase margin tends to decrease as the output voltage is getting low. Enlarge a capacitance for output flatness when phase margin is insufficient, or the transient load response characteristics cannot be satisfied. Since the ceramic capacitor has a very low ESR value, it helps reduce the output ripple voltage; however, because the ceramic capacitor provides less phase margin, it should be thoroughly evaluated.

Output filter capacitors with a smaller value mentioned above can be used by adding a phase compensation circuit to the VFB pin. For example, suppose using two 10-µF ceramic capacitors as output filter capacitors; then the phase compensation circuit should be programmed as follows:

$$C_{P1} (\mu F) = 2 / R_{FB1} (\Omega)$$

......(4)

$C_{P2} (\mu F) = C_{P1} (\mu F) \times 10$  .....(5)

$R_{FB2} / R_{P} = R_{FB1} / 2$  .....(6)

- \* Set the upper cut-off frequency of CP<sub>1</sub> and RFB<sub>1</sub> to approx. 80 kHz (f<sub>OSC</sub>/10). ······(4)

- \* Choose the value of CP2 to produce zero-frequency at 1/10th the upper cut-off frequency. .....(5)

- \* If RFB2 is less than half of RFB1, RP and CP2 are not necessary. ......(6)

(Only CP1 allows programming of VOUT above 1.8 V.)

Figure 4 Phase Compensation Circuit

Examples of Component Values in the Phase Compensation Circuit (For Reference Only)

The following values need tuning, depending on the TCV7100F's I/O conditions and the board layout.

| V <sub>OUT</sub> | C <sub>OUT</sub> | R <sub>FB1</sub> | R <sub>FB2</sub> | Rp                        | C <sub>P1</sub> | C <sub>P2</sub> |

|------------------|------------------|------------------|------------------|---------------------------|-----------------|-----------------|

| 1.2 V            | 10 μF × 2        | 7.5 kΩ           | 15 kΩ            | 4.7 kΩ                    | 270 pF          | 2700 pF         |

| 1.51 V           | 10 μF × 2        | 16 kΩ            | 18 kΩ            | 15 kΩ                     | 120 pF          | 1200 pF         |

| 1.8 V            | 10 μF × 2        | 15 kΩ            | 12 kΩ            | $\langle \rangle \rangle$ | 180 pF          | _               |

| 2.5 V            | 10 μF × 2        | 5.1 kΩ           | 2.4 kΩ           |                           | 390 pF          | _               |

| 3.3 V            | 10 μF × 2        | 7.5 kΩ           | 2.4 kΩ           |                           | 270 pF          | _               |

The phase compensation circuit shown above delivers good transient load response characteristics with small-value output filter capacitors by programming f<sub>0</sub> (the frequency at which the open-loop gain is equal to 0dB) to a high frequency. For output filter capacitors, use low-ESR ceramic capacitors with excellent temperature characteristics (such as the JIS B characteristic). Although the external phase compensation circuit improves noise immunity, they should be thoroughly evaluated to ensure that the system's ripple voltage requirement and transient load response characteristics are met.

#### **Soft-Start Feature**

The TCV7100F has a soft-start feature.

If the SS pin is left open, the soft-start time, tss, for Vour defaults to 1 ms (typ.) internally.

The soft-start time can be extended by adding an external capacitor (CSS) between the SS and SGND pins. The soft-start time can be calculated as follows:

$$\mathbf{t}_{\mathrm{SS2}} = 0.1 \cdot \mathbf{C}_{\mathrm{SS}}$$

······(7)

SS2: Soft-start time (in seconds) when an external capacitor is connected between SS and SGND.

CSS: Capacitor value (µF)

The soft-start feature is activated when the TCV7100F exits the undervoltage lockout (UVLO) state after power-up and when the voltage at the EN pin has changed from logic low to logic high.

2010-02-24

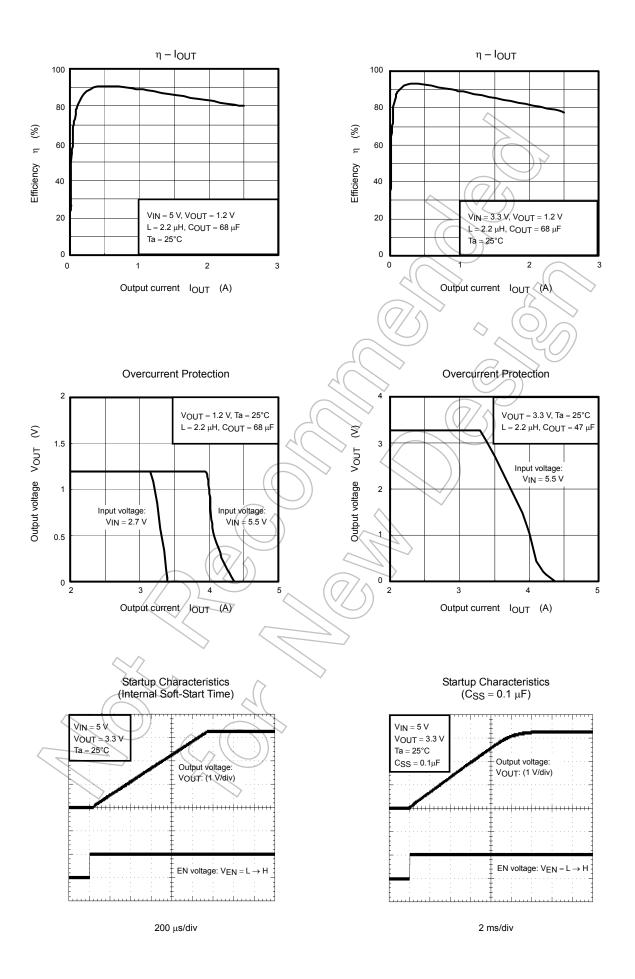

## **Overcurrent Protection (OCP)**

The TCV7100F has maximum current limiting. The TCV7100F limits the ON time of high side switching transistor and decreases output voltage when the peak value of the Lx terminal current exceeds switching terminal peak current limitation  $I_{LIM}$ =4.2A(typ.).

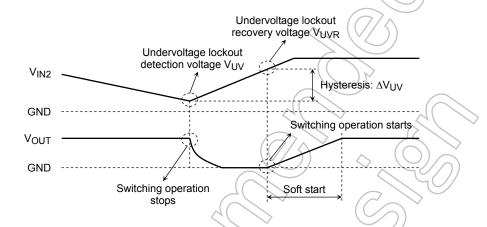

## **Undervoltage Lockout (UVLO)**

The TCV7100F has undervoltage lockout (UVLO) protection circuitry. The TCV7100F does not provide output voltage (V<sub>OUT</sub>) until the input voltage has reached V<sub>UVR</sub> (2.55 V typ.). UVLO has hysteresis of 0.1 V (typ.). After the switch turns on, if V<sub>IN2</sub> drops below V<sub>UV</sub> (2.45 V typ.), UVLO shuts off the switch at V<sub>OUT</sub>.

Figure 5 Undervoltage Lockout Operation

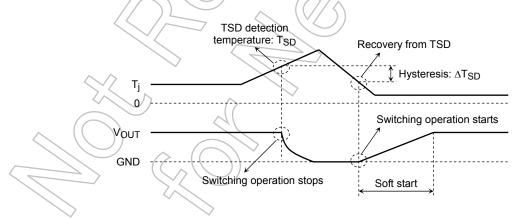

## Thermal Shutdown (TSD)

The TCV7100F provides thermal shutdown. When the junction temperature continues to rise and reaches TSD (150°C typ.), the TCV7100F goes into thermal shutdown and shuts off the power supply. TSD has a hysteresis of about 15°C (typ.). The device is enabled again when the junction temperature has dropped by approximately 15°C from the TSD trip point. The device resumes the power supply when the soft-start circuit is activated upon recovery from TSD state.

Thermal shutdown is intended to protect the device against abnormal system conditions. It should be ensured that the TSD circuit will not be activated during normal operation of the system.

Figure 6 Thermal Shutdown Operation

8

# **Usage Precautions**

- The input voltage, output voltage, output current and temperature conditions should be considered when selecting capacitors, inductors and resistors. These components should be evaluated on an actual system prototype for best selection.

- External components such as capacitors, inductors and resistors should be placed as close to the TCV7100F as possible.

- The TCV7100F has an ESD diode between the EN and VIN2 pins. The voltage between these pins should satisfy VEN - VIN2 < 0.3 V.</li>

- C<sub>IN</sub> should be connected as close to the PGND and V<sub>IN1</sub> pins as possible. Operation might become unstable due to board layout. In that case, add a decoupling capacitor (C<sub>C</sub>) of 0.1 μF to 1 μF between the SGND and V<sub>IN2</sub> pins.

- The minimum programmable output voltage is 0.8 V (typ.). If the difference between the input and output voltages is small, the output voltage might not be regulated accurately and fluctuate significantly.

- When TCV7100F is in operation, a negative voltage is generated since regeneration current flows through the switch pin (Lx). Even if the current flows through the low side parasitic diode during the dead time of switching transistor, operation is undisturbed so an external flywheel diode is unnecessary. If there is the possibility of an external negative voltage generation, add a diode for protection.

- SGND pin is connected with the back of IC chip and serves as the heat radiation pin. Secure the area of a GND pattern as large as possible for greater of heat radiation.

- The overcurrent protection circuits in the Product are designed to temporarily protect Product from minor overcurrent of brief duration. When the overcurrent protective function in the Product activates, immediately cease application of overcurrent to Product. Improper usage of Product, such as application of current to Product exceeding the absolute maximum ratings, could cause the overcurrent protection circuit not to operate properly and/or damage Product permanently even before the protection circuit starts to operate.

- The thermal shutdown circuits in the Product are designed to temporarily protect Product from minor overheating of brief duration. When the overheating protective function in the Product activates, immediately correct the overheating situation. Improper usage of Product, such as the application of heat to Product exceeding the absolute maximum ratings, could cause the overheating protection circuit not to operate properly and/or damage Product permanently even before the protection circuit starts to operate.

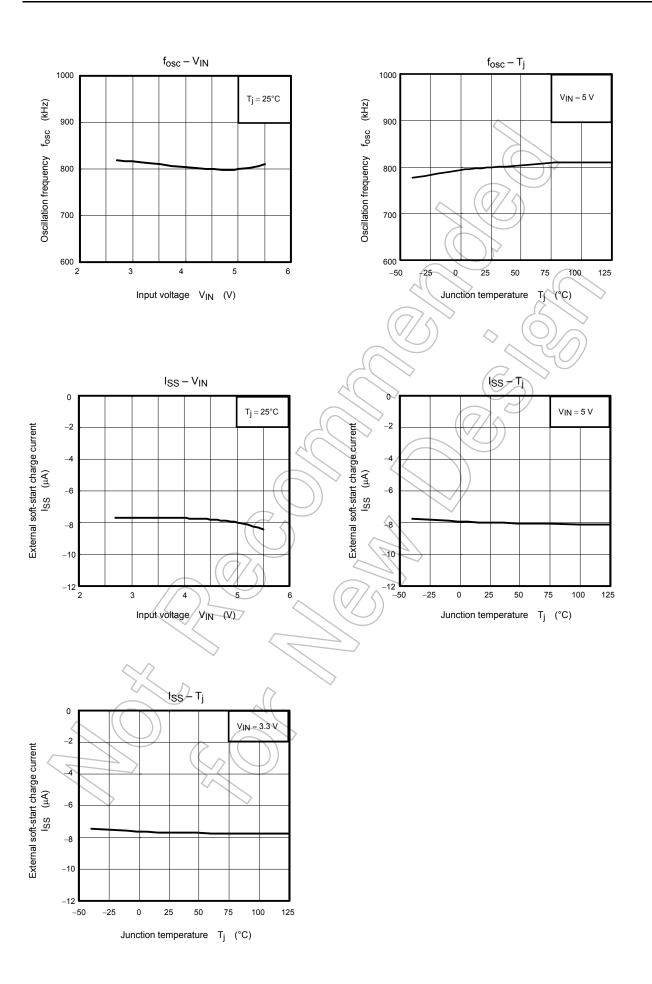

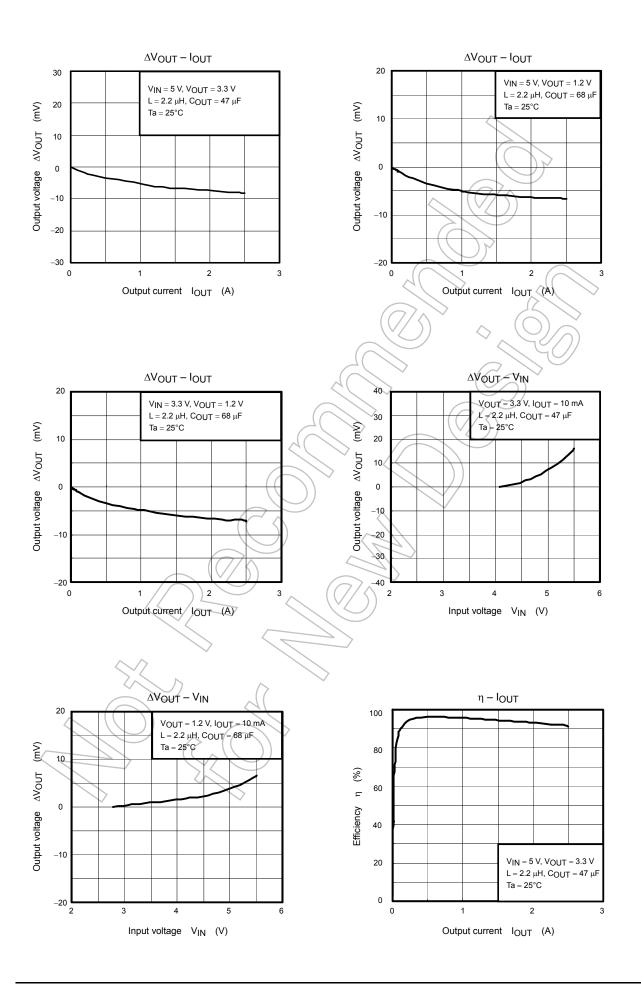

# **Typical Performance Characteristics**

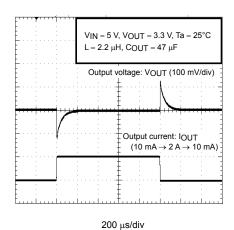

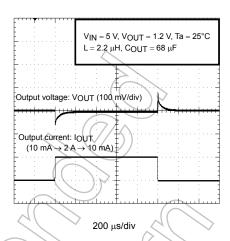

#### Load Response Characteristics

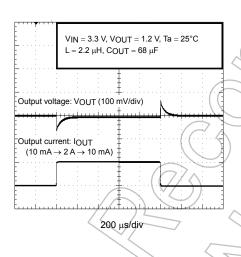

#### Load Response Characteristics

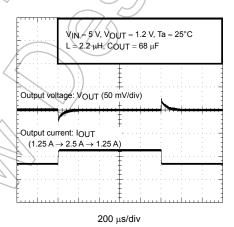

## Load Response Characteristics

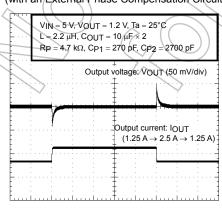

Load Response Characteristics

Load Response Characteristics (with an External Phase Compensation Circuit)

$200~\mu\text{s/div}$

15 2010-02-24

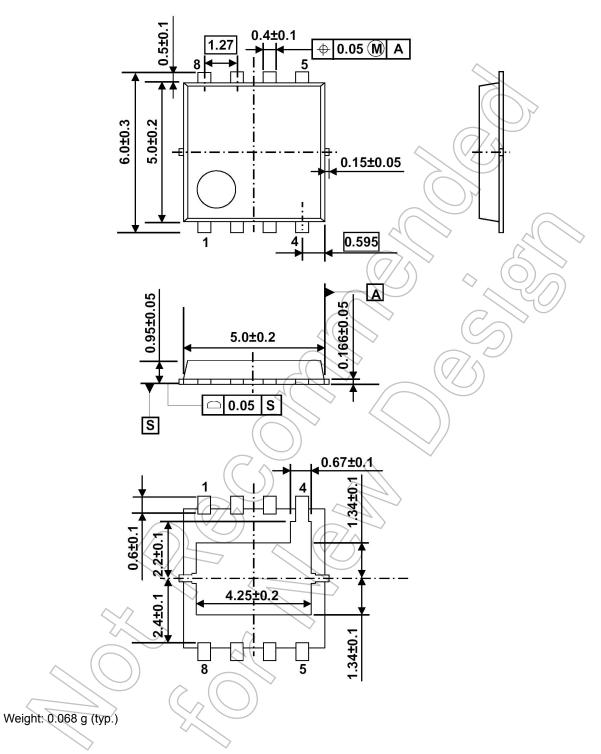

# **Package Dimensions**

HSON8-P-0505-1.27 Unit: mm

16 2010-02-24

#### RESTRICTIONS ON PRODUCT USE

- Toshiba Corporation, and its subsidiaries and affiliates (collectively "TOSHIBA"), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively "Product") without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- Product is intended for use in general electronics applications (e.g., computers, personal equipment, office equipment, measuring equipment, industrial robots and home electronics appliances) or for specific applications as expressly stated in this document. Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact ("Unintended Use"). Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for Unintended Use unless specifically permitted in this document.

- . Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE

FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY

WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR

LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND

LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO

SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product.

Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.