# Memory Products Data Book

# Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **Table of Contents**

|           | <u>PAGE</u>                                                                        |

|-----------|------------------------------------------------------------------------------------|

| SECTION 1 | MICROCHIP TECHNOLOGY INC. INTRODUCTION                                             |

|           | Introduction1-1                                                                    |

| SECTION 2 | SERIAL EEPROM SELECTION GUIDE AND CROSS REFERENCE                                  |

|           | Serial EEPROM Selection Guide2-1                                                   |

|           | Competitor Part Numbering Guide                                                    |

| SECTION 3 | FAMILY DATA SHEETS                                                                 |

|           | I <sup>2</sup> C™ Family Data Sheet3-1                                             |

|           | Microwire Family Data Sheet3-31                                                    |

|           | SPI Family Data Sheet                                                              |

|           | Specialty Product References                                                       |

| SECTION 4 | APPLICATION NOTES                                                                  |

|           | AN1028 – Recommended Usage of Microchip I <sup>2</sup> C™ Serial EEPROM Devices4-1 |

|           | AN1029 – Recommended Usage of Microchip Microwire Serial EEPROM Devices4-9         |

|           | AN1040 – Recommended Usage of Microchip SPI Serial EEPROM Devices4-13              |

| SECTION 5 | PACKAGING                                                                          |

|           | Package Outline Drawings5-1                                                        |

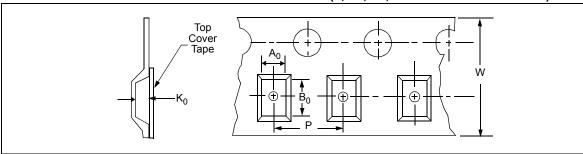

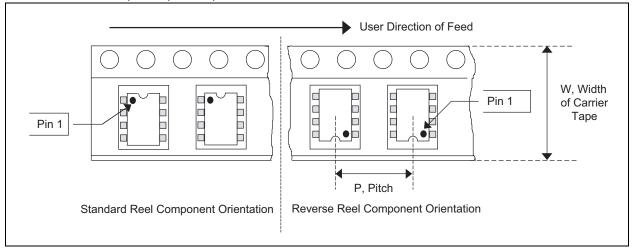

|           | Product Tape and Reel Specifications5-11                                           |

|           | Solder Reflow Recommendation5-19                                                   |

|           | Overview of Microchip Die/Wafer Support5-23                                        |

| SECTION 6 | DEVELOPMENT TOOLS                                                                  |

|           | Total Endurance™ Software Model6-1                                                 |

|           | SEEVAL® 32 Serial EEPROM Designer's Kit                                            |

# SECTION 1 MICROCHIP TECHNOLOGY INC. INTRODUCTION

| Introduction |       |

|--------------|-------|

| INTRODUCTION | i - 1 |

| HILLOUGUUH   | 4 1   |

# MICROCHIP TECHNOLOGY INC.

# **Section 1 - Introduction**

# 1.0 INTRODUCTION

Microchip Technology Inc. is a leading provider of microcontrollers, analog and interface semiconductors, and serial nonvolatile memory. Based in Chandler, Arizona USA, Microchip owns its wafer fabrication facilities in Tempe, Arizona and Gresham, Oregon, as well as its own assembly and test facility in Thailand. One of the most solid and stable performers in the semiconductor world, Microchip provides a broad product portfolio meeting the needs of the embedded control market, including:

- 8-bit PIC® microcontrollers

- 16-bit PIC<sup>®</sup> microcontroller and dsPIC<sup>®</sup> digital signal controllers

- Complete line of Analog products including LDOs, PORs, Voltage refs, ADCs, DACs, op amps, comparators, PGAs, thermal management and power management solutions

- Interface products supporting CAN, IRDA<sup>®</sup> standard, LIN and serial

- High-performance specialty and standard serial EEPROM devices compatible with all three popular buses: I<sup>2</sup>C™, Microwire and SPI

- Security devices (KEELOQ<sup>®</sup> products)

Please request a Microchip Product Line Card for a listing of the entire Microchip product offering. This literature can be obtained from your local sales office or downloaded from Microchip's informative web site at www.microchip.com.

# 1.1 Manual Overview

Serial EEPROM product requirements are provided in three Family Data Sheets which have been grouped into the specific  $I^2C^{TM}$ , Microwire, and SPI bus types. As of the date of printing, all data sheets are current and represent products that are in full production. Since this information is subject to change without notice, it is recommended that the latest version of the data sheet should be downloaded before finalizing any designs. Please check for the most recent revisions or product availability by contacting your local Microchip sales office, Representative, Distributor or by visiting us online at www.microchip.com/Memory.

All buses are compatible with de facto industry standards, including I<sup>2</sup>C, Microwire and SPI. In most cases the Microchip device can be used as a drop-in replacement for competitor devices. And for new designs, Microchip's value-added features can provide smaller footprint, lower power consumption, and faster bus rates than many commodity devices.

Two useful sections are provided at the front of the manual:

- Serial EEPROM Selection Guide every serial EEPROM in the Microchip offering is listed here, along with the most important AC/DC parameters and package options for quick comparison and selection. Full data sheets are provided in this manual for each device listed in the Selection Guide. For the most up-to-date information, be sure to check Microchip's web site at www.microchip.com.

- Competitive Part Numbering Guide this guide provides the basic part numbering schemes from several serial EEPROM manufacturers without having to search through endless versions of old data sheets for a part description. Since part numbers from each manufacturer contains unique codes for temperature, packaging and voltage, as well as other parameters, a single location with this information should be very useful when determining a Microchip replacement. Once the parameters from a competitive device are known, Microchip's MAPS (Microchip Advanced Parts Selector) tool can be used to determine the correct Microchip device to use. You can download MAPS at www.microchip.com/MAPS.

# 1.2 Key EEPROM Parameters

I<sup>2</sup>C EEPROMS from the 24AAXX family of devices now have a wider operating voltage from 1.7V to 5.5V over the entire density range from 128 bits to 1 Mbit. This meets the need for lower operating voltages to support the ever increasing number of battery operated systems. In addition, the higher speed 24FCXX family of devices can also meet the requirements for 400 kHz operation over the voltage range from 1.8V to 2.5V and 1 MHz at voltages of 2.5V and above.

# MICROCHIP TECHNOLOGY INC.

SPI EEPROMs from the 25LCXX family of devices now have higher operating speeds for all densities ranging from 1 Kbit up to 1 Mbit. This includes speeds up to 10 MHz for densities up to 256 Kbits and 20 MHz for the 512 Kbit and 1 Mbit devices. As an added bonus, the 512K and 1 Mbit devices have been released as EEPROM/Flash devices. Designed as a robust EEPROM for high endurance, wide voltage range and byte/page operations, they also respond to standard Flash commands and sector operations.

# 1.3 Packaging: RoHS Compliant

Microchip serial EEPROMs are packaged at Microchip's own facilities and by authorized subcontractors. After packaging, whether in-house or outside at a subcontractor, every device is 100% tested again in a Microchip facility prior to shipment.

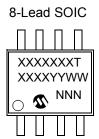

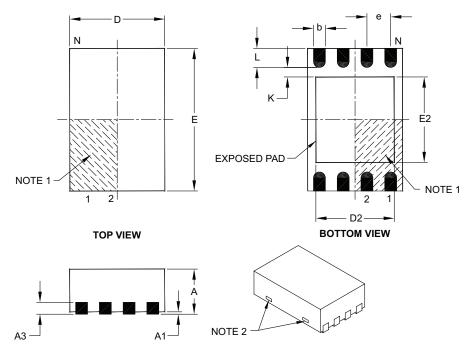

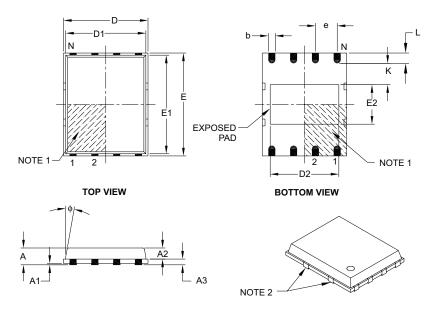

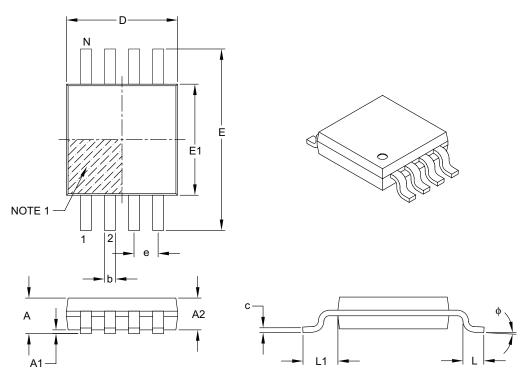

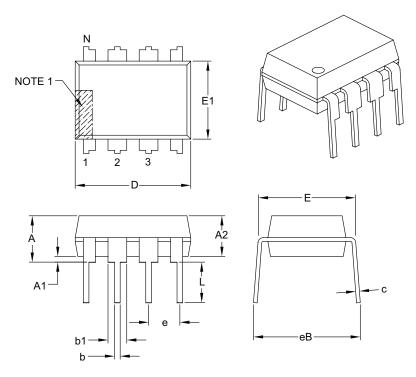

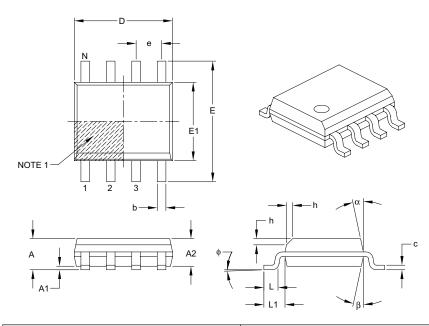

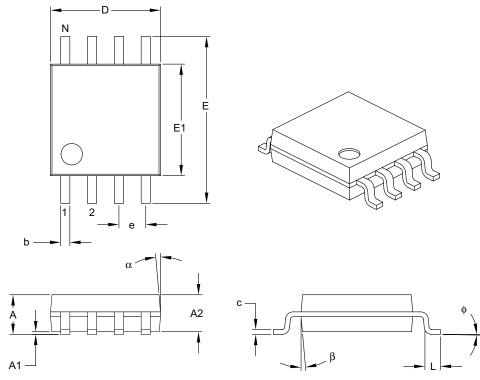

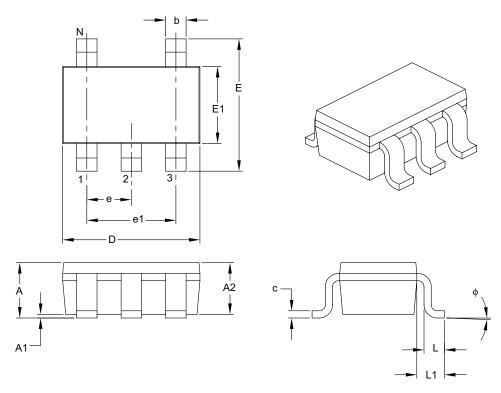

Microchip excels at micro-miniature packaging for serial EEPROMs, including the following:

- 8-lead SOIC up to 1 Mbit

- 8-lead MSOP up to 256 Kbits

- · 8-lead TSSOP up to 256 Kbits

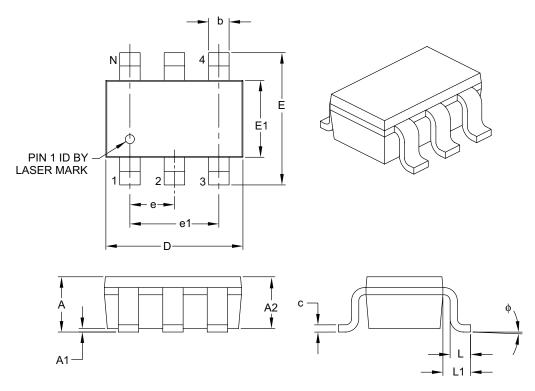

- 5-lead SOT23 up to 16 Kbits

- 6-lead SOT23 up to 16 Kbits

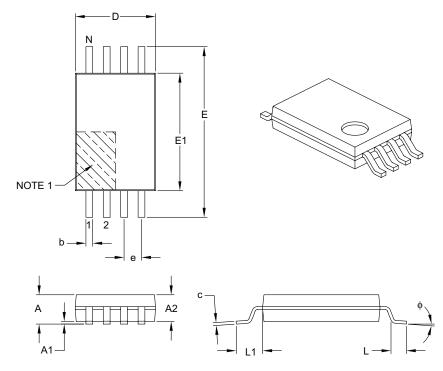

- 8-lead 5x6 DFN up to 1 Mbit

- 8-lead 2x3 DFN up to 64 Kbits

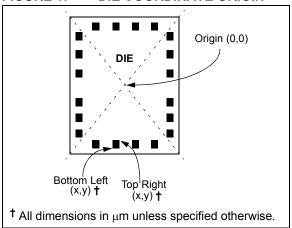

- · Die and wafer packaging all densities

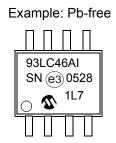

All products use Pb-free plating, and all are RoHS compliant. A rigorous qualification and production environment ensures high-temperature solderability, moisture sensitivity level, absence of whisker growth, and reliability of the new Pb-Free package family.

# 1.4 Quality

Microchip delivers the highest-quality serial EEPROM products in the world, with world-class line yields, well-designed processes, and rigorous Statistical Process Control (SPC) in each of its continuous-improvement facilities. Outgoing quality level is close to 0 ppm across nearly a billion serial EEPROMs shipped each year.

Each serial EEPROM is tested three times: first at wafer-level, where each individual die on the wafer receives 100% AC/DC testing of all data sheet parameters. At the end of that test, each die is programmed with data in each memory cell and then baked for five hours at 250°C to ensure data retention specs. Following the bake, every die on every wafer is tested again, including AC/DC data sheet parameters and special tests of the data array to verify oxide quality and to limit infant mortality. Finally, after packaging, every device receives a final functional test to screen out any potential assembly-related issues.

After final test, quality samples are taken continuously to monitor reliability. The resulting data is available annually in a formal report available at www.microchip.com.

For Microchip, quality is not a side issue - it is integral to our culture, our systems and our products. It is, in fact, our business model.

# 1.5 Development Tools

Microchip provides some of the best serial EEPROM tools in the industry, including:

- SEEVAL<sup>®</sup> 32 Designer's Kit a feature-rich and easy-to-use programmer/data viewer supporting all Microchip Serial EEPROM products. This inexpensive tool can shorten time-to-market by weeks. Easy to set-up and use right out of the box, it can help solve a week's worth of headaches in an afternoon. See the Development Tools section of this manual for more information.

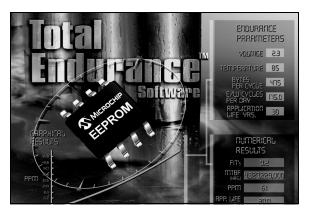

- Total Endurance™ software a powerful mathematical model for predicting Erase/Write endurance of your specific serial EEPROM in your specific application. All serial EEPROMs, from all manufacturers, eventually experience bit-failures after some number of erase/write cycles. Microchip's serial EEPROM endurance is among the best in the world, and Total Endurance software is the only tool of its kind for modeling and predicting device lifetime. This can help designers to produce a robust design since trade-off analysis is so fast with this easy-to-use software modeling tool.

Any discussion of endurance must include the parameters of voltage, temperature, semiconductor process, cell design, array size, bytes per cycle, and cycles per day in order to understand what the endurance number means - and to predict how a given device will perform in a particular application. Total Endurance software accepts your input of each of these parameters and outputs FIT rate or MTBF vs. time or vs. number of cycles. Download it for FREE at www.microchip.com.

# 1.6 e-Commerce

Microchip serial EEPROMs are available from any Microchip distributor, sales representative or sales office and even from Microchip's own e-commerce site, www.microchipDirect.com. They can also be sampled for free from Microchip's main web site www.microchip.com - and delivered fast. Just click the "Sample" button to order free samples or the "Buy Online" button to purchase serial EEPROMs using a credit card.

# SECTION 2 SERIAL EEPROM SELECTION GUIDE AND CROSS REFERENCE

| Serial EEPROM Selection Guide   | 2-1 |

|---------------------------------|-----|

| Competitor Part Numbering Guide | 2-9 |

I<sup>2</sup>C<sup>™</sup> Compatible

| Device                    | Vcc<br>Range | Write<br>Protect | Page<br>Size | Max<br>Clock | Write<br>Cycle | Cascade | Endurance | Temp<br>Grade | Packages              | Data<br>Sheet |

|---------------------------|--------------|------------------|--------------|--------------|----------------|---------|-----------|---------------|-----------------------|---------------|

| 128-bit I <sup>2</sup> C  | compatib     | le               |              |              |                |         |           |               |                       |               |

| 24AA00                    | 1.8-5.5      | No               | N/A          | 400 kHz      | 4 ms           | No      | 1,000,000 | I             | P, SN, ST, OT, MC     | DS21178       |

| 24LC00                    | 2.5-5.5      | No               | N/A          | 400 kHz      | 4 ms           | No      | 1,000,000 | 1             | P, SN, ST, OT, MC     | DS21178       |

| 24C00                     | 4.5-5.5      | No               | N/A          | 400 kHz      | 4 ms           | No      | 1,000,000 | I, E          | P, SN, ST, OT, MC     | DS21178       |

| 1Kbit I <sup>2</sup> C co | ompatible    | <b>;</b>         |              |              |                |         |           |               |                       |               |

| 24AA01                    | 1.8-5.5      | Yes              | 8 bytes      | 400 kHz      | 5 ms           | No      | 1,000,000 | I             | P, SN, ST, MS, OT, MC | DS21711       |

| 24LC01B                   | 2.5-5.5      | Yes              | 8 bytes      | 400 kHz      | 5 ms           | No      | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21711       |

| 24C01C                    | 4.5-5.5      | Yes              | 16 bytes     | 400 kHz      | 1 ms           | 8       | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21201       |

| 24AA014                   | 1.8-5.5      | Yes              | 16 bytes     | 400 kHz      | 10 ms          | 8       | 1,000,000 | I             | P, SN, ST, MS, MC     | DS21809       |

| 24LC014                   | 2.5-5.5      | Yes              | 16 bytes     | 400 kHz      | 10 ms          | 8       | 1,000,000 | 1             | P, SN, ST, MS, MC     | DS21809       |

| 24LC21A                   | 2.5-5.5      | No               | 8 bytes      | 400 kHz      | 10 ms          | No      | 1,000,000 | I             | P, SN                 | DS21160       |

| 24LCS21A                  | 2.5-5.5      | Yes              | 8 bytes      | 400 kHz      | 10 ms          | No      | 1,000,000 | 1             | P, SN                 | DS21161       |

| 2Kbit I <sup>2</sup> C co | ompatible    | )                |              |              |                |         |           |               |                       |               |

| 24AA02                    | 1.8-5.5      | Yes              | 8 bytes      | 400 kHz      | 5 ms           | No      | 1,000,000 | I             | P, SN, ST, MS, OT, MC | DS21709       |

| 24LC02B                   | 2.5-5.5      | Yes              | 8 bytes      | 400 kHz      | 5 ms           | No      | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21709       |

| 24LCS22A                  | 2.5-5.5      | Yes              | 8 bytes      | 400 kHz      | 10 ms          | No      | 1,000,000 | I             | P, SN                 | DS21682       |

| 24C02C                    | 4.5-5.5      | Yes              | 16 bytes     | 400 kHz      | 1 ms           | 8       | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21202       |

| 24LCS52                   | 2.5-5.5      | Yes              | 16 bytes     | 400 kHz      | 5 ms           | 8       | 1,000,000 | I             | P, SN, ST, MS, MC     | DS21166       |

| 24AA52                    | 1.8-5.5      | Yes              | 16 bytes     | 400 kHz      | 5 ms           | 8       | 1,000,000 | I             | P, SN, ST, MS, MC     | DS21166       |

| 24AA024                   | 1.8-5.5      | Yes              | 16 bytes     | 400 kHz      | 10 ms          | 8       | 1,000,000 | I             | P, SN, ST, MS, MC     | DS21210       |

| 24LC024                   | 2.5-5.5      | Yes              | 16 bytes     | 400 kHz      | 10 ms          | 8       | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21210       |

| 24AA025                   | 1.8-5.5      | No               | 16 bytes     | 400 kHz      | 10 ms          | 8       | 1,000,000 | I             | P, SN, ST, MS, MC     | DS21210       |

| 24LC025                   | 2.5-5.5      | No               | 16 bytes     | 400 kHz      | 10 ms          | 8       | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21210       |

P = 8 PDIP, SN = 150 Mil SOIC, SM = 207 Mil SOIC, ST = 8 TSSOP, MS = 8 MSOP, OT = SOT-23, MF = 6x5 mm DFN, ST14 = 14 TSSOP, MC = 2x3 mm DFN Most devices also available in die and wafer form. Please contact Microchip sales office.

I<sup>2</sup>C is a trademark of Philips Corporation.

# Serial EEPROM Selection Guide

# I<sup>2</sup>C Compatible

| Device                      | Vcc<br>Range | Write<br>Protect | Page<br>Size | Max<br>Clock | Write<br>Cycle | Cascade | Endurance | Temp<br>Grade | Packages              | Data<br>Sheet |

|-----------------------------|--------------|------------------|--------------|--------------|----------------|---------|-----------|---------------|-----------------------|---------------|

| 4Kbit I <sup>2</sup> C com  | patible      |                  |              |              |                |         |           |               |                       |               |

| 24AA04                      | 1.8-5.5      | Yes              | 16 bytes     | 400 kHz      | 5 ms           | No      | 1,000,000 | I             | P, SN, ST, MS, OT, MC | DS21708       |

| 24LC04B                     | 2.5-5.5      | Yes              | 16 bytes     | 400 kHz      | 5 ms           | No      | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21708       |

| 8Kbit I <sup>2</sup> C com  | patible      |                  |              |              |                |         |           |               |                       |               |

| 24AA08                      | 1.8-5.5      | Yes              | 16 bytes     | 400 kHz      | 5 ms           | No      | 1,000,000 | I             | P, SN, ST, MS, OT, MC | DS21710       |

| 24LC08B                     | 2.5-5.5      | Yes              | 16 bytes     | 400 kHz      | 5 ms           | No      | 1,000,000 | I, E          | P, SN, ST, SM, OT, MC | DS21710       |

| 16Kbit I <sup>2</sup> C cor | mpatible     |                  |              |              |                |         |           |               |                       |               |

| 24AA16                      | 1.8-5.5      | Yes              | 16 bytes     | 400 kHz      | 5 ms           | No      | 1,000,000 | I             | P, SN, ST, MS, OT, MC | DS21703       |

| 24LC16B                     | 2.5-5.5      | Yes              | 16 bytes     | 400 kHz      | 5 ms           | No      | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21703       |

| 32Kbit I <sup>2</sup> C cor | mpatible     |                  |              |              |                |         |           |               |                       |               |

| 24AA32A                     | 1.8-5.5      | Yes              | 32 bytes     | 400 kHz      | 5 ms           | 8       | 1,000,000 | I             | P, SN, ST, MS, MC     | DS21713       |

| 24LC32A                     | 2.5-5.5      | Yes              | 32 bytes     | 400 kHz      | 5 ms           | 8       | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21713       |

| 64Kbit I <sup>2</sup> C cor | mpatible     |                  |              |              |                |         |           |               |                       |               |

| 24AA64                      | 1.8-5.5      | Yes              | 32 bytes     | 400 kHz      | 5 ms           | 8       | 1,000,000 | I             | P, SN, ST, MS, MC     | DS21189       |

| 24LC64                      | 2.5-5.5      | Yes              | 32 bytes     | 400 kHz      | 5 ms           | 8       | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21189       |

| 24AA65                      | 1.8-5.5      | Yes              | 64 bytes     | 400 kHz      | 2 ms           | 8       | 1M/10M    | Ο             | P, SM                 | DS21073       |

| 24LC65                      | 2.5-5.5      | Yes              | 64 bytes     | 400 kHz      | 2 ms           | 8       | 1M/10M    | I             | P, SM                 | DS21073       |

| 24C65                       | 4.5-5.5      | Yes              | 64 bytes     | 400 kHz      | 2 ms           | 8       | 1M/10M    | 1             | P, SM                 | DS21073       |

| 128Kbit I <sup>2</sup> C co | ompatible    |                  |              |              |                |         |           |               |                       |               |

| 24AA128                     | 1.8-5.5      | Yes              | 64 bytes     | 400 kHz      | 5 ms           | 8       | 1,000,000 | ı             | P, SN, ST, MS, MF     | DS21191       |

| 24LC128                     | 2.5-5.5      | Yes              | 64 bytes     | 400 kHz      | 5 ms           | 8       | 1,000,000 | I, E          | P, SN, ST, MS, MF     | DS21191       |

| 24FC128                     | 1.8-5.5      | Yes              | 64 bytes     | 1 MHz        | 5 ms           | 8       | 1,000,000 | 1             | P, SN, ST, MS, MF     | DS21191       |

| 256Kbit I <sup>2</sup> C co | ompatible    |                  |              |              |                |         |           |               |                       |               |

| 24AA256                     | 1.8-5.5      | Yes              | 64 bytes     | 400 kHz      | 5 ms           | 8       | 1,000,000 | I             | P, SN, ST, MS, MF     | DS21203       |

| 24LC256                     | 2.5-5.5      | Yes              | 64 bytes     | 400 kHz      | 5 ms           | 8       | 1,000,000 | I, E          | P, SN, ST, MS, MF     | DS21203       |

| 24FC256                     | 1.8-5.5      | Yes              | 64 bytes     | 1 MHz        | 5 ms           | 8       | 1,000,000 | 1             | P, SN, ST, MS, MF     | DS21203       |

SERIAL EEPROMS

# I<sup>2</sup>C Compatible

| Device                     | Vcc<br>Range | Write<br>Protect | Page<br>Size | Max<br>Clock | Write<br>Cycle | Cascade | Endurance | Temp<br>Grade | Packages        | Data<br>Sheet |

|----------------------------|--------------|------------------|--------------|--------------|----------------|---------|-----------|---------------|-----------------|---------------|

| 512Kbit I <sup>2</sup> C c | ompatible    |                  |              |              |                |         |           |               |                 |               |

| 24AA512                    | 1.8-5.5      | Yes              | 128 bytes    | 400 kHz      | 5 ms           | 8       | 1,000,000 | I             | P, SM, ST14, MF | DS21754       |

| 24LC512                    | 2.5-5.5      | Yes              | 128 bytes    | 400 kHz      | 5 ms           | 8       | 1,000,000 | I, E          | P, SM, ST14, MF | DS21754       |

| 24FC512                    | 2.5-5.5      | Yes              | 128 bytes    | 1 MHz        | 5 ms           | 8       | 1,000,000 | I             | P, SM, ST14, MF | DS21754       |

| 24AA515                    | 1.8-5.5      | Yes              | 64 bytes     | 400 kHz      | 5 ms           | 4       | 1,000,000 | 1             | P, SM           | DS21673       |

| 24LC515                    | 2.5-5.5      | Yes              | 64 bytes     | 400 kHz      | 5 ms           | 4       | 1,000,000 | I             | P, SM           | DS21673       |

| 24FC515                    | 2.5-5.5      | Yes              | 64 bytes     | 1 MHz        | 5 ms           | 4       | 1,000,000 | 1             | P, SM           | DS21673       |

# **Microwire Compatible**

| Device          | Vcc<br>Range | ORG<br>Pin | Word<br>Size | Max<br>Clock | Write<br>Cycle | Endurance | Temp<br>Grade | Packages              | Data<br>Sheet |

|-----------------|--------------|------------|--------------|--------------|----------------|-----------|---------------|-----------------------|---------------|

| 1Kbit Microwire | compatible   |            |              |              |                |           |               |                       |               |

| 93AA46A         | 1.8-5.5      | No         | 8-bit        | 2 MHz        | 6 ms           | 1,000,000 | I             | P, SN, ST, MS, OT, MC | DS21749       |

| 93AA46B         | 1.8-5.5      | No         | 16-bit       | 2 MHz        | 6 ms           | 1,000,000 | 1             | P, SN, ST, MS, OT, MC | DS21749       |

| 93LC46A         | 2.5-5.5      | No         | 8-bit        | 2 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21749       |

| 93LC46B         | 2.5-5.5      | No         | 16-bit       | 2 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21749       |

| 93C46A          | 4.5-5.5      | No         | 8-bit        | 2 MHz        | 2 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21749       |

| 93C46B          | 4.5-5.5      | No         | 16-bit       | 2 MHz        | 2 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21749       |

| 93AA46C         | 1.8-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 6 ms           | 1,000,000 | I             | P, SN, ST, MS, MC     | DS21749       |

| 93LC46C         | 2.5-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21749       |

| 93C46C          | 4.5-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 2 ms           | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21749       |

| 2Kbit Microwire | compatible   |            |              |              |                |           |               |                       |               |

| 93AA56A         | 1.8-5.5      | No         | 8-bit        | 2 MHz        | 6 ms           | 1,000,000 | I             | P, SN, ST, MS, OT, MC | DS21794       |

| 93AA56B         | 1.8-5.5      | No         | 16-bit       | 2 MHz        | 6 ms           | 1,000,000 | I             | P, SN, ST, MS, OT, MC | DS21794       |

P = 8 PDIP, SN = 150 Mil SOIC, SM = 207 Mil SOIC, ST = 8 TSSOP, MS = 8 MSOP, OT = SOT-23, MF = 6x5 mm DFN, ST14 = 14 TSSOP, MC = 2x3 mm DFN Most devices also available in die and wafer form. Please contact Microchip sales office.

# **Microwire Compatible**

| Device          | Vcc<br>Range | ORG<br>Pin | Word<br>Size | Max<br>Clock | Write<br>Cycle | Endurance | Temp<br>Grade | Packages              | Data<br>Sheet |

|-----------------|--------------|------------|--------------|--------------|----------------|-----------|---------------|-----------------------|---------------|

| 2Kbit Microwire | compatible   | (continue  | ed)          |              |                |           |               |                       |               |

| 93LC56A         | 2.5-5.5      | No         | 8-bit        | 2 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21794       |

| 93LC56B         | 2.5-5.5      | No         | 16-bit       | 2 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21794       |

| 93C56A          | 4.5-5.5      | No         | 8-bit        | 2 MHz        | 2 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21794       |

| 93C56B          | 4.5-5.5      | No         | 16-bit       | 2 MHz        | 2 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21794       |

| 93AA56C         | 1.8-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 6 ms           | 1,000,000 | 1             | P, SN, ST, MS, MC     | DS21794       |

| 93LC56C         | 2.5-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21794       |

| 93C56C          | 4.5-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 2 ms           | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21794       |

| 4Kbit Microwire | compatible   |            |              |              |                |           |               |                       |               |

| 93AA66A         | 1.8-5.5      | No         | 8-bit        | 2 MHz        | 6 ms           | 1,000,000 | I             | P, SN, ST, MS, OT, MC | DS21795       |

| 93AA66B         | 1.8-5.5      | No         | 16-bit       | 2 MHz        | 6 ms           | 1,000,000 | 1             | P, SN, ST, MS, OT, MC | DS21795       |

| 93LC66A         | 2.5-5.5      | No         | 8-bit        | 2 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21795       |

| 93LC66B         | 2.5-5.5      | No         | 16-bit       | 2 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21795       |

| 93C66A          | 4.5-5.5      | No         | 8-bit        | 2 MHz        | 2 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21795       |

| 93C66B          | 4.5-5.5      | No         | 16-bit       | 2 MHz        | 2 ms           | 1,000,000 | I, E          | P, SN, ST, MS, OT, MC | DS21795       |

| 93AA66C         | 1.8-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 6 ms           | 1,000,000 | 1             | P, SN, ST, MS, MC     | DS21795       |

| 93LC66C         | 2.5-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21795       |

| 93C66C          | 4.5-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 2 ms           | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21795       |

| 8Kbit Microwire | compatible   |            |              |              |                |           |               |                       |               |

| 93AA76A         | 1.8-5.5      | No         | 8-bit        | 3 MHz        | 6 ms           | 1,000,000 | I             | OT                    | DS21796       |

| 93AA76B         | 1.8-5.5      | No         | 16-bit       | 3 MHz        | 6 ms           | 1,000,000 | 1             | OT                    | DS21796       |

| 93LC76A         | 2.5-5.5      | No         | 8-bit        | 3 MHz        | 6 ms           | 1,000,000 | I, E          | OT                    | DS21796       |

| 93LC76B         | 2.5-5.5      | No         | 16-bit       | 3 MHz        | 6 ms           | 1,000,000 | I, E          | OT                    | DS21796       |

| 93C76A          | 4.5-5.5      | No         | 8-bit        | 3 MHz        | 2 ms           | 1,000,000 | I, E          | ОТ                    | DS21796       |

| 93C76B          | 4.5-5.5      | No         | 16-bit       | 3 MHz        | 2 ms           | 1,000,000 | I, E          | OT                    | DS21796       |

| 93AA76C         | 1.8-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 6 ms           | 1,000,000 | I             | P, SN, ST, MS, MC     | DS21796       |

| 93LC76C         | 2.5-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21796       |

| 93C76C          | 4.5-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 2 ms           | 1,000,000 | I, E          | P, SN, ST, MS, MC     | DS21796       |

# **Microwire Compatible**

| Device          | Vcc<br>Range | ORG<br>Pin | Word<br>Size | Max<br>Clock | Write<br>Cycle | Endurance | Temp<br>Grade | Packages          | Data<br>Sheet |

|-----------------|--------------|------------|--------------|--------------|----------------|-----------|---------------|-------------------|---------------|

| 16Kbit Microwir | e compatible | )          |              |              |                |           |               |                   |               |

| 93AA86A         | 1.8-5.5      | No         | 8-bit        | 3 MHz        | 6 ms           | 1,000,000 | I             | ОТ                | DS21797       |

| 93AA86B         | 1.8-5.5      | No         | 16-bit       | 3 MHz        | 6 ms           | 1,000,000 | 1             | OT                | DS21797       |

| 93LC86A         | 2.5-5.5      | No         | 8-bit        | 3 MHz        | 6 ms           | 1,000,000 | I, E          | OT                | DS21797       |

| 93LC86B         | 2.5-5.5      | No         | 16-bit       | 3 MHz        | 6 ms           | 1,000,000 | I, E          | OT                | DS21797       |

| 93C86A          | 4.5-5.5      | No         | 8-bit        | 3 MHz        | 2 ms           | 1,000,000 | I, E          | ОТ                | DS21797       |

| 93C86B          | 4.5-5.5      | No         | 16-bit       | 3 MHz        | 2 ms           | 1,000,000 | I, E          | ОТ                | DS21797       |

| 93AA86C         | 1.8-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 6 ms           | 1,000,000 | 1             | P, SN, ST, MS, MC | DS21797       |

| 93LC86C         | 2.5-5.5      | Yes        | 8- or 16-bit | 3 MHz        | 6 ms           | 1,000,000 | I, E          | P, SN, ST, MS, MC | DS21797       |

# **SPI Compatible Products**

| •                |              |                  |              |              |                |           |               |                   |               |

|------------------|--------------|------------------|--------------|--------------|----------------|-----------|---------------|-------------------|---------------|

| Device           | Vcc<br>Range | Write<br>Protect | Page<br>Size | Max<br>Clock | Write<br>Cycle | Endurance | Temp<br>Grade | Packages          | Data<br>Sheet |

| 1Kbit SPI compat | tible        |                  |              |              |                |           |               |                   |               |

| 25AA010A         | 1.8-5.5      | Yes              | 16 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, MS, SN, ST, MC | DS21832       |

| 25LC010A         | 2.5-5.5      | Yes              | 16 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, MS, SN, ST, MC | DS21832       |

| 2Kbit SPI compat | tible        |                  |              |              |                |           |               |                   |               |

| 25AA020A         | 1.8-5.5      | Yes              | 16 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, MS, SN, ST, MC | DS21833       |

| 25LC020A         | 2.5-5.5      | Yes              | 16 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, MS, SN, ST, MC | DS21833       |

| 4Kbit SPI compat | tible        |                  |              |              |                |           |               |                   |               |

| 25AA040A         | 1.8-5.5      | Yes              | 16 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, MS, SN, ST, MC | DS21827       |

| 25LC040A         | 2.5-5.5      | Yes              | 16 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, MS, SN, ST, MC | DS21827       |

# **SPI Compatible Products**

| Device           | Vcc<br>Range | Write<br>Protect | Page<br>Size | Max<br>Clock | Write<br>Cycle | Endurance | Temp<br>Grade | Packages      | Data<br>Sheet |

|------------------|--------------|------------------|--------------|--------------|----------------|-----------|---------------|---------------|---------------|

| 8Kbit SPI compat | ible         |                  |              |              |                |           |               |               |               |

| 25AA080A         | 1.8-5.5      | Yes              | 16 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, SN, ST, MS | DS21808       |

| 25AA080B         | 1.8-5.5      | Yes              | 32 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, SN, ST, MS | DS21808       |

| 25LC080A         | 2.5-5.5      | Yes              | 16 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, SN, ST, MS | DS21808       |

| 25LC080B         | 2.5-5.5      | Yes              | 32 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, SN, ST, MS | DS21808       |

| 16Kbit SPI compa | tible        |                  |              |              |                |           |               |               |               |

| 25AA160A         | 1.8-5.5      | Yes              | 16 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, SN, ST, MS | DS21807       |

| 25AA160B         | 1.8-5.5      | Yes              | 32 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, SN, ST, MS | DS21807       |

| 25LC160A         | 2.5-5.5      | Yes              | 16 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, SN, ST, MS | DS21807       |

| 25LC160B         | 2.5-5.5      | Yes              | 32 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, SN, ST, MS | DS21807       |

| 32Kbit SPI compa | tible        |                  |              |              |                |           |               |               |               |

| 25AA320A         | 1.8-5.5      | Yes              | 32 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, MS, SN, ST | DS21828       |

| 25LC320A         | 2.5-5.5      | Yes              | 32 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, MS, SN, ST | DS21828       |

| 64Kbit SPI compa | tible        |                  |              |              |                |           |               |               |               |

| 25AA640A         | 1.8-5.5      | Yes              | 32 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, MS, SN, ST | DS21830       |

| 25LC640A         | 2.5-5.5      | Yes              | 32 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, MS, SN, ST | DS21830       |

| 128Kbit SPI comp | atible       |                  |              |              |                |           |               |               |               |

| 25AA128          | 1.8-5.5      | Yes              | 64 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, SN, ST, MF | DS21831       |

| 25LC128          | 2.5-5.5      | Yes              | 64 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, SN, ST, MF | DS21831       |

| 256Kbit SPI comp | atible       |                  |              |              |                |           |               |               |               |

| 25AA256          | 1.8-5.5      | Yes              | 64 byte      | 10 MHz       | 5 ms           | 1,000,000 | I             | P, SN, ST, MF | DS21822       |

| 25LC256          | 2.5-5.5      | Yes              | 64 byte      | 10 MHz       | 5 ms           | 1,000,000 | I, E          | P, SN, ST, MF | DS21822       |

| 512Kbit SPI comp | atible       |                  |              |              |                |           |               |               |               |

| 25AA512          | 1.8-5.5      | Yes              | 128 byte     | 20 MHz       | 5 ms           | 1,000,000 | I             | P, SN, MF     | DS22021       |

| 25LC512          | 2.5-5.5      | Yes              | 128 byte     | 20 MHz       | 5 ms           | 1,000,000 | I, E          | P, SN, MF     | DS22021       |

# **SPI Compatible Products**

| Device           | Vcc<br>Range | Write<br>Protect | Page<br>Size | Max<br>Clock | Write<br>Cycle | Endurance  | Temp<br>Grade | Packages  | Data<br>Sheet |

|------------------|--------------|------------------|--------------|--------------|----------------|------------|---------------|-----------|---------------|

| 1 Mbit SPI compa | tible        |                  |              |              |                |            |               |           |               |

| 25AA1024         | 1.8-5.5      | Yes              | 256 byte     | 20 MHz       | 5 ms           | 1,000,000  | I             | P, SM, MF | DS21836       |

| 25LC1024         | 2.5-5.5      | Yes              | 256 byte     | 20 MHz       | 5 ms           | 1,000, 000 | I, E          | P, SM, MF | DS21836       |

# Plug-and-Play $^{\scriptsize{(\!\! R)}}$ and ID Products

| Device       | Density                              | Vcc<br>Range           | Write<br>Protect | Page<br>Size  | Max<br>Clock | Write<br>Cycle | Туре   | Endurance | Temp<br>Grade | Packages          | Data<br>Sheet |  |

|--------------|--------------------------------------|------------------------|------------------|---------------|--------------|----------------|--------|-----------|---------------|-------------------|---------------|--|

| Serial EEPRO | Serial EEPROMs for DRAM DIMM modules |                        |                  |               |              |                |        |           |               |                   |               |  |

| 24LCS52      | 2Kbit                                | 2.5-5.5                | Yes              | 16 bytes      | 400 kHz      | 5 ms           | DDR    | 1,000,000 | I             | P, SN, ST, MS, MC | DS21166       |  |

| 24AA52       | 2Kbit                                | 1.8-5.5                | Yes              | 16 bytes      | 400 kHz      | 5 ms           | DDR    | 1,000,000 | I             | P, SN, ST, MS, MC | DS21166       |  |

| 24LC024      | 2Kbit                                | 2.5-5.5                | Yes              | 16 bytes      | 400 kHz      | 5 ms           | DDR    | 1,000,000 | I, E          | P, SN, ST, MS, MC | DS21210       |  |

| 24LC025      | 2Kbit                                | 2.5-5.5                | No               | 16 bytes      | 400 kHz      | 5 ms           | DDR    | 1,000,000 | I, E          | P, SN, ST, MS, MC | DS21210       |  |

| Serial EEPRO | Ms for VES                           | A <sup>®</sup> monitor | s, projector     | s and flat pa | nels         |                |        |           |               |                   |               |  |

| 24LC21A      | 1Kbit                                | 2.5-5.5                | No               | 8 bytes       | 400 kHz      | 10 ms          | _      | 1,000,000 | I             | P, SN             | DS21160       |  |

| 24LCS21A     | 1Kbit                                | 2.5-5.5                | Yes              | 8 bytes       | 400 kHz      | 10 ms          | _      | 1,000,000 | I             | P, SN             | DS21161       |  |

| 24LCS22A     | 2Kbit                                | 2.5-5.5                | Yes              | 8 bytes       | 400 kHz      | 10 ms          | _      | 1,000,000 | 1             | P, SN             | DS21682       |  |

| 34LC02       | 2Kbit                                | 2.5-5.5                | Yes              | 16 bytes      | 400 kHz      | 5 ms           | DDR2/3 | 1,000,000 | I/E           | P, SN, ST, MS, MC | DS22029       |  |

| 34AA02       | 2Kbit                                | 1.7-5.5                | Yes              | 16 bytes      | 400 kHz      | 5 ms           | DDR2/3 | 1,000,000 | 1             | P, SN, ST, MS, MC | DS22029       |  |

| 34LV02       | 2Kbit                                | 1.5-5.5                | Yes              | 16 bytes      | 400 kHz      | 5 ms           | DDR2/3 | 1,000,000 | 1             | P, SN, ST, MS, MC | DS22029       |  |

| Serial EEPRO | <b>Vis for othe</b>                  | r ID applica           | ations           |               |              |                |        |           |               |                   |               |  |

| 24AA00       | 128 bit                              | 1.8-5.5                | No               | N/A           | 400 kHz      | 4 ms           | _      | 1,000,000 | I             | P, SN, ST, OT, MC | DS21178       |  |

| 24LC00       | 128 bit                              | 2.5-5.5                | No               | N/A           | 400 kHz      | 4 ms           | _      | 1,000,000 | 1             | P, SN, ST, OT, MC | DS21178       |  |

| 24C00        | 128 bit                              | 4.5-5.5                | No               | N/A           | 400 kHz      | 4 ms           | _      | 1,000,000 | I, E          | P, SN, ST, OT, MC | DS21178       |  |

P = 8 PDIP, SN = 150 Mil SOIC, SM = 207 Mil SOIC, ST = 8 TSSOP, MS = 8 MSOP, OT = SOT-23, MF = 8 DFN, ST14 = 14 TSSOP

Most devices also available in die and wafer form. Please contact Microchip sales office.

# **Smart Card Devices**

| Device         | Vcc<br>Range                               | Write<br>Protect | Page<br>Size | Max<br>Clock | Write<br>Cycle | Endurance | Temp<br>Grade | Packages | Pb-Free<br>Available | Data Sheet |  |

|----------------|--------------------------------------------|------------------|--------------|--------------|----------------|-----------|---------------|----------|----------------------|------------|--|

| Smart-Card dev | Smart-Card devices (meet ISO 7816 bondout) |                  |              |              |                |           |               |          |                      |            |  |

| 24AA01SC       | 1.8-5.5                                    | Yes              | 8 bytes      | 400 kHz      | 5 ms           | 1,000,000 | I             | W, WF, S | N/A                  | DS21748    |  |

| 24LC01SC       | 2.5-5.5                                    | Yes              | 8 bytes      | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21748    |  |

| 24AA02SC       | 1.8-5.5                                    | Yes              | 8 bytes      | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21747    |  |

| 24LC02SC       | 2.5-5.5                                    | Yes              | 8 bytes      | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21747    |  |

| 24AA04SC       | 1.8-5.5                                    | Yes              | 16 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21745    |  |

| 24LC04SC       | 2.5-5.5                                    | Yes              | 16 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21745    |  |

| 24AA08SC       | 1.8-5.5                                    | Yes              | 16 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21746    |  |

| 24LC08SC       | 2.5-5.5                                    | Yes              | 16 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21746    |  |

| 24AA16SC       | 1.8-5.5                                    | Yes              | 16 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS20093    |  |

| 24LC16SC       | 2.5-5.5                                    | Yes              | 16 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS20093    |  |

| 24AA32ASC      | 1.8-5.5                                    | Yes              | 32 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21723    |  |

| 24LC32ASC      | 2.5-5.5                                    | Yes              | 32 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21723    |  |

| 24AA64SC       | 1.8-5.5                                    | Yes              | 32 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21716    |  |

| 24LC64SC       | 2.5-5.5                                    | Yes              | 32 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21716    |  |

| 24AA128SC      | 1.8-5.5                                    | Yes              | 64 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS20095    |  |

| 24LC128SC      | 2.5-5.5                                    | Yes              | 64 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS20095    |  |

| 24AA256SC      | 1.8-5.5                                    | Yes              | 64 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS20094    |  |

| 24LC256SC      | 2.5-5.5                                    | Yes              | 64 bytes     | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS20094    |  |

| 24AA512SC      | 1.8-5.5                                    | Yes              | 128 bytes    | 400 kHz      | 5 ms           | 1,000,000 | 1             | W, WF, S | N/A                  | DS21785    |  |

| 24LC512SC      | 2.5-5.5                                    | Yes              | 128 bytes    | 400 kHz      | 5 ms           | 1,000,000 | I             | W, WF, S | N/A                  | DS21785    |  |

SERIAL EEPROMS

W = wafer, WF = wafer on frame, S = single die in waffle pack.

Standard backgrind thickness are 11 and 15 mil and unground (29 mils).

# **SERIAL EEPROMS**

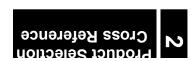

# **Competitor Part Numbering Guide**

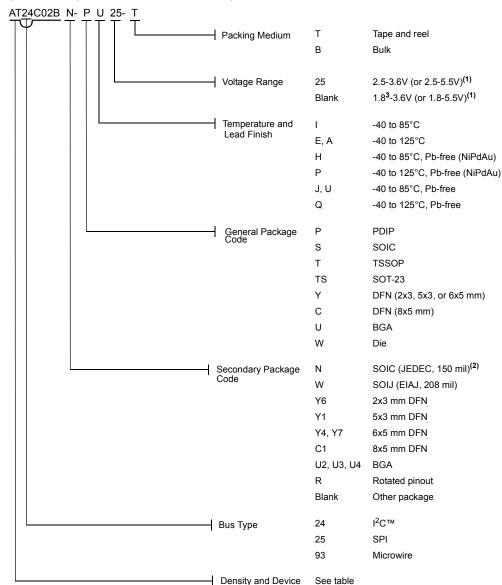

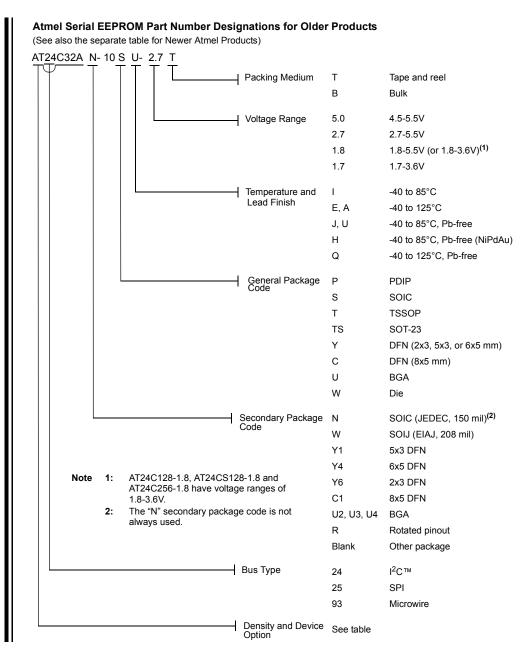

In order to cross-reference a competitor device to a compatible Microchip device, use Microchip's powerful MAPS tool available for free at www.microchip.com/MAPS. You can also decode the competitor part number here, where we have provided a means to translate each code or character.

# **Atmel Serial EEPROM Part Number Designations for Newer Products**

(See also the separate table for Older Atmel Products)

Option

| <b>Device Option</b>     | Bus               | Density  | Comment                                         |

|--------------------------|-------------------|----------|-------------------------------------------------|

| AT24C01B <sup>(1)</sup>  | I <sup>2</sup> C™ | 1 Kbit   |                                                 |

| AT24C02 <sup>(1)</sup>   | I <sup>2</sup> C  | 2 Kbit   |                                                 |

| AT24HC02B <sup>(1)</sup> | I <sup>2</sup> C  | 2 Kbit   | 1/2 array WP                                    |

| AT34C02C <sup>(3)</sup>  | I <sup>2</sup> C  | 2 Kbit   | DIMM serial presence detect, 1.7-3.6V           |

| AT24HC04B <sup>(1)</sup> | I <sup>2</sup> C  | 4 Kbit   | 1/2 array WP                                    |

| AT24C16B                 | I <sup>2</sup> C  | 16 Kbit  | Whole array WP, 1.8-3.6V                        |

| AT24C32C                 | I <sup>2</sup> C  | 32 Kbit  | Whole array WP, 1.8-3.6V                        |

| AT24C64C                 | I <sup>2</sup> C  | 64 Kbit  | Whole array WP, 1.8-3.6V                        |

| AT24C128B                | I <sup>2</sup> C  | 128 Kbit | 1.8-3.6V                                        |

| AT24C256B                | I <sup>2</sup> C  | 256 Kbit | 1.8-3.6V                                        |

| AT24C512B                | I <sup>2</sup> C  | 512 Kbit | 1.8-3.6V                                        |

| AT24C1024B               | I <sup>2</sup> C  | 1 Mbit   | -1.8 version is maximum 3.6V; -2.7 max. is 5.5V |

|                          | -                 | -        |                                                 |

| AT25512                  | SPI               | 512 Kbit | _                                               |

|                          |                   |          |                                                 |

| AT93C46D                 | Microwire         | 1 Kbit   | x8 or x16                                       |

| AT93C46E                 | Microwire         | 1 Kbit   | x16 (no ORG pin)                                |

Note 1: AT24C01B, 24C02B, 24HC02B and 24HC04B have maximum voltages of 5.5V.

The "N" secondary package code is not always used. The AT34C02C has a 1.7-3.6V range.

| Device Option                  | Bus               | Density  | Comment                                        |  |  |

|--------------------------------|-------------------|----------|------------------------------------------------|--|--|

| AT24C01, C11                   | I <sup>2</sup> C™ | 1 Kbit   | No WP, no address pins                         |  |  |

| AT24C01A                       | I <sup>2</sup> C  | 1 Kbit   | Whole array WP, 3 address pins                 |  |  |

| AT24C02                        | I <sup>2</sup> C  | 2 Kbit   | Whole array WP                                 |  |  |

| AT24C02A                       | I <sup>2</sup> C  | 2 Kbit   | 1/2 array WP                                   |  |  |

| AT34C02/02B                    | I <sup>2</sup> C  | 2 Kbit   | DIMM serial presence detect                    |  |  |

| AT24C04                        | I <sup>2</sup> C  | 4 Kbit   | Whole array WP                                 |  |  |

| AT24C04A                       | I <sup>2</sup> C  | 4 Kbit   | 1/2 array WP                                   |  |  |

| AT24C08                        | I <sup>2</sup> C  | 8 Kbit   | No WP                                          |  |  |

| AT24C08A                       | I <sup>2</sup> C  | 8 Kbit   | Whole array WP                                 |  |  |

| AT24C16                        | I <sup>2</sup> C  | 16 Kbit  | 1/2 array WP, no address pins                  |  |  |

| AT24C16A                       | I <sup>2</sup> C  | 16 Kbit  | Whole array WP, no address pins                |  |  |

| AT24C164                       | I <sup>2</sup> C  | 16 Kbit  | Whole array WP, 3 address pins                 |  |  |

| AT24C32                        | I <sup>2</sup> C  | 32 Kbit  | 1/4 array WP                                   |  |  |

| AT24C32A                       | I <sup>2</sup> C  | 32 Kbit  | Whole array WP                                 |  |  |

| AT24C64/64B                    | I <sup>2</sup> C  | 64 Kbit  | 1/4 array WP                                   |  |  |

| AT24C64A                       | I <sup>2</sup> C  | 64 Kbit  | Whole array WP                                 |  |  |

| AT24C128 <sup>(1)</sup> /CS128 | I <sup>2</sup> C  | 128 Kbit | -1.8 version is maximum 3.6V; -2.7 max is 5.5V |  |  |

| AT24C256 <sup>(1)</sup>        | I <sup>2</sup> C  | 256 Kbit | -1.8 version is maximum 3.6V; -2.7 max is 5.5V |  |  |

| AT24C512                       | I <sup>2</sup> C  | 512 Kbit | -1.8 version is maximum 3.6V; -2.7 max is 5.5V |  |  |

| AT24C1024                      | I <sup>2</sup> C  | 1 Mbit   |                                                |  |  |

|                                | Г                 | ı        |                                                |  |  |

| AT25010/010A                   | SPI               | 1 Kbit   |                                                |  |  |

| AT25020/020A                   | SPI               | 2 Kbit   |                                                |  |  |

| AT25040/040A                   | SPI               | 4 Kbit   |                                                |  |  |

| AT25080/080A                   | SPI               | 8 Kbit   |                                                |  |  |

| AT25160/160A                   | SPI               | 16 Kbit  |                                                |  |  |

| AT25320/320A                   | SPI               | 32 Kbit  |                                                |  |  |

| AT25640/640A                   | SPI               | 64 Kbit  |                                                |  |  |

| AT25128/128A                   | SPI               | 128 Kbit |                                                |  |  |

| AT25256/256A                   | SPI               | 256 Kbit |                                                |  |  |

| AT25HP256                      | SPI               | 256 Kbit |                                                |  |  |

| AT25HP512                      | SPI               | 512 Kbit |                                                |  |  |

| AT25P1024                      | SPI               | 1 Mbit   |                                                |  |  |

| AT93C46/46D                    | Microwire         | 1 Kbit   |                                                |  |  |

|                                |                   |          | v16 only (no ODC nin)                          |  |  |

| AT93C46A/46C/46E               | Microwire         | 1 Kbit   | x16 only (no ORG pin)                          |  |  |

| AT93C56/56A                    |                   | 2 Kbit   |                                                |  |  |

| AT93C66/66A                    | Missaudes         | 4 Kbit   |                                                |  |  |

| AT93C86A                       | Microwire         | 16 Kbit  |                                                |  |  |

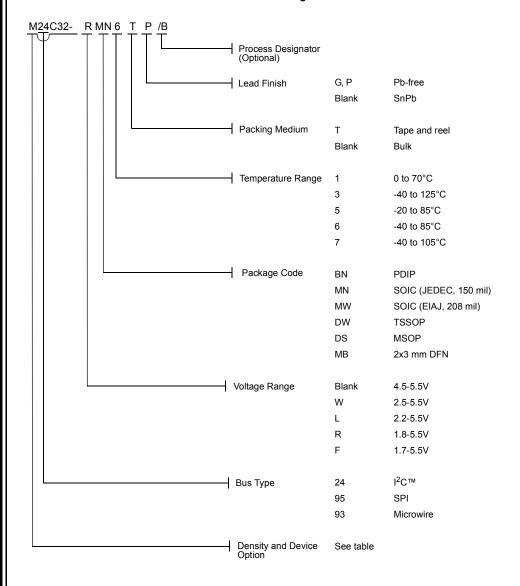

# **STMicroelectronics Serial EEPROM Part Number Designations**

| Device Option | Bus               | Density  | Comment                     |

|---------------|-------------------|----------|-----------------------------|

| M24C01        | I <sup>2</sup> C™ | 1 Kbit   |                             |

| M24C02        | I <sup>2</sup> C  | 2 Kbit   |                             |

| M34C02        | I <sup>2</sup> C  | 2 Kbit   | DIMM serial presence detect |

| M34E02        | I <sup>2</sup> C  | 2 Kbit   | DIMM serial presence detect |

| M34F04        | I <sup>2</sup> C  | 4 Kbit   | 1/2 array WP                |

| M24C04        | I <sup>2</sup> C  | 4 Kbit   |                             |

| M24C08        | I <sup>2</sup> C  | 8 Kbit   |                             |

| M24C16        | I <sup>2</sup> C  | 16 Kbit  |                             |

| M24C32        | I <sup>2</sup> C  | 32 Kbit  |                             |

| M24C64        | I <sup>2</sup> C  | 64 Kbit  |                             |

| M34D64        | I <sup>2</sup> C  | 64 Kbit  | 1/4 array write-protect     |

| M24128-B      | I <sup>2</sup> C  | 128 Kbit |                             |

| M24256-B      | I <sup>2</sup> C  | 128 Kbit |                             |

| M24512        | I <sup>2</sup> C  | 512 Kbit |                             |

| M24M01        | I <sup>2</sup> C  | 1 Mbit   |                             |

|               |                   |          |                             |

| M95010        | SPI               | 1 Kbit   |                             |

| M95020        | SPI               | 2 Kbit   |                             |

| M95040        | SPI               | 4 Kbit   |                             |

| M95080        | SPI               | 8 Kbit   |                             |

| M95160        | SPI               | 16 Kbit  |                             |

| M95320        | SPI               | 32 Kbit  |                             |

| M95640        | SPI               | 64 Kbit  |                             |

| M95128        | SPI               | 128 Kbit |                             |

| M95256        | SPI               | 256 Kbit |                             |

| M95512        | SPI               | 512 Kbit |                             |

| M95M01        | SPI               | 1 Mbit   |                             |

|               |                   |          |                             |

| M93C46        | Microwire         | 1 Kbit   |                             |

| M93C56        | Microwire         | 2 Kbit   |                             |

| M93C66        | Microwire         | 4 Kbit   |                             |

| M93C76        | Microwire         | 8 Kbit   |                             |

| M93C86        | Microwire         | 16 Kbit  |                             |

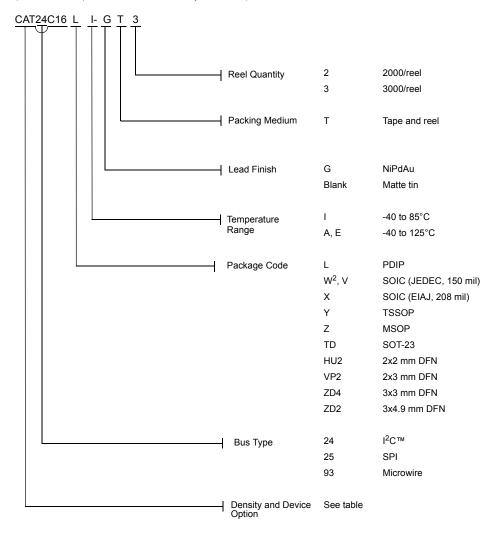

# **Catalyst Serial EEPROM Part Number Designations for Newer Products**

(See also the separate table for Older Catalyst Products)

| Device Option | Bus               | Density  | Comment                                                |  |  |  |

|---------------|-------------------|----------|--------------------------------------------------------|--|--|--|

| CAT24C01      | I <sup>2</sup> C™ | 1 Kbit   |                                                        |  |  |  |

| CAT24C02      | I <sup>2</sup> C  | 2 Kbit   | Full array WP                                          |  |  |  |

| CAT34C02      | I <sup>2</sup> C  | 2 Kbit   | DIMM serial presence detect; 1.7-5.5V                  |  |  |  |

| CAT24C03      | I <sup>2</sup> C  | 2 Kbit   | 1/2 array WP                                           |  |  |  |

| CAT24C04      | I <sup>2</sup> C  | 4 Kbit   | Full array WP                                          |  |  |  |

| CAT24C05      | I <sup>2</sup> C  | 4 Kbit   | 1/2 array WP                                           |  |  |  |

| CAT24C08      | I <sup>2</sup> C  | 8 Kbit   |                                                        |  |  |  |

| CAT24C16      | I <sup>2</sup> C  | 16 Kbit  | No address pins                                        |  |  |  |

| CAT24C164     | I <sup>2</sup> C  | 16 Kbit  | 3 address pins                                         |  |  |  |

| CAT24C32      | I <sup>2</sup> C  | 32 Kbit  |                                                        |  |  |  |

| CAT24C64      | I <sup>2</sup> C  | 64 Kbit  |                                                        |  |  |  |

| CAT24C128     | I <sup>2</sup> C  | 128 Kbit |                                                        |  |  |  |

| CAT24C256     | I <sup>2</sup> C  | 256 Kbit |                                                        |  |  |  |

|               |                   |          |                                                        |  |  |  |

| CAT25010      | SPI               | 1 Kbit   |                                                        |  |  |  |

| CAT25020      | SPI               | 2 Kbit   |                                                        |  |  |  |

| CAT25040      | SPI               | 4 Kbit   |                                                        |  |  |  |

| CAT25080      | SPI               | 8 Kbit   |                                                        |  |  |  |

| CAT25160      | SPI               | 16 Kbit  |                                                        |  |  |  |

| CAT25320      | SPI               | 32 Kbit  |                                                        |  |  |  |

| CAT25640      | SPI               | 64 Kbit  |                                                        |  |  |  |

|               |                   |          |                                                        |  |  |  |

| CAT93C46      | Microwire         | 1 Kb     |                                                        |  |  |  |

| CAT93C46R     | Microwire         | 1 Kb     |                                                        |  |  |  |

| CAT93C66      | Microwire         | 2 Kb     | Older die revs follow the "old" part number convention |  |  |  |

| CAT93C76      | Microwire         | 8 Kb     |                                                        |  |  |  |

Voltage range for all parts is 1.8-5.5V. 1:

For 93-series products, package code "W" is an alternate, rotated pinout. "V" is the standard pinout.

# Catalyst Serial EEPROM Part Number Designations for Older Products

(See also the separate table for Newer Catalyst Products)

| Device Option                                                     | Bus               | Density  | Comment        |

|-------------------------------------------------------------------|-------------------|----------|----------------|

| CAT24C00 <sup>(1, 3)</sup>                                        | I <sup>2</sup> C™ | 128 bit  |                |

| CAT24FC01 <sup>(3)</sup>                                          | I <sup>2</sup> C  | 1 Kbit   |                |

| CAT24WC01                                                         | I <sup>2</sup> C  | 1 Kbit   |                |

| CAT24C01B <sup>(3)</sup>                                          | I <sup>2</sup> C  | 1 Kbit   | No WP          |

| CAT24FC02 <sup>(3)</sup> /WC02                                    | I <sup>2</sup> C  | 2 Kbit   |                |

| CAT24WC04                                                         | I <sup>2</sup> C  | 4 Kbit   |                |

| CAT24WC08                                                         | I <sup>2</sup> C  | 8 Kbit   |                |

| CAT24WC16 <sup>(3)</sup>                                          | I <sup>2</sup> C  | 16 Kbit  |                |

| CAT24WC164 <sup>(3)</sup>                                         | I <sup>2</sup> C  | 16 Kbit  | 3 address pins |

| CAT24FC17 <sup>(3)</sup>                                          | I <sup>2</sup> C  | 16 Kbit  | 1/2 array WP   |

| CAT24FC32 <sup>(3)</sup> /FC32A <sup>(3)</sup> /WC32              | I <sup>2</sup> C  | 32 Kbit  |                |

| CAT24WC33                                                         | I <sup>2</sup> C  | 32 Kbit  | 1/4 array WP   |

| CAT24FC64 <sup>(3)</sup> /WC64                                    | I <sup>2</sup> C  | 64 Kbit  |                |

| CAT24F65 <sup>(3)</sup> /WC65 <sup>(3)</sup> /FC66 <sup>(3)</sup> | I <sup>2</sup> C  | 64 Kbit  |                |

| CAT24WC66                                                         | I <sup>2</sup> C  | 64 Kbit  |                |

| CAT24WC128/AC128/WC129 <sup>(3)</sup>                             | I <sup>2</sup> C  | 128 Kbit |                |

| CAT24FC256 <sup>(3)</sup>                                         | I <sup>2</sup> C  | 256 Kbit |                |

| CAT24WC256/WC257 <sup>(3)</sup>                                   | I <sup>2</sup> C  | 256 Kbit |                |

| CAT25C01 <sup>(3)</sup> /C11 <sup>(3)</sup>                       | CDI               | 4 1/1-14 |                |

| CAT25C01 <sup>(3)</sup> /C03 <sup>(3)</sup>                       | SPI               | 1 Kbit   |                |

| CAT25C02 <sup>(-)</sup> /C03 <sup>(-)</sup>                       | SPI               | 2 Kbit   |                |

|                                                                   | SPI               | 4 Kbit   |                |

| CAT25C08/C09 <sup>(3)</sup>                                       | SPI               | 8 Kbit   |                |

| CAT25C16/C17 <sup>(3)</sup>                                       | SPI               | 16 Kbit  |                |

| CAT25C32/C33 <sup>(3)</sup> CAT25C64/C65 <sup>(3)</sup>           | SPI               | 32 Kbit  |                |

| <u> </u>                                                          | SPI               | 64 Kbit  |                |

| CAT25C128                                                         | SPI               | 128 Kbit |                |

| CAT25C256                                                         | SPI               | 256 Kbit |                |

| 93HC46 <sup>(3)</sup>                                             | Microwire         | 1 Kbit   |                |

| 93C56/C57                                                         | Microwire         | 2 Kbit   |                |

| 93C66                                                             | Microwire         | 4 Kbit   |                |

| 93C86                                                             | Microwire         | 16 Kbit  |                |

Note 1:

- CAT24C00 has a voltage range of 1.8 to 5.5V.

- 2: For 93-series products, package codes "W" and "J" are alternate, rotated pinouts. "V" and "S" are standard pinouts.

- Discontinued part.

# SECTION 3 FAMILY DATA SHEETS

| I <sup>2</sup> C <sup>™</sup> Serial EEPROM Family Data Sheet | 3-1  |

|---------------------------------------------------------------|------|

| 1K-16K Microwire Compatible Serial EEPROM Family Data Sheet   |      |

| SPI Serial EEPROM Family Data Sheet                           | 3-57 |

| Speciality Product References                                 |      |

|                                                               |      |

$\rm I^2C$  is a trademark of Philips Corporation. Smart Serial is a trademark of Microchip Technology Inc.

24AA00/24LC00/24C00 24AA014/24LC014 24AA02/24LC02B

24C02C 24AA024/24LC024 24AA025/24LC025 24AA04/24LC04B 24AA08/24LC08B 24AA16/24LC16B 24AA32A/24LC32A

24AA64/24LC64/24FC64

24AA128/24LC128/24FC128

24AA01/24LC01B

24C01C

# **I**<sup>2</sup>C<sup>™</sup> Serial EEPROM Family Data Sheet

# Features:

- 128-bit through 1024 Kbit Devices

- · Single Supply with Operation Down to 1.7V for 24AAXX Devices

- Low-Power CMOS Technology:

- 1 mA active current, typical

- 1 μA standby current, typical (I-temp)

- 2-Wire Serial Interface Bus, I<sup>2</sup>C™ Compatible

- · Schmitt Trigger Inputs for Noise Suppression

- · Output Slope Control to Eliminate Ground Bounce

- 400 kHz (≥ 2.5V): 24LCXX and 24AAXX

- 1 MHz (≥ 2.5V) and 400 kHz (1.7V): 24FCXX

- Self-Timed Write Cycle (including Auto-Erase)

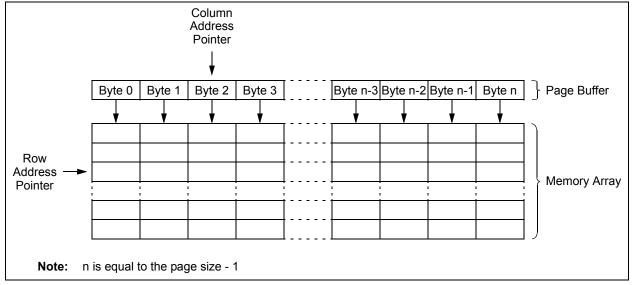

- · Page Write Buffer

- · Hardware Write-Protect Available on Most Devices

- · Factory Programming (QTP) Available

- ESD Protection >4,000V

- · 1 Million Erase/Write Cycles

- · Data Retention >200 years

- · 8-lead PDIP, SOIC, TSSOP and MSOP Packages

- 5-lead SOT-23 Package (Most 1-16 Kbit Devices)

- 8-lead 2x3mm and 5x6mm DFN Packages Available

- · Pb-Free and RoHS Compliant

- · Available for Extended Temperature Ranges:

- Industrial (I): -40°C to +85°C

- Automotive (E): -40°C to +125°C

# **Description:**

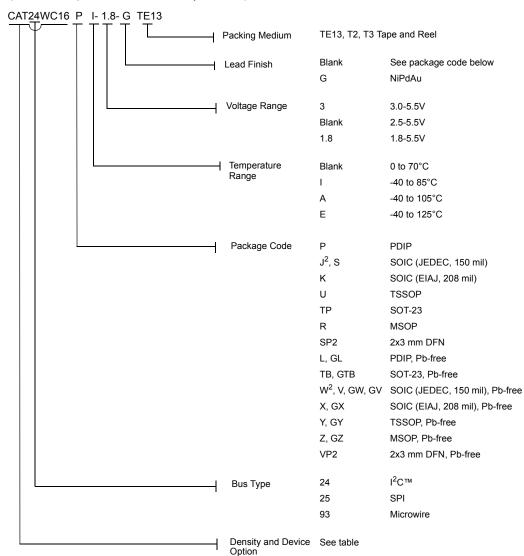

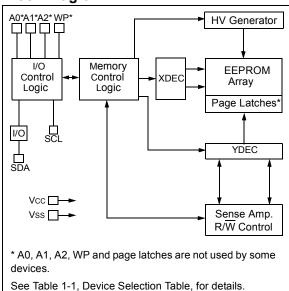

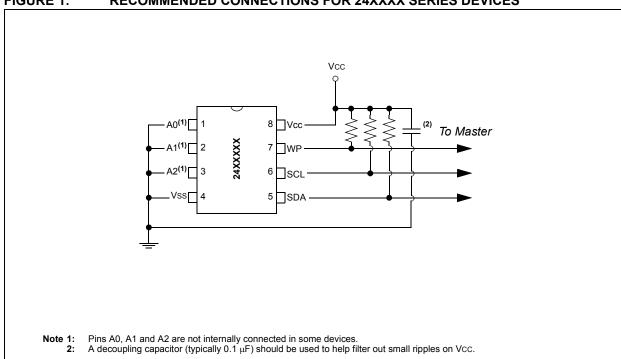

The Microchip Technology Inc. 24CXX, 24LCXX, 24AAXX and 24FCXX (24XX\*) devices are a family of 128-bit through 1024 Kbit Electrically Erased PROMs. The devices are organized in blocks of x8-bit memory with 2-wire serial interfaces. Low-voltage design permits operation down to 1.7V (for 24AAXX devices), with standby and active currents of only 1  $\mu$ A and 1 mA, respectively. Devices 1 Kbit and larger have page write capability. Parts having functional address lines allow connection of up to 8 devices on the same bus. The 24XX family is available in the standard 8-pin PDIP, surface mount SOIC, TSSOP and MSOP packages. Most 128-bit through 16 Kbit devices are also available in the 5-lead SOT-23 package. DFN packages (2x3mm or 5x6mm) are also available. All packages are Pb-free (Matte Tin) finish.

This document is an overview. Note: detailed specifications, please consult the individual product data sheet, available at www.microchip.com.

\*24XX is used in this document as a generic part number for 24 series devices in this data sheet. 24XX64, for example, represents all voltages of the 64 Kbit device.

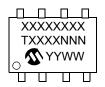

# Package Types<sup>(1)</sup>

# 24AAXX/24LCXX/24FCXX

TABLE 1-1: DEVICE SELECTION TABLE

| IADLE I-I.             | DEVIOL       | SELECTION               | 1 IADEL          |                            |                               |                |                         |

|------------------------|--------------|-------------------------|------------------|----------------------------|-------------------------------|----------------|-------------------------|

| Part Number            | Vcc<br>Range | Max. Clock<br>Frequency | Page<br>Size     | Write-<br>Protect<br>Array | Functional<br>Address<br>Pins | Temp.<br>Range | Packages <sup>(5)</sup> |

| 128-bit device         | es           |                         |                  |                            |                               |                |                         |

| 24AA00                 | 1.7-5.5V     | 400 kHz <sup>(1)</sup>  |                  |                            |                               | I              | P, SN, ST, OT, MC       |

| 24LC00                 | 2.5-5.5V     | 400 kHz <sup>(1)</sup>  | _                | None                       | None                          | I              |                         |

| 24C00                  | 4.5-5.5V     | 400 kHz                 |                  |                            |                               | I, E           |                         |

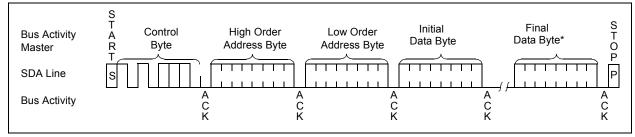

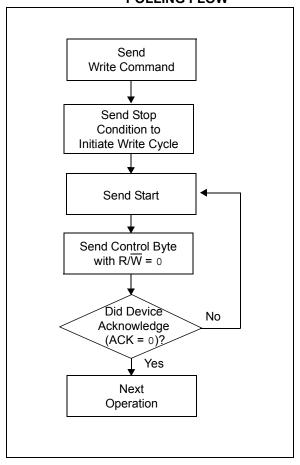

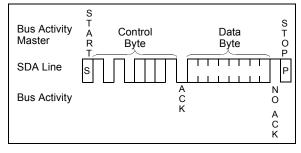

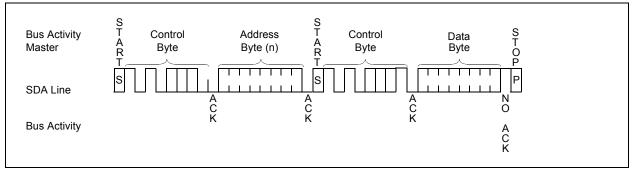

| 1 Kb devices           |              | •                       |                  |                            |                               |                |                         |