# ENC424J600/624J600 Data Sheet

Stand-Alone 10/100 Ethernet Controller with SPI or Parallel Interface

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, Keeloq, Keeloq logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# Stand-Alone 10/100 Ethernet Controller with SPI or Parallel Interface

- IEEE 802.3™ Compliant Fast Ethernet Controller

- Integrated MAC and 10/100Base-T PHY

- · Hardware Security Acceleration Engines

- · 24-Kbyte Transmit/Receive Packet Buffer SRAM

- Supports one 10/100Base-T Port with Automatic Polarity Detection and Correction

- · Supports Auto-Negotiation

- Support for Pause Control Frames, including Automatic Transmit and Receive Flow Control

- · Supports Half and Full-Duplex Operation

- Programmable Automatic Retransmit on Collision

- · Programmable Padding and CRC Generation

- Programmable Automatic Rejection of Erroneous and Runt Packets

- Factory Preprogrammed Unique MAC Address

- MAC

- Support for Unicast, Multicast and Broadcast packets

- Supports promiscuous reception

- Programmable pattern matching

- Programmable filtering on multiple packet formats, including Magic Packet<sup>™</sup>, Unicast, Multicast, Broadcast, specific packet match, destination address hash match or any packet

- · PHY:

- Wave shaping output filter

- Internal Loopback mode

- Energy Detect Power-Down mode

- · Available MCU Interfaces:

- 14 Mbit/s SPI interface with enhanced set of opcodes (44-pin and 64-pin packages)

- 8-bit multiplexed parallel interface (44-pin and 64-pin packages)

- 8-bit or 16-bit multiplexed or demultiplexed parallel interface (64-pin package only)

- · Security Engines:

- High-performance, modular exponentiation engine with up to 1024-bit operands

- Supports RSA® and Diffie-Hellman key exchange algorithms

- High-performance AES encrypt/decrypt engine with 128-bit, 192-bit or 256-bit key

- Hardware AES ECB, CBC, CFB and OFB mode capability

- Software AES CTR mode capability

- Fast MD5 hash computations

- Fast SHA-1 hash computations

- · Buffer:

- Configurable transmit/receive buffer size

- Hardware-managed circular receive FIFO

- 8-bit or 16-bit random and sequential access

- High-performance internal DMA for fast memory copying

- High-performance hardware IP checksum calculations

- Accessible in low-power modes

- Space can be reserved for general purpose application usage in addition to transmit and receive packets

- · Operational:

- Outputs for two LED indicators with support for single and dual LED configurations

- Transmit and receive interrupts

- 25 MHz clock

- 5V tolerant inputs

- Clock out pin with programmable frequencies from 50 kHz to 33.3 MHz

- Operating voltage range of 3.0V to 3.6V

- Temperature range: -40°C to +85°C industrial

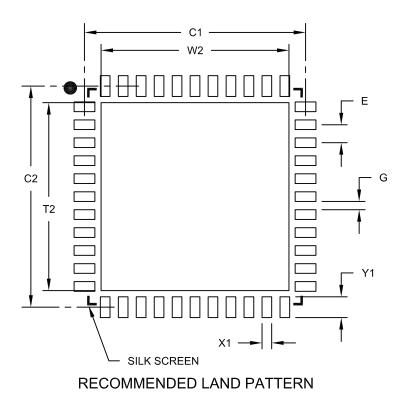

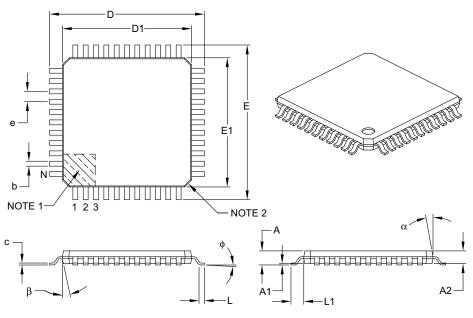

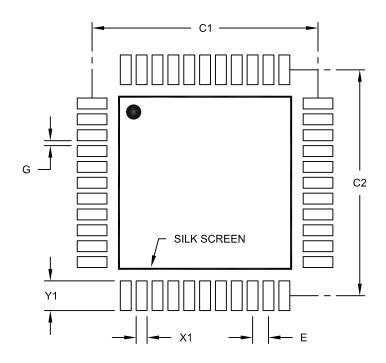

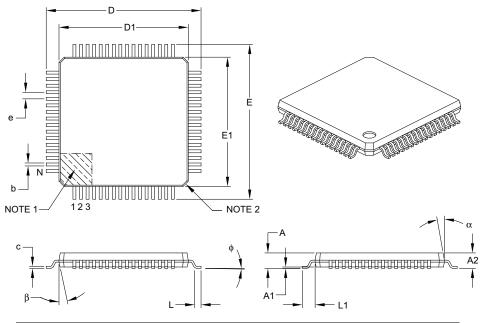

- Available in 44-Pin (TQFP and QFN) and 64-Pin TQFP PackageS

|            |         |         |        | ;                 | Security     |                |           |       | PS     | SP            |        |

|------------|---------|---------|--------|-------------------|--------------|----------------|-----------|-------|--------|---------------|--------|

| Device     | SRAM    | RAM Pin | Speed  |                   |              |                | SPI Multi |       | lexed  | Demultiplexed |        |

| 500.00     | (bytes) | Count   | (Mbps) | ModEx<br>1024-Bit | MD5<br>SHA-1 | AES<br>256-Bit | 5.        | 8-Bit | 16-Bit | 8-Bit         | 16-Bit |

| ENC424J600 | 24K     | 44      | 10/100 | Y                 | Y            | Y              | Y         | Y     | N      | N             | N      |

| ENC624J600 | 24K     | 64      | 10/100 | Υ                 | Υ            | Υ              | Υ         | Υ     | Υ      | Υ             | Υ      |

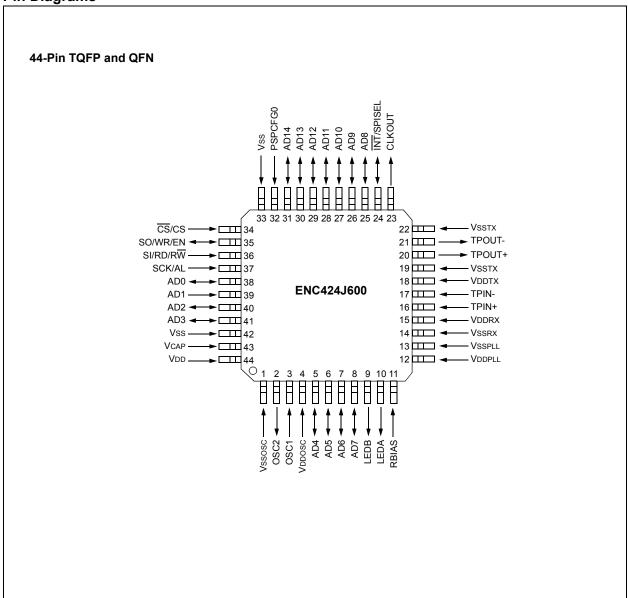

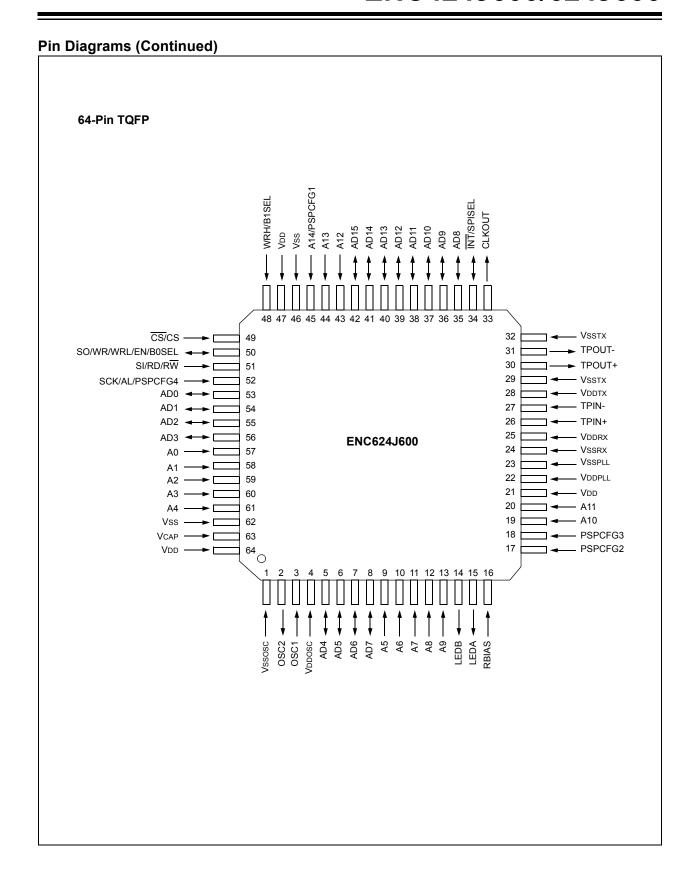

## **Pin Diagrams**

## **Table of Contents**

| 1.0   | Device Overview                                 | 5   |

|-------|-------------------------------------------------|-----|

| 2.0   | External Connections                            | 9   |

| 3.0   | Memory Organization                             | 17  |

| 4.0   | Serial Peripheral Interface (SPI)               | 39  |

| 5.0   | Parallel Slave Port Interface (PSP)             | 51  |

| 6.0   | Ethernet Overview                               | 71  |

| 7.0   | Reset                                           | 73  |

| 8.0   | Initialization                                  | 75  |

| 9.0   | Transmitting and Receiving Packets              | 83  |

| 10.0  | Receive Filters                                 | 95  |

| 11.0  | Flow Control                                    | 105 |

| 12.0  | Speed/Duplex Configuration and Auto-Negotiation | 109 |

| 13.0  | Interrupts                                      | 117 |

| 14.0  | Direct Memory Access (DMA) Controller           | 123 |

| 15.0  | Cryptographic Security Engines                  | 125 |

| 16.0  | Power-Saving Features                           | 137 |

| 17.0  | Electrical Characteristics                      | 141 |

| 18.0  | Packaging Information                           | 149 |

| Appe  | endix A: Revision History                       | 157 |

| Index | C                                               | 159 |

| The I | Vicrochip Web Site                              | 163 |

| Custo | omer Change Notification Service                | 163 |

|       | omer Support                                    |     |

| Read  | ler Response                                    | 164 |

| Prod  | uct Identification System                       | 165 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- ENC424J600

- ENC624J600

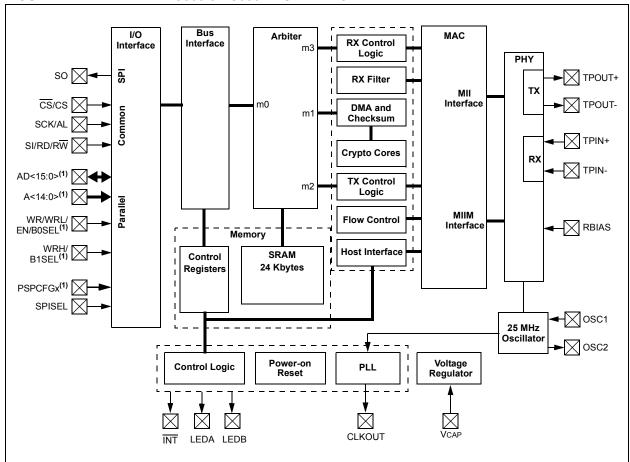

The ENC424J600 and ENC624J600 are stand-alone, Fast Ethernet controllers with an industry standard Serial Peripheral Interface (SPI) or a flexible parallel interface. They are designed to serve as an Ethernet network interface for any microcontroller equipped with SPI or a standard parallel port.

ENC424J600/624J600 devices meet all of the IEEE 802.3 specifications applicable to 10Base-T and 100Base-TX Ethernet, including many optional clauses, such as auto-negotiation. They incorporate a number of packet filtering schemes to limit incoming packets. They also provide an internal, 16-bit wide DMA for fast data throughput and support for hardware IP checksum calculations.

For applications that require the security and authentication features of SSL, TLS and other protocols related to cryptography, a block of security engines is provided. The engines perform RSA, Diffie-Hellman, AES, MD5 and SHA-1 algorithm computations, allowing reduced code size, faster connection establishment and throughput, and reduced firmware development effort.

Communication with the microcontroller is implemented via the SPI or parallel interface, with data rates ranging from 14 Mbit/s (SPI) to 160 Mbit/s (demultiplexed, 16-bit parallel interface). Dedicated pins are used for LED link and activity indication and for transmit/receive/DMA interrupts.

A generous 24-Kbyte on-chip RAM buffer is available for TX and RX operations. It may also be used by the host microcontroller for general purpose storage. Communication protocols, such as TCP, can use this memory for saving data which may need to be retransmitted.

For easy end product manufacturability, each ENC624J600 family device is preprogrammed with a unique nonvolatile MAC address. In most cases, this allows the end device to avoid a serialized programming step.

The only functional difference between the ENC424J600 (44-pin) and ENC624J600 (64-pin) devices are the number of parallel interface options they support. These differences, along with a summary of their common features, are provided in Table 1-1. A general block diagram for the devices is shown in Figure 1-1.

A list of the pin features, sorted by function, is presented in Table 1-2.

TABLE 1-1: DEVICE FEATURES FOR ENC424J600/624J600

| Feature                          | ENC424J600                                                                                                                                                                 | ENC624J600                 |  |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

| Pin Count                        | 44                                                                                                                                                                         | 64                         |  |  |

| Ethernet Operating Speed         | 10/100 Mbps (auto-negotia                                                                                                                                                  | ate, auto-sense or manual) |  |  |

| Ethernet Duplex Modes            | Half and Full (auto-ne                                                                                                                                                     | egotiate and manual)       |  |  |

| Ethernet Flow Control            | Pause and Backpress                                                                                                                                                        | ure (auto and manual)      |  |  |

| Buffer Memory (bytes)            | 24K (organized a                                                                                                                                                           | s 12K word x 16)           |  |  |

| Internal Interrupt Sources       | 11 (mappable to a single                                                                                                                                                   | e external interrupt flag) |  |  |

| Serial Host Interface (SPI)      | Yes                                                                                                                                                                        | Yes                        |  |  |

| Parallel Host Interface:         |                                                                                                                                                                            |                            |  |  |

| Operating modes                  | 2                                                                                                                                                                          | 8                          |  |  |

| Muliplexed, 8-bit                | Yes                                                                                                                                                                        | Yes                        |  |  |

| 16-bit                           | No                                                                                                                                                                         | Yes                        |  |  |

| Demultiplexed, 8-bit             | No                                                                                                                                                                         | Yes                        |  |  |

| 16-bit                           | No                                                                                                                                                                         | Yes                        |  |  |

| Cryptographic Security Options:  |                                                                                                                                                                            |                            |  |  |

| AES, 128/192/256-bit             | Yes                                                                                                                                                                        | Yes                        |  |  |

| MD5/SHA-1                        | Yes                                                                                                                                                                        | Yes                        |  |  |

| Modular Exponentiation, 1024-bit | Yes                                                                                                                                                                        | Yes                        |  |  |

| Receive Filter Options           | Accept or reject packets with CRC match/mismatch, runt error collect or reject, Unicast, Not-Me Unicast, Multicast, Broadcast, Magic Packet™, Pattern Table and Hash Table |                            |  |  |

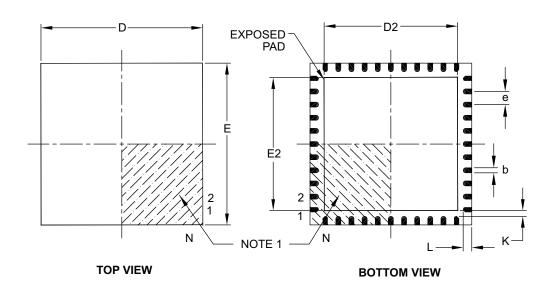

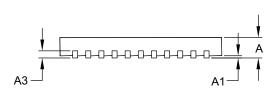

| Packages                         | 44-Pin TQFP, QFN                                                                                                                                                           | 64-Pin TQFP                |  |  |

## FIGURE 1-1: ENC424J600/624J600 BLOCK DIAGRAM

Note 1: A<14:0>, AD15, WRL/B0SEL, WRH/B1SEL and PSPCFG<4:1> are available on 64-pin devices only. PSPCFG0 is available on 44-pin devices only.

TABLE 1-2: ENC424J600/624J600 PINOUT DESCRIPTIONS

|          |        | umber  |          | Input  | CKIF HONG                                                |

|----------|--------|--------|----------|--------|----------------------------------------------------------|

| Pin Name | 44-Pin | 64-Pin | Pin Type | Buffer | Description                                              |

| AD0      | 38     | 53     | I/O      | CMOS   | PSP Multiplexed Address Input and/or Bidirectional       |

| AD1      | 39     | 54     | I/O      | CMOS   | Data Bus                                                 |

| AD2      | 40     | 55     | I/O      | CMOS   |                                                          |

| AD3      | 41     | 56     | I/O      | CMOS   |                                                          |

| AD4      | 5      | 5      | I/O      | CMOS   |                                                          |

| AD5      | 6      | 6      | I/O      | CMOS   |                                                          |

| AD6      | 7      | 7      | I/O      | CMOS   |                                                          |

| AD7      | 8      | 8      | I/O      | CMOS   |                                                          |

| AD8      | 25     | 35     | I/O      | CMOS   |                                                          |

| AD9      | 26     | 36     | I/O      | CMOS   |                                                          |

| AD10     | 27     | 37     | I/O      | CMOS   |                                                          |

| AD11     | 28     | 38     | I/O      | CMOS   |                                                          |

| AD12     | 29     | 39     | I/O      | CMOS   |                                                          |

| AD13     | 30     | 40     | I/O      | CMOS   |                                                          |

| AD14     | 31     | 41     | I/O      | CMOS   |                                                          |

| AD15     | _      | 42     | I/O      | CMOS   |                                                          |

| A0       | _      | 57     | I        | CMOS   | PSP Demultiplexed Address Input Bus                      |

| A1       | _      | 58     | I        | CMOS   |                                                          |

| A2       | _      | 59     | I        | CMOS   |                                                          |

| A3       | _      | 60     | I        | CMOS   |                                                          |

| A4       | _      | 61     | I        | CMOS   |                                                          |

| A5       | _      | 9      | I        | CMOS   |                                                          |

| A6       | _      | 10     | I        | CMOS   |                                                          |

| A7       | _      | 11     | I        | CMOS   |                                                          |

| A8       | _      | 12     | I        | CMOS   |                                                          |

| A9       | _      | 13     | I        | CMOS   |                                                          |

| A10      | _      | 19     | I        | CMOS   |                                                          |

| A11      | _      | 20     | I        | CMOS   |                                                          |

| A12      | _      | 43     | I        | CMOS   |                                                          |

| A13      | _      | 44     | I        | CMOS   |                                                          |

| A14      | _      | 45     | I        | CMOS   |                                                          |

| AL       | 37     | 52     | I        | CMOS   | PSP Address Latch                                        |

| B0SEL    | _      | 50     | I        | CMOS   | PSP Byte 0 Select                                        |

| B1SEL    | _      | 48     | I        | CMOS   | PSP Byte 1 Select                                        |

| CLKOUT   | 23     | 33     | 0        | _      | Programmable Clock Output for External Use               |

| CS       | 34     | 49     | I        | CMOS   | SPI Chip Select (active-low)                             |

| CS       | 34     | 49     | I        | CMOS   | PSP Chip Select (active-high)                            |

| EN       | 35     | 50     | I        | CMOS   | PSP R/W Enable strobe                                    |

| ĪNT      | 24     | 34     | 0        | _      | Interrupt Output (active-low)                            |

| LEDA     | 10     | 15     | 0        | _      | Programmable Ethernet Status/Activity LED                |

| LEDB     | 9      | 14     | 0        | _      | Programmable Ethernet Status/Activity LED                |

|          |        |        |          |        | Compatible input huffer: ANA = Analog level input/output |

**Legend:** I = Input; O = Output; P = Power; CMOS = CMOS compatible input buffer; ANA = Analog level input/output

TABLE 1-2: ENC424J600/624J600 PINOUT DESCRIPTIONS (CONTINUED)

|          | Pin Nu | umber         |          | Input<br>Buffer | D                                                  |  |  |

|----------|--------|---------------|----------|-----------------|----------------------------------------------------|--|--|

| Pin Name | 44-Pin | 64-Pin        | Pin Type |                 | Description                                        |  |  |

| OSC1     | 3      | 3             | ı        | ANA             | 25 MHz Crystal Oscillator/Clock Input              |  |  |

| OSC2     | 2      | 2             | 0        | _               | 25 MHz Crystal Oscillator Output                   |  |  |

| PSPCFG0  | 32     | _             | I        | CMOS            | PSP Mode Select 0                                  |  |  |

| PSPCFG1  | _      | 45            | I        | CMOS            | PSP Mode Select 1                                  |  |  |

| PSPCFG2  | _      | 17            | I        | CMOS            | PSP Mode Select 2                                  |  |  |

| PSPCFG3  | _      | 18            | I        | CMOS            | PSP Mode Select 3                                  |  |  |

| PSPCFG4  | _      | 52            | I        | CMOS            | PSP Mode Select 4                                  |  |  |

| RBIAS    | 11     | 16            | I        | ANA             | PHY Bias (external resistor) Connection            |  |  |

| RD       | 36     | 51            | I        | CMOS            | PSP Read Strobe                                    |  |  |

| RW       | 36     | 51            | I        | CMOS            | PSP Combined Read/Write Signal                     |  |  |

| SCK      | 37     | 52            | I        | CMOS            | SPI Serial Clock Input                             |  |  |

| SI       | 36     | 51            | I        | CMOS            | SPI Serial Data Input (from Master)                |  |  |

| SO       | 35     | 50            | 0        | _               | SPI Serial Data Out (to Master)                    |  |  |

| SPISEL   | 24     | 34            | I        | CMOS            | SPI/PSP Interface Select                           |  |  |

| TPIN-    | 17     | 27            | I        | ANA             | Differential Ethernet Receive Minus Signal Input   |  |  |

| TPIN+    | 16     | 26            | I        | ANA             | Differential Ethernet Receive Plus Signal Input    |  |  |

| TPOUT-   | 21     | 31            | 0        | _               | Differential Ethernet Transmit Minus Signal Output |  |  |

| TPOUT+   | 20     | 30            | 0        | _               | Differential Ethernet Transmit Plus Signal Output  |  |  |

| VCAP     | 43     | 63            | Р        | _               | Regulator External Capacitor connection            |  |  |

| VDD      | 44     | 21, 47,<br>64 | Р        | _               | Positive 3.3V Power Supply for Digital Logic       |  |  |

| VDDOSC   | 4      | 4             | Р        | _               | Positive 3.3V Power Supply for 25 MHz Oscillator   |  |  |

| VDDPLL   | 12     | 22            | Р        | _               | Positive 3.3V Power Supply for PHY PLL Circuitry   |  |  |

| VDDRX    | 15     | 25            | Р        | _               | Positive 3.3V Power Supply for PHY RX Circuitry    |  |  |

| VDDTX    | 18     | 28            | Р        | _               | Positive 3.3V Power Supply for PHY TX Circuitry    |  |  |

| Vss      | 33, 42 | 46, 62        | Р        | _               | Ground Reference for Digital Logic                 |  |  |

| Vssosc   | 1      | 1             | Р        | _               | Ground Reference for 25 MHz Oscillator             |  |  |

| VSSPLL   | 13     | 23            | Р        | _               | Ground Reference for PHY PLL Circuitry             |  |  |

| Vssrx    | 14     | 24            | Р        | _               | Ground Reference for PHY RX Circuitry              |  |  |

| Vsstx    | 19, 22 | 29, 32        | Р        | _               | Ground Reference for PHY TX Circuitry              |  |  |

| WR       | 35     | 50            | I        | CMOS            | PSP Write Strobe                                   |  |  |

| WRH      | _      | 48            | I        | CMOS            | PSP Write High Strobe                              |  |  |

| WRL      | _      | 50            | I        | CMOS            | PSP Write Low Strobe                               |  |  |

**Legend:** I = Input; O = Output; P = Power; CMOS = CMOS compatible input buffer; ANA = Analog level input/output

## 2.0 EXTERNAL CONNECTIONS

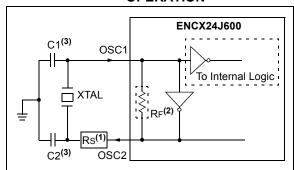

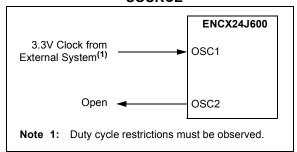

## 2.1 Oscillator

ENC424J600/624J600 devices are designed to operate from a fixed 25 MHz clock input. This clock can be generated by an external CMOS clock oscillator or a parallel resonant, fundamental mode 25 MHz crystal attached to the OSC1 and OSC2 pins. Use of a crystal, rated for series resonant operation, will oscillate at an incorrect frequency. To comply with IEEE 802.3 Ethernet timing requirements, the clock must have no more than ±50 ppm of total error; avoid using resonators or clock generators that exceed this margin.

When clocking the device using a crystal, follow the connections shown in Figure 2-1. When using a CMOS clock oscillator or other external clock source, follow Figure 2-2.

FIGURE 2-1: CRYSTAL OSCILLATOR OPERATION

- Note 1: A series resistor, RS, may be required for crystals with a low drive strength specification or when using large loading capacitors.

- 2: The feedback resistor, RF, is typically 1.5 M $\Omega$  (approx).

- **3:** The load capacitors' value should be derived from the capacitive loading specification provided by the crystal manufacture.

## FIGURE 2-2: EXTERNAL CLOCK SOURCE

## 2.2 CLKOUT Pin

The Clock Out pin (CLKOUT) is provided for use as the host controller clock or as a clock source for other devices in the system. Its use is optional.

The 25 MHz clock applied to OSC1 is multiplied by a PLL to internally generate a 100 MHz base clock. This 100 MHz clock is driven through a configurable postscaler to yield a wide range of different CLKOUT frequencies. The PLL multiplication adds clock jitter, subject to the PLL jitter specification in **Section 17.0** "Electrical Characteristics". However, the postscaler ensures that the clock will have a nearly ideal duty cycle.

The CLKOUT function is enabled and the postscaler is selected via the COCON<3:0> bits (ECON2<11:8>). To create a clean clock signal, the CLKOUT output and COCON bits are unaffected by all resets and power-down modes. The CLKOUT function is enabled out of POR and defaults to producing a 4 MHz clock. This allows the device to directly clock the host processor.

When the COCON bits are written with a new configuration, the CLKOUT output transitions to the new frequency without producing any glitches. No high or low pulses with a shorter period than the original or new clock are generated.

## 2.3 Voltage and Bias Pin

## 2.3.1 VDD AND Vss PINS

To reduce on-die noise levels and provide for the high-current demands of Ethernet, there are many power pins on ENC424J600/624J600 devices:

- VDD and Vss

- VDDosc and Vssosc

- VDDPLL and VSSPLL

- · VDDRX and VSSRX

- VDDTX and VSSTX

Each VDD and Vss pin pair above should have a 0.1  $\mu$ F ceramic bypass capacitor placed as close to the pins as possible. For best EMI emission suppression, other smaller capacitors, such as 0.001  $\mu$ F, should be placed immediately across VDDTX/VSSTX and VDDPLL/VSSPLL.

All VDD power supply pins must be externally connected to the same  $3.3V\pm10\%$  power source. Similarly, all VSS supply references must be externally connected to the same ground node. If a ground connection appears on two pins (e.g., VSSTX), connect both pins; do not allow either to float. In addition, it is recommended that the exposed bottom metal pad on the 44-pin QFN package be tied to VSS.

Placing ferrite beads or inductors between any two of the supply pins (e.g., between VDDOSC and VDDRX) is not recommended. However, it is acceptable to isolate all of the VDD supplies from the main circuit power supply through a single ferrite bead or inductor, if desired for supply noise suppression reasons. Such isolation is generally not necessary.

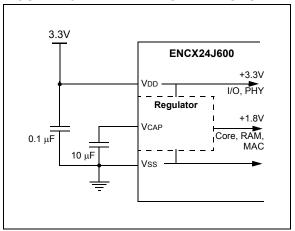

## 2.3.2 VCAP PIN

Most of the device's digital logic operates at a nominal 1.8V. This voltage is supplied by an on-chip voltage regulator, which generates the digital supply voltage from the VDD rail. The only external component required is an external filter capacitor, connected from the VCAP pin to ground, as shown in Figure 2-3. A value of at least 10  $\mu\text{F}$  is recommended.

The capacitor must also have a relatively low Equivalent Series Resistance (ESR). It is recommended that a low-ESR capacitor (ceramic, tantalum or similar) should be used and high-ESR capacitors (such as aluminum electrolytic) should be avoided.

The internal regulator is not designed to drive external loads; therefore, do not attach other circuitry to VCAP.

FIGURE 2-3: VCAP CONNECTIONS

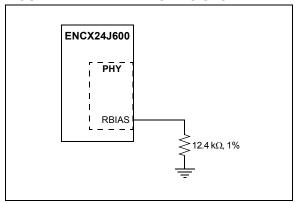

## 2.3.3 RBIAS PIN

The internal analog circuitry in the PHY module requires that an external 12.4 k $\Omega$ , 1% resistor be attached from RBIAS to ground, as shown in Figure 2-4. The resistor influences the TPOUT+/signal amplitude. The RBIAS resistor should be placed as close as possible to the chip with no immediately adjacent signal traces in order to prevent noise capacitively coupling into the pin and affecting the transmit behavior. It is recommended that the resistor be a surface mount type.

FIGURE 2-4: RBIAS RESISTOR

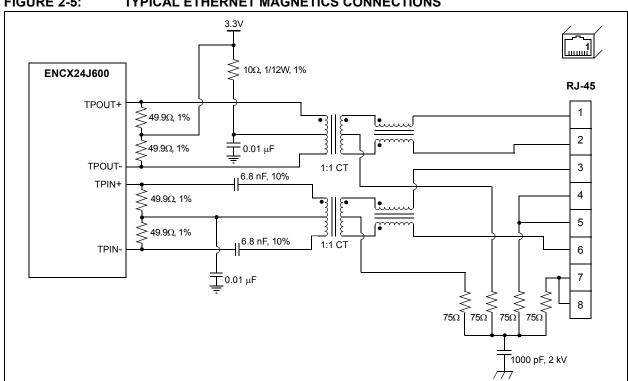

#### 2.4 **Ethernet Signal Pins and External Magnetics**

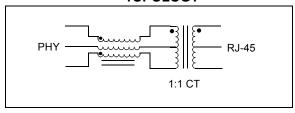

Typical applications for ENC424J600/624J600 devices require an Ethernet transformer module, and a few resistors and capacitors to implement a complete IEEE 802.3 compliant 10/100 Ethernet interface, as shown in Figure 2-5.

The Ethernet transmit interface consists of two pins: TPOUT+ and TPOUT-. These pins implement a differential pair and a current-mode transmitter. To generate an Ethernet waveform, ordinary applications require the use of a 1:1 center tapped pulse transformer, rated for 10/100 or 10/100/1000 Ethernet operations. When the Ethernet module is enabled and linked with a partner, current is continually sunk through both TPOUT pins. When the PHY is actively transmitting, a differential voltage is created on the Ethernet cable by varying the relative current sunk by TPOUT+ compared to TPOUT-.

The Ethernet receive interface similarly consists of a differential pair: TPIN+ and TPIN-. To meet IEEE 802.3 compliance and help protect against electrostatic discharge, these pins are normally isolated from the Ethernet cable by a 1:1 center tapped transformer (available in the same package as the TX transformer).

Internally, the PHY uses a high-speed ADC to sample the receive waveform and decodes it using a DSP. The PHY implements many robustness features, including baseline wander correction (applicable to 100Base-TX) and automatic RX polarity correction (applicable to 10Base-T).

Four  $49.9\Omega$ , 1% resistors are required for proper termination of the TX and RX transmission lines. If the board layout necessitates long traces between the ENCX24J600 and Ethernet transformers, the termination resistors should be placed next to the silicon instead of the transformers.

On the receive signal path, two 6.8 nF 10% capacitors are used. These capacitors, in combination with the  $49.9\Omega$  termination resistors, form an RC high-pass filter to reduce baseline wander. For best performance, these capacitors should not be omitted or changed. The various remaining capacitors provide DC current blocking and provide stability to the common-mode voltage of both of the differential pairs. The TPIN+/pins weakly output a common-mode voltage that is acceptable to the internal ADC. For proper operation, do not attempt to externally force the TPIN+/common-mode voltage to some other value.

The  $10\Omega$  1% resistor provides a current path from the power supply to the center tap of the TX transformer. As mentioned previously, the TPOUT+/- pins implement a Current mode drive topology in which the pins are only capable of sinking current; they do not produce a direct voltage. This current path through the transformer generates the transmit waveform. The  $10\Omega$ resistor reduces the amount of heat that the PHY would have to dissipate, and therefore, must have a power rating of 1/12W or better.

FIGURE 2-5: TYPICAL ETHERNET MAGNETICS CONNECTIONS

## 2.4.1 ADDITIONAL EMI AND LAYOUT CONSIDERATIONS

To reduce EMI emissions, common-mode chokes are shown adjacent to the transformers on the cable (RJ-45) side. These chokes come standard in typical Ethernet transformer modules. Because the ENCX24J600 PHY uses a current-mode drive topology, the transmit choke must normally be located on the cable side of the transmit transformer. Orienting the magnetics such that the choke is on the PHY side of the transmit transformer usually results in a distorted, non-compliant transmit waveform. However, some magnetics which wrap the TX center tap wire around the TX choke core can also be used to generate a compliant waveform (Figure 2-6). These types of transformers may be desirable in some Power-over Ethernet (PoE) applications.

FIGURE 2-6: ALTERNATE TX CHOKE TOPOLOGY

The common-mode choke on the RX interface can be placed on either the cable side or PHY side of the receive transformer. Recommended and required magnetics characteristics are located in **Section 17.0** "Electrical Characteristics".

The four  $75\Omega$  resistors and high-voltage capacitor in Figure 2-5 are intended to prevent each of the twisted pairs in the Ethernet cables from floating and radiating EMI. Their implementation may require adjustment in PoE applications.

Unless the TX and RX signal pairs are kept short, they should be routed between the ENCX24J600 and the Ethernet connector following differential routing rules. Like Ethernet cables,  $100\Omega$  characteristic impedance should be targeted for the differential traces. The use of vias, which introduce impedance discontinuities, should be minimized. Other board level signals should not run immediately parallel to the TX and RX pairs to minimize capacitive coupling and crosstalk.

## 2.5 LEDA and LEDB Pins

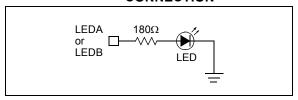

The LEDA and LEDB pins provide dedicated LED status indicator outputs. The LEDs are intended to display link status and TX/RX activity among other programmable options; however, the use of one or both is entirely optional. The pins are driven automatically by the hardware and require no support from the host microcontroller. Aside from the LEDs themselves, a current-limiting resistor is generally the only required component.

By default on POR, LEDA displays the Ethernet link status, while LEDB displays PHY-level TX/RX activity. Because the LEDs operate at the PHY level, RX activity will be displayed on LEDB any time Ethernet packets are detected, regardless of if the packet is valid and meets the correct RX filtering criteria.

Normally, the device illuminates the LED by sourcing current out of the pin, as shown in Figure 2-7. Connecting the LED in reverse, with the anode connected to VDD and the cathode to LEDA/LEDB (through a current-limiting resistor), causes the LED to show "inverted sense" behavior, lighting the LED when it should be off and extinguishing the LED when the LED should be on.

FIGURE 2-7: SINGLE COLOR LED CONNECTION

Both LEDs automatically begin operation whenever power is applied, a 25 MHz clock is present and the Ethernet magnetics are present and wired correctly. A connection to the host microcontroller via the SPI or PSP interface is not required. LEDA and LEDB can, therefore, be used as a quick indicator of successful assembly during initial prototype development.

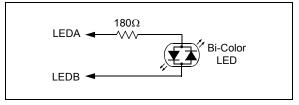

## 2.5.1 USING BI-COLOR LEDs

In space constrained applications, it is frequently desirable to use a single bi-color LED to display multiple operating parameters. These LEDs are connected between LEDA and LEDB, as shown in Figure 2-8.

FIGURE 2-8: BI-COLOR LED CONNECTION

ENCX24J600 devices include two special hardware display modes to make maximal use of a bi-color LED. These modes are selected when the LACFG<3:0> and LBCFG<3:0> bits (EIDLED<15:8>) are set to '1111' or '1110'. In these configurations, the link state turns the LED on, the speed/duplex state sets the LED color and TX/RX events cause the LED to blink off. If a link is present, no TX/RX events are occurring and the speed/duplex state is 100 Mbps/full duplex, respectively, then the LEDB pin will be driven high while LEDA will be driven low.

## 2.6 INT Pin

The INT pin is an active-low signal that is used to flag interrupt events to external devices. Depending on the application, it can be used to signal the host microcontroller whenever a packet has been received or transmitted, or that some other asynchronous operation has occurred. It can also be used to wake-up the microcontroller or other system components based on LAN activity; its use is optional.

The INT pin is driven high when no interrupt is pending and is driven low when an interrupt has occurred. It does not go into a high-impedance state, except during initial power-on while the multiplexed SPISEL pin function is being used.

Since ENC424J600/624J600 devices incorporate a buffer for storing transmit and receive packets, the host microcontroller never needs to perform real-time operations on the device. The microcontroller can poll the device registers to discover if the device status has changed.

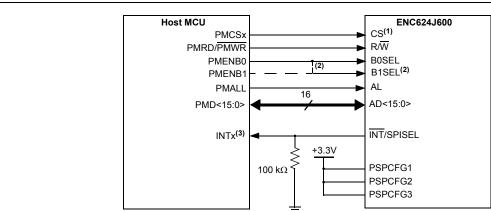

## 2.7 Host Interface Pins

For the maximum degree of flexibility in interfacing with microcontrollers, ENC424J600/624J600 devices offer a choice between a serial interface based on the Serial Peripheral Interface (SPI) standard, and a flexible 8 or 16-bit parallel slave port (PSP) interface. Only one interface may be used at any given time.

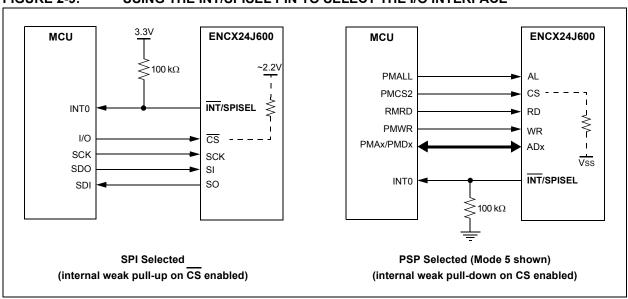

The I/O interface is hardware selected on power-up using the SPISEL function on the  $\overline{\text{INT}}/\text{SPISEL}$  pin. This is done by latching in the voltage level applied to the pin

approximately 1 to 10  $\mu$ s after power is applied to the device and the device exits Power-on Reset. If SPISEL is latched at a logic high state, the serial interface is enabled. If SPISEL is latched at a logic low state, the PSP interface is enabled. Figure 2-9 shows example connections required to select the SPI or PSP interface upon power-up.

To ensure the SPI interface is selected upon power-up, an external pull-up resistor to VDD must be connected to the SPISEL pin. Alternatively, if the parallel interface is to be used, a pull-down resistor to Vss must be connected to the SPISEL pin. In most circuits, it is recommended that a 100 k $\Omega$  or smaller resistor be used to ensure that the correct logic level is latched in reliably. If a large capacitance is present in the SPISEL circuit, such as from stray capacitance, a smaller pull-up or pull-down resistor may be required to compensate and ensure the correct level is sensed during power-up.

As SPISEL is multiplexed with the  $\overline{\text{INT}}$  interrupt output function, a direct connection to VDD or Vss without a resistor is prohibited. If  $\overline{\text{INT}}$  is connected to the host microcontroller, the microcontroller must leave this signal in a high-impedance state and not attempt to drive it to an incorrect logic state during power-up.

If the VDD supply has a slow ramp rate, the device will exit POR, exceed the 1 to 10  $\mu s$  latch timer and sample the SPISEL pin state before VDD has reached the specified minimum operating voltage of the device. In this case, the device will still latch in the correct value, assuming the minimum VIH (D004) or maximum VIL (D006) specification is met, which is a function of VDD.

FIGURE 2-9: USING THE INT/SPISEL PIN TO SELECT THE I/O INTERFACE

## 2.7.1 SPI

When enabled, the SPI interface is implemented with four pins:

- CS

- SO

- SI

- SCK

All four of these pins must be connected to use the SPI interface

The  $\overline{\text{CS}}$ , SI and SCK input pins are 5V tolerant. The SO pin is also 5V tolerant when in a high-impedance state. SO is always high-impedance when  $\overline{\text{CS}}$  is connected to logic high (i.e., chip not selected).

When the SPI interface is enabled, all PSP interface pins (except PSPCFG2 and PSPCFG3 on ENC624J600 devices) are unused. They are placed in a high-impedance state and their input buffers are disabled. For best ESD performance, it is recommended that the unused PSP pins be tied to either Vss or VDD. However, these pins may be left floating if it is desirable for board level layout and routing reasons.

When using an ENC624J600 device in SPI mode, it is recommended that the PSPCFG2 and PSPCFG3 pins be tied to either Vss or any logic high voltage, and not be left floating. The particular state used is unimportant.

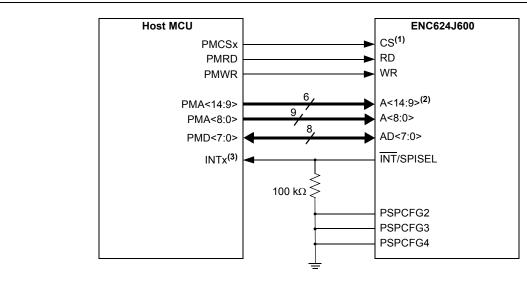

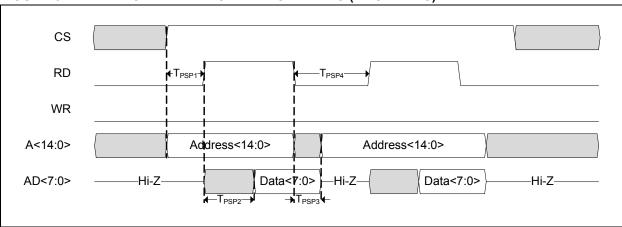

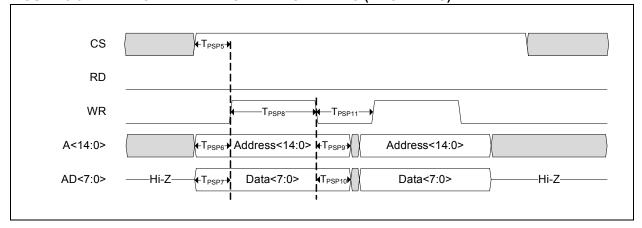

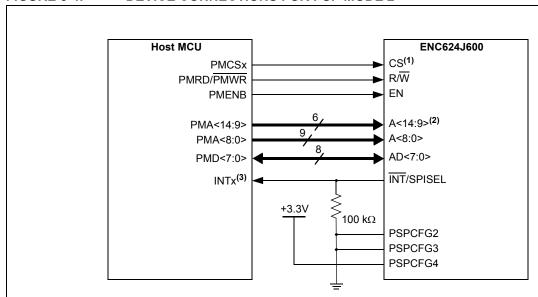

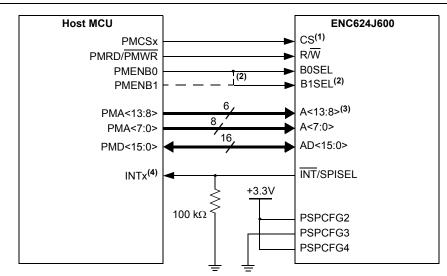

## 2.7.2 PSP

Depending on the particular device, the PSP interface is implemented with up to 34 pins. The interface is highly configurable to accommodate many different

parallel interfaces; not all available pins are used in every configuration. Up to 8 different operating modes are available. These are explained in detail in Section 5.0 "Parallel Slave Port Interface (PSP)".

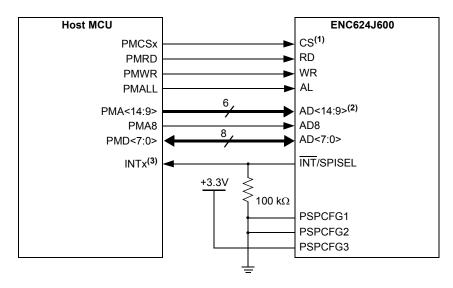

The PSPCFG pins control which parallel interface mode is used. The values on these pins are latched upon device power-up in the same manner as the SPISEL pin. The combinations of VDD and Vss voltages on the different PSPCFG mode pins determine the PSP mode according to Table 2-1.

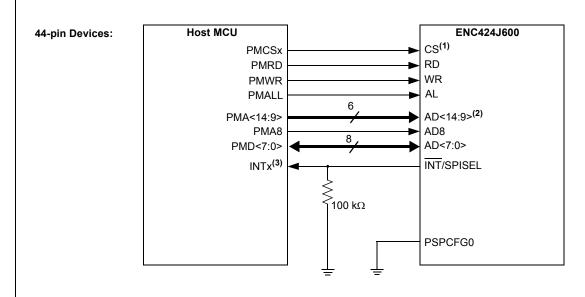

On ENC424J600 devices, only PSP Modes 5 and 6 (8-bit width, multiplexed data and address) are available. The mode is selected by applying Vss or VDD, respectively, to PSPCFG0.

On ENC624J600 devices, all eight PSP modes are available and are selected by connecting the PSPCFG<4:1> pins directly to VDD or ground. The mode selection is encoded such that the multiplexed pin functions, AD14 (on PSPCFG1) and SCK/AL (on PSPCFG4), are used only in the "don't care" positions. Therefore, pull-up/pull-down resistors are not required for these pins.

All PSP pins, except for AD<15:0>, are inputs to the ENC624J600 family device and are 5V tolerant. The AD<15:0> pins are bidirectional I/Os and are 5V tolerant in Input mode. The pins are always inputs when the CS signal is low (chip not selected).

Any unused PSP pins are placed in a high-impedance state. However, it is recommended that they be tied to either Vss or a logic high voltage and not be left floating.

TABLE 2-1: PSP MODE SELECTION FOR ENC424J600/624J600 DEVICES

| Interface<br>Mode | <del>INT</del> (ODIOE) | PSPCFG |   |   |   |      | Divo Hood                               |  |  |

|-------------------|------------------------|--------|---|---|---|------|-----------------------------------------|--|--|

|                   | INT/SPISEL             | 0      | 1 | 2 | 3 | 4    | Pins Used                               |  |  |

| 44-Pin            |                        |        |   |   |   |      |                                         |  |  |

| PSP Mode 5        | Pull Down              | 0      | _ | _ | _ | _    | AL, CS, RD, WR, AD<14:0>                |  |  |

| PSP Mode 6        | Pull Down              | 1      | _ | _ | _ | _    | AL, CS, RW, EN, AD<14:0>                |  |  |

|                   |                        |        |   |   |   | 64-P | in                                      |  |  |

| PSP Mode 1        | Pull Down              | _      | х | 0 | 0 | 0    | CS, RD, WR, A14:A0, AD<7:0>             |  |  |

| PSP Mode 2        | Pull Down              | _      | х | 0 | 0 | 1    | CS, RW, EN, A14:A0, AD<7:0>             |  |  |

| PSP Mode 3        | Pull Down              | _      | х | 1 | 0 | 0    | CS, RD, WRL, WRH, A<13:0>, AD<15:0>     |  |  |

| PSP Mode 4        | Pull Down              | _      | х | 1 | 0 | 1    | CS, RW, B0SEL, B1SEL, A<13:0>, AD<15:0> |  |  |

| PSP Mode 5        | Pull Down              | _      | 0 | 0 | 1 | х    | AL, CS, RD, WR, AD<14:0>                |  |  |

| PSP Mode 6        | Pull Down              | ı      | 1 | 0 | 1 | х    | AL, CS, RW, EN, AD<14:0>                |  |  |

| PSP Mode 9        | Pull Down              | -      | 0 | 1 | 1 | х    | AL, CS, RD, WRL, WRH, AD<15:0>          |  |  |

| PSP Mode 10       | Pull Down              | _      | 1 | 1 | 1 | х    | AL, CS, RW, B0SEL, B1SEL, AD<15:0>      |  |  |

Legend: x = don't care, 0 = logic low (tied to Vss), 1 = logic high (tied to VDD), — = pin not present

## 2.7.3 CS/CS PIN

The chip select functions for the serial and parallel interfaces are shared on one common pin,  $\overline{\text{CS}}/\text{CS}$ . This pin is equipped with both internal weak pull-up and weak pull-down resistors. If the SPI interface is selected  $(\overline{\text{CS}})$ , the pull-up resistor is automatically enabled and the pull-down resistor is disabled. If the PSP interface is chosen (CS), the pull-down resistor is automatically enabled and the pull-up resistor is disabled. This allows the  $\overline{\text{CS}}/\text{CS}$  pin to stay in the unselected state when not being driven, avoiding the need for an external board level resistor on this pin.

When enabled by using SPI mode, the internal weak pull-up only pulls the  $\overline{\text{CS}}/\text{CS}$  pin up to approximately VDD-1.1V or around 2.2V at typical conditions without any loading; it does not pull all the way to VDD. When using the PSP interface, the pull-down will be enabled, which is capable of pulling all the way to VSS when unloaded.

## 2.8 Digital I/O Levels

All digital output pins on ENC424J600/624J600 devices contain CMOS output drivers that are capable of sinking and sourcing up to 18 mA continuously. All digital inputs and I/O pins operating as inputs are 5V tolerant. These features generally mean that the ENCX24J600 can connect directly to the host microcontroller without the need of any glue logic. However, some consideration may be necessary when interfacing with 5V systems.

Since the digital outputs drive only up to the VDD voltage (3.3V nominally), the voltage may not be high enough to ensure a logical high is detected by 5V systems which have high input thresholds. In such cases, unidirectional level translation from the 3.3V ENCX24J600 up to the 5V host microcontroller may be needed.

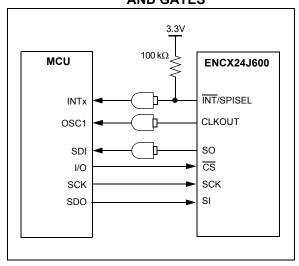

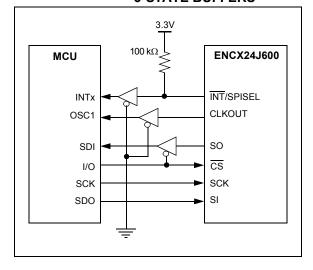

When using the SPI interface, an economical 74HCT08 (quad AND gate), 74ACT125 (quad 3-state buffer) or other 5V CMOS chip with TTL level input buffers may be used to provide the necessary level shifting. The use of 3-state buffers permits easy integration into systems which share the SPI bus with other devices. However, users must make certain that the propagation delay of the level translator does not reduce the maximum SPI frequency below desired levels. Figure 2-10 and Figure 2-11 show two example translation schemes.

When using the PSP interface, eight, or all sixteen of the ADx pins, may need level translation when performing read operations on the ENCX24J600. The 8-bit 74ACT245 or 16-bit 74ACT16245 bus transceiver, or similar devices, may be useful in these situations.

FIGURE 2-10: LEVEL SHIFTING ON THE SPI INTERFACE USING AND GATES

FIGURE 2-11: LEVEL SHIFTING ON THE SPI INTERFACE USING 3-STATE BUFFERS

NOTES:

#### 3.0 MEMORY ORGANIZATION

All memory in ENC424J600/624J600 devices is implemented as volatile RAM. Functionally, there are four unique memories:

- Special Function Registers (SFRs)

- PHY Special Function Registers

- · Cryptographic Data Memory

- · SRAM Buffer

The SFRs configure, control and provide status information for most of the device. They are directly accessible through the I/O interface.

The PHY SFRs configure, control and provide status information for the PHY module. They are located inside the PHY module and isolated from all other normal SFRs, so they are not directly accessible through the I/O interface.

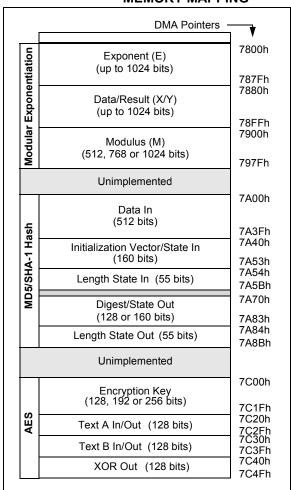

The cryptography data memory is used to store key and data material for the modular exponentiation. AES and MD5/SHA-1 hashing engines. This memory area can only be accessed through the DMA module.

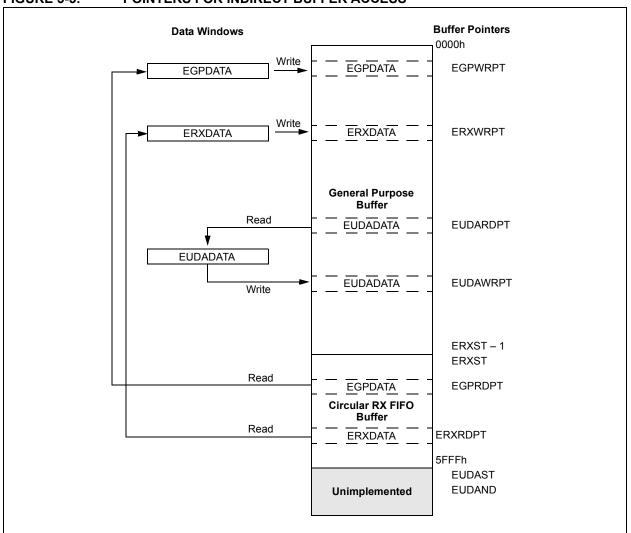

The SRAM buffer is a bulk 12K x 16-bit (24 Kbyte) RAM array used for TX and RX packet buffering, as well as general purpose storage by the host microcontroller. Although the SRAM uses a 16-bit word, it is byte-writable. This memory is indirectly accessible through pointers on all I/O interfaces. It can also be accessed directly through the PSP interfaces.

#### 3.1 I/O Interface and Memory Map

Depending on the I/O interface selected, the four memories are arranged into two or three different memory address spaces. When the serial interface is selected, the memories are grouped into three address spaces. When one of the parallel interfaces is selected, they are arranged into two address spaces. In all cases, the PHY SFRs reside in their own memory address space.

#### 3.1.1 SPI INTERFACE MAP

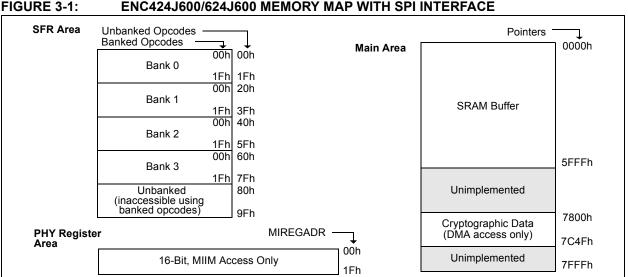

When the SPI interface is selected, the device memory map is comprised of three memory address spaces (Figure ):

- · the SFR area

- · the main memory area

- · the PHY register area

The SFR area is directly accessible to the user. This is a linear memory space that is 160 bytes long. For efficiency, the SFR area can be addressed as four banks of 32 bytes each, starting at the beginning of the space (00h), with an additional unbanked area of 32 bytes at the end of the SFR memory. Banked addressing allows SFRs to be addressed with fewer address bits being exchanged over the serial interface for each transaction. This decreases protocol overhead and enhances performance. SFRs can also be directly addressed by their 8-bit unbanked addresses using unbanked SPI commands. This allows for a simpler interface whenever transaction overhead is not critical.

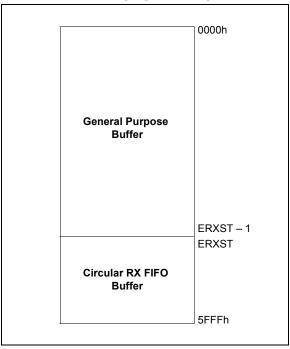

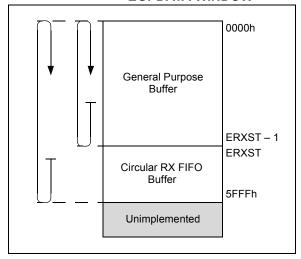

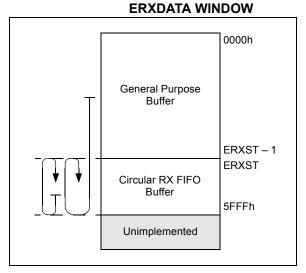

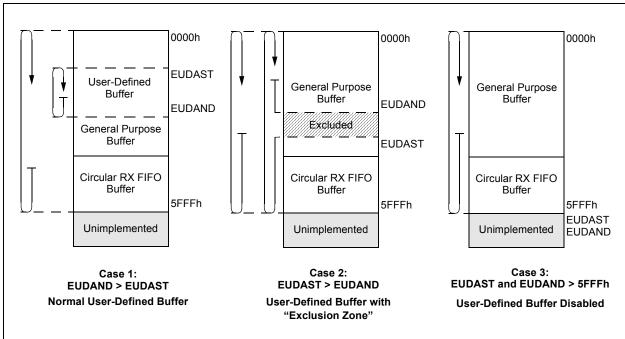

The main memory area is organized as a linear, byte-addressable space of 32 Kbytes. Of this, the first 24-Kbyte area (0000h through 5FFFh) is implemented as the SRAM buffer. The buffer is accessed by the device using several SFRs as memory pointers and virtual data window registers, as described in Section 3.5.5 "Indirect SRAM Buffer Access".

Addresses in the main memory area, between 7800h and 7C4Fh, are mapped to the memory for the cryptographic data modules. These addresses are not directly accessible through the SPI interface; they can only be accessed through the DMA.

The PHY SFRs are the final memory space. This is a linear, word-addressable memory space of 32 words. This area is only accessible by the MIIM interface (see Section 3.3 "PHY Special Function Registers" for more details).

### 3.1.2 PSP INTERFACE MAPS

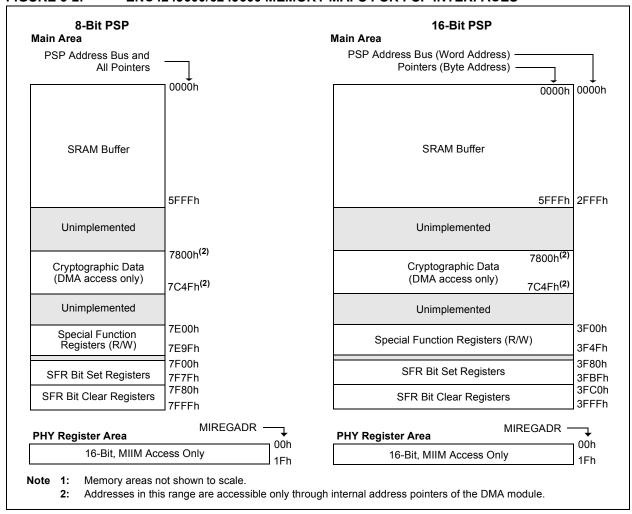

When one of the parallel interfaces is selected, the memory map is very different from the SPI map. There are two different memory address spaces (Figure 3-2):

- · the main memory area

- · the PHY register area

As in the serial memory map, the main memory area is a linear, byte-addressable space of 32 Kbytes, with the SRAM buffer located in the first 24-Kbyte region. The cryptographic data memory is also mapped to the same location as in the serial memory map. The main difference is that the SFRs are now located to an area with a higher address than the cryptographic data space. Additional memory areas above the SFRs are reserved for their accompanying Bit Set and Bit Clear registers.

Except for the cryptographic data memory, all addresses in the main memory area are directly accessible using the PSP bus. As with the serial interface, the cryptographic memory can only be accessed through the DMA.

The difference between the 8-bit and 16-bit interfaces is how the SRAM buffer is addressed by the external address bus. In 16-bit data modes, the address bus treats the buffer as a 16-byte wide, word-addressable space, spanning 000h to 3FFFh. In 8-bit data modes, the address bus treats the buffer as an 8-bit, byte-addressable space, ranging from 0000h to 7FFFh. In either case, the SFRs used as memory pointers still address the buffer as a byte-wide, byte-addressable space.

The PHY SFR space is implemented in the same manner as the SPI interface described above.

In both 8-bit and 16-bit PSP modes, full device functionality can be realized without using the full width of the address bus. This is because the SRAM buffer can still be read and written to by using SFR pointers. In practical terms, this can allow designers in space or pin constrained applications to only connect a subset of the A or AD address pins to the host microcontroller. For example, in the 8-Bit Multiplexed PSP Modes 5 or 6, tying pins, AD<14:9> to VDD, still allows direct address access to all SFRs. This reduces the number of pins required for connection to the host controller, including the interface control pins to 12 or 13.

FIGURE 3-2: ENC424J600/624J600 MEMORY MAPS FOR PSP INTERFACES<sup>(1)</sup>

## 3.2 Special Function Registers

The SFRs provide the main interface between the host controller and the on-chip Ethernet controller logic. Writing to these registers controls the operation of the interface, while reading the registers allows the host controller to monitor operations.

All registers are 16 bits wide. On the SPI and 8-bit PSP interfaces, which are inherently byte-oriented, the registers are split into separate high and low locations which are designated by an "H" or "L" suffix, respectively. All registers are organized in little-endian format such that the low byte is always at the lower memory address.

Some of the available addresses are unimplemented or marked as reserved. These locations should not be written to. Data read from reserved locations should be ignored. Reading from unimplemented locations will return '0'. When reading and writing to registers which contain reserved bits, any rules stated in the register definition should be observed.

The addresses of all user-accessible registers are provided in Tables 3-1 through 3-6. A complete bit level listing of the SFRs is presented in Table 3-7 (page 26).

## 3.2.1 E REGISTERS

SFRs with names starting with "E" are the primary control and pointer registers. They configure and control all of the (non-MAC) top-level features of the device, as well as manipulate the pointers that define the memory buffers. These registers can be read and written in any order, with any length, without concern for address alignment.

## 3.2.2 MAC REGISTERS

SFRs with names that start with "MA" or "MI" are implemented in the MAC module hardware. For this reason, their operation differs from "E" registers in two ways.

First, MAC registers support read and write operations only. Individual bit set and bit clear operations cannot be performed.

Additionally, MAC registers must always be written as a 16-bit word, regardless of the I/O interface being used. That is, on the SPI or 8-bit PSP interfaces, all write operations must be performed by writing to the low byte, followed by a write to the associated high byte. On 16-bit PSP interfaces, both write enables or byte selects must be asserted to perform the 16-bit write. Non-sequential writes, such as writing to the low byte of one MAC register, the low byte of a second MAC register and then the high byte of the first register cannot be performed.

### 3.2.3 SPI REGISTER MAP

As previously described, the SFR memory is partitioned into four banks plus a special region that is not bank addressable. Each bank is 32 bytes long and addressed by a 5-bit address value. All SFR memory may also be accessed via unbanked SPI opcodes which use a full 8-bit address to form a linear address map without banking.

The last 10 bytes (16h to 1Fh) of all SPI banks point to a common set of five registers: EUDAST, EUDAND, ESTAT, EIR and ECON1. These are key registers used in controlling and monitoring the operation of the device. Their common banked addresses allow easy access without switching the bank.

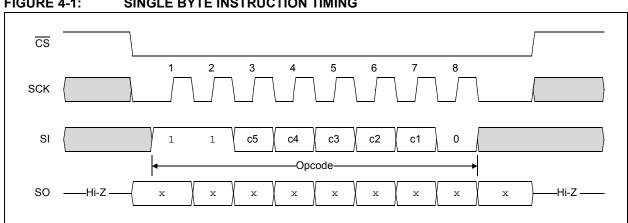

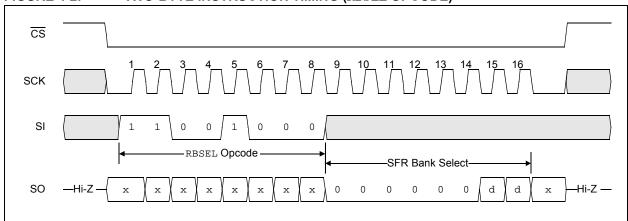

The SPI interface implements a comprehensive instruction set that allows for reading and writing of registers, as well as setting and clearing individual bits or bit fields within registers. The SPI instruction set is explained in detail in **Section 4.0 "Serial Peripheral Interface (SPI)"**.

The SFR map for the SPI interface is shown in Table 3-1. Registers are presented by a bank. The banked (5-bit) address applicable to the registers in each row is shown in the left most column. The unbanked (8-bit) address for each register is shown to the immediate left of the register name.

Note: SFRs in the unbanked region (80h through 9Fh) cannot be accessed using banked addressing. The use of an unbanked SFR opcode is required to perform operations on these registers.

TABLE 3-1: ENC424J600/624J600 SFR MAP (SPI INTERFACE)

| gister                       | Bank 0<br>(00h offset) |          |                     |          | (                   | Bank 2<br>(40h offset) |                                   | Bank 3<br>60h offset) |                     | Unbanked <sup>(1)</sup><br>(80h offset) |  |

|------------------------------|------------------------|----------|---------------------|----------|---------------------|------------------------|-----------------------------------|-----------------------|---------------------|-----------------------------------------|--|

| Banked Register<br>Addresses | Unbanked<br>Address    | Name     | Unbanked<br>Address | Name     | Unbanked<br>Address | Name                   | <b>Unbanked</b><br><b>Address</b> | Name                  | Unbanked<br>Address | Name                                    |  |

| 00                           | 00                     | ETXSTL   | 20                  | EHT1L    | 40                  | MACON1L                | 60                                | MAADR3L               | 80                  | EGPDATA <sup>(2)</sup>                  |  |

| 01                           | 01                     | ETXSTH   | 21                  | EHT1H    | 41                  | MACON1H                | 61                                | MAADR3H               | 81                  | Reserved                                |  |

| 02                           | 02                     | ETXLENL  | 22                  | EHT2L    | 42                  | MACON2L                | 62                                | MAADR2L               | 82                  | ERXDATA <sup>(2)</sup>                  |  |

| 03                           | 03                     | ETXLENH  | 23                  | EHT2H    | 43                  | MACON2H                | 63                                | MAADR2H               | 83                  | Reserved                                |  |

| 04                           | 04                     | ERXSTL   | 24                  | EHT3L    | 44                  | MABBIPGL               | 64                                | MAADR1L               | 84                  | EUDADATA <sup>(2)</sup>                 |  |

| 05                           | 05                     | ERXSTH   | 25                  | EHT3H    | 45                  | MABBIPGH               | 65                                | MAADR1H               | 85                  | Reserved                                |  |

| 06                           | 06                     | ERXTAILL | 26                  | EHT4L    | 46                  | MAIPGL                 | 66                                | MIWRL                 | 86                  | EGPRDPTL                                |  |

| 07                           | 07                     | ERXTAILH | 27                  | EHT4H    | 47                  | MAIPGH                 | 67                                | MIWRH                 | 87                  | EGPRDPTH                                |  |

| 08                           | 08                     | ERXHEADL | 28                  | EPMM1L   | 48                  | MACLCONL               | 68                                | MIRDL                 | 88                  | EGPWRPTL                                |  |

| 09                           | 09                     | ERXHEADH | 29                  | EPMM1H   | 49                  | MACLCONH               | 69                                | MIRDH                 | 89                  | EGPWRPTH                                |  |

| 0A                           | 0A                     | EDMASTL  | 2A                  | EPMM2L   | 4A                  | MAMXFLL                | 6A                                | MISTATL               | 8A                  | ERXRDPTL                                |  |

| 0B                           | 0B                     | EDMASTH  | 2B                  | EPMM2H   | 4B                  | MAMXFLH                | 6B                                | MISTATH               | 8B                  | ERXRDPTH                                |  |

| 0C                           | 0C                     | EDMALENL | 2C                  | EPMM3L   | 4C                  | Reserved               | 6C                                | EPAUSL                | 8C                  | ERXWRPTL                                |  |

| 0D                           | 0D                     | EDMALENH | 2D                  | EPMM3H   | 4D                  | Reserved               | 6D                                | EPAUSH                | 8D                  | ERXWRPTH                                |  |

| 0E                           | 0E                     | EDMADSTL | 2E                  | EPMM4L   | 4E                  | Reserved               | 6E                                | ECON2L                | 8E                  | EUDARDPTL                               |  |

| 0F                           | 0F                     | EDMADSTH | 2F                  | EPMM4H   | 4F                  | Reserved               | 6F                                | ECON2H                | 8F                  | EUDARDPTH                               |  |

| 10                           | 10                     | EDMACSL  | 30                  | EPMCSL   | 50                  | Reserved               | 70                                | ERXWML                | 90                  | EUDAWRPTL                               |  |

| 11                           | 11                     | EDMACSH  | 31                  | EPMCSH   | 51                  | Reserved               | 71                                | ERXWMH                | 91                  | EUDAWRPTH                               |  |

| 12                           | 12                     | ETXSTATL | 32                  | EPMOL    | 52                  | MICMDL                 | 72                                | EIEL                  | 92                  | Reserved                                |  |

| 13                           | 13                     | ETXSTATH | 33                  | EPMOH    | 53                  | MICMDH                 | 73                                | EIEH                  | 93                  | Reserved                                |  |

| 14                           | 14                     | ETXWIREL | 34                  | ERXFCONL | 54                  | MIREGADRL              | 74                                | EIDLEDL               | 94                  | Reserved                                |  |

| 15                           | 15                     | ETXWIREH | 35                  | ERXFCONH | 55                  | MIREGADRH              | 75                                | EIDLEDH               | 95                  | Reserved                                |  |

| 16                           | 16                     | EUDASTL  | 36                  | EUDASTL  | 56                  | EUDASTL                | 76                                | EUDASTL               | 96                  | Reserved                                |  |

| 17                           | 17                     | EUDASTH  | 37                  | EUDASTH  | 57                  | EUDASTH                | 77                                | EUDASTH               | 97                  | Reserved                                |  |

| 18                           | 18                     | EUDANDL  | 38                  | EUDANDL  | 58                  | EUDANDL                | 78                                | EUDANDL               | 98                  | Reserved                                |  |

| 19                           | 19                     | EUDANDH  | 39                  | EUDANDH  | 59                  | EUDANDH                | 79                                | EUDANDH               | 99                  | Reserved                                |  |

| 1A                           | 1A                     | ESTATL   | 3A                  | ESTATL   | 5A                  | ESTATL                 | 7A                                | ESTATL                | 9A                  | Reserved                                |  |

| 1B                           | 1B                     | ESTATH   | 3B                  | ESTATH   | 5B                  | ESTATH                 | 7B                                | ESTATH                | 9B                  | Reserved                                |  |

| 1C                           | 1C                     | EIRL     | 3C                  | EIRL     | 5C                  | EIRL                   | 7C                                | EIRL                  | 9C                  | Reserved                                |  |

| 1D                           | 1D                     | EIRH     | 3D                  | EIRH     | 5D                  | EIRH                   | 7D                                | EIRH                  | 9D                  | Reserved                                |  |

| 1E                           | 1E                     | ECON1L   | 3E                  | ECON1L   | 5E                  | ECON1L                 | 7E                                | ECON1L                | 9E                  | _                                       |  |

| 1F                           | 1F                     | ECON1H   | 3F                  | ECON1H   | 5F                  | ECON1H                 | 7F                                | ECON1H                | 9F                  | _                                       |  |

Note 1: Unbanked SFRs can be accessed only by unbanked SPI opcodes.

<sup>2:</sup> When using these registers to access the SRAM buffer, use only the N-byte SRAM instructions. See Section 4.6.2 "Unbanked SFR Operations" and Section 4.6.3 "SRAM Buffer Operations" for more details.

## 3.2.4 PSP REGISTER MAP

When using a PSP interface, the SFR memory is linear; all registers are directly accessible without banking. To maintain consistency with the SPI interface, the EUDAST, EUDAND, ESTAT, EIR and ECON1 registers are instantiated in four locations in the PSP memory maps. Users may opt to use any one of these four locations.

The SFR maps for the 8-bit and 16-bit PSP interfaces are shown in Table 3-2 and Table 3-3, respectively.

TABLE 3-2: ENC424J600/624J600 SFR MAP (BASE REGISTER MAP, 8-BIT PSP INTERFACE)

| Addr | Name     |

|------|----------|

| 7E00 | ETXSTL   |

| 7E01 | ETXSTH   |

| 7E02 | ETXLENL  |

| 7E03 | ETXLENH  |

| 7E04 | ERXSTL   |

| 7E05 | ERXSTH   |

| 7E06 | ERXTAILL |

| 7E07 | ERXTAILH |

| 7E08 | ERXHEADL |

| 7E09 | ERXHEADH |

| 7E0A | EDMASTL  |

| 7E0B | EDMASTH  |

| 7E0C | EDMALENL |

| 7E0D | EDMALENH |

| 7E0E | EDMADSTL |

| 7E0F | EDMADSTH |

| 7E10 | EDMACSL  |

| 7E11 | EDMACSH  |

| 7E12 | ETXSTATL |

| 7E13 | ETXSTATH |

| 7E14 | ETXWIREL |

| 7E15 | ETXWIREH |

| 7E16 | EUDASTL  |

| 7E17 | EUDASTH  |

| 7E18 | EUDANDL  |

| 7E19 | EUDANDH  |

| 7E1A | ESTATL   |

| 7E1B | ESTATH   |

| 7E1C | EIRL     |

| 7E1D | EIRH     |

| 7E1E | ECON1L   |

| 7E1F | ECON1H   |

| Addr | Name     |

|------|----------|

| 7E20 | EHT1L    |

| 7E21 | EHT1H    |

| 7E22 | EHT2L    |

| 7E23 | EHT2H    |

| 7E24 | EHT3L    |

| 7E25 | EHT3H    |

| 7E26 | EHT4L    |

| 7E27 | EHT4H    |

| 7E28 | EPMM1L   |

| 7E29 | EPMM1H   |

| 7E2A | EPMM2L   |

| 7E2B | EPMM2H   |

| 7E2C | EPMM3L   |

| 7E2D | EPMM3H   |

| 7E2E | EPMM4L   |

| 7E2F | EPMM4H   |

| 7E30 | EPMCSL   |

| 7E31 | EPMCSH   |

| 7E32 | EPMOL    |

| 7E33 | EPMOH    |

| 7E34 | ERXFCONL |

| 7E35 | ERXFCONH |

| 7E36 | EUDASTL  |

| 7E37 | EUDASTH  |

| 7E38 | EUDANDL  |

| 7E39 | EUDANDH  |

| 7E3A | ESTATL   |

| 7E3B | ESTATH   |

| 7E3C | EIRL     |

| 7E3D | EIRH     |

| 7E3E | ECON1L   |

| 7E3F | ECON1H   |

| Addr | Name      |

|------|-----------|

| 7E40 | MACON1L   |

| 7E41 | MACON1H   |

| 7E42 | MACON2L   |

| 7E43 | MACON2H   |

| 7E44 | MABBIPGL  |

| 7E45 | MABBIPGH  |

| 7E46 | MAIPGL    |

| 7E47 | MAIPGH    |

| 7E48 | MACLCONL  |

| 7E49 | MACLCONH  |

| 7E4A | MAMXFLL   |

| 7E4B | MAMXFLH   |

| 7E4C | Reserved  |

| 7E4D | Reserved  |

| 7E4E | Reserved  |

| 7E4F | Reserved  |

| 7E50 | Reserved  |

| 7E51 | Reserved  |

| 7E52 | MICMDL    |

| 7E53 | MICMDH    |

| 7E54 | MIREGADRL |

| 7E55 | MIREGADRH |

| 7E56 | EUDASTL   |

| 7E57 | EUDASTH   |

| 7E58 | EUDANDL   |

| 7E59 | EUDANDH   |

| 7E5A | ESTATL    |

| 7E5B | ESTATH    |

| 7E5C | EIRL      |

| 7E5D | EIRH      |

| 7E5E | ECON1L    |

| 7E5F | ECON1H    |

| Addr | Name    |

|------|---------|

| 7E60 | MAADR3L |

| 7E61 | MAADR3H |

| 7E62 | MAADR2L |

| 7E63 | MAADR2H |

| 7E64 | MAADR1L |

| 7E65 | MAADR1H |

| 7E66 | MIWRL   |

| 7E67 | MIWRH   |

| 7E68 | MIRDL   |

| 7E69 | MIRDH   |

| 7E6A | MISTATL |

| 7E6B | MISTATH |

| 7E6C | EPAUSL  |

| 7E6D | EPAUSH  |

| 7E6E | ECON2L  |

| 7E6F | ECON2H  |

| 7E70 | ERXWML  |

| 7E71 | ERXWMH  |

| 7E72 | EIEL    |

| 7E73 | EIEH    |

| 7E74 | EIDLEDL |

| 7E75 | EIDLEDH |

| 7E76 | EUDASTL |

| 7E77 | EUDASTH |

| 7E78 | EUDANDL |

| 7E79 | EUDANDH |

| 7E7A | ESTATL  |

| 7E7B | ESTATH  |

| 7E7C | EIRL    |

| 7E7D | EIRH    |

| 7E7E | ECON1L  |

| 7E7F | ECON1H  |

| SP INTE | RFACE)    |

|---------|-----------|

| Addr    | Name      |

| 7E80    | EGPDATA   |

| 7E81    | Reserved  |

| 7E82    | ERXDATA   |

| 7E83    | Reserved  |

| 7E84    | EUDADATA  |

| 7E85    | Reserved  |

| 7E86    | EGPRDPTL  |

| 7E87    | EGPRDPTH  |

| 7E88    | EGPWRPTL  |

| 7E89    | EGPWRPTH  |

| 7E8A    | ERXRDPTL  |

| 7E8B    | ERXRDPTH  |

| 7E8C    | ERXWRPTL  |

| 7E8D    | ERXWRPTH  |

| 7E8E    | EUDARDPTL |

| 7E8F    | EUDARDPTH |

| 7E90    | EUDAWRPTL |

| 7E91    | EUDAWRPTH |

| 7E92    | Reserved  |

| 7E93    | Reserved  |

| 7E94    | Reserved  |

| 7E95    | Reserved  |

| 7E96    | Reserved  |

| 7E97    | Reserved  |

| 7E98    | Reserved  |

| 7E99    | Reserved  |

| 7E9A    | Reserved  |

| 7E9B    | Reserved  |

| 7E9C    | Reserved  |

| 7E9D    | Reserved  |

| 7E9E    | _         |

| 7E9F    | _         |

|         |           |

TABLE 3-3: ENC424J600/624J600 SFR MAP (BASE REGISTER MAP, 16-BIT PSP INTERFACE)

| IADL | L 0-0. LIV |  |  |  |  |

|------|------------|--|--|--|--|

| Addr | Name       |  |  |  |  |

| 3F00 | ETXST      |  |  |  |  |

| 3F01 | ETXLEN     |  |  |  |  |

| 3F02 | ERXST      |  |  |  |  |

| 3F03 | ERXTAIL    |  |  |  |  |

| 3F04 | ERXHEAD    |  |  |  |  |

| 3F05 | EDMAST     |  |  |  |  |

| 3F06 | EDMALEN    |  |  |  |  |

| 3F07 | EDMADST    |  |  |  |  |

| 3F08 | EDMACS     |  |  |  |  |

| 3F09 | ETXSTAT    |  |  |  |  |

| 3F0A | ETXWIRE    |  |  |  |  |

| 3F0B | EUDAST     |  |  |  |  |

| 3F0C | EUDAND     |  |  |  |  |

| 3F0D | ESTAT      |  |  |  |  |

| 3F0E | EIR        |  |  |  |  |

| 3F0F | ECON1      |  |  |  |  |

|      | -2-0000/02-0000 0 |  |  |  |  |  |  |  |  |  |  |

|------|-------------------|--|--|--|--|--|--|--|--|--|--|

| Addr | Name              |  |  |  |  |  |  |  |  |  |  |

| 3F10 | EHT1              |  |  |  |  |  |  |  |  |  |  |

| 3F11 | EHT2              |  |  |  |  |  |  |  |  |  |  |

| 3F12 | EHT3              |  |  |  |  |  |  |  |  |  |  |

| 3F13 | EHT4              |  |  |  |  |  |  |  |  |  |  |

| 3F14 | EPMM1             |  |  |  |  |  |  |  |  |  |  |

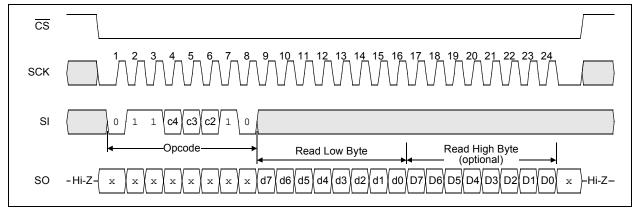

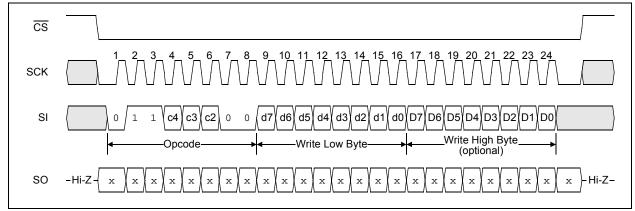

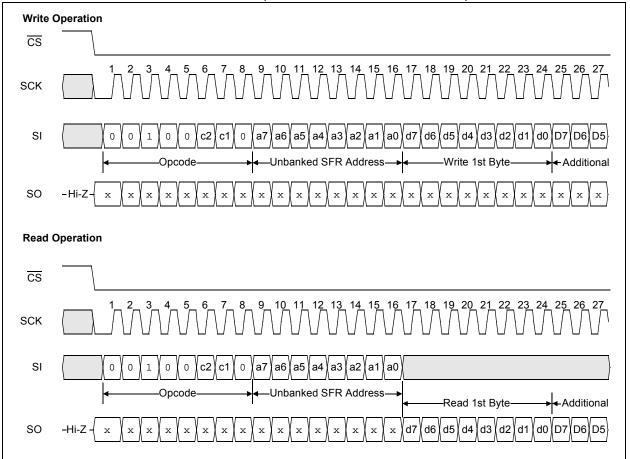

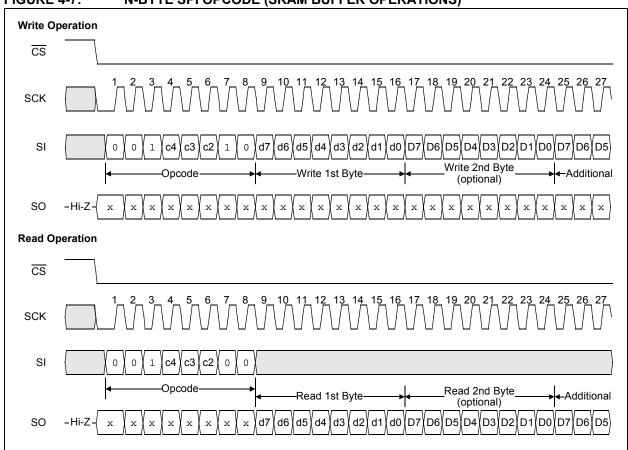

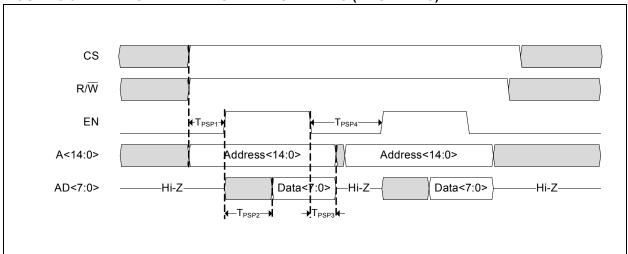

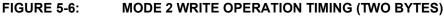

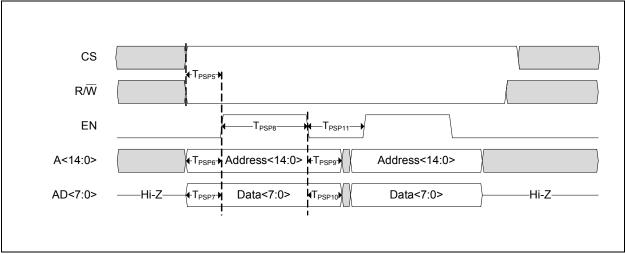

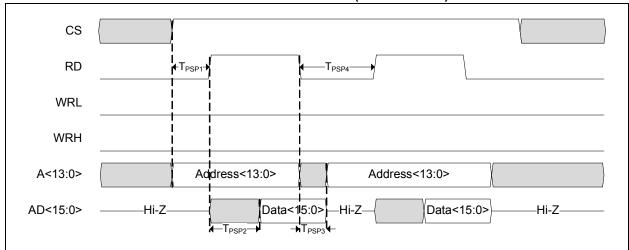

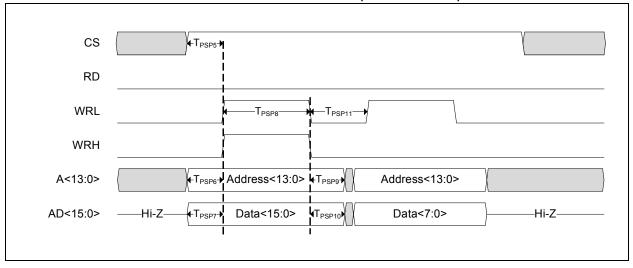

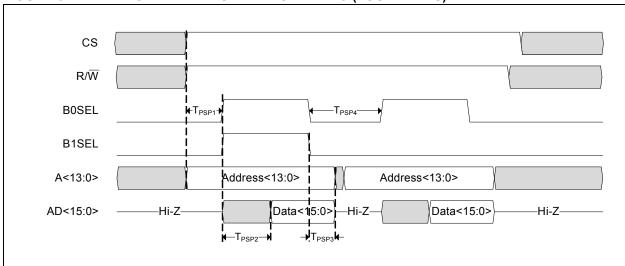

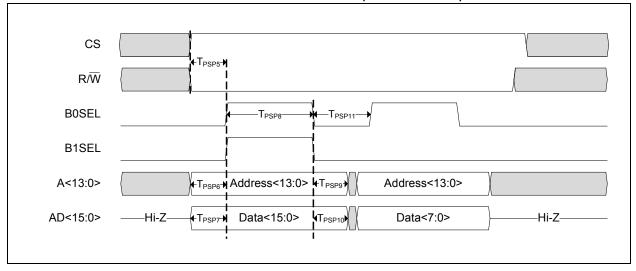

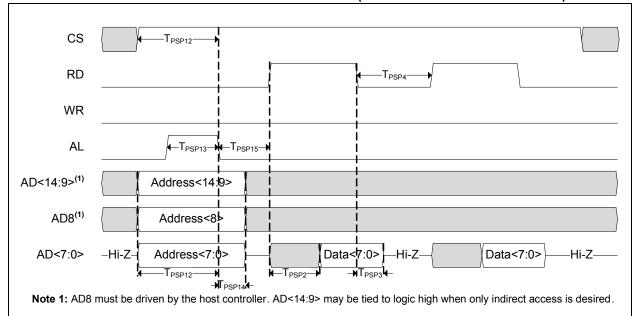

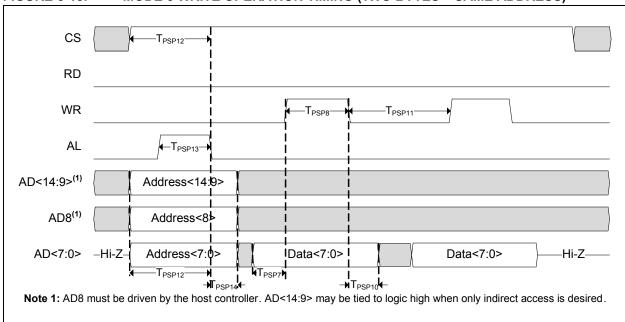

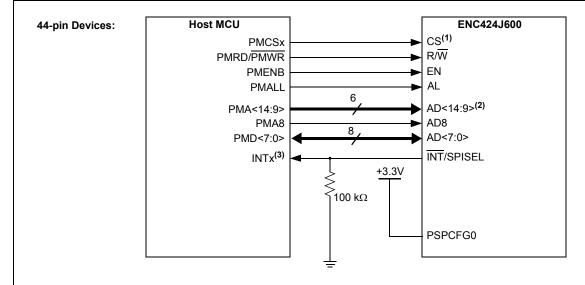

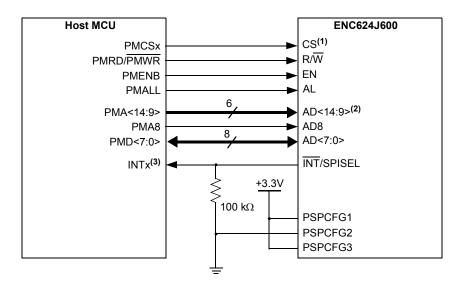

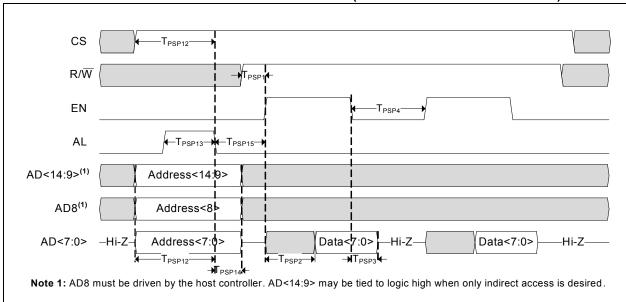

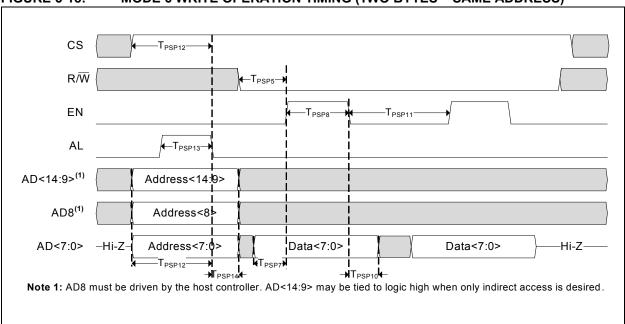

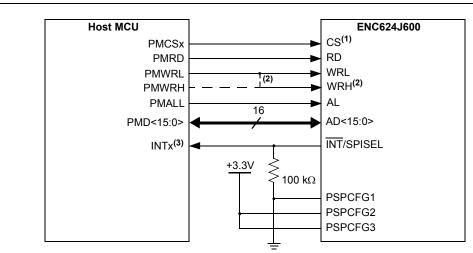

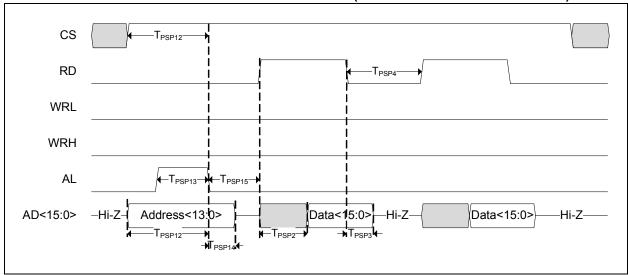

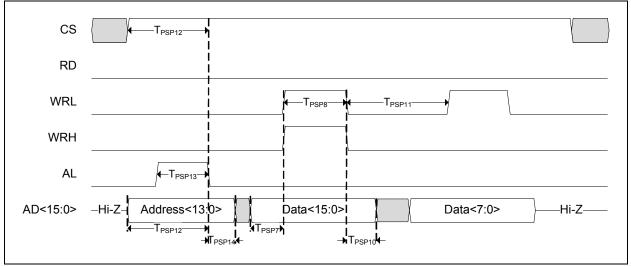

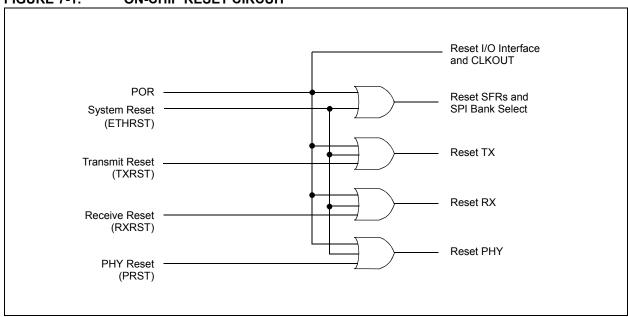

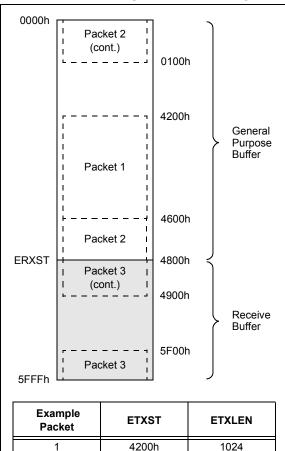

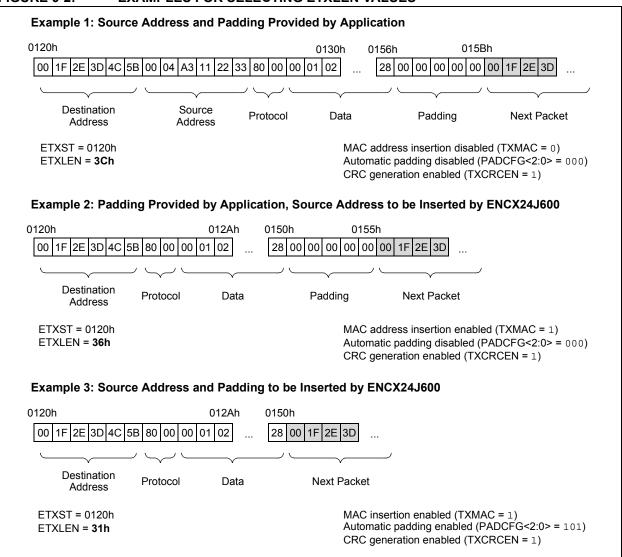

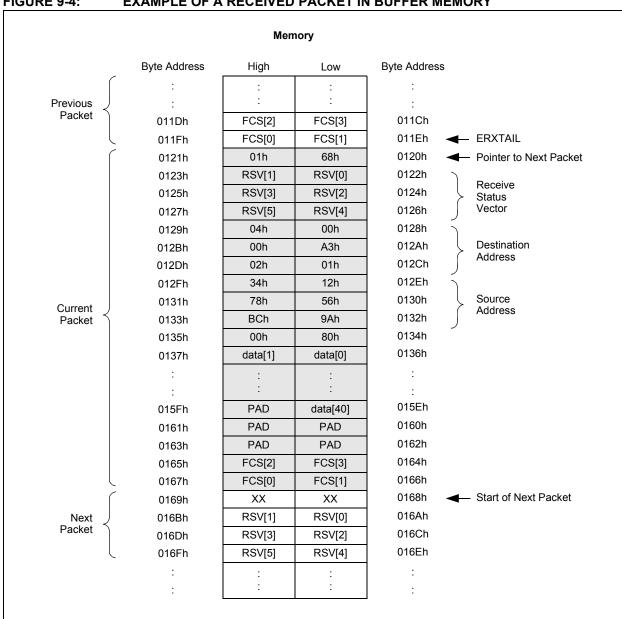

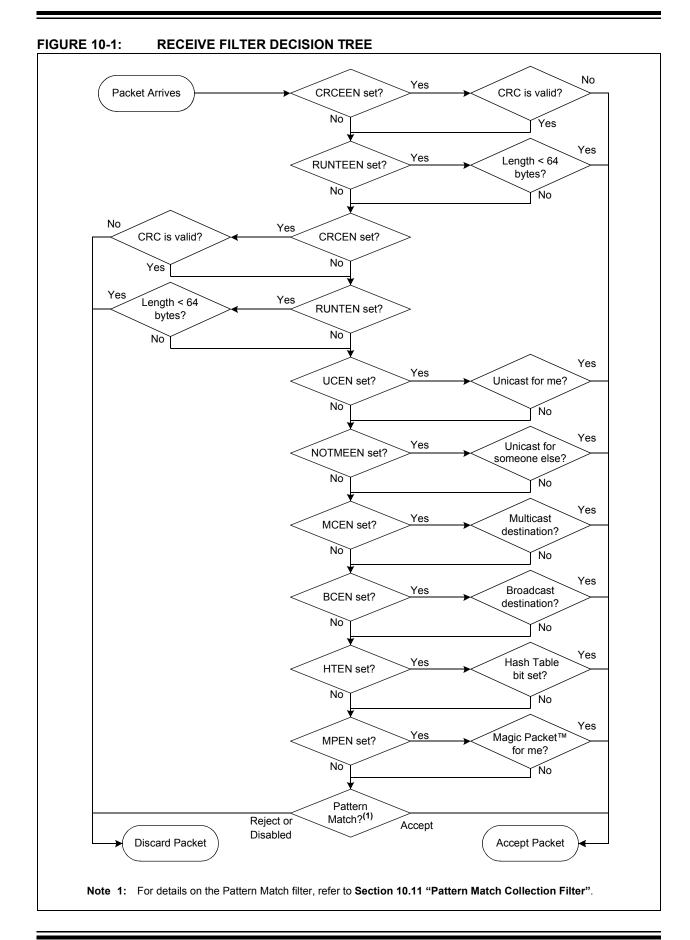

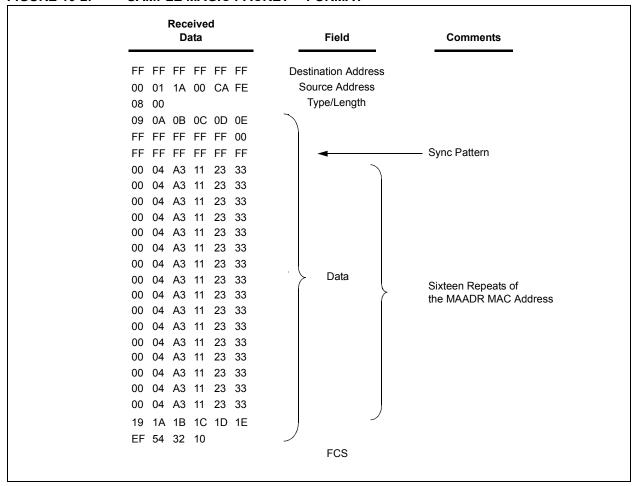

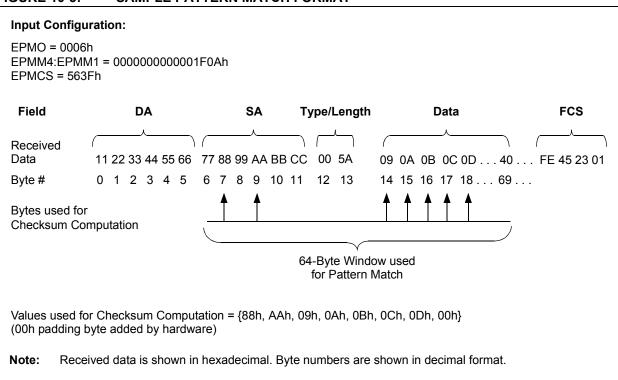

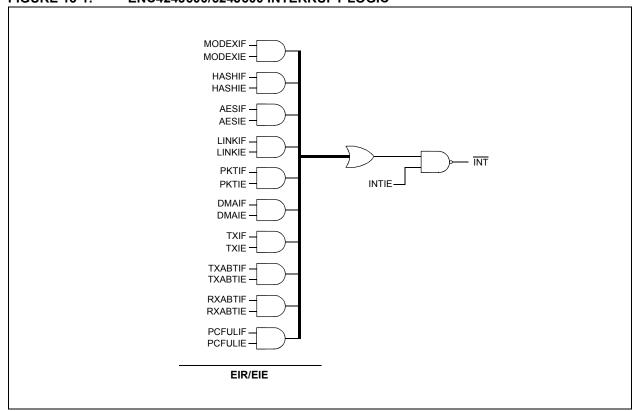

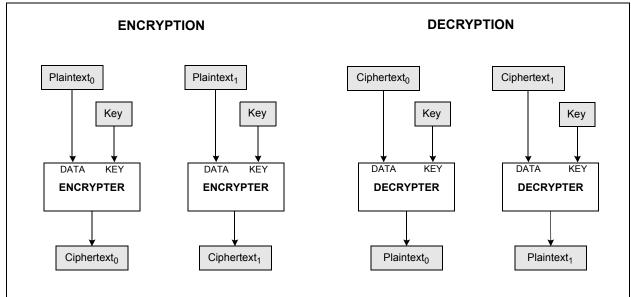

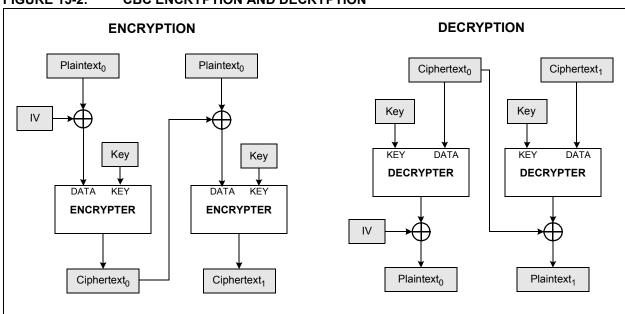

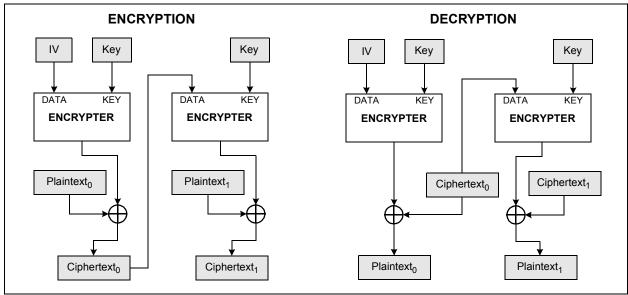

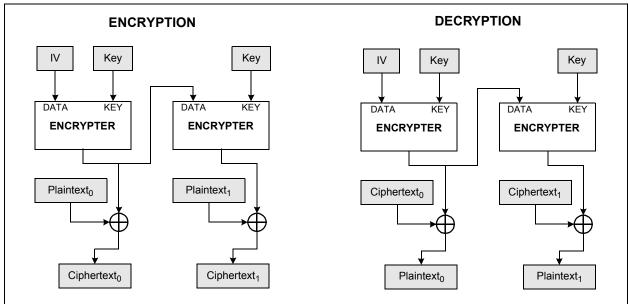

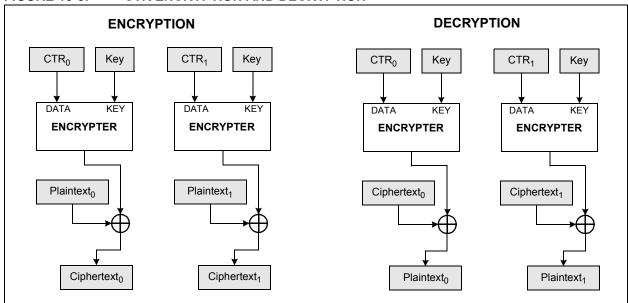

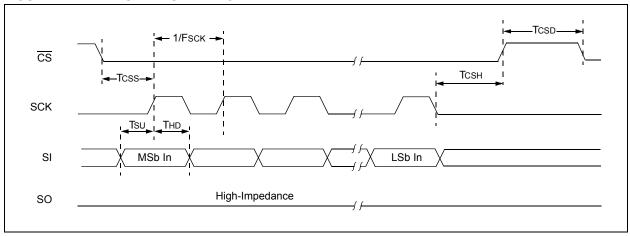

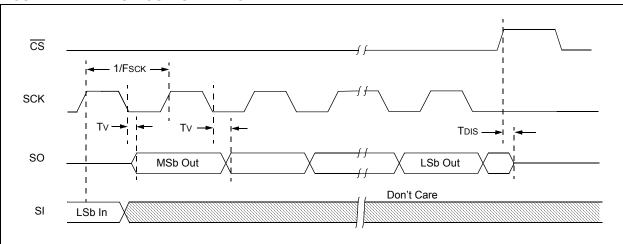

| 3F15 | EPMM2             |  |  |  |  |  |  |  |  |  |  |