3-Port 10/100 Integrated Switch with PHY and Frame Buffer

#### Rev. 2.06

### **General Description**

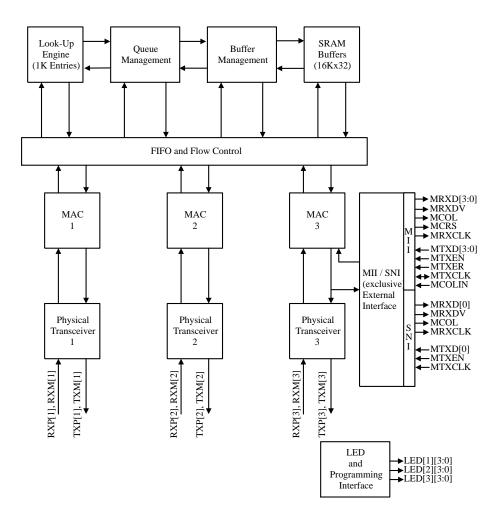

The KS8993 contains three 10/100 physical layer transceivers, three MAC (Media Access Control) units with an integrated layer 2 switch. The device runs in two modes. The first mode is a three port integrated switch and the second is as a three port switch with the third port decoupled from the physical port. In this mode access to the third MAC is provided using a reverse or forward MII (Media Independent Interface) such that an external MAC can be directly connected to the KS8993. This interface also supports the 7-wire (serial network interface) as used by some routing devices.

Useful configurations include a stand alone three port switch as well as a two port switch with a routing element connected to the extra MII port. The additional port is also useful for public network interfacing. The KS8993 has rich features such as VLAN and priority queuing and is designed to reside in an unmanaged design not requiring processor intervention. This is achieved through I/O strapping at system reset time.

On the media side, the KS8993 supports 10BaseT, 100BaseTX and 100BaseFX as specified by the IEEE 802.3 committee.

Physical signal transmission and reception are enhanced through use of analog circuitry that makes the design more efficient and allows for lower power consumption and smaller chip die size.

Data sheets and support documentation can be found on Micrel's web site at www.micrel.com.

## **Functional Diagram**

Micrel, Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

## Features

- 3-port 10/100 integrated switch with physical layer transceivers

- 64k Byte of SRAM on chip for frame buffering

- 1.0Gbps high performance memory bandwidth

- 10BaseT, 100BaseTX and 100BaseFX modes of operation

- Support for UTP or fiber installations

- Superior analog technology for reduced power and die size

- Supports port based VLAN

- QoS feature!! Supports 802.1p based priority or portbased priority

- Indicators for link, activity, full/half-duplex and speed

- Unmanaged operation via strapping at system reset time

- Hardware based 10/100, full/half, flow control and autonegotiation

- Individual port forced modes (full-duplex, 100BaseTX) when auto-negotiation is disabled

- Wire speed reception and transmission

- On chip integrated address look-up engine, supports 1K absolute MAC addresses

- Automatic address learning, address aging and address migration

- Full-duplex IEEE 802.3x flow control (Pause) with force mode option

- Half-duplex back pressure flow control

- Comprehensive LED support

- External MAC interface (MII or SNI 7-wire) for router applications

- 300mA (0.75W) including physical transmit drivers

- Commercial temperature range: 0°C to +70°C

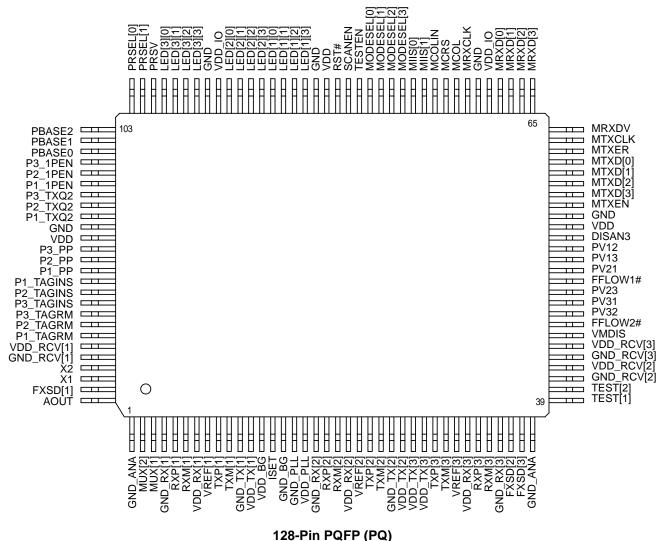

- Available in 128-pin PQFP with single 2.5V power supply

# **Ordering Information**

| Part Numbe | r       | Temperature  | Package      |  |

|------------|---------|--------------|--------------|--|

| Standard   | Pb-Free | Range        |              |  |

| KS8993     | KSZ8993 | 0°C to +70°C | 128-Pin PQFP |  |

| Revision | Date     | Summary of Changes                                                                                                                                                                                                                                                                                                                   |

|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.00     | 04/13/00 | Document origination                                                                                                                                                                                                                                                                                                                 |

| 1.01     | 05/31/00 | Miscellaneous changes                                                                                                                                                                                                                                                                                                                |

| 1.02     | 06/08/00 | Index repair                                                                                                                                                                                                                                                                                                                         |

| 1.03     | 09/20/00 | MII forward correction.<br>MRXD[3:1] correction.                                                                                                                                                                                                                                                                                     |

| 1.04     | 10/30/00 | Update voltage ratings.                                                                                                                                                                                                                                                                                                              |

| 1.05     | 10/31/00 | Correct I/O descriptions.                                                                                                                                                                                                                                                                                                            |

| 1.06     | 11/08/00 | Correct mode operation for LED[1:3][0]<br>Add timing information                                                                                                                                                                                                                                                                     |

| 1.07     | 12/21/00 | Correct pin information                                                                                                                                                                                                                                                                                                              |

| 1.08     | 03/23/01 | Correct VLAN description.                                                                                                                                                                                                                                                                                                            |

| 1.09     | 03/26/01 | Update MODESEL descriptions for packet size extensions                                                                                                                                                                                                                                                                               |

| 1.10     | 04/19/01 | Update electrical characteristics; Correct I/O information.                                                                                                                                                                                                                                                                          |

| 1.11     | 04/20/01 | Correct timing information                                                                                                                                                                                                                                                                                                           |

| 1.12     | 05/10/01 | Update I/O descriptions                                                                                                                                                                                                                                                                                                              |

| 1.13     | 06/08/01 | Define control for LED[3][3]                                                                                                                                                                                                                                                                                                         |

| 1.14     | 06/26/01 | Revise definition for LED[3][3]                                                                                                                                                                                                                                                                                                      |

| 1.15     | 08/1/01  | Update timing information and power dissipation<br>Add power up timing description; Correct DISAN3 default mode.                                                                                                                                                                                                                     |

| 1.16     | 08/9/01  | Correct LED [1] [1] to float configuration<br>Add Reverse and Forward MII timing                                                                                                                                                                                                                                                     |

| 2.00     | 4/8/02   | Correct reserve buffer from 128 to 96 for PRSV pin.<br>Add max. current.<br>Add force flow control Option as follows:<br>Change pin 50 from reserved to FFLOW1# for force flow control on port 1.)<br>Change pin 46 from reserved to FFLOW2# for force flow control on port 2.<br>Modify LED[1][2] for force flow control on port 3. |

| 2.01     | 5/6/02   | Add TX Disable for Port 1 and port 2, Power down for port 3 and Far end Fault Disable features using MUX[1:2] and TEST[1:2] pins.                                                                                                                                                                                                    |

| 2.02     | 7/2/02   | Recommend pull-down on LED[3][3]                                                                                                                                                                                                                                                                                                     |

| 2.03     | 8/29/03  | Convert to new format.                                                                                                                                                                                                                                                                                                               |

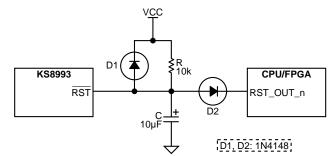

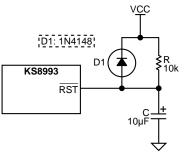

| 2.04     | 1/24/05  | Added reset circuit recommendation.                                                                                                                                                                                                                                                                                                  |

| 2.05     | 5/12/05  | Added lead-free part number                                                                                                                                                                                                                                                                                                          |

**Table of Contents**

| System Level Applications                       | 5  |

|-------------------------------------------------|----|

| Pin Description                                 | 6  |

| I/O Grouping                                    | 9  |

| I/O Descriptions                                | 10 |

| Pin Configuration                               | 15 |

| Functional Overview: Physical Layer Transceiver | 16 |

| 100BaseTX Transmit                              | 16 |

| 100BaseTX Receive                               | 16 |

| PLL Clock Synthesizer                           | 16 |

| Scrambler/De-scrambler (100BaseTX only)         | 16 |

| 100BaseFX operation                             |    |

| 100BaseFX Signal Detection                      | 16 |

| 100BaseFX Far End Fault                         | 16 |

| 10BaseT Transmit                                | 16 |

| 10BaseT Receive                                 | 16 |

| Power Management                                | 17 |

| LED Mode Selection                              |    |

| Auto-Negotiation                                | 17 |

| Functional Overview: Switch Core                | 18 |

| Address Look Up                                 | 18 |

| Learning                                        | 18 |

| Migration                                       | 18 |

| Aging                                           |    |

| Forwarding                                      | 18 |

| Switching Engine                                | 18 |

| MAC (Media Access Controller) Operation         | 18 |

| Inter Packet Group                              | 18 |

| Back off Algorithm                              |    |

| Late Collision                                  |    |

| Illegal Frame                                   | 18 |

| Flow Control                                    | 18 |

| Full-Duplex Flow Control                        | 18 |

| Half-Duplex Back Pressure                       | 18 |

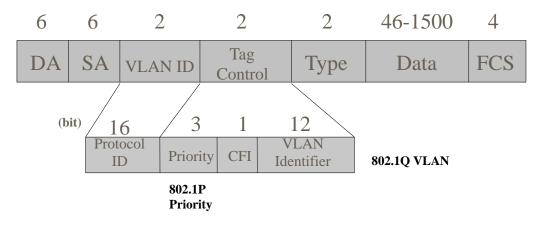

| VLAN Support                                    | 19 |

| QoS Priority Support                            | 20 |

| MII Interface Operation                         |    |

| SNI Interface (7-wire) Operation                |    |

| Absolute Maximum Ratings                        |    |

| Operating Ratings                               |    |

| Electrical Characteristics                      |    |

| Timing Diagrams                                 |    |

| Reference Circuit                               |    |

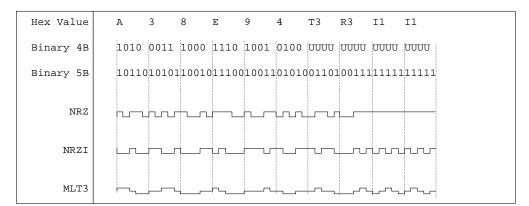

| 4B/5B Coding                                    |    |

| MLT Coding                                      |    |

| 802.1q VLAN and 802.1p Priority Frame           |    |

| Selection of Isolation Transformers             |    |

| Selection of Reference Crystals                 |    |

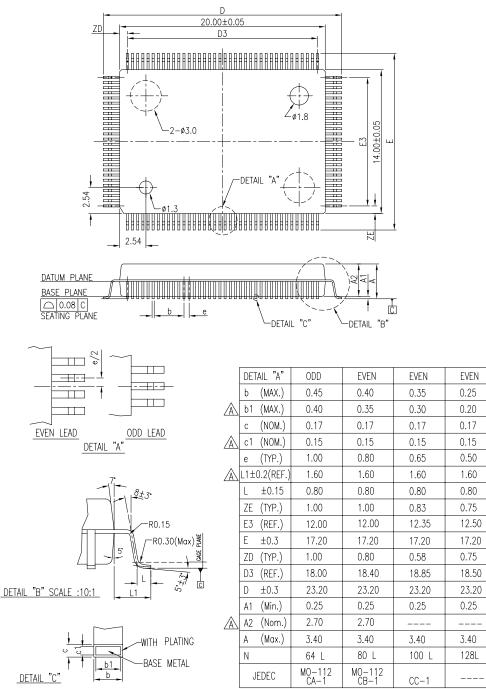

| Package Outline and Dimensions                  | 35 |

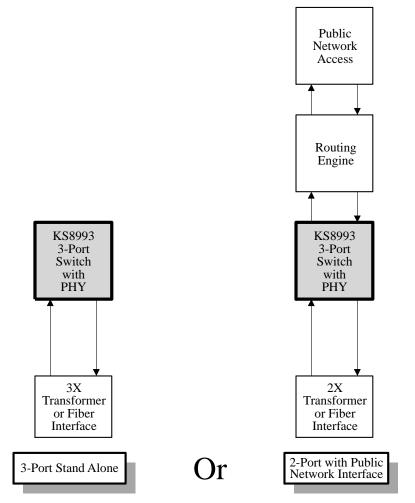

## **System Level Applications**

The KS8993 can be configured to fit either in a three port 10/ 100 application or as a two port 10/100 network interface with an extra MII or SNI port. This MII/SNI port can be connected to an external processor and used for routing purposes or public network access. The major benefits of using the KS8993 are the lower power consumption, unmanaged operation, flexible configuration and built in frame buffering. Two such applications are depicted below.

Figure 1. KS8993 Applications

| Pin Number | Pin Name  | Type <sup>(Note 1)</sup> | Port | Pin Function                                          |  |

|------------|-----------|--------------------------|------|-------------------------------------------------------|--|

| 1          | GND_ANA   | GND                      |      | Analog ground                                         |  |

| 2          | MUX[2]    | I                        |      | Factory test pin                                      |  |

| 3          | MUX[1]    | I                        |      | Factory test pin                                      |  |

| 4          | GND_RX[1] | GND                      | 1    | Ground for receiver                                   |  |

| 5          | RXP[1]    | I                        | 1    | Physical receive signal + (differential)              |  |

| 6          | RXM[1]    | I                        | 1    | Physical receive signal - (differential)              |  |

| 7          | VDD_RX[1] | Pwr                      | 1    | 2.5V for receiver                                     |  |

| 8          | VREF[1]   | 0                        | 1    | Reference voltage for transmit transformer center tap |  |

| 9          | TXP[1]    | 0                        | 1    | Physical transmit signal + (differential)             |  |

| 10         | TXM[1]    | 0                        | 1    | Physical transmit signal - (differential)             |  |

| 11         | GND_TX[1] | GND                      | 1    | Ground for transmit circuitry                         |  |

| 12         | VDD_TX[1] | Pwr                      | 1    | 2.5V for transmit circuitry                           |  |

| 13         | VDD_BG    | Pwr                      |      | 2.5V for analog circuitry                             |  |

| 14         | ISET      | 0                        |      | Set physical transmit output current                  |  |

| 15         | GND_BG    | GND                      |      | Ground for analog circuitry                           |  |

| 16         | GND_PLL   | GND                      |      | Ground for phase locked loop circuitry                |  |

| 17         | VDD_PLL   | Pwr                      |      | 2.5V for phase locked loop circuitry                  |  |

| 18         | GND_RX[2] | GND                      | 2    | Ground for receiver                                   |  |

| 19         | RXP[2]    | I                        | 2    | Physical receive signal + (differential)              |  |

| 20         | RXM[2]    | I                        | 2    | Physical receive signal - (differential)              |  |

| 21         | VDD_RX[2] | Pwr                      | 2    | 2.5V for receiver                                     |  |

| 22         | VREF[2]   | 0                        | 2    | Reference voltage for transmit transformer center tap |  |

| 23         | TXP[2]    | 0                        | 2    | Physical transmit signal + (differential)             |  |

| 24         | TXM[2]    | 0                        | 2    | Physical transmit signal - (differential)             |  |

| 25         | GND_TX[2] | GND                      | 2    | Ground for transmit circuitry                         |  |

| 26         | VDD_TX[2] | Pwr                      | 2    | 2.5V for transmit circuitry                           |  |

| 27         | VDD_TX[3] | Pwr                      | 3    | 2.5V for transmit circuitry                           |  |

| 28         | GND_TX[3] | GND                      | 3    | Ground for transmit circuitry                         |  |

| 29         | TXP[3]    | 0                        | 3    | Physical transmit signal + (differential)             |  |

| 30         | TXM[3]    | 0                        | 3    | Physical transmit signal - (differential)             |  |

| 31         | VREF[3]   | 0                        | 3    | Reference voltage for transmit transformer center tap |  |

| 32         | VDD_RX[3] | Pwr                      | 3    | 2.5V for receiver                                     |  |

| 33         | RXP[3]    | I                        | 3    | Physical receive signal + (differential)              |  |

| 34         | RXM[3]    | I                        | 3    | Physical receive signal - (differential)              |  |

| 35         | GND_RX[3] | GND                      | 3    | Ground for receiver                                   |  |

| 36         | FXSD[2]   | I                        | 2    | Fiber signal detect                                   |  |

| 37         | FXSD[3]   | I                        | 3    | Fiber signal detect                                   |  |

| 38         | GND_ANA   | GND                      |      | Analog ground                                         |  |

GND = ground

I = input

O = output

I/O = bi-directional

| Pin Number | Pin Name   | Type <sup>(Note 1)</sup> | Port | Pin Function                                                                       |  |

|------------|------------|--------------------------|------|------------------------------------------------------------------------------------|--|

| 39         | TEST[1]    | I                        |      | Factory test pin                                                                   |  |

| 40         | TEST[2]    | I                        |      | Factory test pin                                                                   |  |

| 41         | GND_RCV[2] | GND                      | 2    | Ground for clock recovery circuitry                                                |  |

| 42         | VDD_RCV[2] | Pwr                      | 2    | 2.5V for clock recovery circuitry                                                  |  |

| 43         | GND_RCV[3] | GND                      | 3    | Ground for clock recovery circuitry                                                |  |

| 44         | VDD_RCV[3] | Р                        | 3    | 2.5V for clock recovery circuitry                                                  |  |

| 45         | VMDIS      | I                        |      | DIScard VLAN Mismatch packets                                                      |  |

| 46         | FFLOW2#    | I                        | 2    | Force flow control on port 2                                                       |  |

| 47         | PV32       | I                        | 3    | Port 3 VLAN Port mask bit 1                                                        |  |

| 48         | PV31       | I                        | 3    | Port 3 VLAN Port mask bit 0                                                        |  |

| 49         | PV23       | I                        | 2    | Port 2 VLAN Port mask bit 2                                                        |  |

| 50         | FFLOW1#    | I                        | 1    | Force flow control on port 1                                                       |  |

| 51         | PV21       | I                        | 2    | Port 2 VLAN Port mask bit 0                                                        |  |

| 52         | PV13       | I                        | 1    | Port 1 VLAN Port mask bit 2                                                        |  |

| 53         | PV12       | I                        | 1    | Port 1 VLAN Port mask bit 1                                                        |  |

| 54         | DISAN3     | I                        | 3    | Port 3 auto-negotiation disable (pull this down to enable port 3 auto negotiation) |  |

| 55         | VDD        | Pwr                      |      | 2.5V for core digital circuitry                                                    |  |

| 56         | GND        | GND                      |      | Ground for digital circuitry                                                       |  |

| 57         | MTXEN      | I                        | 3    | MII transmit enable                                                                |  |

| 58         | MTXD[3]    | I                        | 3    | MII transmit bit 3                                                                 |  |

| 59         | MTXD[2]    | I                        | 3    | MII transmit bit 2                                                                 |  |

| 60         | MTXD[1]    | I                        | 3    | MII transmit bit 1                                                                 |  |

| 61         | MTXD[0]    | I                        | 3    | MII transmit bit 0                                                                 |  |

| 62         | MTXER      | I                        | 3    | MII transmit error                                                                 |  |

| 63         | MTXCLK     | I/O                      | 3    | MII output clock                                                                   |  |

| 64         | MRXDV      | 0                        | 3    | MII receive data valid                                                             |  |

| 65         | MRXD[3]    | 0                        | 3    | MII receive bit 3                                                                  |  |

| 66         | MRXD[2]    | 0                        | 3    | MII receive bit 2                                                                  |  |

| 67         | MRXD[1]    | 0                        | 3    | MII receive bit 1                                                                  |  |

| 68         | MRXD[0]    | 0                        | 3    | MII receive bit 0                                                                  |  |

| 69         | VDD_IO     | Pwr                      |      | 2.5V or 3.3V for MII interface, LEDs and other digital I/O                         |  |

| 70         | GND        | GND                      |      | Ground for digital circuitry                                                       |  |

| 71         | MRXCLK     | I/O                      | 3    | MII input clock                                                                    |  |

| 72         | MCOL       | 0                        | 3    | MII collision detect output                                                        |  |

| 73         | MCRS       | I/O                      | 3    | MII carrier sense                                                                  |  |

| 74         | MCOLIN     | I                        | 3    | MII collision detect input                                                         |  |

| 75         | MIIS[1]    | I                        | 3    | MII mode select bit 1                                                              |  |

| 76         | MIIS[0]    | I                        | 3    | MII mode select bit 0                                                              |  |

$\mathsf{GND} = \mathsf{ground}$

I = input

O = output

I/O = bi-directional

| Pin Number | Pin Name   | Type <sup>(Note 1)</sup> | Port | Pin Function                                               |  |

|------------|------------|--------------------------|------|------------------------------------------------------------|--|

| 77         | MODESEL[3] | I                        |      | Selects LED and test modes                                 |  |

| 78         | MODESEL[2] | I                        |      | Selects LED and test modes                                 |  |

| 79         | MODESEL[1] | I                        |      | Selects LED and test modes                                 |  |

| 80         | MODESEL[0] | I                        |      | Selects LED and test modes                                 |  |

| 81         | TESTEN     | I                        |      | Factory test pin - tie low for normal operation            |  |

| 82         | SCANEN     | I                        |      | Factory test pin - tie low for normal operation            |  |

| 83         | RST#       | I                        |      | Reset                                                      |  |

| 84         | VDD        | Pwr                      |      | 2.5V for core digital circuitry                            |  |

| 85         | GND        | GND                      |      | Ground for digital circuitry                               |  |

| 86         | LED[1][3]  | 0                        | 1    | Port 1 LED indicator 3                                     |  |

| 87         | LED[1][2]  | 0                        | 1    | Port 1 LED indicator 2                                     |  |

| 88         | LED[1][1]  | 0                        | 1    | Port 1 LED indicator 1                                     |  |

| 89         | LED[1][0]  | 0                        | 1    | Port 1 LED indicator 0                                     |  |

| 90         | LED[2][3]  | 0                        | 2    | Port 2 LED indicator 3                                     |  |

| 91         | LED[2][2]  | 0                        | 2    | Port 2 LED indicator 2                                     |  |

| 92         | LED[2][1]  | 0                        | 2    | Port 2 LED indicator 1                                     |  |

| 93         | LED[2][0]  | 0                        | 2    | Port 2 LED indicator 0                                     |  |

| 94         | VDD_IO     | Pwr                      |      | 2.5V or 3.3V for MII interface, LEDs and other digital I/O |  |

| 95         | GND        | GND                      |      | Ground for digital circuitry                               |  |

| 96         | LED[3][3]  | 0                        | 3    | Port 3 LED indicator 3                                     |  |

| 97         | LED[3][2]  | 0                        | 3    | Port 3 LED indicator 2                                     |  |

| 98         | LED[3][1]  | 0                        | 3    | Port 3 LED indicator 1                                     |  |

| 99         | LED[3][0]  | 0                        | 3    | Port 3 LED indicator 0                                     |  |

| 100        | PRSV       | I                        |      | Priority queue buffer reserve                              |  |

| 101        | PRSEL[1]   | I                        |      | Priority scheme select bit 1                               |  |

| 102        | PRSEL[0]   | I                        |      | Priority scheme select bit 0                               |  |

| 103        | PBASE2     | I                        |      | Priority base value bit 2                                  |  |

| 104        | PBASE1     | I                        |      | Priority base value bit 1                                  |  |

| 105        | PBASE0     | I                        |      | Priority base value bit 0                                  |  |

| 106        | P3_1PEN    | I                        | 3    | Port 3 802.1p receive priority classification enable       |  |

| 107        | P2_1PEN    | I                        | 2    | Port 2 802.1p receive priority classification enable       |  |

| 108        | P1_1PEN    | I                        | 1    | Port 1 802.1p receive priority classification enable       |  |

| 109        | P3_TXQ2    | I                        | 3    | Port 3 transmit queue split, priority queueing enable      |  |

| 110        | P2_TXQ2    | I                        | 2    | Port 2 transmit queue split, priority queueing enable      |  |

| 111        | P1_TXQ2    | I                        | 1    | Port 1 transmit queue split, priority queueing enable      |  |

| 112        | GND        | GND                      |      | Ground for digital circuitry                               |  |

| 113        | VDD        | Pwr                      |      | 2.5V for core digital circuitry                            |  |

| 114        | P3_PP      | I                        | 3    | Port 3 receive port based priority classification          |  |

| 115        | P2_PP      | I                        | 2    | Port 2 receive port based priority classification          |  |

GND = ground

I = input

O = output

I/O = bi-directional

| Pin Number | Pin Name   | Type <sup>(Note 1)</sup> | Port | Pin Function                                      |

|------------|------------|--------------------------|------|---------------------------------------------------|

| 116        | P1_PP      | I                        | 1    | Port 1 receive port based priority classification |

| 117        | P1_TAGINS  | I                        | 1    | Port 1 tag insertion enable                       |

| 118        | P2_TAGINS  | I                        | 2    | Port 2 tag insertion enable                       |

| 119        | P3_TAGINS  | I                        | 3    | Port 3 tag insertion enable                       |

| 120        | P3_TAGRM   | I                        | 3    | Port 3 tag removal enable                         |

| 121        | P2_TAGRM   | I                        | 2    | Port 2 tag removal enable                         |

| 122        | P1_TAGRM   | I                        | 1    | Port 1 tag removal enable                         |

| 123        | VDD_RCV[1] | Pwr                      | 1    | 2.5V for clock recovery circuitry                 |

| 124        | GND_RCV[1] | GND                      | 1    | Ground for clock recovery circuitry               |

| 125        | X2         | 0                        |      | Connect to crystal input                          |

| 126        | X1         | I                        |      | Crystal or clock input                            |

| 127        | FXSD[1]    | I                        | 1    | Fiber signal detect                               |

| 128        | AOUT       | 0                        |      | Factory test output                               |

GND = ground

I = input

O = output I/O = bi-directional

# I/O Grouping

| Group Name | Description                 |

|------------|-----------------------------|

| PHY        | Physical Interface          |

| MII        | Media Independant Interface |

| SNI        | Serial Network Interface    |

| IND        | LED Indicators              |

| UP         | Unmanaged Programmable      |

| CTRL       | Control and Miscellaneous   |

| TEST       | Test (Factory)              |

| PWR        | Power and Ground            |

| Group | I/O Names            | Active Status | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|----------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHY   | RXP[1:3]<br>RXM[1:3] | Analog        | Differential inputs (receive) for connection to media (transformer or fiber module).                                                                                                                                                                                                                                                                                                                                        |

|       | TXP[1:3]<br>TXM[1:3] | Analog        | Differential outputs (transmit) for connection to media (transformer or fiber module).                                                                                                                                                                                                                                                                                                                                      |

|       | FXSD[1:3]            | н             | Fiber signal detect - connect to fiber signal detect output on fiber module. Tie low for 100TX mode.                                                                                                                                                                                                                                                                                                                        |

|       | VREF[1:3]            | Analog        | Center tap transformer reference for transmit data.                                                                                                                                                                                                                                                                                                                                                                         |

|       | ISET                 | Analog        | Transmit Current Set. Connecting an external reference resistor to set transmitter output current. This pin connects a 1% $3k\Omega$ resistor if a transformer of turns ratio of 1:1 is used.                                                                                                                                                                                                                               |

| MII   |                      |               | See "Table 2, MII Interconnect" for forward and reverse signal usage.                                                                                                                                                                                                                                                                                                                                                       |

|       | MRXD[0:3]            | Н             | Four bit wide data bus for receiving MAC frames.                                                                                                                                                                                                                                                                                                                                                                            |

|       | MRXDV                | Н             | Receive data valid.                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | MCRS                 | Н             | Receive carrier sense.                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | MCOL                 | Н             | Receive collision detection.                                                                                                                                                                                                                                                                                                                                                                                                |

|       | MCOLIN               | Н             | Collision in (for forward operation only).                                                                                                                                                                                                                                                                                                                                                                                  |

|       | MRXCLK               | Clock         | Receive clock.                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | MTXD[0:3]            | н             | Four bit wide data bus for transmitting MAC frames.                                                                                                                                                                                                                                                                                                                                                                         |

|       | MTXEN                | Н             | Transmit enable.                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | MTXER                | н             | Transmit error.                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | MTXCLK               | Clock         | Transmit clock.                                                                                                                                                                                                                                                                                                                                                                                                             |

| SNI   | MTXD[0]              | н             | Serial transmit data.                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | MTXEN                | н             | Transmit enable.                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | MTXCLK               | Clock         | Transmit clock.                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | MRXD[0]              | н             | Serial receive data.                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | MRXDV                | н             | Receive carrier sense/data valid.                                                                                                                                                                                                                                                                                                                                                                                           |

|       | MCOL                 | н             | Collision detection.                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | MRXCLK               | Clock         | Receive clock.                                                                                                                                                                                                                                                                                                                                                                                                              |

| IND   | LED[1:3][0]          | L             | Output (after reset).<br>Mode 0: Speed (low = 100/high = 10).<br>Mode 1: Reserved.<br>Mode 2: Collision (toggle = collision during receiving , high = no collision).<br>Mode 3: Speed (low = 100/high = 10).                                                                                                                                                                                                                |

|       | LED[1:3][1]          | L             | Output (after reset).<br>Mode 0: Duplex (low = full/high = half).<br>Mode 1: Duplex (low = full/high = half).<br>Mode 2: Duplex (low = full/high = half).<br>Mode 3: Reserved.                                                                                                                                                                                                                                              |

|       | LED[1:3][2]          | L             | Output (after reset).<br>Mode 0: Collision (toggle = collision during receiving , high = no collision).<br>Mode 1: Transmit Activity (toggle during transmission, high = idle).<br>Mode 2: 10/link/act (constant low = link, toggle = act, constant high = no link).<br>Mode 3: Full-Duplex + Collision (constant low = full-duplex, toggle = collision in half.<br>duplex, constant high = half-duplex with no collision). |

| Group | I/O Names    | Active Status | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                     |                          |                                        |                                                                                    |                                                                                                                              |  |

|-------|--------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------|----------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|

|       | LED[1:3][3]  | L             | Output (after reset).<br>Mode 0: Link + Activity (toggle = receiving or transmitting, constant low = link,<br>constant high = no link).<br>Mode 1: Receive Activity (toggle during receiving / high = no receiving activity).<br>Mode 2: 100/link/act (constant low = link, toggle = act, constant high = no link).<br>Mode 3: Mode 3: Link + Activity (toggle = receiving or transmitting, constant low =<br>link, constant high = no link).<br>Note: Mode is set by MODESEL[3:0] ; please see description in UP "Unmanaged<br>Programming" section. |                                     |                          |                                        |                                                                                    |                                                                                                                              |  |

| UP    | MODESEL[3:0] | Н             | Mode select at reset time. LED mode is selected by using the table below. MODESEL also controls the maximum frame length accepted.                                                                                                                                                                                                                                                                                                                                                                                                                    |                                     |                          |                                        |                                                                                    |                                                                                                                              |  |

|       |              |               | MOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ESEL                                |                          |                                        |                                                                                    |                                                                                                                              |  |

|       |              |               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2                                   | 1                        | 0                                      | LED mode                                                                           | Max Length (no tag/tag)                                                                                                      |  |

|       |              |               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                   | 0                        | 0                                      | LED mode 0                                                                         | 1518/1522                                                                                                                    |  |

|       |              |               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                   | 0                        | 1                                      | LED mode 1                                                                         | 1518/1522                                                                                                                    |  |

|       |              |               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                   | 1                        | 0                                      | LED mode 2                                                                         | 1518/1522                                                                                                                    |  |

|       |              |               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                   | 1                        | 1                                      | LED mode 3                                                                         | 1518/1522                                                                                                                    |  |

|       |              |               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                   | 0                        | 0                                      | Factory testing                                                                    | Not applicable                                                                                                               |  |

|       |              |               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                   | 0                        | 1                                      | Factory testing                                                                    | Not applicable                                                                                                               |  |

|       |              |               | 0 1 1 0 Factory testing Not applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |                          |                                        |                                                                                    |                                                                                                                              |  |

|       |              |               | 0 1 1 1 Factory testing Not applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |                          |                                        |                                                                                    |                                                                                                                              |  |

|       |              |               | 1 0 0 0 Factory testing Not applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |                          |                                        |                                                                                    |                                                                                                                              |  |

|       |              |               | 1 0 0 1 Factory testing Not applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |                          |                                        |                                                                                    |                                                                                                                              |  |

|       |              |               | 1 0 1 0 Factory testing Not applicable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |                          |                                        |                                                                                    |                                                                                                                              |  |

|       |              |               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                   | 1                        | 1                                      | LED mode 3                                                                         | 1536/1536                                                                                                                    |  |

|       |              |               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                   | 0                        | 0                                      | LED mode 0                                                                         | 1536/1536                                                                                                                    |  |

|       |              |               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                   | 0                        | 1                                      | Factory testing                                                                    | Not applicable                                                                                                               |  |

|       |              |               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                   | 1                        | 0                                      | LED mode 2                                                                         | 1536 / 1536                                                                                                                  |  |

|       |              |               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                   | 1                        | 1                                      | Factory testing                                                                    | Not applicable                                                                                                               |  |

|       | FFLOW1#      | L             | Pulleo<br>Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | d up = no<br>control fo<br>d down = | o force flo<br>eature is | ow contro<br>enabled a                 | e on port 1.<br>I feature on port 1 (<br>and disabled by aut<br>control feature on |                                                                                                                              |  |

|       | FFLOW2#      | L             | Program force flow control feature on port 2.<br>Pulled up = no force flow control feature on port 2 (default).<br>Flow control feature is enabled and disabled by auto-negotiation.<br>Pulled down = enable force flow control feature on port 2 regardless of auto-negotia-<br>tion result.                                                                                                                                                                                                                                                         |                                     |                          |                                        |                                                                                    |                                                                                                                              |  |

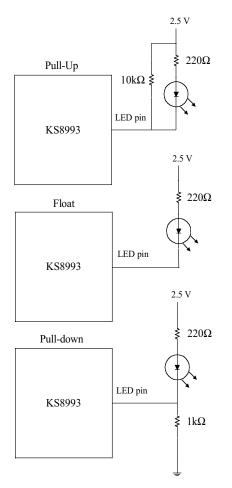

|       | LED[1][3]    |               | Program advertise flow control feature for 10/100BaseTX ports during auto-negotia-<br>tion at reset time.<br>Pulled low = no advertise flow control during auto-negotiation.<br>Pulled high = advertise flow control during auto-negotiation (default).                                                                                                                                                                                                                                                                                               |                                     |                          |                                        |                                                                                    |                                                                                                                              |  |

|       | LED[1][2]    |               | Pulled<br>Flow<br>Pulled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | d low = 1<br>control fe<br>d high = | no force t<br>eature is  | flow contr<br>enabled/o<br>prce flow o | ol feature on port 3 disabled by auto-ne                                           | ling MII port at reset time.<br>, including MII port (default).<br>gotiation result.<br>ort 3, including MII port regardless |  |

|       | LED[1][1]    |               | Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | rved - us                           | se float co              | onfiguratio                            | on.                                                                                |                                                                                                                              |  |

| Group | I/O Names   | Active Status | Descriptio                                                                                                                                                                              | n             |                                                                                  |                                                                            |  |  |  |

|-------|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|

|       | LED[1][0]   |               | Programs buffer allocation per port at reset time. Use the following table to select the option.<br>Pulled low = 170 buffers (default).<br>Pulled high = adaptive mode.                 |               |                                                                                  |                                                                            |  |  |  |

|       | LED[2][3]   |               | Programs MAC address aging in the address look-up table at reset time. Aging eliminates old entries from the table.<br>Pulled high = 5 minute aging (default).<br>Pulled low = disable. |               |                                                                                  |                                                                            |  |  |  |

|       | LED[2][2]   |               |                                                                                                                                                                                         | n = enable (c | re enable at reset time.<br>lefault).                                            |                                                                            |  |  |  |

|       | LED[2][1]   |               |                                                                                                                                                                                         | n = enable (c | back off in half-duplex at res<br>lefault).                                      | et time.                                                                   |  |  |  |

|       | LED[2][0]   |               |                                                                                                                                                                                         | n = enable (c | e collision drop at reset time<br>lefault).                                      |                                                                            |  |  |  |

|       | LED[3][3]   |               |                                                                                                                                                                                         | al pulldown   |                                                                                  | nd LED[3][3] is being used. If<br>to pull-down is required ( floating).    |  |  |  |

|       | LED[3][2:0] |               |                                                                                                                                                                                         |               |                                                                                  | e the table below to set this mode<br>g port auto-negotiation is disabled. |  |  |  |

|       |             |               | Signal                                                                                                                                                                                  | Port          | Force 10BaseTX                                                                   | Force 100BaseTX                                                            |  |  |  |

|       |             |               | LED[3][2]                                                                                                                                                                               | 3             | Pulled low                                                                       | Pulled high (default)                                                      |  |  |  |

|       |             |               | LED[3][1]                                                                                                                                                                               | 2             | Pulled low                                                                       | Pulled high (default)                                                      |  |  |  |

|       |             |               | LED[3][0]                                                                                                                                                                               | 1             | Pulled low                                                                       | Pulled high (default)                                                      |  |  |  |

|       | MRXD[3:1]   |               |                                                                                                                                                                                         |               |                                                                                  | e the table below to set this mode<br>g port auto-negotiation is disabled. |  |  |  |

|       |             |               | Signal                                                                                                                                                                                  | Port          | Force Half-Duplex                                                                | Force Full-Duplex                                                          |  |  |  |

|       |             |               | MRXD[3]                                                                                                                                                                                 | 3             | Pulled low (default)                                                             | Pulled high                                                                |  |  |  |

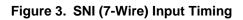

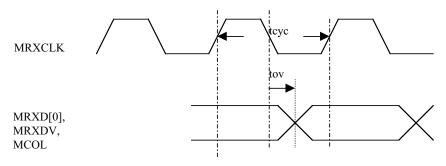

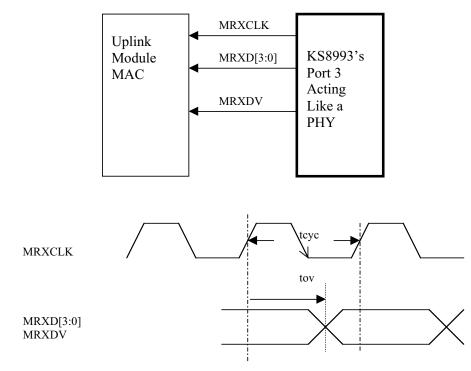

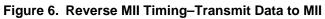

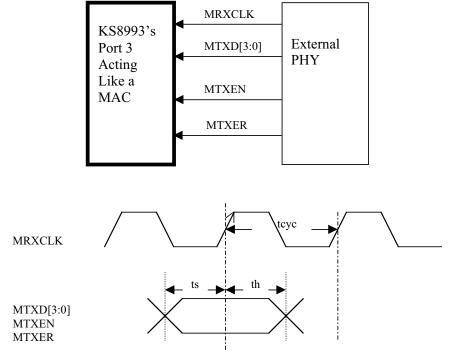

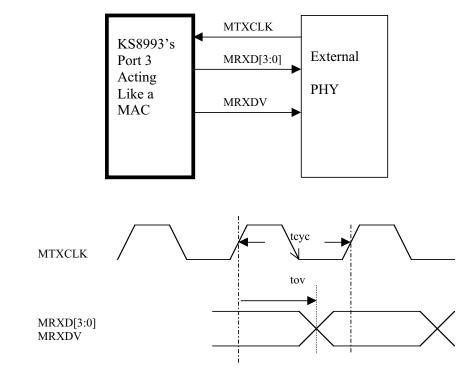

|       |             |               | MRXD[2]                                                                                                                                                                                 | 2             | Pulled low (default)                                                             | Pulled high                                                                |  |  |  |