# PROGRAMMABLE FREQUENCY SYNTHESIZER (25MHz to 400MHz)

Precision Edge® SY89429A

# **FEATURES**

- Improved jitter performance over SY89429

- 25MHz to 400MHz differential PECL outputs

- ±25ps peak-to-peak output jitter

- Minimal frequency over-shoot

- Synthesized architecture

- Serial 3 wire interface

- Parallel interface for power-on

- Internal quartz reference oscillator driven by quartz crystal or PECL source

- PECL output can operate with either +3.3V or +5V VCC\_OUT power supply

- **■** External loop filter optimizes performance/cost

- Applications note (AN-06) for ease of design-ins

- Available in PLCC and SOIC 28-pin packages

Precision Edge®

## **DESCRIPTION**

The SY89429A is a general purpose, synthesized clock source targeting applications that require both serial and parallel interfaces. Its internal VCO will operate over a range of frequencies from 400MHz to 800MHz. The differential PECL output can be configured to be the VCO frequency divided by 2, 4, 8 or 16. With the output configured to divide the VCO frequency by 2, and with a 16MHz external quartz crystal used to provide the reference frequency, the output frequency can be specified in 1MHz steps.

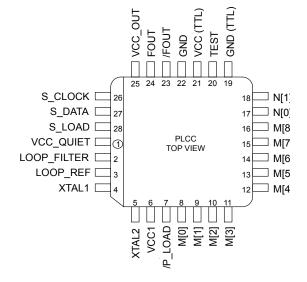

### PIN CONFIGURATION

# **APPLICATIONS**

- Workstations

- Advanced communications

- High end consumer

- High-performance computing

- RISC CPU clock

- Graphics pixel clock

- Test equipment

- Other high-performance processor-based applications

0 M[0] 1 28 /P\_LOAD 27 VCC1 M[1] 2 26 XTAL2 M[2] 3 M[3] 4 25 XTAL1 M[4] 5 24 LOOP REF M[5] 6 23 LOOP\_FILTER M[6] 7 SOIC 22 VCC QUIET **TOP VIEW** M[7] 8 21 S\_LOAD M[8] 9 20 S\_DATA N[0] 10 19 S\_CLOCK 18 VCC\_OUT N[1] 11 GND (TTL) 12 17 FOUT TEST 13 16 /FOUT VCC (TTL) 14 15 GND

Precision Edge is a registered trademark of Micrel, Inc.

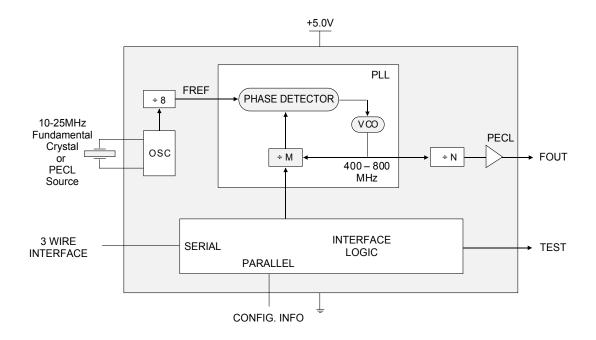

# **BLOCK DIAGRAM**

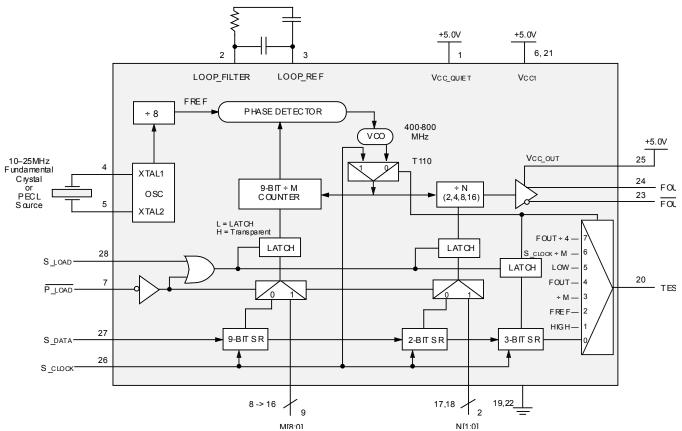

# **DETAILED BLOCK DIAGRAM**

NOTE:

Pin numbers reference PLCC pinout.

# PIN DESCRIPTIONS

### **INPUTS**

### XTAL1, XTAL2

These pins form an oscillator when connected to an external crystal. The crystal is series resonant. Alternatively, these pins can be driven with 100K PECL level by an external source.

### S\_LOAD

This TTL pin loads the configuration latches with the contents of the shift registers. The latches will be transparent when this signal is HIGH; thus, the register data must be stable on the HIGH-to-LOW transition of S\_LOAD for proper operation.

### S\_DATA

This TTL pin is the input to the serial configuration shift registers.

### S\_CLOCK

This TTL pin clocks the serial configuration shift registers. On the rising edge of this signal, data from S DATA is sampled.

### P\_LOAD

This TTL pin loads the configuration latches with the contents of the parallel inputs. The latches will be transparent when this signal is LOW; thus, the parallel data must be stable on the LOW-to-HIGH transition of P\_LOAD for proper operation.

### M[8:0]

These TTL pins are used to configure the PLL loop divider. They are sampled on the LOW-to-HIGH transition of  $\underline{P}_{LOAD}$ . M[8] is the MSB, M[0] is the LSB. The binary count on the M pins equates to the divide-by value for the PLL.

### N[1:0]

These TTL pins are used to configure the output divider modulus. They are sampled on the LOW-to-HIGH transition of P\_LOAD.

# N[1:0] Output Division 0 0 2 0 1 4 1 0 8 1 1 16

### **OUTPUTS**

### FOUT, FOUT

These differential positive-referenced ECL signals (PECL) are the output of the synthesizer.

### **TEST**

The function of this TTL output is determined by the serial configuration bits T[2:0].

### **POWER**

### VCC1

This is the positive supply for the chip and is normally connected to +5.0V.

### VCC\_OUT

This is the positive reference for the PECL outputs, FOUT and FOUT. It is constrained to be less than or equal to VCC1.

### VCC\_QUIET

This is the positive supply for the PLL and should be as noise-free as possible for low-jitter operation.

### **GND**

These pins are the negative supply for the chip and are normally all connected to ground.

### **OTHER**

### LOOP\_FILTER

This is an analog I/O pin that provides the loop filter for the PLL.

### LOOP\_REF

This is an analog I/O pin that provides a reference voltage for the PLL.

### **WITH 16MHZ INPUT**

| VCO Frequency |         | 256 | 128 | 64 | 32 | 16 | 8  | 4  | 2  | 1  |

|---------------|---------|-----|-----|----|----|----|----|----|----|----|

| (MHz)         | M Count | M8  | M7  | M6 | M5 | M4 | М3 | M2 | M1 | M0 |

| 400           | 200     | 0   | 1   | 1  | 0  | 0  | 1  | 0  | 0  | 0  |

| 402           | 201     | 0   | 1   | 1  | 0  | 0  | 1  | 0  | 0  | 1  |

| 404           | 202     | 0   | 1   | 1  | 0  | 0  | 1  | 0  | 1  | 0  |

| 406           | 203     | 0   | 1   | 1  | 0  | 0  | 1  | 0  | 1  | 1  |

| •             | •       | •   | •   | •  | •  | •  | •  | •  | •  | •  |

| •             |         | •   | •   | •  | •  | •  | •  | •  | •  | •  |

| •             |         | •   | •   | •  | •  | •  | •  | •  | •  | •  |

| 794           | 397     | 1   | 1   | 0  | 0  | 0  | 1  | 1  | 0  | 1  |

| 796           | 398     | 1   | 1   | 0  | 0  | 0  | 1  | 1  | 1  | 0  |

| 798           | 399     | 1   | 1   | 0  | 0  | 0  | 1  | 1  | 1  | 1  |

| 800           | 400     | 1   | 1   | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Param                             | Parameter Value                   |              |    |  |

|--------|-----------------------------------|-----------------------------------|--------------|----|--|

| Vcc    | Power Supply Voltag               | Power Supply Voltage -0.5 to +7.0 |              |    |  |

| Vı     | Input Voltage                     |                                   | -0.5 to +7.0 | V  |  |

| Іоит   | Output Source Continuous<br>Surge |                                   | 50<br>100    | mA |  |

| Tstore | Storage Temperature               | e                                 | -65 to +150  | °C |  |

| ТА     | Operating Temperatu               | ıre                               | –0 to +75    | °C |  |

### NOTE:

### **FUNCTIONAL DESCRIPTION**

The internal oscillator uses the external quartz crystal as the basis of its frequency reference. The output of the reference oscillator is divided by eight before being sent to the phase detector. With a 16MHz crystal, this provides a reference frequency of 2MHz.

The VCO within the PLL operates over a range of 400–800MHz. Its output is scaled by a divider that is configured by either the serial or parallel interfaces. The output of this loop divider is also applied to the phase detector.

The phase detector and loop filter force the VCO output frequency to be M times the reference frequency by adjusting the VCO control voltage. Note that for some values of M (either too high or too low) the PLL will not achieve loop lock. External loop filter components are utilized to allow for optimal phase jitter performance.

The output of the VCO is also passed through an output divider before being sent to the PECL output driver. The output divider is configured through either the serial or the parallel interfaces and can provide one of four divider ratios (2, 4, 8 or 16). This divider extends the performance of the part while providing a 50% duty cycle.

The output driver is driven differentially from the output divider and is capable of driving a pair of transmission lines terminated in 50ý. The positive reference for the output driver is provided by a dedicated power pin (VCC\_OUT) to reduce noise and provide application flexibility.

The configuration logic has two sections: serial and parallel. The parallel interface uses the values at the M[8:0] and N[1:0] inputs to configure the internal counters. Normally upon system reset, the  $P\_LOAD$  input is held LOW until sometime after power becomes valid. With  $S\_LOAD$  held LOW, on the LOW-to-HIGH transition of  $P\_LOAD$ , the parallel inputs are captured. The parallel interface has priority over the serial interface. Internal pull-up resistors are provided on the M[8:0] and N[1:0] inputs to reduce component count.

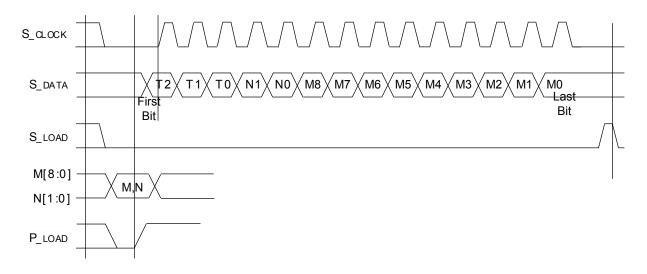

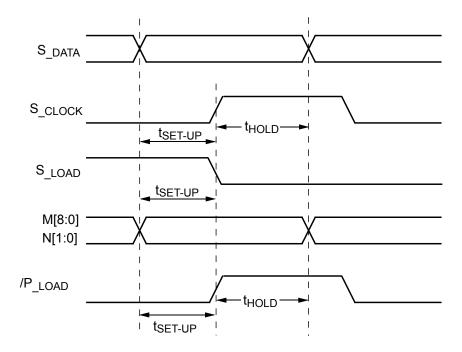

The serial interface logic is implemented with a 14-bit shift register scheme. The register shifts once per rising edge of the S\_CLOCK input. The serial input S\_DATA must meet set-up and hold timing as specified in the AC parameters section of this data sheet. With P\_LOAD held HIGH, the configuration latches will capture the value in the shift register on the HIGH-to-LOW edge of the S\_LOAD input. See the programming section for more information.

The TEST output reflects various internal node values and is controlled by the T[2:0] bits in the serial data stream. See the programming section for more information.

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. This is a stress rating only and functional operation is not implied at

conditions other than those detailed in the operational sections of this data sheet. Exposure to ABSOLUTE MAXIMUM RATING conditions for extended periods

may affect device reliability.

# PROGRAMMING INTERFACE

Programming the device is accomplished by properly configuring the internal dividers to produce the desired frequency at the outputs. The output frequency can be represented by this formula:

$$FOUT = \left(\frac{FXTAL}{8}\right) X \frac{M}{N}$$

Where FXTAL is the crystal frequency, M is the loop divider modulus, and N is the output divider modulus. Note that it is possible to select values of M such that the PLL is unable to achieve loop lock. To avoid this, always make sure that M is selected to be 200 M 400 for a 16MHz input reference.

M[8:0] and N[1:0] are normally specified once at power-on, through the parallel interface, and then possibly again through the serial interface. This approach allows the designer to bring up the application at one frequency and then change or fine-tune the clock, as the ability to control the serial interface becomes available. To minimize transients in the frequency domain, the output should be varied in the smallest step size possible.

| T2 | T1 | T0 | TEST                   | FOUT / FOUT |

|----|----|----|------------------------|-------------|

| 0  | 0  | 0  | Data Out – Last Bit SR | FVCO ÷ N    |

| 0  | 0  | 1  | HIGH                   | FVCO ÷ N    |

| 0  | 1  | 0  | FREF                   | FVCO ÷ N    |

| 0  | 1  | 1  | M Counter Output       | FVCO ÷ N    |

| 1  | 0  | 0  | FOUT                   | FVCO ÷ N    |

| 1  | 0  | 1  | LOW                    | FVCO ÷ N    |

| 1  | 1  | 0  | S_clock ÷ M            | S_clock ÷ N |

| 1  | 1  | 1  | FOUT ÷ 4               | FVCO ÷ N    |

The TEST output provides visibility for one of several internal nodes (as determined by the T[1:0] bits in the serial configuration stream). It is not configurable through the parallel interface. Although it is possible to select the node that represents FOUT, the TTL output may not be able to toggle fast enough for some of the higher output frequencies. The T2, T1, T0 configuration latches are preset to 000 when  $P\_LOAD$  is low, so that the FOUT outputs are as jitter-free as possible. The serial configuration port can be used to select one of the alternate functions for this pin.

The Test register is loaded with the first three bits, the N register with the next two and the M register with the final eight bits of the data stream on the S\_DATA input. For each register the most significant bit is loaded first (T2, N1 and M8).

When T[2:0] is set to 100 the SY89429A is placed in PLL bypass mode. In this mode the S\_CLOCK input is fed directly into the M and N dividers. The N divider drives the FOUT differential pair and the M counter drives the TEST output pin. In this mode the S\_CLOCK input could be used for low speed board level functional test or debug. Bypassing the PLL and driving FOUT directly gives the user more control on the test clocks sent through the clock tree (See detailed Block Diagram). Because the S\_CLOCK is a TTL level the input frequency is limited to 250MHz or less. This means the fastest the FOUT pin can be toggled via the S\_CLOCK is 125MHz as the minimum divide ratio of the N counter is 2. Note that the M counter output on the TEST output will not be a 50% duty cycle due to the way the divider is implemented.

Input S\_DATA to M0 then M1, then M2, etc., as indicated above.

# **100H ECL DC ELECTRICAL CHARACTERISTICS**

VCC1 = VCC\_QUIET = VCC\_TTL =  $+5.0V \pm 5\%$ ; VCC\_OUT =  $+3.3V \text{ to } +5.0V \pm 5\%$ ; TA =  $0^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$

| Symbol | Parameter           | Parameter Min. |                | Unit | Condition          |

|--------|---------------------|----------------|----------------|------|--------------------|

| Vон    | Output HIGH Voltage | Vcc_out -1.075 | Vcc_out -0.830 | V    | 50ý to Vcc_оuт –2V |

| Vol    | Output LOW Voltage  | Vcc_оит -1.860 | Vcc_out -1.570 | V    | 50ý to Vcc_оuт –2V |

# TTL DC ELECTRICAL CHARACTERISTICS

VCC1 = VCC\_QUIET = VCC\_TTL =  $+5.0V \pm 5\%$ ; VCC\_OUT =  $+3.3V \text{ to } +5.0V \pm 5\%$ ; TA = 0°C to +75°C

|        |                              | TA = 0°C   |      | TA = +25°C TA = +75°C |      |            |      |      |              |

|--------|------------------------------|------------|------|-----------------------|------|------------|------|------|--------------|

| Symbol | Parameter                    | Min.       | Max. | Min.                  | Max. | Min.       | Max. | Unit | Condition    |

| VIH    | Input HIGH Voltage           | 2.0        | _    | 2.0                   | _    | 2.0        | _    | V    | _            |

| VIL    | Input LOW Voltage            | _          | 0.8  | _                     | 0.8  | _          | 0.8  | V    | <del>-</del> |

| lін    | Input HIGH Current           | _          | 50   | _                     | 50   | _          | 50   | μA   | VIN = 2.7V   |

| lıL    | Input LOW Current            | _          | -0.6 | _                     | -0.6 | _          | -0.6 | mA   | VIN = 0.5V   |

| Vık    | Input Clamp Voltage          | _          | -1.2 | _                     | -1.2 | _          | -1.2 | V    | IIN = -12mA  |

| Vон    | Output HIGH Voltage          | _          | 2.5  | _                     | 2.5  | _          | 2.5  | V    | Iон = -2.0mA |

| Vol    | Output LOW Voltage           | _          | 0.5  | _                     | 0.5  | _          | 0.5  | V    | IoL = 8mA    |

| los    | Output Short Circuit Current | –80 (Typ.) |      | –80 (Typ.)            |      | –80 (Typ.) |      | mA   | Vout = 0V    |

| ICC1   | Supply Current               | _          | 225  | _                     | 225  | _          | 225  | mA   | _            |

|        | Typical % of Icc1 Vcc1       | 91         | %    | 91                    | %    | 91         | %    |      |              |

|        | Vcc_out                      | 4.5        | 5%   | 4.5                   | %    | 4.5        | 5%   |      |              |

|        | Vcc_quiet                    | 2.2        | 5%   | 2.2                   | 5%   | 2.2        | 5%   |      |              |

|        | Vcc_ttl                      | 2.25%      |      | 2.25%                 |      | 2.25%      |      |      |              |

|        |                              |            |      |                       |      |            |      |      |              |

# **AC ELECTRICAL CHARACTERISTICS**

Vcc1 = Vcc\_quiet = Vcc\_ttl =  $+5.0V \pm 5\%$ ; Vcc\_out = +3.3V to  $+5.0V \pm 5\%$ ; Ta =  $0^{\circ}$ C to  $+75^{\circ}$ C

|          |                                     |                                                          | Ta=            | 0°C        | TA = +         | -25°C      | TA = +75°C     |            |      |                        |

|----------|-------------------------------------|----------------------------------------------------------|----------------|------------|----------------|------------|----------------|------------|------|------------------------|

| Symbol   | Paran                               | neter                                                    | Min.           | Max.       | Min.           | Max.       | Min.           | Max.       | Unit | Condition              |

| fmaxi    | Maximum Input Freque                | ncy <sup>(1)</sup> S_clock<br>Xtal Oscillator            | —<br>10        | 10<br>25   | _<br>10        | 10<br>25   | —<br>10        | 10<br>25   | MHz  | Fundamental<br>Cyrstal |

| fMAXO    | Maximum Output Frequ                | uency VCO (Internal)<br>FOUT                             | 400<br>25      | 800<br>400 | 400<br>25      | 800<br>400 | 400<br>25      | 800<br>400 | MHz  |                        |

| tLOCK    | Maximum PLL Lock Time               |                                                          | _              | 10         | _              | 10         | _              | 10         | ms   |                        |

| tjitter  | Cycle-to-Cycle Jitter (Peak-toPeak) |                                                          |                | ±25        | _              | ±25        | _              | ±25        | ps   | Test output static     |

| ts       | Setup Time                          | S_DATA to S_CLOCK                                        | 20             | _          | 20             | _          | 20             | _          | ns   |                        |

|          |                                     | S_CLOCK to S_LOAD<br>M, N to P_LOAD                      | 20<br>20       | _<br>_     | 20<br>20       | _<br>_     | 20<br>20       | _          |      |                        |

| tH       | Hold Time                           | S_DATA to S_CLOCK<br>S_CLOCK to S_LOAD<br>M, N to P_LOAD | 20<br>20<br>20 |            | 20<br>20<br>20 |            | 20<br>20<br>20 | _          | ns   |                        |

| tpw(MIN) | Minimum Pulse Width                 | S_LOAD<br>P_LOAD                                         | 50<br>50       | _          | 50<br>50       | _<br>_     | 50<br>50       | _          | ns   |                        |

| tDC      | FOUT Duty Cycle                     |                                                          | 45             | 55         | 45             | 55         | 45             | 55         | %    |                        |

| tr<br>tf | Output Rise/Fall<br>20% to 80%      | FOUT                                                     | 300            | 800        | 300            | 800        | 300            | 800        | ps   |                        |

# NOTE:

<sup>1. 10</sup>MHz is the maximum frequency to load the feedback divide registers. S\_clock can be switched at high frequencies when used as a test clock in TEST\_MODE 6.

# **TIMING DIAGRAM**

# PRODUCT ORDERING CODE

| Part Number  | Package<br>Type | Operating<br>Range | Package<br>Marking                       | Lead<br>Finish      |

|--------------|-----------------|--------------------|------------------------------------------|---------------------|

| SY89429AJC   | J28-1           | Commercial         | SY89429A                                 | Sn-Pb               |

| SY89429AJCTR | J28-1           | Commercial         | SY89429A                                 | Sn-Pb               |

| SY89429AJZ   | J28-1           | Industrial         | SY89429A with Pb-Free bar-line indicator | Pb-Free<br>Matte-Sn |

| SY89429AJZTR | J28-1           | Industrial         | SY89429A with Pb-Free bar-line indicator | Pb-Free<br>Matte-Sn |

| SY89429AZC   | Z28-1           | Commercial         | SY89429A                                 | Sn-Pb               |

| SY89429AZCTR | Z28-1           | Commercial         | SY89429A                                 | Sn-Pb               |

| SY89429AZH   | Z28-1           | Industrial         | SY89429A with Pb-Free bar-line indicator | Pb-Free<br>NiPdAu   |

| SY89429AZHTR | Z28-1           | Industrial         | SY89429A with Pb-Free bar-line indicator | Pb-Free<br>NiPdAu   |

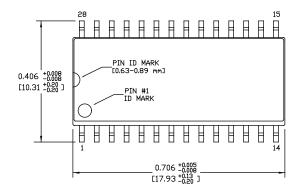

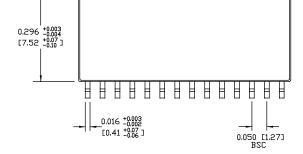

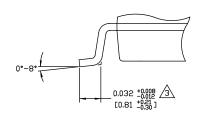

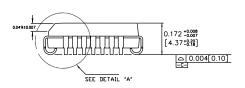

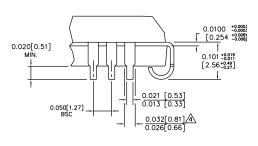

# 28 LEAD SOIC .300" WIDE (Z28-1)

TOP VIEW

DETAIL "A"

### NOTES:

- 1. DIMENSIONS ARE IN INCHESIMMI.

2. CONTROLLING DIMENSION: INCHES.

DIMENSION DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS, EITHER OF WHICH SHALL NOT EXCEED 0.006[0.15] PER SIDE.

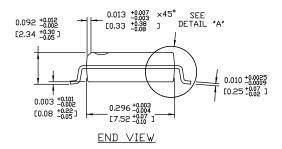

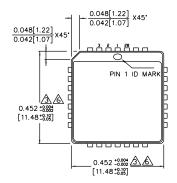

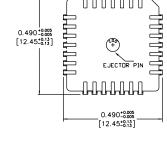

# 28 LEAD PLCC (J28-1)

TOP VIEW

**BOTTOM VIEW**

SIDE VIEW

DETAIL "A"

- NOTES:

1. DIMENSIONS ARE IN INCHES [MM].

2. CONTROLLING DIMENSION: INCHES.

- 2. CONTROLLING DIMENSION: INCHES.

3. DIMENSION DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS, EITHER OF WHICH SHALL NOT EXCEED 0.008 [0.203].

4. LEAD DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION.

5. MAXIMUM AND MINIMUM SPECIFICATIONS ARE INDICATED AS FOLLOWS: MAX/MIN

6. PACKAGE TOP DIMENSION MAY BE SLIGHTLY SMAILER THAN BOTTOM DIMENSION

# MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2003 Micrel, Incorporated.