# Circuit Note

| Circuits          |

|-------------------|

| from the Lab®     |

| Reference Designs |

Circuits from the Lab® reference designs are engineered and tested for quick and easy system integration to help solve today's analog, mixed-signal, and RF design challenges. For more information and/or support, visit www.analog.com/CN0336.

| Devices Connected/Referenced |                                                                 |  |

|------------------------------|-----------------------------------------------------------------|--|

| AD8606                       | Precision, Low Noise, CMOS, Rail-to-Rail<br>Input/Output Op Amp |  |

| AD7091R                      | 1 MSPS, Ultralow Power, 12-Bit ADC                              |  |

| ADuM5401                     | 4-Channel, 2.5 kV Isolators with Integrated DC-to-DC Converter  |  |

## 12-Bit, 300 kSPS, Single-Supply, Fully Isolated, Data Acquisition System for 4-20 mA Inputs

#### **EVALUATION AND DESIGN SUPPORT**

**Circuit Evaluation Boards**

CN0336 Circuit Evaluation Board (EVAL-CN0336-PMDZ) SDP/PMD Interposer Board (SDP-PMD-IB1Z) System Demonstration Platform (EVAL-SDP-CB1Z)

**Design and Integration Files**

**Schematics, Layout Files, Bill of Materials**

#### **CIRCUIT FUNCTION AND BENEFITS**

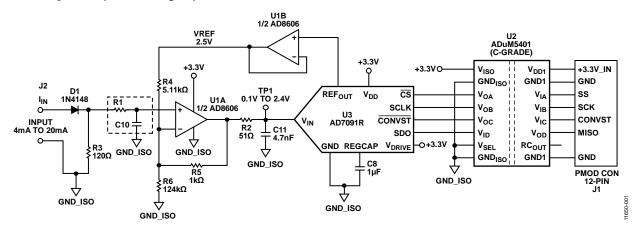

The circuit shown in Figure 1 is a completely isolated 12-bit, 300 kSPS data acquisition system utilizing only three active devices.

The system processes 4 mA to 20 mA input signals using a single 3.3 V supply. The total error after room temperature calibration is  $\pm 0.06\%$  FSR over a  $\pm 10^{\circ}$ C temperature change, making it ideal for a wide variety of industrial measurements

The small footprint of the circuit makes this combination an industry-leading solution for 4 mA to 20 mA data acquisition systems where the accuracy, speed, cost, and size play a critical role. Both data and power are isolated, thereby making the circuit robust to high voltages and also ground-loop interference often encountered in harsh industrial environments.

Figure 1. 4 mA to 20 mA Single Supply Analog to Digital Conversion with Isolation (All Connections and Decoupling Not Shown)

CN-0336 Circuit Note

#### CIRCUIT DESCRIPTION

The circuit consists of an input current-to-voltage converter, a level shifting circuit, an ADC stage, and an output isolation stage. The 4 mA to 20 mA input signal is converted to a voltage by resistor R3. For R3 =  $120\Omega$  and an input current of 4 mA to 20 mA, the input voltage to the level shifting circuit is: 0.48 V to 2.4 V. The diode D1 is used for protection against an accidental reverse connection of the input current source.

The voltage across R3 is level shifted and attenuated by the U1A op amp that is one-half of the dual AD8606. The output of the op amp is 0.1 V to 2.4 V which matches the input range of the ADC (0 V to 2.5 V) with 100 mV headroom to maintain linearity. The buffered voltage reference ( $V_{REF} = 2.5 \text{ V}$ ) from the AD7091R ADC is used to generate the required offset. Resistor values can be modified to accommodate other popular input ranges as described later in this circuit note.

The circuit design allows single-supply operation. The minimum output voltage specification of the AD8606 is 50 mV for a 2.7 V power supply and 290 mV for 5 V power supply with 10 mA load current, over the temperature range of -40°C to +125°C. A minimum output voltage of 45 mV to 60 mV is a conservative estimate for a 3.3 V power supply, a load current less than 1 mA, and a narrower temperature range.

Considering the tolerances of the parts, the minimum output voltage (low limit of the range) is set to 100 mV to allow for a safety margin. The upper limit of the output range is set to 2.4 V in order to give 100 mV headroom for the positive swing at the ADC input. Therefore, the nominal output voltage range of the input op amp is  $0.1~\rm V$  to  $2.4~\rm V$ .

The second half of the AD8606 (U1B) is used to buffer the internal 2.5 V voltage reference of the AD7091R (U3) ADC.

The AD8606 is chosen for this application because of its low offset voltage (65  $\mu$ V maximum), low bias current (1 pA maximum) and low noise (12 nV/ $\sqrt{Hz}$  maximum). Power dissipation is only 9.2 mW on a 3.3 V supply.

A single-pole RC filter (R2/C11) follows the op amp output stage to reduce the out-of-band noise. The cutoff frequency of the RC filter is set to 664 kHz. An optional filter (R1/C10) can be added to reduce the filter cutoff frequency even further in case of low frequency industrial noise. In such case, the sampling rate of the AD7091R can be reduced because of the lower signal bandwidth.

The AD7091R 12-bit 1 MSPS SAR ADC is chosen because of its ultralow power 349  $\mu A$  at 3.3 V (1.2 mW) which is significantly lower than any competitive ADC currently available in the market. The AD7091R also contains an internal 2.5 V reference with  $\pm 4.5$  ppm/°C typical drift. The input bandwidth is 7.5 MHz, and the high speed serial interface is SPI compatible. The AD7091R is available in a small footprint 10-lead MSOP.

The total power dissipation of the circuit (excluding the ADuM5401 isolator) is approximately 10.4 mW when operating on a 3.3 V supply.

Galvanic isolation is provided by the ADuM5401 (C-Grade) quad channel digital isolator. In addition to the isolated output data, the ADuM5401 also provides isolated +3.3 V for the circuit. The ADuM5401 is not required for normal circuit operation unless isolation is needed. The ADuM5401 quad-channel, 2.5 kV isolators with integrated dc-to-dc converter, is available in a small 16-lead SOIC. Power dissipation of the ADuM5401 with a 7 MHz clock is approximately 140 mW.

The AD7091R requires a 50 MHz serial clock (SCLK) to achieve a 1 MSPS sampling rate. However, the ADuM5401 (C-grade) isolator has a maximum data rate of 25 Mbps that corresponds to a maximum serial clock frequency of 12.5 MHz. In addition, the SPI port requires that the trailing edge of the SCLK clock the output data into the processor, therefore the total round-trip propagation delay through the ADuM5401 (120 ns maximum) limits the upper clock frequency to 1/120 ns = 8.3 MHz.

Even though the AD7091R is a 12-bit ADC, the serial data is formatted into a 16-bit word to be compatible with the processor serial port requirements. The sampling period,  $T_s$ , therefore consists of the AD7091R 650 ns conversion time plus 58 ns (extra time required from data sheet,  $t_1$  delay +  $t_{QUIET}$  delay) plus 16 clock cycles for the SPI interface data transfer.

$$T_s = 650 \text{ ns} + 58 \text{ ns} + 16 \times 120 \text{ ns} = 2628 \text{ ns}$$

$f_s = 1/T_s = 1/2628 \text{ ns} = 380 \text{ kSPS}$

In order to provide a safety margin, a maximum SCLK of 7 MHz and a maximum sampling rate of 300 kSPS is recommended. The digital SPI interface can be connected to the microprocessor evaluation board using the 12-pin, Pmod-compatible connector (Digilent Pmod Specifications).

#### Circuit Design

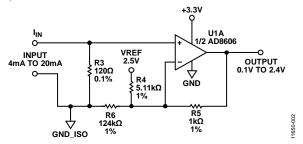

The circuit shown in Figure 2 provides the proper gain and level shifting to shift the  $0.48~\rm V$  to  $2.4~\rm V$  signal to the ADC input range of  $0.1~\rm V$  to  $2.4~\rm V$ .

Figure 2. Current-to-Voltage Converter and Level Shifting Circuit

Circuit Note CN-0336

The transfer function is obtained from the superposition principle.

$$V_{OUT} = I_{IN} R3 \left( 1 + \frac{R5}{R4/|R6} \right) - V_{REF} \frac{R5}{R4} = I *_{IN} R3 \left( 1 + \frac{R5}{R4/|R6} \right) + 4 \text{ mA} \times R3 \left( 1 + \frac{R5}{R4/|R6} \right) - V_{REF} \frac{R5}{R4}$$

(1)

where:

$$I_{IN} = I_{IN}^* + 4 \text{ mA}$$

(2)

$$I_{IN}^* = 0 \text{ mA to } 16 \text{ mA}$$

(3)

and

$$R4 \| R6 = \frac{R4R6}{R4 + R6}$$

(4)

#### Calculation of the Gain and the Resistor Values

The gain of the circuit is:

$$GAIN = \frac{\Delta V_{OUT}}{\Delta I_{IN}} = \frac{(2.4 - 0.1) \text{ V}}{(I_{IN}^*)_{MAX}} = \frac{2.3 \text{ V}}{16 \text{ mA}} = 143.75 \left[ \frac{\text{V}}{\text{mA}} \right] (5)$$

$$= R3 \left( 1 + \frac{R5}{R4/(R6)} \right)$$

In case of an input range from 0 mA to 20 mA, the circuit does not need level shifting, and the op amp operates as follower. Then, the voltage drop on R3 must not exceed the upper limit (2.4 V) of the output range, and can be calculated from the equation:

$$R3 \times (I_{IN})_{MAY} = R3 \times 20 \text{ mA} \le 2.4 \text{ V}$$

(6)

If R3 = 120  $\Omega$ , the ratio R5/(R4||R6) can be calculated from Equation 5:

$$\frac{R5}{R4|R6} = \frac{GAIN}{R3} - 1 = \frac{143.75}{120} - 1 = 0.198\tag{7}$$

The output offset of the circuit can be derived from Equation 1 for  $I_{\rm IN}=4$  mA:

$$OFFSET = V_{OUT} (I_{IN} = 4 \text{ mA}) = 0.1 \text{ V}$$

$$= 4 \text{ mA} \times R3 \left( 1 + \frac{R5}{R4 \| R6} \right) - V_{REF} \frac{R5}{R4}$$

(8)

Substituting Equation 7 into Equation 8 and solving for R5/R4:

$$\frac{R5}{R4} = \frac{1}{V_{REF}} \left[ 4 \text{ mA} \times R3 \left( 1 + \frac{R5}{R4 \| R6} \right) - 0.1 \text{ V} \right] = 0.19$$

(9)

Resistors R4, R5, and R6 can now be calculated from Equations 7 and 9, if a value to one of them is given. For example if R5 =  $1000 \Omega$ , then R4 =  $5,263 \Omega$ , and R6 =  $125,310 \Omega$ .

In the actual circuit the nearest available standard resistor values were chosen for R4 and R6. The values selected were R4 =  $5.11k\Omega$  and R6 =  $124 k\Omega$ .

If these values are chosen carefully, the overall error due to substituting standard value resistors can be made less than a few percent. However, Equation 1 should be used to re-calculate the U1A op amp output for 4 mA and 20 mA input currents to ensure that the required headroom is preserved.

The absolute accuracy in this type of circuit is primarily determined by the resistors, and therefore gain and offset calibration is required to remove the error due to standard value substitution and resistor tolerances.

#### **Effect of Resistor Temperature Coefficients on Overall Error**

Equation 1 shows that the output voltage is a function of four resistors: R3, R4, R5, and R6. The sensitivity of the full-scale output voltage at TP1 to small changes in each of the four resistors was calculated using a simulation program. The input current to the circuit was 20 mA. The individual sensitivities calculated were  $S_{R3} = 1.2$ ,  $S_{R4} = 0.01$ ,  $S_{R5} = 0.00$ ,  $S_{R6} = 0.01$ . Assuming the individual temperature coefficients combine in a root-sum-square (rss) manner, then the overall full-scale drift using a 25 ppm/°C resistor for R3 and 100 ppm/°C resistors for R4, R5, and R6 is approximately:

Full scale drift

- = 100 ppm/°C $\sqrt{(0.25 \times S_{R3})^2 + S_{R4}^2 + S_{R5}^2 + S_{R6}^2)}$

- = 100 ppm/°C $\sqrt{(0.25 \times 1.2)^2 + 0.01^2 + 0.00^2 + 0.01^2)}$

- = 30 ppm/°C

The full-scale drift of 30 ppm/°C corresponds to 0.003%FSR/°C.

### Effect of Active Component Temperature Coefficients on Overall Error

The dc offsets of the AD8606 op amps and the AD7091R ADC are eliminated by the calibration procedure.

The offset drift of the ADC AD7091R internal reference is 4.5 ppm/°C typical and 25 ppm/°C maximum.

The offset drift of the AD8606 op amp is 1  $\mu$ V/°C typical and 4.5  $\mu$ V/°C maximum.

The error due to the input offset of the U1A AD8606 is referenced to the input voltage range of 2.4~V-0.48~V=1.92~V, and is therefore  $2.3~ppm/^{\circ}C$ . The error due to the U1B reference buffer is referenced to 2.5~V and is also approximately  $2~ppm/^{\circ}C$ .

The total drift error is summarized in Table 1. These errors do not include the ±1 LSB integral nonlinearity error of the AD7091R.

Table 1. Error Due to Temperature Drift

| Tuble 1. Error Bue to Temperature Britis                                                                  |                    |  |  |

|-----------------------------------------------------------------------------------------------------------|--------------------|--|--|

| Error Source                                                                                              | <b>Total Error</b> |  |  |

| Resistors (1%, 100 ppm/°C)                                                                                | ±0.0030 %FSR/°C    |  |  |

| AD7091R ( $\Delta V_{VREF}/\Delta T = 25 \text{ ppm/}^{\circ}\text{C}$ )                                  | ±0.0025 %FSR/°C    |  |  |

| AD8606, U1A ( $\Delta V_{OS}/\Delta T = 4.5 \mu V/^{\circ}C$ ), 2 ppm/ $^{\circ}C$ , Referenced to 1.92 V | ±0.0002 %FSR/°C    |  |  |

| AD8606, U1B ( $\Delta V_{OS}/\Delta T = 4.5 \mu V/^{\circ}C$ ), 2 ppm/ $^{\circ}C$ , Referenced to 2.5 V  | ±0.0002 %FSR/°C    |  |  |

| Total FSR Error Temperature Coefficient                                                                   | ±0.0059 %FSR/°C    |  |  |

| Total %FSR Error for $\Delta T = \pm 10^{\circ}C$                                                         | ±0.059 %FSR        |  |  |

CN-0336 Circuit Note

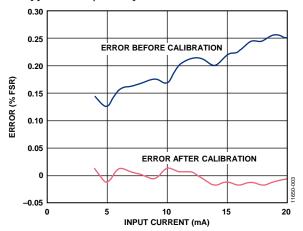

#### Test Data Before and After Two-Point Calibration

To perform the two-point calibration, 4 mA is first applied to the input, and the ADC output code is recorded as Code\_1. Then 20 mA is applied to the input, and the ADC output code is recorded as Code\_2. The gain factor is calculated by

$$GF = \frac{16 \text{ mA}}{\text{Code } 2 - \text{Code } 1}$$

(10)

The input current can now be calculated corresponding to any output code, Code\_x, using the equation:

$$I_{IN} = 4 \text{ mA} + GF (\text{Code}_x - \text{Code}_1). \tag{11}$$

The error before calibration is obtained by comparing the ideal transfer function calculated using the nominal values of the components, and real circuit transfer function without calibration. The tested circuits have been built with resistors having  $\pm 1\%$  tolerance. The test results do not include temperature changes.

The graph in Figure 3 shows test results for percent error (FSR) before and after calibration at ambient temperature. As it is shown, the maximum error before calibration is about 0.25% FSR. After calibration, the error decreases to  $\pm 0.02\%$  FSR, which approximately corresponds to 1 LSB error of the ADC.

Figure 3. Circuit Test Error Before and After Room Temperature Calibration

#### **PCB Layout Considerations**

In any circuit where accuracy is crucial, it is important to consider the power supply and ground return layout on the board. The PCB should isolate the digital and analog sections as much as possible. The PCB for this system was constructed in a simple 2-layer stack up, but 4-layer stack up gives better EMS. See the MT-031 Tutorial for information on layout and grounding and the MT-101 Tutorial for information on decoupling techniques. Decouple the power supply to the AD8606 with 10  $\mu F$  and 0.1  $\mu F$

capacitors to properly suppress noise and reduce ripple. Place the capacitors as close to the device as possible with the low ESR value, 0.1  $\mu$ F capacitor. Ceramic capacitors are advised for all high frequency decoupling. Power supply lines must have as large trace width as possible to provide low impedance path and reduce glitch effects on the supply line. The ADuM5401 *iso* Power integrated dc-to-dc converter requires power supply bypassing at the input and output supply pins. Note that low ESR bypass capacitors are required between Pin 1 and Pin 2 and between Pin 15 and Pin 16, as close to the chip pads as possible.

To suppress noise and reduce ripple, a parallel combination of at least two capacitors is required. The recommended capacitor values are 0.1  $\mu F$  and 10  $\mu F$  for  $V_{\rm DDI}$  and  $V_{\rm ISO}$ . The smaller capacitor must have a low ESR; for example, use of a ceramic capacitor is advised. The total lead length between the ends of the low ESR capacitor and the input power supply pin must not exceed 2 mm. Installing the bypass capacitor with traces more than 2 mm in length may result in data corruption. Consider bypassing between Pin 1 and Pin 8 and between Pin 9 and Pin 16 unless both common ground pins are connected together close to the package. For more information, see the ADuM5401 data sheet.

A complete documentation package including schematics, board layout, and bill of materials (BOM) can be found at www.analog.com/CN0336-DesignSupport.

#### High Voltage Capability

This PCB is designed in adherence with 2500 V basic insulation practices. High voltage testing beyond 2500 V is not recommended. Appropriate care must be taken when using this evaluation board at high voltages, and the PCB should not be relied on for safety functions because it has not been high potential tested (also known as hipot tested or dielectric withstanding voltage tested) or certified for safety.

#### **COMMON VARIATIONS**

The circuit is proven to work with good stability and accuracy with component values shown. Other precision op-amps and other ADCs can be used in this configuration to convert the 4 mA-to-20 mA input to a digital output and for other various applications for this circuit.

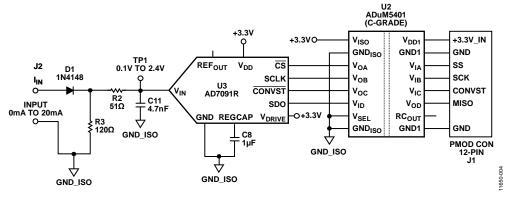

The circuit in Figure 1 can be recalculated for other than 4 mA-to-20 mA input current range, following the recommendations, given in the Circuit Design section. In these cases, when the low limit of the range is zero (0 mA to 20 mA, 0 mA to 10 mA, 0 mA to 5 mA), the conversion does not require level shifting, and the input circuit can be simplified, as is shown in Figure 4.

Circuit Note CN-0336

Figure 4. 0 mA-to-20 mA Single Supply Analog to Digital Conversion with Isolation (All Connections and Decoupling Not Shown)

The AD7091 is similar to the AD7091R, but without the voltage reference output, and the input range is equal to the power supply voltage. The AD7091 can be used with a 2.5 V ADR391 reference. The ADR391 does not require buffering, therefore a single AD8605 can be used in the circuit.

The ADR391 is a precision 2.5 V band gap voltage reference, featuring low power and high precision (9 ppm/°C of temperature drift) in a tiny TSOT package.

The AD8608 is a quad version of the AD8605 and can be used as a substitute for the AD8606, if additional precision op-amps are needed.

The AD8601, AD8602, and AD8604 are single, dual, and quad rail-to-rail, input and output, single-supply amplifiers featuring very low offset voltage and wide signal bandwidth, that can be used in place of AD8605, AD8606, and AD8608.

The AD7457 is a 12-bit, 100 kSPS, low power, SAR ADC, and can be used in combination with the ADR391 voltage reference in place of AD7091R, when a 300 kSPS throughput rate is not needed.

#### **CIRCUIT EVALUATION AND TEST**

This circuit uses the EVAL-CN0336-PMDZ circuit board, the SDP-PMD-IB1Z, and the EVAL-SDP-CB1Z system demonstration platform (SDP) evaluation board. The interposer board SDP-PMD-IB1Z and the SDP board EVAL-SDP-CB1Z have 120-pin mating connectors. The interposer board and the EVAL-CN0336-PMDZ board have 12-pin Pmod matching connectors, allowing quick setup and evaluation of the circuit's performance. The EVAL-CN0336-PMDZ board contains the circuit to be evaluated, as described in this note and the SDP evaluation board is used with the CN0336 evaluation software to capture the data from the EVAL-CN0336-PMDZ circuit board.

#### **Equipment Needed**

- PC with a USB port Windows® XP or Windows Vista® (32-bit), or Windows® 7/8 (64- or 32-bit)

- EVAL-CN0336-PMDZ circuit evaluation board

- EVAL-SDP-CB1Z SDP evaluation board

- SDP-PMD-IB1Z interposer board

- CN0336 evaluation software

• Current calibrator (4 mA to 20mA current source)

#### **Getting Started**

Load the evaluation software by placing the CN0336 evaluation software disc in the CD drive of the PC. You also can download the most up to date copy of the evaluation software from CN0336 evaluation software. Using **My Computer**, locate the drive that contains the evaluation software disc and open the Readme file. Follow the instructions in the readme file for installing and using the evaluation software.

#### **Functional Block Diagram**

Figure 5 shows a functional block diagram of the test setup.

#### Setup

- Connect the EVAL-CFTL-6V-PWRZ (+6 V dc power supply) to SDP-PMD-IB1Z Interposer Board via the dc barrel jack.

- Connect the SDP-PMD-IB1Z (interposer board) to EVAL-SDP-CB1Z SDP board via the 120-pin Con A connector.

- Connect the EVAL-SDP-CB1Z (SDP board) to the PC via the USB cable.

- Connect the EVAL-CN0336-PMDZ evaluation board to the SDP-PMD-IB1Z Interposer Board via the 12-pin header Pmod connector.

- Connect the 4 mA to 20 mA current source (current calibrator) to the EVAL-CN0336-PMDZ evaluation board via the terminal block J2.

#### Test

Launch the evaluation software. The software can communicate to the SDP board if the Analog Devices System Development Platform drivers are listed in the Device Manager. Once USB communications are established, the SDP board can be used to send, receive, and capture serial data from the EVAL-CN0336-PMDZ board. Data can be saved in the computer for various values of input current. Information and details regarding how to use the evaluation software for data capturing can be found in the CN0336 Software User Guide. Information and details on the SDP board can be found in the SDP User Guide.

A photo of the EVAL-CN0336-PMDZ evaluation board is shown in Figure 6.

CN-0336 Circuit Note

Figure 5. Test Setup Functional Block Diagram

Figure 6. Photo of EVAL-CN0336-PMDZ Board

Circuit Note CN-0336

#### **LEARN MORE**

CN0336 Design Support Package: http://www.analog.com/CN0336-DesignSupport

Chen, Baoxing, John Wynne, and Ronn Kliger. *High Speed Digital Isolators Using Microscale On-Chip Transformers*, Analog Devices, 2003

Chen, Baoxing. *iCoupler® Products with isoPower™ Technology:*Signal and Power Transfer Across Isolation Barrier Using

Microtransformers, Analog Devices, 2006

Ghiorse, Rich. Application Note AN-825, Power Supply Considerations in iCoupler\* Isolation Products, Analog Devices

Krakauer, David. "Digital Isolation Offers Compact, Low-Cost Solutions to Challenging Design Problems." Analog Dialogue. Volume 40, December 2006.

MT-031 Tutorial, *Grounding Data Converters and Solving the Mystery of "AGND" and "DGND,"* Analog Devices

MT-101 Tutorial, Decoupling Techniques, Analog Devices

Wayne, Scott. "*i*Coupler Digital Isolators Protect RS-232, RS-485, and CAN Buses in Industrial, Instrumentation, and Computer Apps, Analog Dialogue, Volume 39, Number 4, 2005.

#### **Data Sheets and Evaluation Boards**

AD8606 Data Sheet

AD7091R Data Sheet

ADuM5401 Data Sheet

#### **REVISION HISTORY**

3/14—Rev. 0 to Rev. A

Change to Circuit Function and Benefits Section......1

2/14—Revision 0: Initial Version

(Continued from first page) Circuits from the Lab reference designs are intended only for use with Analog Devices products and are the intellectual property of Analog Devices or its licensors. While you may use the Circuits from the Lab reference designs in the design of your product, no other license is granted by implication or otherwise under any patents or other intellectual property by application or use of the Circuits from the Lab reference designs. Information furnished by Analog Devices is believed to be accurate and reliable. However, Circuits from the Lab reference designs are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability, noninfringement or fitness for a particular purpose and no responsibility is assumed by Analog Devices for their use, nor for any infringements of patents or other rights of third parties that may result from their use. Analog Devices reserves the right to change any Circuits from the Lab reference designs at any time without notice but is under no obligation to do so.