# Variable Resolution, Monolithic Resolver-to-Digital Converter

# AD2S80A

#### **FEATURES**

Monolithic (BiMOS II) Tracking R/D Converter 40-Lead DIP Package 44-Terminal LCC Package 10-,12-,14-, and 16-Bit Resolution Set by User Ratiometric Conversion Low Power Consumption: 300 mW Typ Dynamic Performance Set by User High Max Tracking Rate 1040 RPS (10 Bits) Velocity Output Industrial Temperature Range Versions Military Temperature Range Versions ESD Class 2 Protection (2,000 V Min) /883 B Parts Available

#### APPLICATIONS

DC Brushless and AC Motor Control Process Control Numerical Control of Machine Tools Robotics Axis Control Military Servo Control

#### **GENERAL DESCRIPTION**

The AD2S80A is a monolithic 10-, 12-, 14-, or 16-bit tracking resolver-to-digital converter contained in a 40-lead DIP or 44terminal LCC ceramic package. It is manufactured on a BiMOS II process that combines the advantages of CMOS logic and bipolar high accuracy linear circuits on the same chip.

The converter allows users to *select their own resolution and dynamic performance with external components.* This allows the users great flexibility in defining the converter that best suits their system requirements. The converter allows users to select the resolution to be 10, 12, 14, or 16 bits and to track resolver signals rotating at up to 1040 revs per second (62,400 rpm) when set to 10-bit resolution.

The AD2S80A converts resolver format input signals into a parallel natural binary digital word using a ratiometric tracking conversion method. This ensures high-noise immunity and toler-ance of lead length when the converter is remote from the resolver.

The 10-, 12-, 14- or 16-bit output word is in a three-state digital logic available in 2 bytes on the 16 output data lines. BYTE SELECT, ENABLE and INHIBIT pins ensure easy data transfer to 8- and 16-bit data buses, and outputs are provided to allow for cycle or pitch counting in external counters.

An analog signal proportional to velocity is also available and can be used to replace a tachogenerator.

The AD2S80A operates over 50 Hz to 20,000 Hz reference frequency.

#### REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

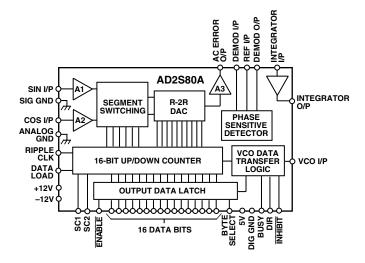

#### FUNCTIONAL BLOCK DIAGRAM

#### **PRODUCT HIGHLIGHTS**

**Monolithic.** A one chip solution reduces the package size required and increases the reliability.

**Resolution Set by User.** Two control pins are used to select the resolution of the AD2S80A to be 10, 12, 14, or 16 bits allowing the user to use the AD2S80A with the optimum resolution for each application.

**Ratiometric Tracking Conversion.** Conversion technique provides continuous output position data without conversion delay and is insensitive to absolute signal levels. It also provides good noise immunity and tolerance to harmonic distortion on the reference and input signals.

**Dynamic Performance Set by the User.** By selecting external resistor and capacitor values the user can determine bandwidth, maximum tracking rate and velocity scaling of the converter to match the system requirements. The external components required are all low cost preferred value resistors and capacitors, and the component values are easy to select using the simple instructions given.

**Velocity Output.** An analog signal proportional to velocity is available and is linear to typically one percent. This can be used in place of a velocity transducer in many applications to provide loop stabilization in servo controls and velocity feedback data.

Low Power Consumption. Typically only 300 mW.

**Military Product.** The AD2S80A is available processed in accordance with MIL-STD-883B, Class B.

#### **MODELS AVAILABLE**

Information on the models available is given in the section "Ordering Information."

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com ©Analog Devices, Inc., 1986-2015

# **AD2S80A\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### **DOCUMENTATION**

#### **Application Notes**

- AN-203: Using the AD2S80 Series Resolver-to-Digital Converters as Control Transformers

- AN-234: Digital Resolver Integration

- AN-252: Using the AD2S80 Series Resolver to Digital Converters with Synchro's; Solid State Scott-T Circuit.

- AN-263: Resolver to Digital Conversion; Simple Alternative to Optical Shaft Encoders

- AN-264: Dynamic Characteristics of Tracking Converter

- AN-265: Circuit Applications of the AD2S80 and AD2S81 Resolver to Digital

- AN-266: Passive Component Selection and Dynamic Modeling for the AD2S80 Series Resolver to Digital Converter

#### **Data Sheet**

- AD2S80A: Errata Sheet

- AD2S80A: Variable Resolution, Monolithic Resolver-to-Digital Converter Data Sheet

- AD2S81A/AD2S82A: Variable Resolution, Monolithic Resolver-to-Digital Converters Data Sheet

### REFERENCE MATERIALS

#### **Technical Articles**

- DSP Motor Control in Domestic Appliance Applications

- Single Chip DSP Motor Control Systems Catching on in Home Appliances

### DESIGN RESOURCES

- AD2S80A Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all AD2S80A EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# AD2S80A—SPECIFICATIONS (typical at 25°C unless otherwise noted)

| Parameter                                                                                                                                                                           | Conditions                                                                                    | Min Typ          |                                         | Max                                                                    | Unit                                                           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------|-----------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------|--|

| SIGNAL INPUTS<br>Frequency<br>Voltage Level<br>Input Bias Current<br>Input Impedance<br>Maximum Voltage                                                                             |                                                                                               | 50<br>1.8<br>1.0 | 2.0<br>60                               | 20,000<br>2.2<br>150<br>8                                              | Hz<br>V rms<br>nA<br>MΩ<br>V pk                                |  |

| REFERENCE INPUT<br>Frequency<br>Voltage Level<br>Input Bias Current<br>Input Impedance                                                                                              |                                                                                               | 50<br>1.0<br>1.0 | 60                                      | 20,000<br>8.0<br>150                                                   | Hz<br>V pk<br>nA<br>MΩ                                         |  |

| CONTROL DYNAMICS<br>Repeatability<br>Allowable Phase Shift<br>Tracking Rate<br>Bandwidth <sup>1</sup>                                                                               | (Signals to Reference)<br>10 Bits<br>12 Bits<br>14 Bits<br>16 Bits<br>User Selectable         | -10              |                                         | $     1 \\     +10 \\     1040 \\     260 \\     65 \\     16.25     $ | LSB<br>Degrees<br>rps<br>rps<br>rps<br>rps                     |  |

| ACCURACY<br>Angular Accuracy<br>Monotonicity<br>Missing Codes (16-Bit Resolution)                                                                                                   | A, J, S<br>B, K, T<br>L, U<br>Guaranteed Monotonic<br>A, B, J, K, S, T<br>L, U                |                  |                                         | ±8 +1 LSB<br>±4 +1 LSB<br>±2 +1 LSB<br>4<br>1                          | arc min<br>arc min<br>arc min<br>Codes<br>Code                 |  |

| VELOCITY SIGNAL<br>Linearity<br>Reversion Error<br>DC Zero Offset <sup>2</sup><br>DC Zero Offset Tempco<br>Gain Scaling Accuracy<br>Output Voltage<br>Dynamic Ripple<br>Output Load | Over Full Range<br>1 mA Load<br>Mean Value                                                    | ±8               |                                         | ±3<br>±2<br>6<br>±10<br>±10.5<br>1.5<br>1.0                            | % FSD<br>% FSD<br>mV<br>µV/°C<br>% FSD<br>V<br>% rms O/P<br>kΩ |  |

| INPUT/OUTPUT PROTECTION<br>Analog Inputs<br>Analog Outputs                                                                                                                          | Overvoltage Protection<br>Short Circuit O/P Protection                                        | ±5.6             | $\begin{array}{c}\pm8\\\pm8\end{array}$ | ±10.4                                                                  | V<br>mA                                                        |  |

| DIGITAL POSITION<br>Resolution<br>Output Format<br>Load                                                                                                                             | 10, 12, 14, and 16<br>Bidirectional Natural Binary                                            |                  |                                         | 3                                                                      | LSTTL                                                          |  |

| INHIBIT <sup>3</sup> Sense       Time to Stable Data                                                                                                                                | Logic LO to Inhibit                                                                           |                  |                                         | 600                                                                    | ns                                                             |  |

| ENABLE <sup>3</sup><br>ENABLE Time                                                                                                                                                  | Logic LO Enables Position<br>Output. Logic HI Outputs in<br>High Impedance State              | 35               |                                         | 110                                                                    | ns                                                             |  |

| BYTE SELECT <sup>3</sup><br>Sense<br>LOGIC LO<br>Time to Data Available                                                                                                             | MS Byte DB1–DB8,<br>LS Byte DB9–DB16<br>LS Byte DB1–DB8,<br>LS Byte DB9–DB16                  | 60               |                                         | 140                                                                    | ns                                                             |  |

| SHORT CYCLE INPUTS           SC1         SC2           0         0           0         1           1         0           1         1                                                | Internally Pulled High<br>(100 kΩ) to +V <sub>S</sub><br>10 Bit<br>12 Bit<br>14 Bit<br>16 Bit |                  |                                         |                                                                        |                                                                |  |

|                                                  |                                                                                                                                                                             |     |     |                 | ADZOUA      |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|-------------|--|

| Parameter                                        | Conditions                                                                                                                                                                  | Min | Тур | Max             | Unit        |  |

| DATA LOAD<br>Sense                               | Internally Pulled High (100 k $\Omega$ ) to V <sub>S</sub> . Logic LO Allows<br>Data to be Loaded into the<br>Counters from the Data Lines                                  |     | 150 | 300             | ns          |  |

| BUSY <sup>3</sup><br>Sense                       | Logic HI When Position O/P<br>Changing                                                                                                                                      |     |     |                 |             |  |

| Width<br>Load                                    | Use Additional Pull-Up                                                                                                                                                      | 200 |     | <b>600</b><br>1 | ns<br>LSTTL |  |

| DIRECTION <sup>3</sup><br>Sense<br>Max Load      | Logic HI Counting Up<br>Logic LO Counting Down                                                                                                                              |     |     | 3               | LSTTL       |  |

| RIPPLE CLOCK <sup>3</sup>                        |                                                                                                                                                                             |     |     |                 |             |  |

| Width                                            | Logic HI<br>All 1s to All 0s<br>All 0s to All 1s<br>Dependent on Input Velocity                                                                                             | 200 |     |                 |             |  |

| Reset<br>Load                                    | Before Next Busy                                                                                                                                                            | 300 |     | 3               | LSTTL       |  |

| DIGITAL INPUTS<br>High Voltage, V <sub>IH</sub>  | INHIBIT, ENABLE<br>DB1–DB16, Byte Select                                                                                                                                    | 2.0 |     |                 | v           |  |

| Low Voltage, $V_{IL}$                            | $\frac{\pm V_{S} = \pm 10.8 \text{ V}, V_{L} = 5.0 \text{ V}}{\text{INHIBIT, ENABLE}}$<br>DB1-DB16, Byte Select<br>$\pm V_{S} = \pm 13.2 \text{ V}, V_{L} = 5.0 \text{ V}$  |     |     | 0.8             | v           |  |

| DIGITAL INPUTS<br>High Current, I <sub>IH</sub>  | INHIBIT, ENABLE<br>DB1-DB16                                                                                                                                                 |     |     | ±100            | μΑ          |  |

| Low Current, $I_{IL}$                            | $\frac{\pm V_{S} = \pm 13.2 \text{ V}, V_{L} = 5.5 \text{ V}}{\text{INHIBIT, ENABLE}}$<br>DB1-DB16, Byte Select<br>$\pm V_{S} = \pm 13.2 \text{ V}, V_{L} = 5.5 \text{ V}$  |     |     | ±100            | μΑ          |  |

| DIGITAL INPUTS<br>Low Voltage, V <sub>IL</sub>   | ENABLE = HI<br>SC1, SC2, Data Load                                                                                                                                          |     |     | 1.0             | V           |  |

| Low Current, $I_{IL}$                            | $\frac{\pm V_{S} = \pm 12.0 \text{ V}, V_{L} = 5.0 \text{ V}}{\text{ENABLE} = \text{HI}}$<br>SC1, SC2, Data Load<br>$\pm V_{S} = \pm 12.0 \text{ V}, V_{L} = 5.0 \text{ V}$ |     |     | -400            | μΑ          |  |

| DIGITAL OUTPUTS<br>High Voltage, V <sub>OH</sub> | DB1–DB16<br>RIPPLE CLK, DIR<br>$\pm V_{S} = \pm 12.0 V$ , $V_{L} = 4.5 V$                                                                                                   | 2.4 |     |                 | v           |  |

| Low Voltage, V <sub>OL</sub>                     | $I_{OH} = 100 \ \mu A$<br>DB1-DB16<br>RIPPLE CLK, DIR<br>$\pm V_{S} = \pm 12.0 \ V, V_{L} = 5.5 \ V$<br>$I_{OL} = 1.2 \ mA$                                                 |     |     | 0.4             | v           |  |

| THREE-STATE LEAKAGE Current $I_L$                | DB1-DB16 Only<br>$\pm V_{S} = \pm 12.0 \text{ V}, V_{L} = 5.5 \text{ V}$                                                                                                    |     |     | ±100            | μΑ          |  |

|                                                  | $V_{OL} = 0 V$<br>$\pm V_S = \pm 12.0 V, V_L = 5.5 V$<br>$V_{OH} = 5.0 V$                                                                                                   |     |     | ±100            | μΑ          |  |

NOTES

<sup>1</sup>Refer to small signal bandwidth. <sup>2</sup>Output offset dependent on value for R6.

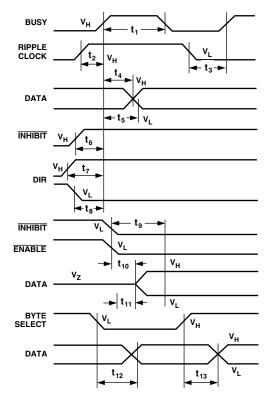

<sup>3</sup>Refer to timing diagram.

Specifications subject to change without notice.

All min and max specifications are guaranteed. Specifications in **boldface** are tested on all production units at final electrical test.

# AD2S80A—SPECIFICATIONS (typical at 25°C unless otherwise noted)

| Parameter                                                                                                                                                                                                                                                                                                                                                   | Conditions                                                                                                | Min                  | Тур                                                    | Max                                                    | Unit                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| RATIO MULTIPLIER<br>AC Error Output Scaling                                                                                                                                                                                                                                                                                                                 | 10 Bit<br>12 Bit<br>14 Bit<br>16 Bit                                                                      |                      | 177.6<br>44.4<br>11.1<br>2.775                         |                                                        | mV/Bit<br>mV/Bit<br>mV/Bit<br>mV/Bit                                                                                                       |

| PHASE SENSITIVE DETECTOR<br>Output Offset Voltage<br>Gain<br>In Phase<br>In Quadrature<br>Input Bias Current<br>Input Impedance<br>Input Voltage                                                                                                                                                                                                            | w.r.t. REF<br>w.r.t. REF                                                                                  | -0.882               | -0.9<br>60                                             | 12<br>-0.918<br>±0.02<br>150<br>±8                     | mV<br>V rms/V dc<br>V rms/V dc<br>nA<br>MΩ<br>V                                                                                            |

| INTEGRATOR<br>Open-Loop Gain<br>Dead Zone Current (Hysteresis)<br>Input Offset Voltage<br>Input Bias Current<br>Output Voltage Range                                                                                                                                                                                                                        | At 10 kHz<br>$\pm V_S = \pm 10.8 \text{ V dc}$                                                            | 57<br>±7             | 100<br>1<br>60                                         | 63<br>5<br>150                                         | dB<br>nA/LSB<br>mV<br>nA<br>V                                                                                                              |

| VCO<br>Maximum Rate<br>VCO Rate<br>VCO Power Supply Sensitivity<br>Increase<br>Decrease<br>Input Offset Voltage<br>Input Bias Current<br>Input Bias Current Tempco<br>Input Voltage Range<br>Linearity of Absolute Rate<br>Full Range<br>Over 0% to 50% of Full Range<br>Reversion Error<br>Sensitivity of Reversion Error<br>to Symmetry of Power Supplies | $\pm V_{S} = \pm 12 V dc$ Positive Direction<br>Negative Direction<br>$+V_{S}$ $-V_{S}$ $+V_{S}$ $-V_{S}$ | 7.1<br>7.1           | 7.9<br>7.9<br>+0.5<br>-8.0<br>+2.0<br>1<br>70<br>-1.22 | 1.1<br>8.7<br>8.7<br>5<br>380<br>±8<br><2<br><1<br>1.5 | MHz<br>kHz/µA<br>kHz/µA<br>%/V<br>%/V<br>%/V<br>mV<br>nA<br>nA/°C<br>V<br>% FSD<br>% FSD<br>% FSD<br>% FSD<br>% FSD<br>% V of<br>Asymmetry |

| $\begin{array}{c} \text{POWER SUPPLIES} \\ \text{Voltage Levels} \\ + \text{V}_{\text{S}} \\ - \text{V}_{\text{S}} \\ + \text{V}_{\text{L}} \\ \text{Current} \\ \pm \text{I}_{\text{S}} \\ \pm \text{I}_{\text{S}} \\ \pm \text{I}_{\text{L}} \end{array}$                                                                                                 | $\begin{array}{c} \pm V_{S} @ \pm 12 \ V \\ \pm V_{S} @ 13.2 \ V \\ + V_{L} @ \pm 5.0 \ V \end{array}$    | +10.8<br>-10.8<br>+5 | ±12<br>±19<br>±0.5                                     | +13.2<br>-13.2<br>+13.2<br>±23<br>±30<br>±1.5          | V<br>V<br>V<br>mA<br>mA<br>mA                                                                                                              |

Specification subject to change without notice.

All min and max specifications are guaranteed. Specifications in **boldface** are tested on all production units at final electrical test.

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD2S80A features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

#### **RECOMMENDED OPERATING CONDITIONS**

| $+v_{\rm S}$                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------|

| $-V_S$ $-14 V dc$                                                                                                                     |

| $+V_L$ $V_S$                                                                                                                          |

| Reference 14 V to -V <sub>S</sub>                                                                                                     |

| SIN 14 V to -V <sub>S</sub>                                                                                                           |

| COS 14 V to -V <sub>S</sub>                                                                                                           |

| Any Logical Input $\dots \dots \dots$ |

| Demodulator Input 14 V to -V <sub>S</sub>                                                                                             |

| Integrator Input 14 V to -V <sub>S</sub>                                                                                              |

| VCO Input 14 V to -V <sub>s</sub>                                                                                                     |

| Power Dissipation                                                                                                                     |

| Operating Temperature                                                                                                                 |

| Commercial (JD, KD, LD)                                                                                                               |

| Industrial (AD, BD)40°C to +85°C                                                                                                      |

| Extended (SD, SE, TD, TE, UD, UE) –55°C to +125°C                                                                                     |

| $\theta_{IC}^{3}$ (40-Lead DIP 883 Parts Only) 11°C/W                                                                                 |

| $\theta_{\rm IC}^3$ (44-Terminal LCC 883 Parts Only) 10°C/W                                                                           |

| Storage Temperature (All Grades)65°C to +150°C                                                                                        |

| Lead Temperature (Soldering, 10 sec) 300°C                                                                                            |

|                                                                                                                                       |

#### **CAUTION NOTES:**

<sup>1</sup>Absolute Maximum Ratings are those values beyond which damage to the device may occur.

<sup>2</sup>Correct polarity voltages must be maintained on the  $+V_s$  and  $-V_s$  pins.

<sup>3</sup>With reference to Appendix C of MIL-M-38510.

#### Bit Weight Table

| Binary<br>Bits (N) | Resolution (2 <sup>N</sup> ) | Degrees<br>/Bit | Minutes<br>/Bit | Seconds<br>/Bit |

|--------------------|------------------------------|-----------------|-----------------|-----------------|

| 0                  | 1                            | 360.0           | 21600.0         | 1296000.0       |

| 1                  | 2                            | 180.0           | 10800.0         | 648000.0        |

| 2                  | 4                            | 90.0            | 5400.0          | 324000.0        |

| 3                  | 8                            | 45.0            | 2700.0          | 162000.0        |

| 4                  | 16                           | 22.5            | 1350.0          | 81000.0         |

| 5                  | 32                           | 11.25           | 675.0           | 40500.0         |

| 6                  | 64                           | 5.625           | 337.5           | 20250.0         |

| 7                  | 128                          | 2.8125          | 168.75          | 10125.0         |

| 8                  | 256                          | 1.40625         | 84.375          | 5062.5          |

| 9                  | 512                          | 0.703125        | 42.1875         | 2531.25         |

| 10                 | 1024                         | 0.3515625       | 21.09375        | 1265.625        |

| 11                 | 2048                         | 0.1757813       | 10.546875       | 632.8125        |

| 12                 | 4096                         | 0.0878906       | 5.273438        | 316.40625       |

| 13                 | 8192                         | 0.0439453       | 2.636719        | 158.20313       |

| 14                 | 16384                        | 0.0219727       | 1.318359        | 79.10156        |

| 15                 | 32768                        | 0.0109836       | 0.659180        | 39.55078        |

| 16                 | 65536                        | 0.0054932       | 0.329590        | 19.77539        |

| 17                 | 131072                       | 0.0027466       | 0.164795        | 9.88770         |

| 18                 | 262144                       | 0.0013733       | 0.082397        | 4.94385         |

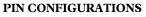

#### **PIN DESIGNATIONS**

| MNEMONIC       | DESCRIPTION                                |

|----------------|--------------------------------------------|

| REFERENCE I/P  | REFERENCE SIGNAL INPUT                     |

| DEMOD I/P      | DEMODULATOR INPUT                          |

| AC ERROR O/P   | RATIO MULTIPLIER OUTPUT                    |

| cos            | COSINE INPUT                               |

| ANALOG GROUND  | POWER GROUND                               |

| SIGNAL GROUND  | RESOLVER SIGNAL GROUND                     |

| SIN            | SINE INPUT                                 |

| +Vs            | POSITIVE POWER SUPPLY                      |

| DB1–DB16       | PARALLEL OUTPUT DATA                       |

| VL             | LOGIC POWER SUPPLY                         |

| ENABLE         | LOGIC HI-OUTPUT DATA IN HIGH IMPEDANCE     |

|                | STATE, LOGIC LO PRESENTS DATA TO THE       |

|                | OUTPUT LATCHES                             |

| BYTE SELECT    | LOGIC HI-MOST SIGNIFICANT BYTE TO DB1–DB8  |

|                | LOGIC LO-LEAST SIGNIFICANT BYTE TO DB1–DB8 |

| INHIBIT        | LOGIC LO INHIBITS DATA TRANSFER TO         |

|                | OUTPUT LATCHES                             |

| DIGITAL GROUND | DIGITAL GROUND                             |

| SC1-SC2        | SELECT CONVERTER RESOLUTION                |

| DATA LOAD      | LOGIC LO DB1–DB16 INPUTS LOGIC HI DB1–D16  |

|                | OUTPUTS                                    |

| BUSY           | CONVERTER BUSY, DATA NOT VALID WHILE       |

|                | BUSY HI                                    |

| DIRECTION      | LOGIC STATE DEFINES DIRECTION              |

|                | OF INPUT SIGNAL ROTATION                   |

| RIPPLE CLOCK   | POSITIVE PULSE WHEN CONVERTER OUTPUT       |

|                | CHANGES FROM 1S TO ALL 0S OR VICE VERSA    |

| -Vs            | NEGATIVE POWER SUPPLY                      |

| VCO I/P        | VCO INPUT                                  |

| INTEGRATOR I/P | INTEGRATOR INPUT                           |

| INTEGRATOR O/P | INTEGRATOR OUTPUT                          |

| DEMOD O/P      | DEMODULATOR OUTPUT                         |

|                |                                            |

#### CONNECTING THE CONVERTER

The power supply voltages connected to  $+V_S$  and  $-V_S$  pins should be +12 V dc and -12 V dc and must not be reversed. The voltage applied to  $V_L$  can be 5 V dc to  $+V_S$ .

It is recommended that the decoupling capacitors are connected in parallel between the power lines  $+V_S$ ,  $-V_S$  and ANALOG GROUND adjacent to the converter. Recommended values are 100 nF (ceramic) and 10  $\mu$ F (tantalum). Also capacitors of 100 nF and 10  $\mu$ F should be connected between  $+V_L$  and DIGITAL GROUND adjacent to the converter.

When more than one converter is used on a card, then separate decoupling capacitors should be used for each converter.

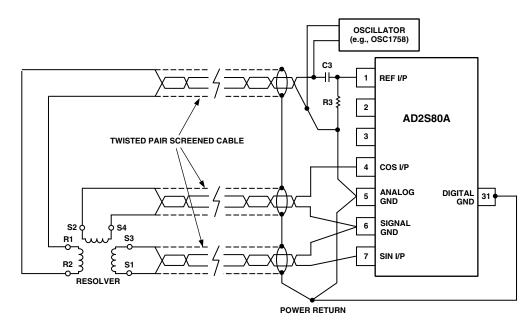

The resolver connections should be made to the SIN and COS inputs, REFERENCE INPUT and SIGNAL GROUND as shown in Figure 7 and described in section "CONNECTING THE RESOLVER."

The two signal ground wires from the resolver should be joined at the SIGNAL GROUND pin of the converter to minimize the coupling between the sine and cosine signals. For this reason it is also recommended that the resolver is connected using individually screened twisted pair cables with the sine, cosine and reference signals twisted separately. SIGNAL GROUND and ANALOG GROUND are connected internally. ANALOG GROUND and DIGITAL GROUND must be connected externally.

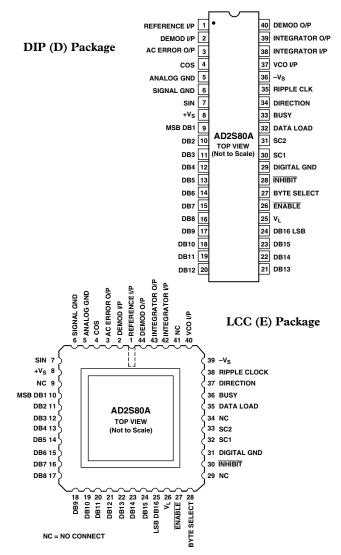

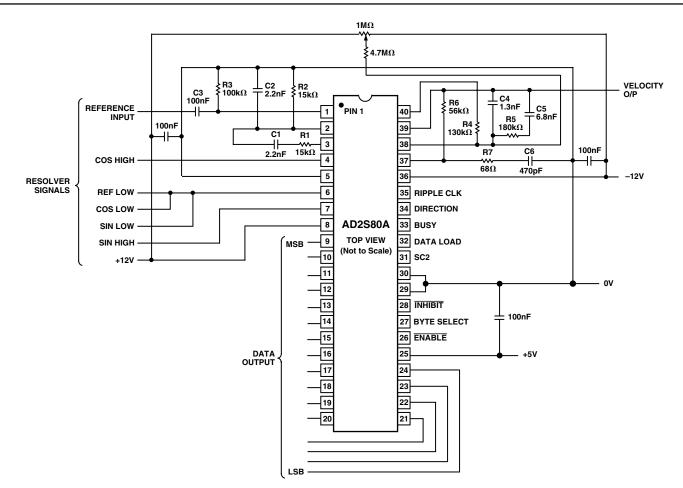

The external components required should be connected as shown in Figure 1.

#### **CONVERTER RESOLUTION**

Two major areas of the AD2S80A specification can be selected by the user to optimize the total system performance. The resolution of the digital output is set by the logic state of the inputs SC1 and SC2 to be 10, 12, 14, or 16 bits; and the dynamic characteristics of bandwidth and tracking rate are selected by the choice of external components.

The choice of the resolution will affect the values of R4 and R6 which scale the inputs to the integrator and the VCO respectively (see section COMPONENT SELECTION). If the resolution is changed, then new values of R4 and R6 must be switched into the circuit.

Note: When changing resolution under dynamic conditions, do it when the BUSY is low, i.e., when Data is not changing.

Figure 1. AD2S80A Connection Diagram

#### **CONVERTER OPERATION**

When connected in a circuit such as shown in Figure 1 the AD2S80A operates as a tracking resolver-to-digital converter and forms a Type 2 closed-loop system. The output will automatically follow the input for speeds up to the selected maximum tracking rate. No convert command is necessary as the conversion is automatically initiated by each LSB increment, or decrement, of the input. Each LSB change of the converter initiates a BUSY pulse.

The AD2S80A is remarkably tolerant of input amplitude and frequency variation because the conversion depends only on the ratio of the input signals. Consequently there is no need for accurate, stable oscillator to produce the reference signal. The inclusion of the phase sensitive detector in the conversion loop ensures a high immunity to signals that are not coherent or are in quadrature with the reference signal.

#### SIGNAL CONDITIONING

The amplitude of the SINE and COSINE signal inputs should be maintained within 10% of the nominal values if full performance is required from the velocity signal.

The digital position output is relatively insensitive to amplitude variation. Increasing the input signal levels by more than 10% will result in a loss in accuracy due to internal overload. Reducing levels will result in a steady decline in accuracy. With the signal levels at 50% of the correct value, the angular error will increase to an amount equivalent to 1.3 LSB. At this level the repeatability will also degrade to 2 LSB and the dynamic response will also change, since the dynamic characteristics are proportional to the signal level.

The AD2S80A will not be damaged if the signal inputs are applied to the converter without the power supplies and/or the reference.

#### **REFERENCE INPUT**

The amplitude of the reference signal applied to the converter's input is not critical, but care should be taken to ensure it is kept within the recommended operating limits.

The AD2S80A will not be damaged if the reference is supplied to the converter without the power supplies and/or the signal inputs.

#### HARMONIC DISTORTION

The amount of harmonic distortion allowable on the signal and reference lines is 10%.

Square waveforms can be used but the input levels should be adjusted so that the average value is 1.9 V rms. (For example, a square wave should be 1.9 V peak.) Triangular and sawtooth waveforms should have a amplitude of 2 V rms.

Note: The figure specified of 10% harmonic distortion is for calibration convenience only.

#### **POSITION OUTPUT**

The resolver shaft position is represented at the converter output by a natural binary parallel digital word. As the digital position output of the converter passes through the major carries, i.e., all "1s" to all "0s" or the converse, a RIPPLE CLOCK (RC) logic output is initiated indicating that a revolution or a pitch of the input has been completed.

The direction of input rotation is indicated by the DIRECTION (DIR) logic output. This direction data is always valid in advance of a RIPPLE CLOCK pulse and, as it is internally latched, only changing state (1 LSB min change) with a corresponding change in direction.

Both the RIPPLE CLOCK pulse and the DIRECTION data are unaffected by the application of the INHIBIT. The static positional accuracy quoted is the worst case error that can occur over the full operating temperature excluding the effects of offset signals at the INTEGRATOR INPUT (which can be trimmed out—see Figure 1), and with the following conditions: input signal amplitudes are within 10% of the nominal; phase shift between signal and reference is less than 10 degrees.

These operating conditions are selected primarily to establish a repeatable acceptance test procedure which can be traced to national standards. In practice, the AD2S80A can be used well outside these operating conditions providing the above points are observed.

#### VELOCITY SIGNAL

The tracking converter technique generates an internal signal at the output of the integrator (the INTEGRATOR OUTPUT pin) that is proportional to the rate of change of the input angle. This is a dc analog output referred to as the VELOCITY signal.

In many applications it is possible to use the velocity signal of the AD2S80A to replace a conventional tachogenerator.

#### DC ERROR SIGNAL

The signal at the output of the phase sensitive detector (DEMODULATOR OUTPUT) is the signal to be nulled by the tracking loop and is, therefore, proportional to the error between the input angle and the output digital angle. This is the dc error of the converter; and as the converter is a Type 2 servo loop, it will increase if the output fails to track the input for any reason. It is an indication that the input has exceeded the maximum tracking rate of the converter or, due to some internal malfunction, the converter is unable to reach a null. By connecting two external comparators, this voltage can be used as a "built-in-test."

#### **COMPONENT SELECTION**

The following instructions describe how to select the external components for the converter in order to achieve the required bandwidth and tracking rate. In all cases the nearest "preferred value" component should be used, and a 5% tolerance will not degrade the overall performance of the converter. Care should be taken that the resistors and capacitors will function over the required operating temperature range. The components should be connected as shown in Figure 1.

PG compatible software is available to help users select the optimum component values for the AD2S80A, and display the transfer gain, phase and small step response.

For more detailed information and explanation, see section "CIR-CUIT FUNCTIONS AND DYNAMIC PERFORMANCE."

#### 1. HF Filter (R1, R2, C1, C2)

The function of the HF filter is to remove any dc offset and to reduce the amount of noise present on the signal inputs to the AD2S80A, reaching the Phase Sensitive Detector and affecting the outputs. R1 and C2 may be omitted-in which case R2 = R3 and C1 = C3, calculated below—but their use is particularly recommended if noise from switch mode power supplies and brushless motor drive is present.

Values should be chosen so that

$$C1 = C2 = 15 \ k\Omega \le R1 = R2 \le 56 \ k\Omega$$

$$C1 = C2 = \frac{1}{2\pi R1 f_{REF}}$$

and  $f_{REF}$  = Reference frequency (Hz)

This filter gives an attenuation of three times at the input to the phase sensitive detector.

2. Gain Scaling Resistor (R4) If R1, C2 are used:

$$R4 = \frac{E_{DC}}{100 \times 10^{-9}} \times \frac{1}{3} \Omega$$

$\boldsymbol{E}$

where  $100 \times 10^{-9}$  = current/LSB If R1, C2 are not used:

$$R4 = \frac{E_{DC}}{100 \times 10^{-9}} \Omega$$

where  $E_{DC} = 160 \times 10^{-3}$  for 10 bits resolution

$$= 40 \times 10^{-3}$$

for 12 bits

$$= 10 \times 10^{-3}$$

for 14 bits

$$= 2.5 \times 10^{-3}$$

for 16 bits

= Scaling of the DC ERROR in volts

3. AC Coupling of Reference Input (R3, C3) Select R3 and C3 so that there is no significant phase shift at the reference frequency. That is,

$$R3 = 100 k\Omega$$

$$C3 > \frac{1}{R3 \times f_{REE}} F$$

#### with R3 in $\Omega$ .

#### 4. Maximum Tracking Rate (R6)

The VCO input resistor R6 sets the maximum tracking rate of the converter and hence the velocity scaling as at the max tracking rate, the velocity output will be 8 V.

Decide on your maximum tracking rate, "T," in revolutions per second. Note that "T" must not exceed the maximum tracking rate or 1/16 of the reference frequency.

$$R6 = \frac{6.32 \times 10^{10}}{T \times n} \,\Omega$$

where n = bits per revolution= 1,024 for 10 bits resolution

= 16,384 for 14 bits

- 5. Closed-Loop Bandwidth Selection (C4, C5, R5)

- a. Choose the closed-loop bandwidth  $(f_{BW})$  required ensuring that the ratio of reference frequency to bandwidth does not exceed the following guidelines:

| Resolution | Ratio of Reference Frequency/Bandwidth |

|------------|----------------------------------------|

| 10         | 2.5 : 1                                |

| 12         | 4 : 1                                  |

| 14         | 6 :1                                   |

| 16         | 7.5 :1                                 |

Typical values may be 100 Hz for a 400 Hz reference frequency and 500 Hz to 1000 Hz for a 5 kHz reference frequency.

b. Select C4 so that

$$C4 = \frac{21}{R6 \times f_{BW}^2} F$$

with R6 in  $\Omega$  and f<sub>BW</sub>, in Hz selected above.

c. C5 is given by

d. R5 is given by

$R5 = \frac{4}{2 \times \pi \times f_{BW} \times C5} \,\Omega$

$C5 = 5 \times C4$

6. VCO Phase Compensation

The following values of C6 and R7 should be fitted.

$$C6 = 470 \ pF, \ R7 = 68 \ \Omega$$

7. Offset Adjust

Offsets and bias currents at the integrator input can cause an additional positional offset at the output of the converter of 1 arc minute typical, 5.3 arc minutes maximum. If this can be tolerated, then R8 and R9 can be omitted from the circuit.

If fitted, the following values of R8 and R9 should be used:

$$R8 = 4.7 M\Omega$$

,  $R9 = 1 M\Omega$  potentiometer

To adjust the zero offset, ensure the resolver is disconnected and all the external components are fitted. Connect the COS pin to the REFERENCE INPUT and the SIN pin to the SIGNAL GROUND and with the power and reference applied, adjust the potentiometer to give all "0s" on the digital output bits.

The potentiometer may be replaced with select on test resistors if preferred.

#### DATA TRANSFER

To transfer data the  $\overline{\text{INHIBIT}}$  input should be used. The data will be valid 600 ns after the application of a logic "LO" to the  $\overline{\text{INHIBIT}}$ . This is regardless of the time when the  $\overline{\text{INHIBIT}}$  is applied and allows time for an active BUSY to clear. By using the  $\overline{\text{ENABLE}}$  input the two bytes of data can be transferred after which the  $\overline{\text{INHIBIT}}$  should be returned to a logic "HI" state to enable the output latches to be updated.

#### **BUSY Output**

The validity of the output data is indicated by the state of the BUSY output. When the input to the converter is changing, the signal appearing on the BUSY output is a series of pulses at TTL level. A BUSY pulse is initiated each time the input moves by the analog equivalent of one LSB and the internal counter is incremented or decremented.

#### **INHIBIT** Input

The INHIBIT logic input only inhibits the data transfer from the up-down counter to the output latches and, therefore, does not interrupt the operation of the tracking loop. Releasing the INHIBIT automatically generates a BUSY pulse to refresh the output data.

#### **ENABLE** Input

The  $\overline{\text{ENABLE}}$  input determines the state of the output data. A logic "HI" maintains the output data pins in the high impedance condition, and the application of a logic "LO" presents the data in the latches to the output pins. The operation of the  $\overline{\text{ENABLE}}$  has no effect on the conversion process.

#### **BYTE SELECT Input**

The BYTE SELECT input selects the byte of the position data to be presented at the data output DB1 to DB8. The least significant byte will be presented on data output DB9 to DB16 (with the ENABLE input taken to a logic "LO") regardless of the state of the BYTE SELECT pin. Note that when the AD2S80A is used with a resolution less than 16 bits the unused data lines are pulled to a logic "LO." A logic "HI" on the BYTE SELECT input will present the eight most significant data bits on data output DB1 and DB8. A logic "LO" will present the least significant byte on data outputs 1 to 8, i.e., data outputs 1 to 8 will duplicate data outputs 9 to 16.

The operation of the BYTE SELECT has no effect on the conversion process of the converter.

#### **RIPPLE CLOCK**

As the output of the converter passes through the major carry, i.e., all "1s" to all "0s" or the converse, a positive going edge on the RIPPLE CLOCK (RC) output is initiated indicating that a revolution, or a pitch, of the input has been completed.

The minimum pulse width of the ripple clock is 300 ns. RIPPLE CLOCK is normally set high before a BUSY pulse and resets before the next positive going edge of the next consecutive pulse.

The only exception to this is when DIR changes while the RIPPLE CLOCK is high. Resetting of the RIPPLE clock will only occur if the DIR remains stable for two consecutive positive BUSY pulse edges.

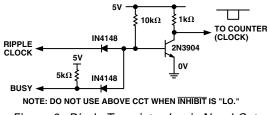

If the AD2S80A is being used in a pitch and revolution counting application, the ripple and busy will need to be gated to prevent false decrement or increment (see Figure 2).

RIPPLE CLOCK is unaffected by INHIBIT.

Figure 2. Diode Transistor Logic Nand Gate

#### **DIRECTION Output**

The DIRECTION (DIR) logic output indicates the direction of the input rotation. Any change in the state of DIR precedes the corresponding BUSY, DATA and RIPPLE CLOCK updates. DIR can be considered as an asynchronous output and can make multiple changes in state between two consecutive LSB update cycles. This corresponds to a change in input rotation direction but less than 1 LSB.

#### DIGITAL TIMING

| PARAMETER       | T <sub>MIN</sub> | T <sub>MAX</sub> | CONDITION                                          |

|-----------------|------------------|------------------|----------------------------------------------------|

| t <sub>1</sub>  | 200              | 600              | BUSY WIDTH V <sub>H</sub> -V <sub>H</sub>          |

| t <sub>2</sub>  | 10               | 25               | RIPPLE CLOCK V <sub>H</sub> TO BUSY V <sub>H</sub> |

| t <sub>3</sub>  | 470              | 580              | RIPPLE CLOCK VL TO NEXT BUSY VH                    |

| t <sub>4</sub>  | 16               | 45               | BUSY V <sub>H</sub> TO DATA V <sub>H</sub>         |

| t <sub>5</sub>  | 3                | 25               | BUSY V <sub>H</sub> TO DATA VL                     |

| t <sub>6</sub>  | 70               | 140              | INHIBIT V <sub>H</sub> TO BUSY V <sub>H</sub>      |

| t <sub>7</sub>  | 485              | 625              | MIN DIR $V_H$ TO BUSY $V_H$                        |

| t <sub>8</sub>  | 515              | 670              | MIN DIR V <sub>H</sub> TO BUSY V <sub>H</sub>      |

| t <sub>9</sub>  | -                | 600              | INHIBIT VL TO DATA STABLE                          |

| t <sub>10</sub> | 40               | 110              | ENABLE VL TO DATA VH                               |

| t <sub>11</sub> | 35               | 110              | ENABLE VL TO DATA VL                               |

| t <sub>12</sub> | 60               | 140              | BYTE SELECT VL TO DATA STABLE                      |

| t <sub>13</sub> | 60               | 125              | BYTE SELECT V <sub>H</sub> TO DATA STABLE          |

#### CIRCUIT FUNCTIONS AND DYNAMIC PERFORMANCE

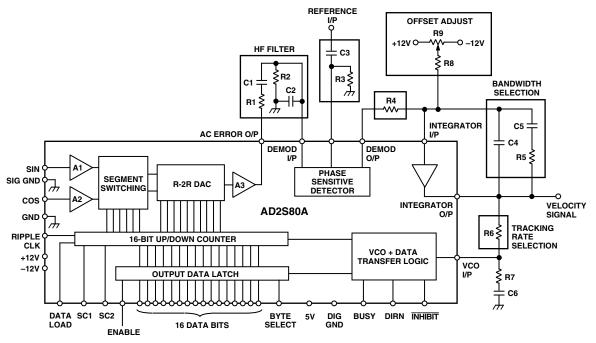

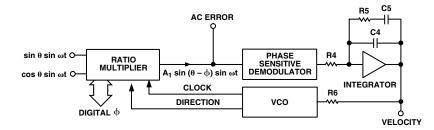

The AD2S80A allows the user greater flexibility in choosing the dynamic characteristics of the resolver-to-digital conversion to ensure the optimum system performance. The characteristics are set by the external components shown in Figure 1, and the section "COMPONENT SELECTION" explains how to select desired maximum tracking rate and bandwidth values. The following paragraphs explain in greater detail the circuit of the AD2S80A and the variations in the dynamic performance available to the user.

#### Loop Compensation

The AD2S80A (connected as shown in Figure 1) operates as a Type 2 tracking servo loop where the VCO/counter combination and Integrator perform the two integration functions inherent in a Type 2 loop.

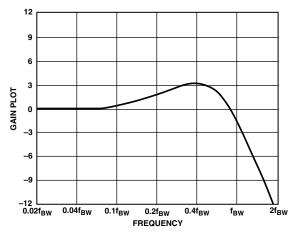

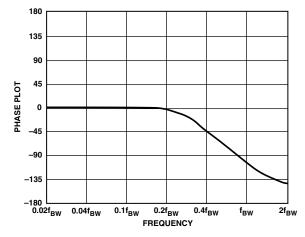

Additional compensation in the form of a pole/zero pair is required to stabilize any Type 2 loop to avoid the loop gain characteristic crossing the 0 dB axis with 180° of additional phase lag, as shown in Figure 5.

This compensation is implemented by the integrator components (R4, C4, R5, C5).

The overall response of such a system is that of a unity gain second order low pass filter, with the angle of the resolver as the input and the digital position data as the output.

The AD2S80A does not have to be connected as tracking converter, parts of the circuit can be used independently. This is particularly true of the Ratio Multiplier which can be used as a control transformer (see Application Note).

A block diagram of the AD2S80A is given in Figure 3.

Figure 3. Functional Diagram

#### **Ratio Multiplier**

The ratio multiplier is the input section of the AD2S80A and compares the signal from the resolver input angle,  $\theta$ , to the digital angle,  $\phi$ , held in the counter. Any difference between these two angles results in an analog voltage at the AC ERROR OUTPUT. This circuit function has historically been called a "Control Transformer" as it was originally performed by an electromechanical device known by that name.

The AC ERROR signal is given by

where  $\omega = 2 \pi f_{REF}$

$f_{REF}$  = reference frequency

A1, the gain of the ratio multiplier stage is 14.5.

So for 2 V rms inputs signals AC ERROR output in volts/(bit of error)

$$=2 \times \sin\left(\frac{360}{n}\right) \times A1$$

where n = bits per rev

- = 1,024 for 10 bits resolution

- = 4,096 for 12 bits

- = 16,384 for 14 bits

- = 65,536 for 16 bits

giving an AC ERROR output

= 178 mV/bit @ 10 bits resolution

= 44.5 mV/bit @ 12 bits

= 11.125 mV/bit @ 14 bits

= 2.78 mV/bit @ 16 bits

The ratio multiplier will work in exactly the same way whether the AD2S80A is connected as a tracking converter or as a control transformer, where data is preset into the counters using the DATA LOAD pin.

#### **HF Filter**

The AC ERROR OUTPUT may be fed to the PSD via a simple ac coupling network (R2, C1) to remove any dc offset at this point. Note, however, that the PSD of the AD2S80A is a wideband demodulator and is capable of aliasing HF noise down to within the loop bandwidth. This is most likely to happen where the resolver is situated in particularly noisy environments, and the user is advised to fit a simple HF filter R1, C2 prior to the phase sensitive demodulator.

The attenuation and frequency response of a filter will affect the loop gain and must be taken into account in deriving the loop transfer function. The suggested filter (R1, C1, R2, C2) is shown in Figure 1 and gives an attenuation at the reference frequency ( $f_{REF}$ ) of 3 times at the input to the phase sensitive demodulator .

Values of components used in the filter must be chosen to ensure that the phase shift at  $f_{REF}$  is within the allowable signal to reference phase shift of the converter.

#### Phase Sensitive Demodulator

The phase sensitive demodulator is effectively ideal and develops a mean dc output at the DEMODULATOR OUTPUT pin of

$$\frac{\pm 2\sqrt{2}}{\pi}$$

× (DEMODULATOR INPUT rms voltage)

for sinusoidal signals in phase or antiphase with the reference (for a square wave the DEMODULATOR OUTPUT voltage will equal the DEMODULATOR INPUT). This provides a signal at the DEMODULATOR OUTPUT which is a dc level proportional to the positional error of the converter.

DC Error Scaling = 160 mV/bit (10 bits resolution)

= 40 mV/bit (12 bits resolution)

= 10 mV/bit (14 bits resolution) = 2.5 mV/bit (16 bits resolution)

When the tracking loop is closed, this error is nulled to zero unless the converter input angle is accelerating.

#### Integrator

The integrator components (R4, C4, R5, C5) are external to the AD2S80A to allow the user to determine the optimum dynamic characteristics for any given application. The section "COMPO-NENT SELECTION" explains how to select components for a chosen bandwidth.

Since the output from the integrator is fed to the VCO INPUT, it is proportional to velocity (rate of change of output angle) and can be scaled by selection of R6, the VCO input resistor. This is explained in the section "VOLTAGE CONTROLLED OSCIL-LATOR (VCO)" below.

To prevent the converter from "flickering" (i.e., continually toggling by  $\pm 1$  bit when the quantized digital angle,  $\phi$ , is not an exact representation of the input angle,  $\theta$ ) feedback is internally applied from the VCO to the integrator input to ensure that the VCO will only update the counter when the error is greater than or equal to 1 LSB. In order to ensure that this feedback "hysteresis" is set to 1 LSB the input current to the integrator must be scaled to be 100 nA/bit. Therefore,

$$R4 = \frac{DC \ Error \ Scaling \ (mV/bit \ )}{100 \ (nA/bit)}$$

Any offset at the input of the integrator will affect the accuracy of the conversion as it will be treated as an error signal and offset the digital output. One LSB of extra error will be added for each 100 nA of input bias current. The method of adjusting out this offset is given in the section "COMPONENT SELECTION."

#### Voltage Controlled Oscillator (VCO)

The VCO is essentially a simple integrator feeding a pair of dc level comparators. Whenever the integrator output reaches one of the comparator threshold voltages, a fixed charge is injected into the integrator input to balance the input current. At the same time the counter is clocking either up or down, dependent on the polarity of the input current. In this way the counter is clocked at a rate proportional to the magnitude of the input current of the VCO.

During the reset period the input continues to be integrated, the reset period is constant at 400 ns.

The VCO rate is fixed for a given input current by the VCO scaling factor:

The tracking rate in rps per  $\mu$ A of VCO input current can be found by dividing the VCO scaling factor by the number of LSB changes per rev (i.e., 4096 for 12-bit resolution).

The input resistor R6 determines the scaling between the converter velocity signal voltage at the INTEGRATOR OUTPUT pin and the VCO input current. Thus to achieve a 5 V output at 100 rps (6000 rpm) and 12-bit resolution the VCO input current must be:

$$(100 \times 4096)/(7900) = 51.8 \,\mu A$$

Thus, R6 would be set to:  $5/(51.8 \times 10^{-6}) = 96 \text{ k}\Omega$

The velocity offset voltage depends on the VCO input resistor, R6, and the VCO bias current and is given by

Velocity Offset Voltage =  $R6 \times (VCO \ bias \ current)$

The temperature coefficient of this offset is given by

Velocity Offset Tempco =  $R6 \times (VCO \ bias \ current \ tempco)$

where the VCO bias current tempco is typically -1.22 nA/°C.

The maximum recommended rate for the VCO is 1.1 MHz which sets the maximum possible tracking rate.

Since the minimum voltage swing available at the integrator output is  $\pm 8$  V, this implies that the minimum value for R6 is 57 k $\Omega$ . As

$$Max Current = \frac{1.1 \times 10^{6}}{7.9 \times 10^{3}} = 139 \ \mu A$$

$$Min Value R6 = \frac{8}{139 \times 10^{-6}} = 57 \ k\Omega$$

#### **Transfer Function**

By selecting components using the method outlined in the section "Component Selection," the converter will have a critically damped time response and maximum phase margin. The Closed-Loop Transfer Function is given by:

$$\frac{\theta_{OUT}}{\theta_{IN}} = \frac{14(1+s_N)}{(s_N+2.4)(s_N^2+3.4s_N+5.8)}$$

where, s<sub>N</sub>, the normalized frequency variable is:

$$s_N = \frac{2}{\pi} \frac{s}{f_{BW}}$$

and  $f_{BW}\,$  is the closed-loop 3 dB bandwidth (selected by the choice of external components).

The acceleration K<sub>A</sub>, is given approximately by

$$K_A = 6 \times (f_{BW})^2 \text{ sec}^{-2}$$

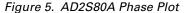

The normalized gain and phase diagrams are given in Figures 4 and 5.

Figure 4. AD2S80A Gain Plot

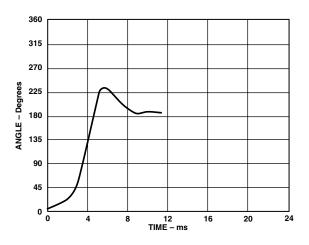

The small signal step response is shown in Figure 6. The time from the step to the first peak is  $t_1$  and the  $t_2$  is the time from

the step until the converter is settled to 1 LSB. The times  $t_1$  and  $t_2$  are given approximately by

$$t_1 = \frac{1}{f_{BW}}$$

$$t_2 = \frac{5}{f_{BW}} \times \frac{R}{12}$$

where R = resolution, i.e., 10, 12, 14, or 16.

The large signal step response (for steps greater than 5 degrees) applies when the error voltage exceeds the linear range of the converter.

Typically the converter will take 3 times longer to reach the first peak for a 179 degrees step.

In response to a velocity step, the velocity output will exhibit the same time response characteristics as outlined above for the position output.

#### **ACCELERATION ERROR**

A tracking converter employing a Type 2 servo loop does not suffer any velocity lag, however, there is an additional error due to acceleration. This additional error can be defined using the acceleration constant  $K_A$  of the converter.

$$K_A = \frac{Input \ Acceleration}{Error \ in \ Output \ Angle}$$

The numerator and denominator must have consistent angular units. For example if  $K_A$  is in sec<sup>-2</sup>, then the input acceleration may be specified in degrees/sec<sup>2</sup> and the error output in degrees. Angular measurement may also be specified using radians, minutes of arc, LSBs, etc.

$K_A$  does not define maximum input acceleration, only the error due to it's acceleration. The maximum acceleration allowable before the converter loses track is dependent on the angular accuracy requirements of the system.

Angular Accuracy  $\times$  K<sub>A</sub> = Degrees/sec<sup>2</sup>

$K_A$  can be used to predict the output position error for a given input acceleration. For example for an acceleration of 100 revs/sec<sup>2</sup>,  $K_A = 2.7 \times 10^6$  sec<sup>-2</sup> and 12-bit resolution.

$$Error in LSBs = \frac{Input \ acceleration \ [LSB/sec^2]}{K_A[sec^{-2}]}$$

$$= \frac{100 \ [rev/sec^2] \times 2^{12}}{2.7 \times 10^6} = 0.15 \ LSBs \ or \ 47.5 \ seconds \ of \ arc$$

To determine the value of  $K_A$  based on the passive components used to define the dynamics of the converter the following should be used.

$$K_A = \frac{4.04 \times 10^{11}}{2^n \cdot R6 \cdot R4 \cdot (C4 + C5)}$$

Where n = resolution of the converter. R4, R6 in ohms C5, C4 in farads

#### SOURCES OF ERRORS

#### Integrator Offset

Additional inaccuracies in the conversion of the resolver signals will result from an offset at the input to the integrator as it will be treated as an error signal. This error will typically be 1 arc minute over the operating temperature range.

A description of how to adjust from zero offset is given in the section "COMPONENT SELECTION" and the circuit required is shown in Figure 1.

#### **Differential Phase Shift**

Phase shift between the sine and cosine signals from the resolver is known as differential phase shift and can cause static error. Some differential phase shift will be present on all resolvers as a result of coupling. A small resolver residual voltage (quadrature voltage) indicates a small differential phase shift. Additional phase shift can be introduced if the sine channel wires and the cosine channel wires are treated differently. For instance, different cable lengths or different loads could cause differential phase shift.

The additional error caused by differential phase shift on the input signals approximates to

*Error* =  $0.53 a \times b$  arc minutes

where a = differential phase shift (degrees).

b = signal to reference phase shift (degrees).

This error can be minimized by choosing a resolver with a small residual voltage, ensuring that the sine and cosine signals are handled identically and removing the reference phase shift (see section "CONNECTING THE RESOLVER"). By taking these precautions the extra error can be made insignificant.

Under static operating conditions phase shift between the reference and the signal lines alone will not theoretically affect the converter's static accuracy.

However, most resolvers exhibit a phase shift between the signal and the reference. This phase shift will give rise under dynamic conditions to an additional error defined by:

For example, for a phase shift of 20 degrees, a shaft rotation of 22 rps and a reference frequency of 5 kHz, the converter will

exhibit an additional error of:

$$\frac{22 \times 20}{5000} 0.088 \text{ Degrees}$$

This effect can be eliminated by placing a phase shift in the reference to the converter equivalent to the phase shift in the resolver (see section "CONNECTING THE RESOLVER").

Note: Capacitive and inductive crosstalk in the signal and reference leads and wiring can cause similar problems.

#### **VELOCITY ERRORS**

The signal at the INTEGRATOR OUTPUT pin relative to the ANALOG GROUND pin is an analog voltage proportional to the rate of change of the input angle. This signal can be used to stabilize servo loops or in the place of a velocity transducer. Although the conversion loop of the AD2S80A includes a digital section there is an additional analog feedback loop around the velocity signal. This ensures against flicker in the digital positional output in both dynamic and static states.

A better quality velocity signal will be achieved if the following points are considered:

1. Protection.

The velocity signal should be buffered before use.

2. Reversion error.<sup>1</sup>

The reversion error can be nulled by varying one supply rail relative to the other.

3. Ripple and Noise.

Noise on the input signals to the converter is the major cause of noise on the velocity signal. This can be reduced to a minimum if the following precautions are taken:

The resolver is connected to the converter using separate twisted pair cable for the sine, cosine and reference signals.

Care is taken to reduce the external noise wherever possible.

An HF filter is fltted before the Phase Sensitive Demodulator (as described in the section HF FILTER).

A resolver is chosen that has low residual voltage, i.e., a small signal in quadrature with the reference.

Components are selected to operate the AD2S80A with the lowest acceptable bandwidth.

Feedthrough of the reference frequency should be removed by a filter on the velocity signal.

Maintenance of the input signal voltages at 2 V rms will prevent LSB flicker at the positional output. The analog feedback or hysteresis employed around the VCO and the intergrator is a function of the input signal levels (see section "INTEGRATOR").

Following the preceding precautions will allow the user to use the velocity signal in very noisy environments, for example, PWM motor drive applications. Resolver/converter error curves may exhibit apparent acceleration/deceleration at a constant velocity. This results in ripple on the velocity signal of frequency twice the input rotation.

<sup>1</sup>Reversion error, or side-to-side nonlinearity, is a result of differences in the up and down rates of the VCO.

#### **CONNECTING THE RESOLVER**

The recommended connection circuit is shown in Figure 7.

In cases where the reference phase relative to the input signals from the resolver requires adjustment, this can be easily achieved by varying the value of the resistor R2 of the HF filter (see Figure 1).

Assuming that R1 = R2 = R and C1 = C2 = C

and Reference Frequency =  $\frac{1}{2 \pi RC}$

by altering the value of R2, the phase of the reference relative to the input signals will change in an approximately linear manner for phase shifts of up to 10 degrees.

Increasing R2 by 10% introduces a phase lag of 2 degrees. Decreasing R2 by 10% introduces a phase lead of 2 degrees.

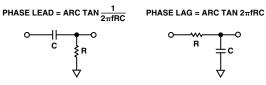

Phase Shift Circuits

#### TYPICAL CIRCUIT CONFIGURATION

Figure 8 shows a typical circuit configuration for the AD2S80A in a 12-bit resolution mode. Values of the external components have been chosen for a reference frequency of 5 kHz and a maximum tracking rate of 260 rps with a bandwidth of 520 Hz. Placing the values for R4, R6, C4 and C5 in the equation for K<sub>A</sub> gives a value of  $1.67 \times 10^6$ . The resistors are 0.125 W, 5% tolerance preferred values. The capacitors are 100 V ceramic, 10% tolerance components.

For signal and reference voltages greater than 2 V rms a simple voltage divider circuit of resistors can be used to generate the correct signal level at the converter. Care should be taken to ensure that the ratios of the resistors between the sine signal line and ground and the cosine signal line and ground are the same. Any difference will result in an additional position error.

For more information on resistive scaling of SIN, COS and REFERENCE converter inputs refer to the application note, "Circuit Applications of the 2S81 and 2S81 Resolver-to-Digital Converters."

#### RELIABILITY

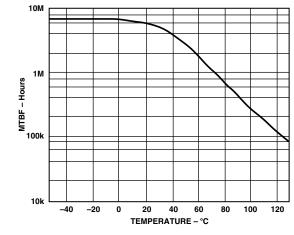

The AD2S80A Mean Time Between Failures (MTBF) has been calculated according to MIL-HDBK-217E, Figure 10 shows the MTBF in hours in naval sheltered conditions for AD2S80A/883B only.

Figure 7. Connecting the AD2S80A to a Resolver

Figure 8. Typical Circuit Configuration

*Figure 9. Large Step Response Curves for Typical Circuit Shown in Figure 8*

Figure 10. AD2S80A MTBF Curve

#### APPLICATIONS

#### **Control Transformer**

The ratio multiplier of the AD2S80A can be used independently of the loop integrators as a control transformer. In this mode the resolver inputs  $\theta$  are multiplied by a digital angle  $\phi$  any difference between  $\phi$  and  $\theta$  will be represented by the AC ERROR output as SIN  $\omega t \sin(\theta - \phi)$  or the DEMOD output as  $\sin(\theta - \phi)$ . To use the AD2S80A in this mode refer to the "Control Transformer" application note.

#### **Dynamic Switching**

In applications where the user requires wide band response from the converter, for example 100 rpm to 6000 rpm, superior performance is achieved if the converters control characteristics are switched dynamically. This reduces velocity offset levels at low tracking rates. For more information on the technique refer to "Dynamic Resolution Switching Using the Variable Resolution Monolithic Resolver-to-Digital Converters."

#### **OTHER PRODUCTS**

The AD2S82A is a monolithic, variable resolution 10-, 12-, 14and 16-bit resolver-to-digital converter in a 44-terminal J-leaded PLCC package. In addition to the AD2S80A functions it has a VCO OUTPUT which is a measure of position within a LSB, and a COMPLEMENT Data Output.

The AD2S81A is a low cost, monolithic, 12-bit resolver-todigital converter in a 28-lead ceramic DIP package.

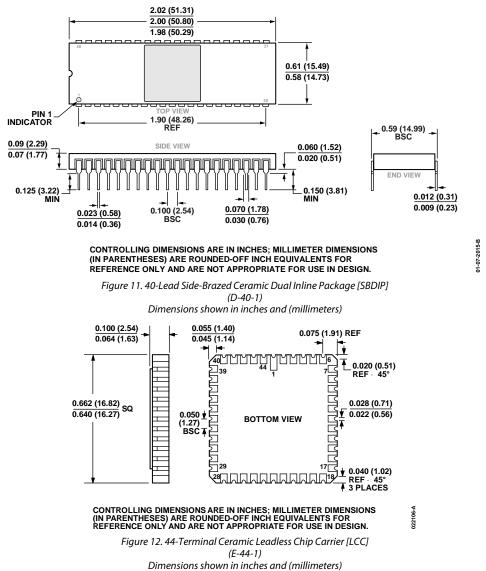

### **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Accuracy  | Package Description                                     | Package Option |

|--------------------|-------------------|-----------|---------------------------------------------------------|----------------|

| 5962-9096201MQA    | -55°C to +125°C   |           | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

| 5962-9096201MXA    | –55°C to +125°C   |           | 44-Terminal Ceramic Leadless Chip Carrier [LLC]         | E-44-1         |

| AD2S80AAD          | -40°C to +85°C    | 8 arc min | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

| AD2S80ABD          | -40°C to +85°C    | 4 arc min | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

| AD2S80AJD          | 0°C to 70°C       | 8 arc min | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

| AD2S80AKD          | 0°C to 70°C       | 4 arc min | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

| AD2S80ALD          | 0°C to 70°C       | 2 arc min | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

| AD2S80ASD          | –55°C to +125°C   | 8 arc min | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

| AD2S80ASD/883B     | –55°C to +125°C   | 8 arc min | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

| AD2S80ATD          | –55°C to +125°C   | 4 arc min | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

| AD2S80ATD/B        | –55°C to +125°C   | 4 arc min | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

| AD2S80ATE          | –55°C to +125°C   | 4 arc min | 44-Terminal Ceramic Leadless Chip Carrier [LLC]         | E-44-1         |

| AD2S80AUD          | –55°C to +125°C   | 2 arc min | 40-Lead Side-Brazed Ceramic Dual Inline Package [SBDIP] | D-40-1         |

<sup>1</sup> Z = RoHS Compliant Part.

### **REVISION HISTORY**

| 1/15—Rev. C to Rev. D      |    |

|----------------------------|----|

| Updated Outline Dimensions | 17 |

#### 2/14-Rev. B to Rev. C

| Updated Outline Dimensions 17 |

|-------------------------------|

| Changes to Ordering Guide 17  |

www.analog.com

$^{\odot}$ 1986–2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D12143-0-1/15(D)