# Serial Input 16-Bit 4 mA-20 mA, 0 mA-20 mA DAC

Data Sheet AD420

#### **FEATURES**

4 mA-20 mA, 0 mA-20 mA or 0 mA-24 mA current output

16-bit resolution and monotonicity

±0.012% max integral nonlinearity

±0.05% max offset (trimmable)

±0.15% max total output error (trimmable)

Flexible serial digital interface (3.3 MBPS)

On-Chip loop fault detection

On-chip 5 V reference (25 ppm/°C max)

Asynchronous CLEAR function

Maximum power supply range of 32 V

Output loop compliance of 0 V to Vcc - 2.75 V

24-Lead SOIC and PDIP packages

#### **GENERAL DESCRIPTION**

The AD420 is a complete digital to current loop output converter, designed to meet the needs of the industrial control market. It provides a high precision, fully integrated, low cost single-chip solution for generating current loop signals in a compact 24-lead SOIC or PDIP package.

The output current range can be programmed to 4 mA to 20 mA, 0 mA to 20 mA or to an overrange function of 0 mA to 24 mA. The AD420 can alternatively provide a voltage output from a separate pin that can be configured to provide 0 V to 5 V, 0 V to 10 V,  $\pm 5$  V, or  $\pm 10$  V with the addition of a single external buffer amplifier.

The 3.3 M Baud serial input logic design minimizes the cost of galvanic isolation and allows for simple connection to commonly used microprocessors. It can be used in 3-wire or asynchronous mode and a serial-out pin is provided to allow daisy chaining of multiple DACs on the current loop side of the isolation barrier.

The AD420 uses sigma-delta ( $\Sigma$ - $\Delta$ ) DAC technology to achieve 16-bit monotonicity at very low cost. Full-scale settling to 0.1% occurs within 3 ms. The only external components that are required (in addition to normal transient protection circuitry) are two low cost capacitors which are used in the DAC output filter.

If the AD420 is used at extreme temperatures and supply voltages, an external output transistor can be used to minimize power dissipation on the chip via the BOOST pin. The FAULT DETECT pin signals when an open circuit occurs in the loop. The on-chip voltage reference can be used to supply a precision +5 V to external components in addition to the AD420 or, if the

Rev. I

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

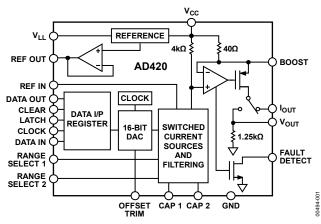

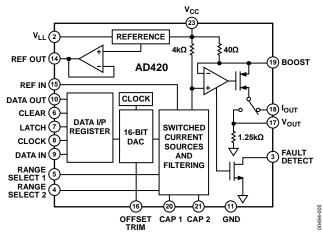

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

user desires temperature stability exceeding 25 ppm/°C, an external precision reference such as the AD586 can be used as the reference. The AD420 is available in a 24-lead SOIC and PDIP over the industrial temperature range of -40°C to +85°C.

#### **PRODUCT HIGHLIGHTS**

- The AD420 is a single chip solution for generating 4 mA to 20 mA or 0 mA to 20 mA signals at the controller end of the current loop.

- 2. The AD420 is specified with a power supply range from 12 V to 32 V. Output loop compliance is 0 V to 0 V to

- 3. The flexible serial input can be used in 3-wire mode with SPI\* or MICROWIRE\* microcontrollers, or in asynchronous mode, which minimizes the number of control signals required.

- 4. The serial data out pin can be used to daisy chain any number of AD420s together in 3-wire mode.

- At power-up, the AD420 initializes its output to the low end of the selected range.

- 6. The AD420 has an asynchronous CLEAR pin, which sends the output to the low end of the selected range (0 mA, 4 mA, or 0 V).

- 7. The AD420 BOOST pin accommodates an external transistor to off-load power dissipation from the chip.

- 8. The offset of  $\pm 0.05\%$  and total output error of  $\pm 0.15\%$  can be trimmed if desired, using two external potentiometers.

# **AD420\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

# **DOCUMENTATION**

#### **Data Sheet**

AD420: Serial Input 16-Bit 4 mA-20 mA, 0 mA-20 mA DAC Data Sheet

### REFERENCE MATERIALS •

#### **Solutions Bulletins & Brochures**

• Digital to Analog Converters ICs Solutions Bulletin

# **DESIGN RESOURCES**

- · AD420 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

## **DISCUSSIONS**

View all AD420 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

9/99—Rev. E to Rev. F

| Features                                                            |

|---------------------------------------------------------------------|

| Functional Block Diagram 1                                          |

| General Description1                                                |

| Product Highlights                                                  |

| Revision History                                                    |

| Specifications                                                      |

| Absolute Maximum Ratings                                            |

| ESD Caution5                                                        |

| Pin Configuration and Function Descriptions6                        |

| Timing Requirements                                                 |

| Three-Wire Interface                                                |

| Three-Wire Interface Fast Edges on Digital Input7                   |

| Asynchronous Interface                                              |

| Terminology                                                         |

| Theory of Operation9                                                |

| Applications Information                                            |

| Current Output                                                      |

| REVISION HISTORY                                                    |

| 3/15—Rev. H to Rev. I                                               |

| Changes to Three-Wire Interface Fast Edges on Digital Input Section |

| 1/11—Rev. G to Rev. H                                               |

| Changes to Figure 13                                                |

| 11/09—Rev. F to Rev. G                                              |

| Updated Format                                                      |

| Driving Inductive Loads                      |

|----------------------------------------------|

| Voltage-Mode Output10                        |

| Optional Span and Zero Trim10                |

| Three-Wire Interface                         |

| Using Multiple DACS with Fault Detect11      |

| Asynchronous Interface Using Optocouplers 11 |

| Microprocessor Interface                     |

| AD420-To-MC68HC11 (SPI Bus) Interface        |

| AD420 to Microwire Interface12               |

| External Boost Function                      |

| AD420 Protection                             |

| Transient Voltage Protection                 |

| Board Layout And Grounding14                 |

| Power Supplies and Decoupling14              |

| Outline Dimensions                           |

| Ordering Guide                               |

# **SPECIFICATIONS**

$T_{\text{A}} = T_{\text{MIN}} - T_{\text{MAX}}\text{, }V_{\text{CC}} = +24\text{ V, unless otherwise noted.}$

Table 1.

|                                                              | AD420-32 Version |        |                            |         |                    |

|--------------------------------------------------------------|------------------|--------|----------------------------|---------|--------------------|

| Parameter                                                    | Min              | Тур    | Max                        | Units   | Comments           |

| RESOLUTION                                                   | 16               |        |                            | Bits    |                    |

| I <sub>OUT</sub> CHARACTERISTICS                             |                  |        |                            |         | $R_L = 500 \Omega$ |

| Operating Current Ranges                                     | 4                |        | 20                         | mA      |                    |

|                                                              | 0                |        | 20                         | mA      |                    |

|                                                              | 0                |        | 24                         | mA      |                    |

| Current Loop Voltage Compliance                              | 0                |        | $V_{\text{CC}}$ – 2.75 $V$ | V       |                    |

| Settling Time (to 0.1% of FS) <sup>1</sup>                   |                  | 2.5    | 3                          | ms      |                    |

| Output Impedance (Current Mode)                              |                  | 25     |                            | ΜΩ      |                    |

| Accuracy <sup>2</sup>                                        |                  |        |                            |         |                    |

| Monotonicity                                                 | 16               |        |                            | Bits    |                    |

| Integral Nonlinearity                                        |                  | ±0.002 | ±0.012                     | %       |                    |

| Offset (0 mA or 4 mA) $(T_A = +25^{\circ}C)$                 |                  |        | ±0.05                      | %       |                    |

| Offset Drift                                                 |                  | 20     | 50                         | ppm/° C |                    |

| Total Output Error (20 mA or 24 mA) $(T_A = +25$ °C)         |                  |        | ±0.15                      | %       |                    |

| Total Output Error Drift                                     |                  | 20     | 50                         | ppm/° C |                    |

| PSRR <sup>3</sup>                                            |                  | 5      | 10                         | μA/V    |                    |

| V <sub>OUT</sub> CHARACTERISTICS                             |                  |        |                            |         |                    |

| FS Output Voltage Range (Pin 17)                             | 0                |        | 5                          | V       |                    |

| VOLTAGE REFERENCE                                            |                  |        |                            |         |                    |

| REF OUT                                                      |                  |        |                            |         |                    |

| Output Voltage ( $T_A = +25^{\circ} C$ )                     | 4.995            | 5.0    | 5.005                      | V       |                    |

| Drift                                                        |                  |        | ±25                        | ppm/° C |                    |

| Externally Available Current                                 |                  | 5      |                            | mA      |                    |

| Short Circuit Current                                        |                  | 7      |                            | mA      |                    |

| REF IN                                                       |                  |        |                            |         |                    |

| Resistance                                                   |                  | 30     |                            | kΩ      |                    |

| $V_{LL}$                                                     |                  |        |                            |         |                    |

| Output Voltage                                               |                  | 4.5    |                            | V       |                    |

| Externally Available Current                                 |                  | 5      |                            | mA      |                    |

| Short Circuit Current                                        |                  | 20     |                            | mA      |                    |

| DIGITAL INPUTS                                               |                  |        |                            |         |                    |

| V <sub>H</sub> (Logic 1)                                     | 2.4              |        |                            | V       |                    |

| V <sub>IL</sub> (Logic 0)                                    |                  |        | 0.8                        | V       |                    |

| $I_{IH} (V_{IN} = 5.0 \text{ V})$                            |                  |        | ±10                        | μΑ      |                    |

| $I_{IL}(V_{IN}=0V)$                                          |                  |        | ±10                        | μA      |                    |

| Data Input Rate (3-Wire Mode)                                | No Minimum       |        | 3.3                        | MBPS    |                    |

| Data Input Rate (Asynchronous Mode)                          | No Minimum       |        | 150                        | kBPS    |                    |

| DIGITAL OUTPUTS                                              |                  |        |                            |         |                    |

| FAULT DEFECT                                                 |                  |        |                            |         |                    |

| $V_{OH}$ (10 k $\Omega$ Pull-Up Resistor to $V_{LL}$ )       | 3.6              | 4.5    |                            | V       |                    |

| V <sub>OL</sub> (10 kΩ Pull-Up Resistor to V <sub>LL</sub> ) |                  | 0.2    | 0.4                        | V       |                    |

| V <sub>OL</sub> @ 2.5 mA                                     |                  | 0.6    |                            | V       |                    |

| DATA OUT                                                     |                  |        |                            |         |                    |

| $V_{OH}$ ( $I_{OH} = -0.8 \text{ mA}$ )                      | 3.6              | 4.3    |                            | V       |                    |

| $V_{OL}$ ( $I_{OL} = 1.6 \text{ mA}$ )                       |                  | 0.3    | 0.4                        | V       |                    |

|                                  |     | AD420-32 Version |     |       |          |

|----------------------------------|-----|------------------|-----|-------|----------|

| Parameter                        | Min | Тур              | Max | Units | Comments |

| POWER SUPPLY                     |     |                  |     |       |          |

| Operating Range V <sub>CC</sub>  | 12  |                  | 32  | V     |          |

| Quiescent Current                |     | 4.2              | 5.5 | mA    |          |

| Quiescent Current (External VLL) |     | 3                |     | mA    |          |

| TEMPERATURE RANGE                |     |                  |     |       |          |

| Specified Performance            | -40 |                  | +85 | °C    |          |

<sup>&</sup>lt;sup>1</sup> External capacitor selection must be as described in Figure 6.

<sup>2</sup> Total Output Error includes Offset and Gain Error. Total Output Error and Offset Error are with respect to the Full-Scale Output and are measured with an ideal +5 V reference. If the internal reference is used, the reference errors must be added to the Offset and Total Output Errors.

<sup>3</sup> PSRR is measured by varying V<sub>CC</sub> from 12 V to its maximum 32 V.

# **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                                                | Rating                                               |

|--------------------------------------------------------------------------|------------------------------------------------------|

| V <sub>cc</sub> to GND                                                   | 32 V                                                 |

| I <sub>OUT</sub> to GND                                                  | V <sub>CC</sub>                                      |

| Digital Inputs to GND                                                    | −0.5 V to +7 V                                       |

| Digital Output to GND                                                    | $-0.5  \text{V}$ to $ \text{V}_{LL} + 0.3  \text{V}$ |

| V <sub>LL</sub> and REF OUT: Outputs Safe for Indefinite Short to Ground |                                                      |

| Storage Temperature                                                      | −65°C to +150°C                                      |

| Lead Temperature (Soldering, 10 sec)                                     | +300°C                                               |

| Lead Temperature, Soldering Reflow                                       | +260°C                                               |

| Thermal Impedance:                                                       |                                                      |

| SOIC (R) Package                                                         | $\theta_{JA} = 75^{\circ}C/W$                        |

| PDIP (N) Package                                                         | $\theta_{JA} = 50^{\circ}\text{C/W}$                 |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

**Table 3. Truth Table**

| Inputs |                     |                   |                     |

|--------|---------------------|-------------------|---------------------|

| CLEA   | Range<br>R Select 2 | Range<br>Select 1 | Operation           |

| 0      | Х                   | X                 | Normal operation    |

| 1      | X                   | X                 | Output at bottom of |

|        |                     |                   | span                |

| Χ      | 0                   | 0                 | 0 V–5 V range       |

| Χ      | 0                   | 1                 | 4 mA-20 mA range    |

| Χ      | 1                   | 0                 | 0 mA-20 mA range    |

| X      | 1                   | 1                 | 0 mA-24 mA range    |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

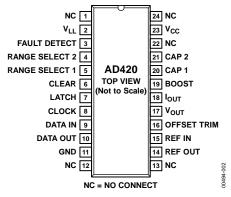

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No.          | Mnemonic         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 12,<br>13, 24 | NC               | No Connection. No internal connections inside device.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2                | V <sub>LL</sub>  | Auxiliary buffered $+4.5\text{V}$ digital logic voltage. This pin is the internal supply voltage for the digital circuitry and can be used as a termination for pull-up resistors. An external $+5\text{V}$ power supply can be connected to $V_{LL}$ . It will override this buffered voltage, thus reducing the internal power dissipation. The $V_{LL}$ pin should be decoupled to GND with a 0.1 $\mu\text{F}$ capacitor. See the Power Supplies and Decoupling section. |

| 3                | FAULT DETECT     | FAULT DETECT, connected to a pull-up resistor, is asserted low when the output current does not match the DAC's programmed value, for example, in case the current loop is broken.                                                                                                                                                                                                                                                                                           |

| 4                | RANGE SELECT 2   | Selects the converter's output operating range. One output voltage range and three                                                                                                                                                                                                                                                                                                                                                                                           |

| 5                | RANGE SELECT 1   | output current ranges are available.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6                | CLEAR            | Valid $V_{\mathbb{H}}$ unconditionally forces the output to go to the minimum of its programmed range. After CLEAR is removed the DAC output will remain at this value. The data in the input register is unaffected.                                                                                                                                                                                                                                                        |

| 7                | LATCH            | In the 3-wire interface mode a rising edge parallel loads the serial input register data into the DAC. To use the asynchronous mode connect LATCH through a current limiting resistor to Vcc.                                                                                                                                                                                                                                                                                |

| 8                | CLOCK            | Data Clock Input. The clock period is equal to the input data bit rate in the 3-wire interface mode and is 16 times the bit rate in asynchronous mode.                                                                                                                                                                                                                                                                                                                       |

| 9                | DATA IN          | Serial Data Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10               | DATA OUT         | Serial Data Output. In the 3-wire interface mode, this output can be used for daisy-chaining multiple AD420s. In the asynchronous mode a positive pulse will indicate a framing error after the stop-bit is received.                                                                                                                                                                                                                                                        |

| 11               | GND              | Ground (Common).                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14               | REF OUT          | +5 V Reference Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15               | REF IN           | Reference Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16               | OFFSET TRIM      | Offset Adjust.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 17               | V <sub>OUT</sub> | Voltage Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18               | Гоит             | Current Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 19               | BOOST            | Connect to an external transistor to reduce the power dissipated in the AD420 output transistor, if desired.                                                                                                                                                                                                                                                                                                                                                                 |

| 20               | CAP 1            | These pins are used for internal filtering. Connect capacitors between each of these                                                                                                                                                                                                                                                                                                                                                                                         |

| 21               | CAP 2            | pins and V <sub>CC</sub> . Refer to the description of current output operation.                                                                                                                                                                                                                                                                                                                                                                                             |

| 22               | NC               | No Connection. Do not connect anything to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 23               | V <sub>CC</sub>  | Power Supply Input. The $V_{CC}$ pin should always be decoupled to GND with a 0.1 $\mu$ F capacitor. See the Power Supplies and Decoupling section.                                                                                                                                                                                                                                                                                                                          |

### TIMING REQUIREMENTS

$T_A = -40$ °C to +85°C,  $V_{CC} = +12 \text{ V}$  to +32 V.

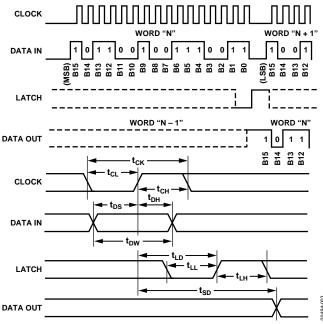

#### THREE-WIRE INTERFACE

Figure 3. Timing Diagram for 3-Wire Interface

Table 5. Timing Specification for 3-Wire Interface

| Parameter                | Label            | Limit | Units  |

|--------------------------|------------------|-------|--------|

| Data Clock Period        | tcĸ              | 300   | ns min |

| Data Clock Low Time      | <b>t</b> cL      | 80    | ns min |

| Data Clock High Time     | <b>t</b> cH      | 80    | ns min |

| Data Stable Width        | t <sub>DW</sub>  | 125   | ns min |

| Data Setup Time          | t <sub>DS</sub>  | 40    | ns min |

| Data Hold Time           | t <sub>DH</sub>  | 5     | ns min |

| Latch Delay Time         | t <sub>LD</sub>  | 80    | ns min |

| Latch Low Time           | t <sub>LL</sub>  | 80    | ns min |

| Latch High Time          | t <sub>LH</sub>  | 80    | ns min |

| Serial Output Delay Time | t <sub>SD</sub>  | 225   | ns max |

| Clear Pulse Width        | t <sub>CLR</sub> | 50    | ns min |

# THREE-WIRE INTERFACE FAST EDGES ON DIGITAL INPUT

With a fast rising edge (<100 ns) on one of the serial inputs (CLOCK, DATA IN, LATCH) while another input is logic high, the part may be triggered into a test mode and the contents of the data register may become corrupted, which may result in the output being loaded with an incorrect value. If fast edges are expected on the digital input lines, it is recommended that the latch line remain at Logic 0 during serial loading of the DAC. Similarly, the clock line should remain low during updates of the DAC via the latch pin. Alternatively, the addition of small value capacitors on the digital lines will slow down the edge.

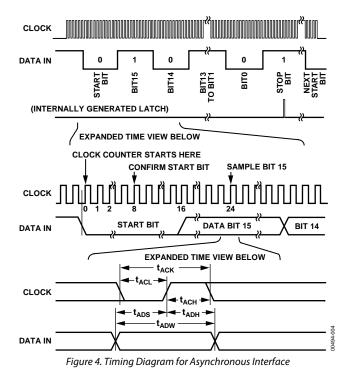

Table 6. Timing Specifications for Asynchronous Interface

| Parameter                               | Label                   | Limit | Units  |

|-----------------------------------------|-------------------------|-------|--------|

| Asynchronous Clock Period               | t <sub>ACK</sub>        | 400   | ns min |

| Asynchronous Clock Low Time             | t <sub>ACL</sub>        | 50    | ns min |

| Asynchronous Clock High Time            | <b>t</b> <sub>ACH</sub> | 150   | ns min |

| Data Stable Width (Critical Clock Edge) | t <sub>ADW</sub>        | 300   | ns min |

| Data Setup Time (Critical Clock Edge)   | t <sub>ADS</sub>        | 60    | ns min |

| Data Hold Time (Critical Clock Edge)    | t <sub>ADH</sub>        | 20    | ns min |

| Clear Pulse Width                       | t <sub>CLR</sub>        | 50    | ns min |

#### **ASYNCHRONOUS INTERFACE**

Note that in the timing diagram for asynchronous mode operation each data word is framed by a START (0) bit and a STOP (1) bit. The data timing is with respect to the rising edge of the CLOCK at the center of each bit cell. Bit cells are 16 clocks long, and the first cell (the START bit) begins at the first clock following the leading (falling) edge of the START bit. Thus, the MSB (D15) is sampled 24 clock cycles after the beginning of the START bit, D14 is sampled at clock number 40, and so on. During any dead time before writing the next word the DATA IN pin must remain at Logic 1.

The DAC output updates when the STOP bit is received. In the case of a framing error (the STOP bit sampled as a 0) the AD420 will output a pulse at the DATA OUT pin one clock period wide during the clock period subsequent to sampling the STOP bit. The DAC output will not update if a framing error is detected.

### **TERMINOLOGY**

#### Resolution

For 16-bit resolution, 1 LSB = 0.0015% of the FSR. In the 4 mA-20 mA range 1 LSB = 244 nA.

#### **Integral Nonlinearity**

Analog Devices defines integral nonlinearity as the maximum deviation of the actual, adjusted DAC output from the ideal analog output (a straight line drawn from 0 to FS – 1 LSB) for any bit combination. This is also referred to as relative accuracy.

#### **Differential Nonlinearity**

Differential nonlinearity is the measure of the change in the analog output, normalized to full scale, associated with an LSB change in the digital input code. Monotonic behavior requires that the differential linearity error be greater than –1 LSB over the temperature range of interest.

#### Monotonicity

A DAC is monotonic if the output either increases or remains constant for increasing digital inputs with the result that the output will always be a single-valued function of the input.

#### **Gain Error**

Gain error is a measure of the output error between an ideal DAC and the actual device output with all 1s loaded after offset error has been adjusted out.

#### Offset Error

Offset error is the deviation of the output current from its ideal value expressed as a percentage of the fullscale output with all 0s loaded in the DAC.

#### Drift

Drift is the change in a parameter (such as gain and offset) over a specified temperature range. The drift temperature coefficient, specified in ppm/°C, is calculated by measuring the parameter at  $T_{\text{MIN}}$ , 25°C, and  $T_{\text{MAX}}$  and dividing the change in the parameter by the corresponding temperature change.

#### **Current Loop Voltage Compliance**

The voltage compliance is the maximum voltage at the  $I_{\text{OUT}}$  pin for which the output current will be equal to the programmed value.

### THEORY OF OPERATION

The AD420 uses a sigma-delta  $(\Sigma - \Delta)$  architecture to carry out the digital-to-analog conversion. This architecture is particularly well suited for the relatively low bandwidth requirements of the industrial control environment because of its inherent monotonicity at high resolution.

In the AD420 a second order modulator is used to keep complexity and die size to a minimum. The single bit stream from the modulator controls a switched current source that is then filtered by two, continuous time resistor-capacitor sections. The capacitors are the only external components that have to be added for standard current-out operation. The filtered current is amplified and mirrored to the supply rail so that the application simply sees a 4 mA-20 mA, 0 mA-20 mA, or 0 mA-24 mA current source output with respect to ground. The AD420 is manufactured on a BiCMOS process that is well suited to implementing low voltage digital logic with high performance and high voltage analog circuitry.

The AD420 can also provide a voltage output instead of a current loop output if desired. The addition of a single external amplifier allows the user to obtain 0 V–5 V, 0 V–10 V,  $\pm$ 5 V, or  $\pm$ 10 V.

The AD420 has a loop fault detection circuit that warns if the voltage at  $I_{\rm OUT}$  attempts to rise above the compliance range, due to an open-loop circuit or insufficient power supply voltage. The FAULT DETECT is an active low open drain signal so that one can connect several AD420s together to one pull-up resistor for global error detection. The pull-up resistor can be tied to the  $V_{\rm LL}$  pin, or an external +5 V logic supply.

The  $I_{OUT}$  current is controlled by a PMOS transistor and an internal amplifier as shown in the functional block diagram. The internal circuitry that develops the fault output avoids using a comparator with window limits since this would require an actual output error before the FAULT DETECT output becomes active. Instead, the signal is generated when the internal amplifier in the output stage of the AD420 has less than

approximately one volt remaining of drive capability (when the gate of the output PMOS transistor nearly reaches ground). Thus the FAULT DETECT output activates slightly before the compliance limit is reached. Since the comparison is made within the feedback loop of the output amplifier, the output accuracy is maintained by its open-loop gain, and no output error occurs before the fault detect output becomes active.

The 3-wire digital interface, comprising DATA IN, CLOCK, and LATCH, interfaces to all commonly used serial microprocessors without the addition of any external glue logic. Data is loaded into an input register under control of CLOCK and is loaded to the DAC when LATCH is strobed. If a user wants to minimize the number of galvanic isolators in an intrinsically safe application, the AD420 can be configured to run in asynchronous mode. This mode is selected by connecting the LATCH pin to  $V_{\rm CC}$  through a current limiting resistor. The data must then be combined with a start and stop bit to frame the information and trigger the internal LATCH signal.

Figure 5. Functional Block Diagram

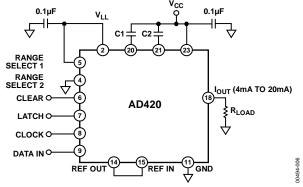

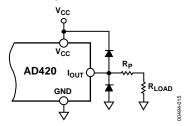

# APPLICATIONS INFORMATION CURRENT OUTPUT

The AD420 can provide 4 mA–20 mA, 0 mA–20 mA, or 0 mA–24 mA output without any active external components. Filter capacitors C1 and C2 can be any type of low cost ceramic capacitors. To meet the specified full-scale settling time of 3 ms, low dielectric absorption capacitors (NPO) are required. Suitable values are C1 = 0.01  $\mu$ F and C2 = 0.01  $\mu$ F.

Figure 6. Standard Configuration

#### **DRIVING INDUCTIVE LOADS**

When driving inductive or poorly defined loads ,connect a 0.01  $\mu F$  capacitor between  $I_{\rm OUT}$  (Pin 18) and GND (Pin 11). This ensures stability of the AD420 with loads beyond 50 mH. There is no maximum capacitance limit. The capacitive component of the load may cause slower settling, though this may be masked by the settling time of the AD420. A programmed change in the current may cause a back EMF voltage on the output that may exceed the compliance of the AD420. To prevent this voltage from exceeding the supply rails connect protective diodes between  $I_{\rm OUT}$  and each of  $V_{\rm CC}$  and GND.

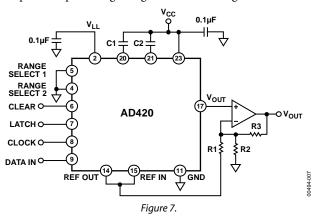

#### **VOLTAGE-MODE OUTPUT**

Since the AD420 is a single supply device, it is necessary to add an external buffer amplifier to the  $V_{\text{OUT}}$  pin to obtain a selection of bipolar output voltage ranges as shown in Figure 7.

Table 7. Buffer Amplifier Configuration

| R1   | R2   | R3 | V <sub>OUT</sub> |

|------|------|----|------------------|

| Open | Open | 0  | 0 V – 5 V        |

| Open | R    | R  |                  |

| R    | Open | R  | ±5 V             |

| R    | 2R   | 2R | ±10 V            |

Suitable  $R = 5 k\Omega$ .

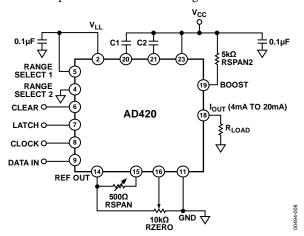

#### **OPTIONAL SPAN AND ZERO TRIM**

For users who would like lower than the specified values of offset and gain error, Figure 8 shows a simple way to trim these parameters. Care should be taken to select low drift resistors because they affect the temperature drift performance of the DAC.

The adjustment algorithm is iterative. The procedure for trimming the AD420 in the 4 mA-20 mA mode can be accomplished as follows:

- 1. Offset adjust. Load all zeros. Adjust RZERO for 4.00000 mA of output current.

- 2. Gain adjust. Load all ones. Adjust RSPAN for 19.99976 mA (FS 1 LSB) of output current.

Return to Step I and iterate until convergence is obtained.

Figure 8. Offset and Gain Adjust

Variation of RZERO between REF OUT (5 V) and GND leads to an offset adjust range from −1.5 mA to 6 mA, (1.5 mA/V centered at 1 V).

The 5 k $\Omega$  RSPAN2 resistor is connected in parallel with the internal 40 W sense resistor, which leads to a gain increase of +0.8%.

As RSPAN is changed to 500  $\Omega$ , the voltage on REF IN is attenuated by the combination of RSPAN and the 30 k $\Omega$  REF IN input resistance. When added together with RSPAN2 this results in an adjustment range of -0.8% to +0.8%.

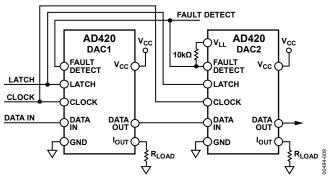

#### THREE-WIRE INTERFACE

Figure 9 shows the AD420 connected in the 3-wire interface mode. The AD420 data input block contains a serial input shift register and a parallel latch. The contents of the shift register are controlled by the DATA IN signal and the rising edges of the CLOCK. Upon request of the LATCH pin the DAC and internal latch are updated from the shift register parallel outputs. The CLOCK should remain inactive while the DAC is updated. Refer to the timing requirements for 3-wire interface.

Figure 9. Three-Wire Interface Using Multiple DACs with Joint Fault Detect

#### **USING MULTIPLE DACS WITH FAULT DETECT**

The 3-wire interface mode can utilize the serial DATA OUT for easy interface to multiple DACs. To program the two AD420s in Figure 9, 32 data bits are required. The first 16 bits are clocked into the input shift register of DAC1. The next 16 bits transmitted pass the first 16 bits from the DATA OUT pin of DAC1 to the input register of DAC2. The input shift registers of the two DACs operate as a single 32-bit shift register, with the leading 16 bits representing information for DAC2 and the trailing 16 bits serving for DAC1. Each DAC is then updated upon request of the LATCH pin. The daisy-chain can be extended to as many DACs as required.

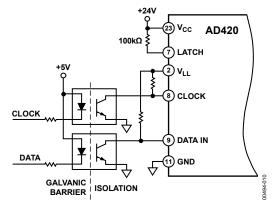

# ASYNCHRONOUS INTERFACE USING OPTOCOUPLERS

The AD420 connected in asynchronous interface mode with optocouplers is shown in Figure 10. Asynchronous operation minimizes the number of control signals required for isolation of the digital system from the control loop. The resistor connected between the LATCH pin and  $V_{\rm CC}$  is required to activate this mode. For operation with  $V_{\rm CC}$  below 18 V use a 50 k $\Omega$  pull-up resistor; from 18 V to 32 V, use 100 k $\Omega$ .

Asynchronous mode requires that the clock run at 16 times the data bit rate, therefore, to operate at the maximum input data rate of 150 kBPS, an input clock of 2.4 MHz is required. The actual data rate achieved may be limited by the type of optocouplers chosen. The number of control signals can be further reduced by creating the appropriate clock signal on the current loop side of the isolation barrier. If optocouplers with relatively slow rise and fall times are used, Schmitt triggers may be required on the digital inputs to prevent erroneous data being presented to the DAC.

Figure 10. Asynchronous Interface Using Optocouplers

### MICROPROCESSOR INTERFACE

#### AD420-TO-MC68HC11 (SPI BUS) INTERFACE

The AD420 interface to the Motorola serial peripheral interface (SPI) is shown in Figure 11. The MOSI, SCK, and  $\overline{SS}$  pins of the HC11 are respectively connected to the DATA IN, CLOCK, and LATCH pins of the AD420. The majority of the interfacing issues are done in the software initialization. A typical routine, such as the one shown below, begins by initializing the state of the various SPI data and control registers.

|        |      |             | 0                                                |

|--------|------|-------------|--------------------------------------------------|

| INIT   | LDAA | #\$2F       | $; \overline{SS} = 1; SCK = 0;$ $MOSI = 1$       |

|        | STAA | PORTD       | ;SEND TO SPI OUTPUTS                             |

|        | LDAA | #\$38       | ; <del>SS</del> , SCK, MOSI =<br>OUTPUTS         |

|        | STAA | DDRD        | ;SEND DATA DIRECTION INFO                        |

|        | LDAA | #\$50       | ;DABL INTRPTS, SPI<br>IS MASTER & ON             |

|        | STAA | SPCR        | ;CPOL = 0, CPHA = 0,<br>1MHZ BAUDRATE            |

| NEXTPT | LDAA | MSBY        | ;LOAD ACCUM W/UPPER<br>8 BITS                    |

|        | BSR  | SENDAT      | ;JUMP TO DAC OUTPUT ROUTINE                      |

|        | JMP  | NEXTPT      | ;INFINITE LOOP                                   |

| SENDAT | LDY  | #\$1000     | ;POINT AT ON-CHIP<br>REGISTERS                   |

|        | BCLR | \$08,Y,\$20 | ;DRIVE SS (LATCH)                                |

|        | STAA | SPDR        | ;SEND MS-BYTE TO SPI<br>DATA REG                 |

| WAIT1  | LDAA | SPSR        | ;CHECK STATUS OF<br>SPIE                         |

|        | BPL  | WAIT1       | ; POLL FOR END OF X-MISSION                      |

|        | LDAA | LSBY        | ;GET LOW 8 BITS FROM MEMORY                      |

|        | STAA | SPDR        | ;SEND LS-BYTE TO SPI<br>DATA REG                 |

| WAIT2  | LDAA | SPSR        | ;CHECK STATUS OF<br>SPIE                         |

|        | BPL  | WAIT2;      | ; POLL FOR END OF X-MISSION                      |

|        | BSET | \$08,Y,\$20 | ;DRIVE $\overline{\text{SS}}$ HIGH TO LATCH DATA |

|        | RTS  |             |                                                  |

|        |      |             |                                                  |

The SPI data port is configured to process data in 8-bit bytes. The most significant data byte (MSBY) is retrieved from memory and processed by the SENDAT routine. The  $\overline{SS}$  pin is driven low by indexing into the PORTD data register and clear Bit 5. The MSBY is then sent to the SPI data register where it is automatically transferred to the AD420 internal shift resister. The HC11 generates the requisite eight clock pulses with data valid on the rising edges. After the MSBY is transmitted, the least significant byte (LSBY) is loaded from memory and transmitted in a similar fashion. To complete the transfer, the LATCH pin is driven high when loading the complete 16-bit word into the AD420.

Figure 11. AD420-to-68HC11 (SPI) Interface

#### **AD420 TO MICROWIRE INTERFACE**

The flexible serial interface of the AD420 is also compatible with the National Semiconductor MICROWIRE interface. The MICROWIRE interface is used in microcontrollers such as the COP400 and COP800 series of processors. A generic interface to use the MICROWIRE interface is shown in Figure 12. The G1, SK, and SO pins of the MICROWIRE interface are respectively connected to the LATCH, CLOCK, and DATA IN pins of the AD420.

Figure 12. AD420-to-MICROWIRE Interface

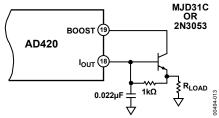

#### **EXTERNAL BOOST FUNCTION**

The external boost transistor reduces the power dissipated in the AD420 by reducing the current flowing in the on-chip output transistor (dividing it by the current gain of the external circuit). A discrete NPN transistor with a breakdown voltage, BV<sub>CEO</sub>, greater than 32 V can be used as shown in Figure 13.

Figure 13. External Boost Configuration

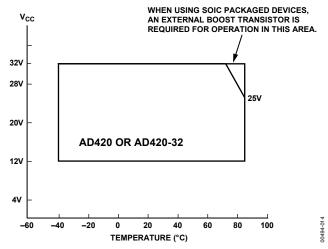

The external boost capability has been developed for those users who may wish to use the AD420, in the SOIC package, at the extremes of the supply voltage, load current, and temperature range. The PDIP package (because of its lower thermal resistance) will operate safely over the entire specified voltage, temperature, and load current ranges without the boost

transistor. The plot in Figure 14 shows the safe operating region for both package types. The boost transistor can also be used to reduce the amount of temperature induced drift in the part. This will minimize the temperature induced drift of the on-chip voltage reference, which improves drift and linearity.

Figure 14. Safe Operating Region

### **AD420 PROTECTION**

#### TRANSIENT VOLTAGE PROTECTION

The AD420 contains ESD protection diodes, which prevent damage from normal handling. The industrial control environment can, however, subject I/O circuits to much higher transients. To protect the AD420 from excessively high voltage transients, such as those specified in IEC 801, external power diodes and a surge current limiting resistor may be required, as shown in Figure 15. The constraint on the resistor is that during normal operation the output voltage level at I<sub>OUT</sub> must remain within its voltage compliance limit

$$(I_{OUT} \times (Rp + R_{LOAD}) \le V_{CC} - 2.75 V)$$

and the two protection diodes and resistor must have appropriate power ratings.

Figure 15. Output Transient Voltage Protection

#### **BOARD LAYOUT AND GROUNDING**

The AD420 ground pin, designated GND, is the high quality ground reference point for the device. Any external loads on the REF OUT and  $V_{\text{OUT}}$  pins of the AD420 should be returned to this reference point. Analog and digital ground currents should not share a common path. Each signal should have an appropriate analog or digital signal return routed close to it. Using this approach, signal loops enclose a small area, minimizing the inductive coupling of noise. Wide PC tracks, large gauge wire, and ground planes are highly recommended to provide low impedance signal paths.

#### **POWER SUPPLIES AND DECOUPLING**

The AD420 supply pins,  $V_{\rm CC}$  (Pin 23) and  $V_{\rm LL}$  (Pin 2), should be decoupled to GND with 0.1  $\mu$ F capacitors to eliminate high frequency noise that may otherwise get coupled into the analog system. High frequency ceramic capacitors are recommended. The decoupling capacitors should be located in close proximity to the pins and the ground line to have maximum effect. Further reductions in noise, and improvements in performance, may be achieved by using a larger value capacitor on the  $V_{\rm LL}$  pin.

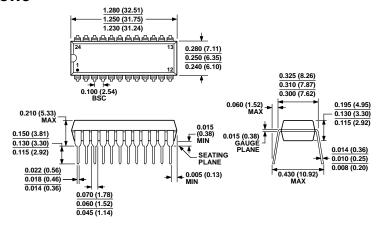

# **OUTLINE DIMENSIONS**

#### COMPLIANT TO JEDEC STANDARDS MS-001

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 16. 24-Lead Plastic Dual In-Line Package [PDIP] Narrow Body (N-24-1)

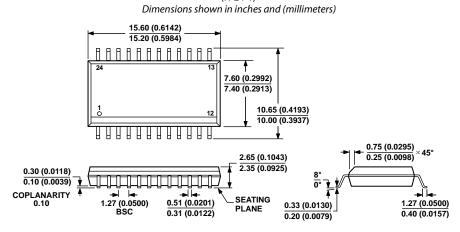

COMPLIANT TO JEDEC STANDARDS MS-013-AD

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 17. 24-Lead Standard Small Outline [SOIC\_W]

Wide Body

(RW-24)

Dimensions shown in millimeters and (inches)

#### ORDERING GUIDE

| Model <sup>1</sup> | Temperature Range | Max Operating Voltage | Package Description | Package Option |

|--------------------|-------------------|-----------------------|---------------------|----------------|

| AD420AN-32         | -40°C to +85°C    | 32 V                  | 24-Lead PDIP        | N-24-1         |

| AD420ANZ-32        | -40°C to +85°C    | 32 V                  | 24-Lead PDIP        | N-24-1         |

| AD420AR-32         | -40°C to +85°C    | 32 V                  | 24-Lead SOIC_W      | RW-24          |

| AD420AR-32-REEL    | -40°C to +85°C    | 32 V                  | 24-Lead SOIC_W      | RW-24          |

| AD420ARZ-32        | -40°C to +85°C    | 32 V                  | 24-Lead SOIC_W      | RW-24          |

| AD420ARZ-32-REEL   | −40°C to +85°C    | 32 V                  | 24-Lead SOIC_W      | RW-24          |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

**NOTES**