# **ANALOG** 40-Channel, 3 V/5 V, Single-Supply, Serial, 14-Bit *dense*DAC<sup>®</sup>

## **Data Sheet**

## AD5384

#### **FEATURES**

#### **Guaranteed monotonic**

Relative accuracy (INL): ±4 LSB maximum On-chip 1.25 V/2.5 V, 10 ppm/°C reference Temperature range: -40°C to +85°C Rail-to-rail output amplifier Power-down Package type: 100-ball CSP\_BGA User interfaces Serial (SPI-/QSPI™-/MICROWIRE®-/DSP-compatible, featuring data readback) I<sup>2</sup>C-compatible

#### **INTEGRATED FUNCTIONS**

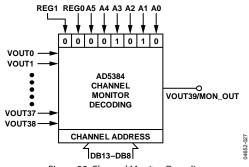

**Channel monitor**

Simultaneous output update via LDAC Clear function to user programmable code Amplifier boost mode to optimize slew rate User programmable offset and gain adjust Toggle mode enables square wave generation Thermal monitor

#### APPLICATIONS

Variable optical attenuators (VOAs) Level settings (automatic test equipment [ATE]) Optical micro-electromechanical systems (MEMS) control systems Instrumentation

Figure 1.

Rev. C Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

#### One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2004-2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## AD5384\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

## COMPARABLE PARTS

View a parametric search of comparable parts.

#### DOCUMENTATION

#### Data Sheet

• AD5384: 40-Channel, 3 V/5 V, Single-Supply, Serial, 14-Bit denseDAC Data Sheet

#### **Product Highlight**

• Extending the *dense*DAC<sup>™</sup> Multichannel D/As

## SOFTWARE AND SYSTEMS REQUIREMENTS $\square$

AD5380 IIO Multi-Channel DAC Linux Driver

#### REFERENCE MATERIALS

#### **Solutions Bulletins & Brochures**

Digital to Analog Converters ICs Solutions Bulletin

#### **Technical Articles**

Software Calibration Reduces D/A Converter Offset and Gain Errors

## DESIGN RESOURCES

- AD5384 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all AD5384 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK

Submit feedback for this data sheet.

## TABLE OF CONTENTS

| Features 1                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------|

| Integrated Functions                                                                                                                 |

| Applications1                                                                                                                        |

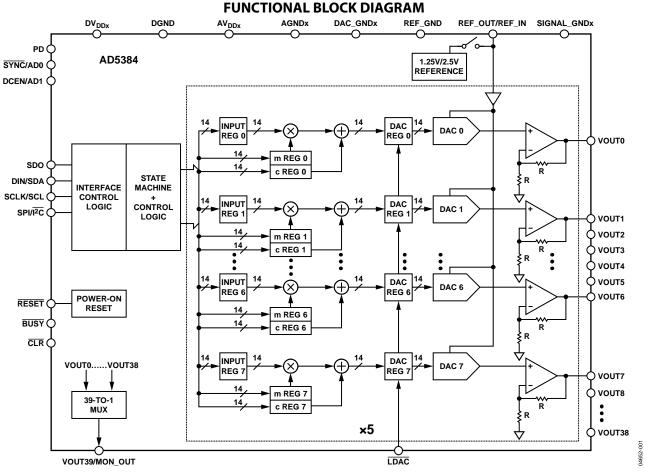

| Functional Block Diagram1                                                                                                            |

| Revision History                                                                                                                     |

| General Description                                                                                                                  |

| Specifications                                                                                                                       |

| AC Characteristics                                                                                                                   |

| Timing Characteristics7                                                                                                              |

| Absolute Maximum Ratings10                                                                                                           |

| ESD Caution10                                                                                                                        |

|                                                                                                                                      |

| Pin Configuration and Function Descriptions11                                                                                        |

| Pin Configuration and Function Descriptions                                                                                          |

|                                                                                                                                      |

| Typical Performance Characteristics                                                                                                  |

| Typical Performance Characteristics                                                                                                  |

| Typical Performance Characteristics 15   Terminology 18   Functional Description 19                                                  |

| Typical Performance Characteristics                                                                                                  |

| Typical Performance Characteristics 15   Terminology 18   Functional Description 19   DAC Architecture—General 19   Data Decoding 19 |

#### **REVISION HISTORY**

#### 6/14-Rev. B to Rev. C

#### 1/14—Rev. A to Rev. B

| Updated FormatUniversal                                                                    |

|--------------------------------------------------------------------------------------------|

| Changed DVDD to $DV_{\text{DDX}}\text{,}$ AVDD to $AV_{\text{DDx}}\text{,}$ AGND to AGNDx, |

| VOUT to VOUT <sub>x</sub> , REFIN TO REF_IN, REFOUT to REF_OUT,                            |

| SCLK to SCLK/SCL, DAC GND to DAC_GND, SIGNAL GND                                           |

| to SIGNAL_GND, REFGND to REF_GND, SYNC/AD 0 to                                             |

| SYNC/AD0, DCEN/AD1 to DCEN/AD1,                                                            |

| DIN to DIN/SDA Throughout                                                                  |

| Changes to Title and Features Section1                                                     |

| Deleted Table 1 and Table 2; Renumbered Sequentially 3                                     |

| Changes to Table 1                                                                         |

| Changed $AV_{DD}$ = 2.7 V to 3.6 V to $AV_{DD}$ = 4.5 V to 5.5 V,                          |

| AC Characteristics Section                                                                 |

| Changes to Table 2                                                                         |

| Deleted AD5384-3 Specifications Section and Table 57                                       |

| Changes to Serial Interface Section and Table 37                                           |

| Deleted AC Characteristics Section and Table 69                                            |

| Change to I <sup>2</sup> C Serial Interface Section9                                       |

| Changes to Absolute Maximum Ratings Section and Table 5 10                                 |

| Changes to Table 611                                                                       |

|                                                                                            |

|    | Reset Function                                    | . 23 |

|----|---------------------------------------------------|------|

|    | Asynchronous Clear Function                       | . 23 |

|    | BUSY and LDAC Functions                           | . 23 |

|    | Power-On Reset                                    | . 23 |

|    | Power-Down Feature                                | . 23 |

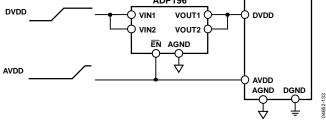

|    | Power Supply Sequencing                           | . 23 |

| Ir | iterfaces                                         | . 24 |

|    | DSP-, SPI-, Microwire-Compatible Serial Interface | . 24 |

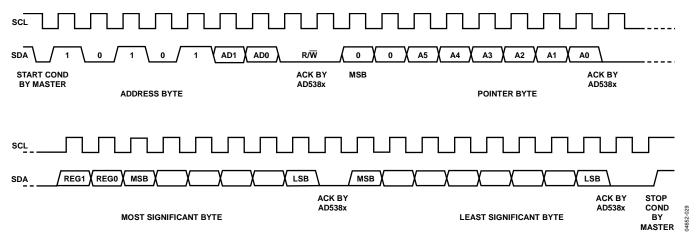

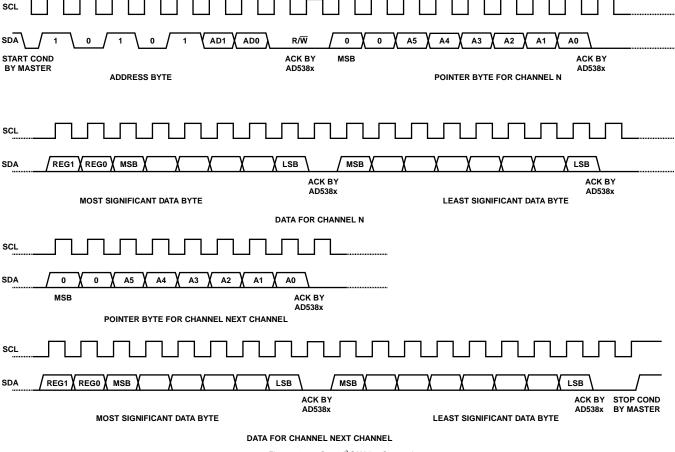

|    | I <sup>2</sup> C Serial Interface                 | . 26 |

| A  | pplications Information                           | . 29 |

|    | Power Supply Decoupling                           | . 29 |

|    | Power Supply Sequencing                           | . 29 |

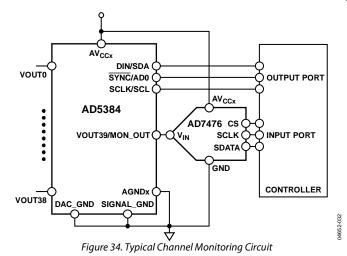

|    | Monitor Function                                  | . 30 |

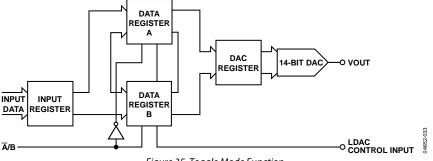

|    | Toggle Mode Function                              | . 30 |

|    | Thermal Monitor Function                          | . 31 |

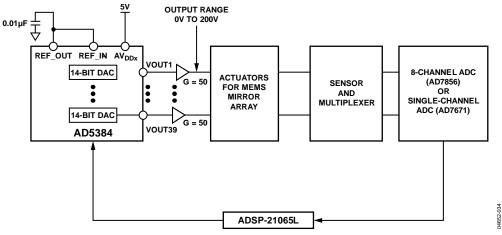

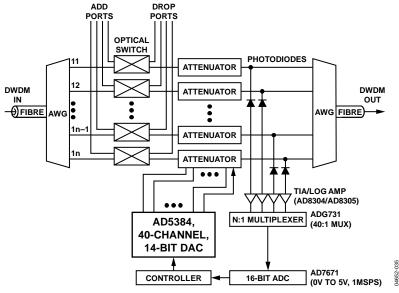

|    | AD5384 in a MEMS-Based Optical Switch             | . 31 |

|    | Optical Attenuators                               | . 32 |

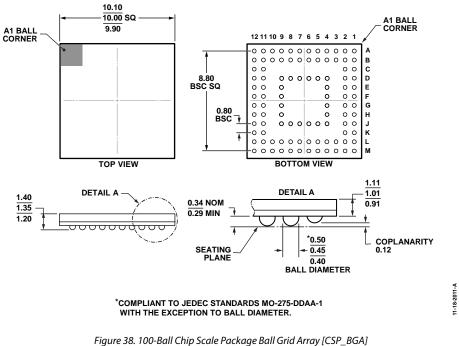

| С  | utline Dimensions                                 | . 33 |

|    | Ordering Guide                                    | . 33 |

|    |                                                   |      |

| Changes to Figure 9, Figure 10, and Figure 12 15              |

|---------------------------------------------------------------|

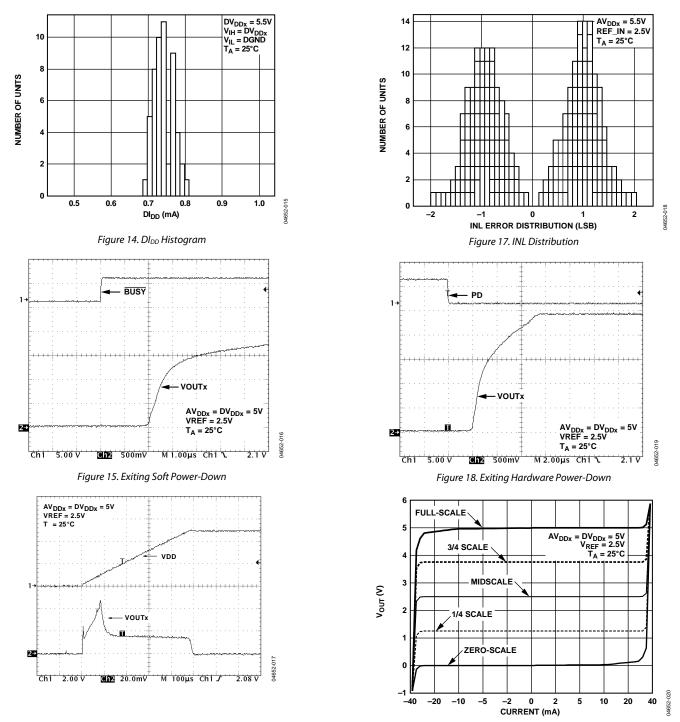

| Changes to Figure 14, Figure 15, Figure 16, and Figure 18 16  |

| Deleted Table 11 15                                           |

| Changes to Terminology Section                                |

| Deleted Figure 11; Renumbered Sequentially 18                 |

| Changes to Soft Reset Section                                 |

| Changes to Control Register Contents 21                       |

| Deleted Figure 23 20                                          |

| Changes to Table 14 22                                        |

| Changes to Reset Function Section, Asynchronous Clear         |

| Function Section, and Power-On Reset Section 23               |

| Added Power Supply Sequencing Section 23                      |

| Deleted Microprocessor Interfacing Section, AD5384 to         |

| MC68HC11 Section, Figure 32, AD5384 to PIC16C6x/7x            |

| Section, Figure 33, AD5384 to 8051 Section, Figure 34, AD5384 |

| to ADSP-2101/ADSP-2103 Section, and Figure 35 31              |

| Updated Outline Dimensions                                    |

| Changes to Ordering Guide                                     |

#### 10/04—Rev. 0 to Rev. A

| Changes to | Table 19       | 24 |

|------------|----------------|----|

| Changes to | Ordering Guide | 35 |

7/04—Revision 0: Initial Version

## **GENERAL DESCRIPTION**

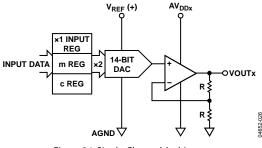

The AD5384 is a complete single-supply, 40-channel, 14-bit digital-to-analog converter (DAC) available in a 100-ball CSP\_BGA package. All 40 channels have an on-chip output amplifier with rail-to-rail operation. The AD5384 includes an internal 1.25 V/2.5 V, 10 ppm/°C reference, an on-chip channel monitor function that multiplexes the analog outputs to a common MON\_OUT pin for external monitoring, and an output amplifier boost mode that allows the amplifier slew rate to be optimized. The AD5384 contains a serial interface compatible with SPI, QSPI, MICROWIRE, and DSP interface standards with interface speeds in excess of 30 MHz and an I<sup>2</sup>C-compatible interface supporting 400 kHz data transfer rate. An input register followed by a DAC register provides double buffering, allowing the DAC outputs to be updated independently or simultaneously, using the  $\overline{\text{LDAC}}$  input. Each channel has a programmable gain and offset adjust register letting the user fully calibrate any DAC channel. Power consumption is typically 0.25 mA per channel with boost mode off.

## SPECIFICATIONS

$AV_{DDx} = 4.5 \text{ V}$  to 5.5 V;  $DV_{DDx} = 2.7 \text{ V}$  to 5.5 V, AGNDx = DGND = 0 V; external REF\_IN = 2.5 V; all specifications T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. The AD5384 is calibrated using an external 2.5 V reference. Temperature range-40°C to +85°C.

| Parameter                                      | Min   | Тур | Мах        | Unit       | Test Conditions/Comments                                                              |

|------------------------------------------------|-------|-----|------------|------------|---------------------------------------------------------------------------------------|

| ACCURACY                                       |       |     |            |            |                                                                                       |

| Resolution                                     |       | 14  |            | Bits       |                                                                                       |

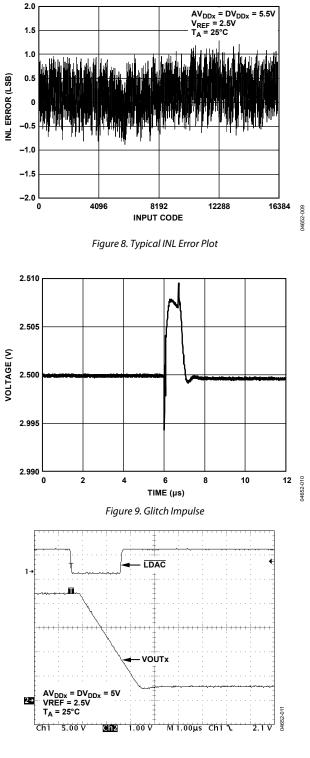

| Relative Accuracy <sup>1</sup> (INL)           |       |     | ±4         | LSB        | ±1 LSB typical                                                                        |

| Differential Nonlinearity (DNL)                | -1    |     | +2         | LSB        | Guaranteed monotonic by design over temperature                                       |

| Zero-Scale Error                               |       |     | 4          | mV         |                                                                                       |

| Offset Error                                   |       |     | ±4         | mV         | Measured at Code 32 in the linear region                                              |

| Offset Error Temperature Coefficient           |       | ±5  |            | μV/°C      |                                                                                       |

| Gain Error                                     |       |     | ±0.05      | % FSR      | At 25°C                                                                               |

|                                                |       |     | ±0.06      | % FSR      | T <sub>MIN</sub> to T <sub>MAX</sub>                                                  |

| Gain Temperature Coefficient <sup>2</sup>      |       | 2   |            | ppm FSR/°C |                                                                                       |

| DC Crosstalk <sup>2</sup>                      |       |     | 1          | LSB        |                                                                                       |

| REFERENCE INPUT/OUTPUT                         |       |     |            |            |                                                                                       |

| Reference Input <sup>2</sup>                   |       |     |            |            |                                                                                       |

| Reference Input Voltage                        |       | 2.5 |            | V          | $\pm 1\%$ for specified performance,<br>AV <sub>DDx</sub> = 2 × REF_IN + 50 mV        |

| DC Input Impedance                             | 1     |     |            | MΩ         | Typically 100 MΩ                                                                      |

| Input Current                                  |       |     | ±1         | μΑ         | Typically ±30 nA                                                                      |

| Reference Range                                | 1     |     | $V_{DD}/2$ | V          |                                                                                       |

| Reference Output <sup>3</sup>                  |       |     |            |            | Enabled via CR10 in the AD5384 control register (CR12) and selects the output voltage |

| Output Voltage                                 | 2.495 |     | 2.505      | V          | At ambient, CR12 = 1, optimized for 2.5 V operation                                   |

|                                                | 1.22  |     | 1.28       | V          | CR12 = 0                                                                              |

| Reference Temperature Coefficient <sup>2</sup> |       |     | ±10        | ppm        | Temperature range: 25°C to 85°C                                                       |

|                                                |       |     | ±15        | ppm        | Temperature range: –40°C to +85°C                                                     |

| Output Impedance                               |       | 800 |            | Ω          |                                                                                       |

| OUTPUT CHARACTERISTICS <sup>2</sup>            |       |     |            |            |                                                                                       |

| Output Voltage Range <sup>1</sup>              | 0     |     | AVDD       | V          |                                                                                       |

| Short-Circuit Current                          |       |     | 40         | mA         |                                                                                       |

| Load Current                                   |       |     | ±1         | mA         |                                                                                       |

| Capacitive Load Stability                      |       |     |            |            |                                                                                       |

| $R_L = \infty$                                 |       |     | 200        | pF         |                                                                                       |

| $R_L = 5 k\Omega$                              |       |     | 1000       | pF         |                                                                                       |

| DC Output Impedance                            |       |     | 0.6        | Ω          |                                                                                       |

| MONITOR PIN                                    |       |     |            |            |                                                                                       |

| Output Impedance                               |       | 1   |            | kΩ         |                                                                                       |

| Three-State Leakage Current                    |       | 100 |            | nA         |                                                                                       |

| LOGIC INPUTS (EXCEPT SDA, SCL) <sup>2</sup>    |       |     |            |            | $DV_{DDx} = 2.7 V \text{ to } 5.5 V$                                                  |

| Input High Voltage, V <sub>II</sub>            | 2     |     |            | V          |                                                                                       |

| Input Low Voltage, V <sub>L</sub>              |       |     |            |            |                                                                                       |

| $DV_{DDx} > 3.6 V$                             |       |     | 0.8        | V          |                                                                                       |

| $DV_{DDx} \leq 3.6 V$                          |       |     | 0.6        | V          |                                                                                       |

| Input Current                                  |       |     | ±10        | μΑ         | Total for all pins; $T_A = T_{MIN}$ to $T_{MAX}$                                      |

| Pin Capacitance                                |       |     | 10         | pF         |                                                                                       |

## **Data Sheet**

| Parameter                              | Min                           | Тур | Max                          | Unit       | Test Conditions/Comments                                                    |

|----------------------------------------|-------------------------------|-----|------------------------------|------------|-----------------------------------------------------------------------------|

| LOGIC INPUTS (SDA, SCL ONLY)           |                               |     |                              |            |                                                                             |

| Input High Voltage, V⊩                 | $0.7 \times DV_{\text{DDx}}$  |     |                              | V          | SMBus-compatible at DV <sub>DDx</sub> < 3.6 V                               |

| Input Low Voltage, V⊾                  |                               |     | $0.3 \times DV_{\text{DDx}}$ | V          | SMBus-compatible at DV <sub>DDx</sub> < 3.6 V                               |

| Input Leakage Current, I <sub>IN</sub> |                               |     | ±1                           | μA         |                                                                             |

| Input Hysteresis, V <sub>HYST</sub>    | $0.05 \times DV_{\text{DDx}}$ |     |                              | V          |                                                                             |

| Input Capacitance, C <sub>IN</sub>     |                               | 8   |                              | pF         |                                                                             |

| Glitch Rejection                       |                               |     | 50                           | ns         | Input filtering suppresses noise spikes of less than 50 ns                  |

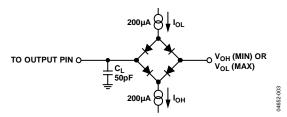

| LOGIC OUTPUTS (BUSY, SDO) <sup>2</sup> |                               |     |                              |            |                                                                             |

| Output Low Voltage, V <sub>OL</sub>    |                               |     | 0.4                          | V max      | $DV_{DDx} = 5 V \pm 10\%$ , sinking 200 $\mu$ A                             |

|                                        |                               |     | 0.4                          | V max      | $DV_{DDx} = 2.7 V$ to 3.6 V, sinking 200 $\mu$ A                            |

| Output High Voltage, V <sub>он</sub>   | DV <sub>DDx</sub> – 1         |     |                              | V min      | $DV_{DDx} = 5 V \pm 10\%$ , sourcing 200 $\mu$ A                            |

|                                        | DV <sub>DDx</sub> - 0.5       |     |                              | V min      | $DV_{DDx} = 2.7 V$ to 3.6 V, sourcing 200 $\mu$ A                           |

| High Impedance Leakage Current         |                               |     | ±1                           | μΑ         | SDO only                                                                    |

| High Impedance Output Capacitance      |                               | 5   |                              | pF         | SDO only                                                                    |

| LOGIC OUTPUT (SDA) <sup>2</sup>        |                               |     |                              |            |                                                                             |

| Output Low Voltage, V <sub>oL</sub>    |                               |     | 0.4                          | V          | $I_{SINK} = 3 \text{ mA}$                                                   |

|                                        |                               |     | 0.6                          | V          | $I_{SINK} = 6 \text{ mA}$                                                   |

| Three-State Leakage Current            |                               |     | ±1                           | μΑ         |                                                                             |

| Three-State Output Capacitance         |                               | 8   |                              | pF         |                                                                             |

| POWER REQUIREMENTS                     |                               |     |                              |            |                                                                             |

| AV <sub>DDx</sub>                      | 4.5                           |     | 5.5                          | V          |                                                                             |

| DV <sub>DDx</sub>                      | 2.7                           |     | 5.5                          | V          |                                                                             |

| Power Supply Sensitivity <sup>2</sup>  |                               |     |                              |            |                                                                             |

| ΔMidscale/ΔAV <sub>DDx</sub>           |                               | -85 |                              | dB         |                                                                             |

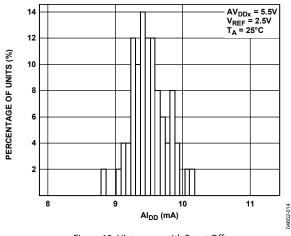

| Aldd                                   |                               |     | 0.375                        | mA/channel | Outputs unloaded, boost off;<br>0.25 mA per channel typical                 |

|                                        |                               |     | 0.475                        | mA/channel | Outputs unloaded, boost on;<br>0.325 mA per channel typical                 |

| DI <sub>DD</sub>                       |                               |     | 1                            | mA         | $V_{IH} = DV_{DDx}, V_{IL} = DGND$                                          |

| Al <sub>DD</sub> (Power-Down)          |                               |     | 20                           | μA         | Typically 100 nA                                                            |

| DI <sub>DD</sub> (Power-Down)          |                               |     | 20                           | μA         | Typically 1 μA                                                              |

| Power Dissipation                      |                               |     | 80                           | mW         | Outputs unloaded, boost off,<br>AV <sub>DDx</sub> = DV <sub>DDx</sub> = 5 V |

<sup>1</sup> Accuracy guaranteed from V<sub>out</sub> = 10 mV to AV<sub>DD</sub>- 50 mV.

<sup>2</sup> Guaranteed by characterization, not production tested.

<sup>3</sup> Default on the AD5384 is 2.5 V. Programmable to 1.25 V via CR12 in the AD5384 control register; operating the AD5384 with a 1.25 V reference leads to degraded accuracy specifications.

#### **AC CHARACTERISTICS**

AV<sub>DDx</sub> = 4.5 V to 5.5 V; DV<sub>DDx</sub> = 2.7 V to 5.5 V; AGND<sub>x</sub> = DGND = 0 V. Guaranteed by design and characterization, not production tested.

## Table 2.

| Parameter                       | Min | Тур | Max | Unit   | Test Conditions/Comments                                                            |

|---------------------------------|-----|-----|-----|--------|-------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE             |     |     |     |        |                                                                                     |

| Output Voltage Settling Time    |     |     |     |        | Boost mode off, CR11 = 0, $1/4$ scale to $3/4$ scale change settling to $\pm 1$ LSB |

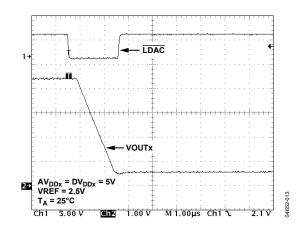

|                                 |     | 3   |     | μs     | Boost mode off, CR11 = 0                                                            |

|                                 |     |     | 8   | μs     | Boost mode off, $CR11 = 0$                                                          |

| Slew Rate <sup>1</sup>          |     | 1.5 |     | V/µs   | Boost mode off, $CR11 = 0$                                                          |

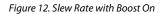

|                                 |     | 2.5 |     | V/µs   | Boost mode on, CR11 = 1                                                             |

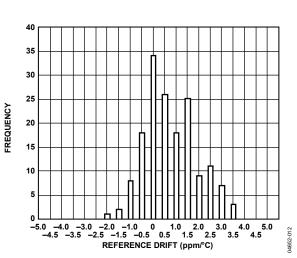

| Digital-to-Analog Glitch Energy |     | 12  |     | nV-sec |                                                                                     |

| Glitch Impulse Peak Amplitude   |     | 15  |     | mV     |                                                                                     |

| Channel-to-Channel Isolation    |     | 100 |     | dB     | See the Terminology section                                                         |

| DAC-to-DAC Crosstalk            |     | 1   |     | nV-sec | See the Terminology section                                                         |

| Digital Crosstalk               |     | 0.8 |     | nV-sec |                                                                                     |

| Digital Feedthrough             |     | 0.1 |     | nV-sec | Effect of input bus activity on DAC output under test                               |

| Output Noise 0.1 Hz to 10 Hz    |     | 15  |     | μV p-p | External reference, midscale loaded to DAC                                          |

|                                 |     | 40  |     | μV p-p | Internal reference, midscale loaded to DAC                                          |

| Output Noise Spectral Density   |     |     |     |        |                                                                                     |

| At 1 kHz                        |     | 150 |     | nV/√Hz |                                                                                     |

| At 10 kHz                       |     | 100 |     | nV/√Hz |                                                                                     |

<sup>1</sup> Program the slew rate via the current boost control bit (CR11).

#### TIMING CHARACTERISTICS

#### Serial Interface

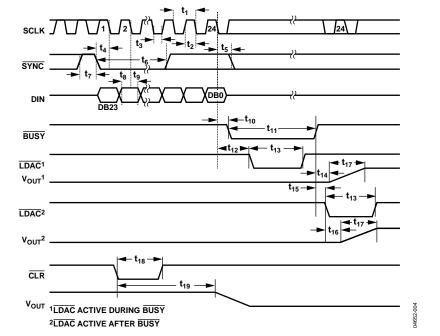

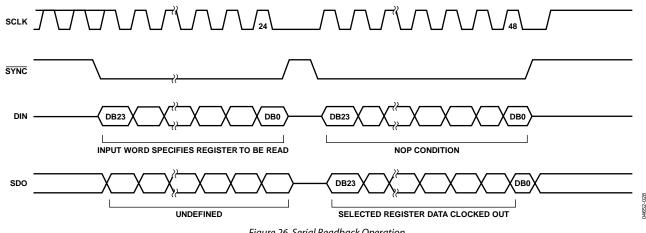

$DV_{DDx} = 2.7 V$  to 5.5 V;  $AV_{DDx} = 4.5 V$  to 5.5 V;  $AGND_x = DGND = 0 V$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. The AD5384 must remain powered up when part of a multidevice system with a common I<sup>2</sup>C bus. Guaranteed by design and characterization, not production tested. All input signals are specified with  $t_r = t_f = 5 ns (10\% to 90\% of DV_{DDx})$  and are timed from a voltage level of 1.2 V. See Figure 2, Figure 3, Figure 4, and Figure 5.

| Table | 3  |

|-------|----|

| raute | э. |

| Parameter                    | Min | Тур | Max  | Unit | Description                                             |

|------------------------------|-----|-----|------|------|---------------------------------------------------------|

| t <sub>1</sub>               | 33  |     |      | ns   | SCLK cycle time                                         |

| t <sub>2</sub>               | 13  |     |      | ns   | SCLK high time                                          |

| t <sub>3</sub>               | 13  |     |      | ns   | SCLK low time                                           |

| t4                           | 13  |     |      | ns   | SYNC falling edge to SCLK falling edge setup time       |

| t5 <sup>1</sup>              | 13  |     |      | ns   | 24 <sup>th</sup> SCLK falling edge to SYNC falling edge |

| $t_6^1$                      | 33  |     |      | ns   | Minimum SYNC low time                                   |

| t <sub>7</sub>               | 10  |     |      | ns   | Minimum SYNC high time                                  |

| t <sub>7A</sub>              | 140 |     |      | ns   | Minimum SYNC high time in readback mode                 |

| t <sub>8</sub>               | 5   |     |      | ns   | Data setup time                                         |

| t9                           | 4.5 |     |      | ns   | Data hold time                                          |

| t <sub>10</sub> 1            |     |     | 36   | ns   | 24 <sup>th</sup> SCLK falling edge to BUSY falling edge |

| <b>t</b> 11                  |     |     | 670  | ns   | BUSY pulse width low (single channel update)            |

| t <sub>12</sub> <sup>1</sup> | 20  |     |      | ns   | 24 <sup>th</sup> SCLK falling edge to LDAC falling edge |

| <b>t</b> 13                  | 20  |     |      | ns   | LDAC pulse width low                                    |

| <b>t</b> 14                  | 100 |     | 2000 | ns   | BUSY rising edge to DAC output response time            |

| <b>t</b> 15                  | 0   |     |      | ns   | BUSY rising edge to LDAC falling edge                   |

| t <sub>16</sub>              | 100 |     |      | ns   | LDAC falling edge to DAC output response time           |

| t <sub>17</sub>              |     | 3   |      | μs   | DAC output settling time boost mode off                 |

| t <sub>18</sub>              | 20  |     |      | ns   | CLR pulse width low                                     |

| <b>t</b> <sub>19</sub>       |     |     | 40   | μs   | CLR pulse activation time                               |

| $t_{20}^2$                   |     |     | 30   | ns   | SCLK rising edge to SDO valid                           |

| $t_{21}^2$                   | 5   |     |      | ns   | SCLK falling edge to SYNC rising edge                   |

| $t_{22}^2$                   | 8   |     |      | ns   | SYNC rising edge to SCLK rising edge                    |

| t <sub>23</sub>              | 20  |     |      | ns   | SYNC rising edge to LDAC falling edge                   |

<sup>1</sup> Standalone mode only.

<sup>2</sup> Daisy-chain mode only.

Figure 2. Load Circuit for Digital Output Timing

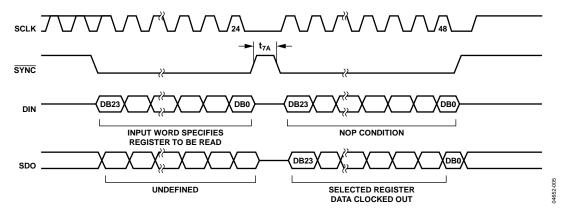

Figure 4. Serial Interface Timing Diagram (Data Readback Mode)

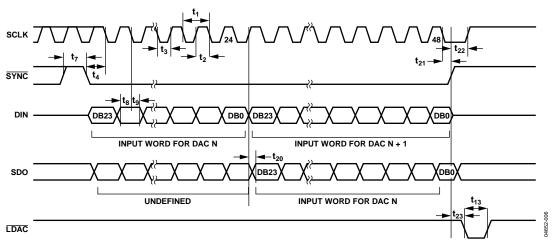

Figure 5. Serial Interface Timing Diagram (Daisy-Chain Mode)

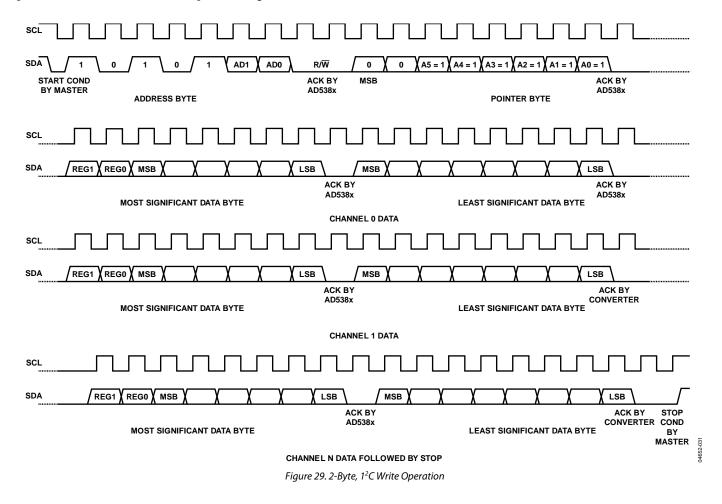

#### **I<sup>2</sup>C Serial Interface**

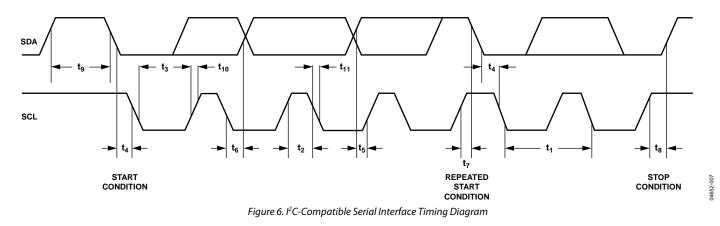

$DV_{DDx} = 2.7 V$  to 5.5 V;  $AV_{DDx} = 4.5 V$  to 5.5 V;  $AGND_x = DGND = 0 V$ ; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. See Figure 6. Limit at  $T_{MIN}$ ,  $T_{MAX}$ .

|--|

| Parameter        | Min              | Тур Мах | Unit | Description                                                       |

|------------------|------------------|---------|------|-------------------------------------------------------------------|

| fscl             |                  | 400     | kHz  | SCL clock frequency                                               |

| t <sub>1</sub>   | 2.5              |         | μs   | SCL cycle time                                                    |

| t <sub>2</sub>   | 0.6              |         | μs   | SCL high time, t <sub>HIGH</sub>                                  |

| t <sub>3</sub>   | 1.3              |         | μs   | SCL low time, t <sub>LOW</sub>                                    |

| t <sub>4</sub>   | 0.6              |         | μs   | Start/repeated start condition hold time, t <sub>HD, STA</sub>    |

| t <sub>5</sub>   | 100              |         | ns   | Data setup time, t <sub>su,DAT</sub>                              |

| t <sub>6</sub> 1 |                  | 0.9     | μs   | Data hold time, t <sub>HD,DAT</sub>                               |

|                  | 0                |         | μs   | Data hold time, t <sub>HD,DAT</sub>                               |

| t <sub>7</sub>   | 0.6              |         | μs   | Setup time for repeated start, tsu,sta                            |

| t <sub>8</sub>   | 0.6              |         | μs   | Stop condition setup time, t <sub>SU, STO</sub>                   |

| t9               | 1.3              |         | μs   | Bus free time between a stop and a start condition, tBUF          |

| t <sub>10</sub>  |                  | 300     | ns   | Rise time of SCL and SDA when receiving, $t_{\text{R}}$           |

|                  | 0                |         | ns   | Rise time of SCL and SDA when receiving (CMOS-compatible), $t_R$  |

| t11              |                  | 300     | ns   | Fall time of SDA when transmitting, t <sub>F</sub>                |

|                  | 0                |         | ns   | Fall time of SDA when receiving (CMOS-compatible), t <sub>F</sub> |

|                  |                  | 300     | ns   | Fall time of SCL and SDA when receiving, t <sub>F</sub>           |

|                  | $20 + 0.1 C_b^2$ |         | ns   | Fall time of SCL and SDA when transmitting, t <sub>F</sub>        |

| Cb               |                  | 400     | pF   | Capacitive load for each bus line                                 |

<sup>1</sup> A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the V<sub>H</sub> min of the SCL signal) in order to bridge the undefined region of the SCL falling edge.

$^2$  Cb is the total capacitance, in pF, of one bus line.  $t_{\text{R}}$  and  $t_{\text{F}}$  are measured between 0.3 DV\_{\text{DDx}} and 0.7 DV\_{\text{DDx}}.

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}$ C, unless otherwise noted. Transient currents of up to 100 mA do not cause silicon controlled rectifier (SCR) latch-up.

| Table 5. |

|----------|

|----------|

| Table 5.                                      |                                     |

|-----------------------------------------------|-------------------------------------|

| Parameter                                     | Rating                              |

| AV <sub>DDx</sub> to AGND <sub>x</sub>        | –0.3 V to +7 V                      |

| DV <sub>DDx</sub> to DGND                     | –0.3 V to +7 V                      |

| Digital Inputs to DGND                        | -0.3 V to DV <sub>DDx</sub> + 0.3 V |

| SDA/SCL to DGND                               | –0.3 V to + 7 V                     |

| Digital Outputs to DGND                       | -0.3 V to DV <sub>DDx</sub> + 0.3 V |

| REF_IN/REF_OUT to AGND <sub>x</sub>           | -0.3 V to AV <sub>DDx</sub> + 0.3 V |

| AGND <sub>x</sub> to DGND                     | –0.3 V to +0.3 V                    |

| VOUTx to AGND <sub>x</sub>                    | -0.3 V to AV <sub>DDx</sub> + 0.3 V |

| Analog Inputs to AGND                         | -0.3 V to AV <sub>DDx</sub> + 0.3 V |

| Operating Temperature Range                   |                                     |

| Commercial (B Version)                        | -40°C to +85°C                      |

| Storage Temperature Range                     | –65°C to +150°C                     |

| Junction Temperature (TJ max)                 | 150°C                               |

| 100-Ball CSP_BGA Package                      |                                     |

| θ <sub>JA</sub> Thermal Impedance             | 40°C/W                              |

| Reflow Soldering                              |                                     |

| Peak Temperature                              | 230°C                               |

| ESD                                           |                                     |

| Human Body Model (HBM)                        | 6.5 kV                              |

| Field-Induced Charged Device<br>Model (FICDM) | 1.6 kV                              |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

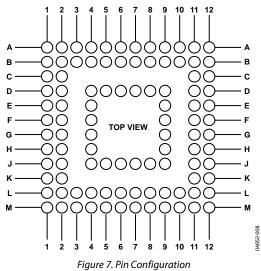

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### Table 6. Pin Function Descriptions

| Pin No.                                            | Mnemonic                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A12, B2, B11,<br>C11, K11, L2, L11,<br>M1, M12 | NC                                        | No Connect. Do not connect to these pins.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A2                                                 | VOUT24                                    | Buffered Analog Output. The analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. The output is capable of driving an output load of 5 k $\Omega$ to ground.<br>Typical output impedance is 0.5 $\Omega$ .                                                                                                                                                                                                                        |

| A3                                                 | CLR                                       | Asynchronous Clear Input. The CLR input is falling edge sensitive. When $\overline{\text{CLR}}$ is activated, all channels are updated with the data in the $\overline{\text{CLR}}$ code register. BUSY is low for a duration of 35 µs while all channels are being updated with the $\overline{\text{CLR}}$ code.                                                                                                                                               |

| A4                                                 | SYNC/AD0                                  | Multifunction Pin. In serial interface mode, the SYNC pin is the frame synchronization input signal for the serial clocks before the address register is updated.                                                                                                                                                                                                                                                                                                |

|                                                    |                                           | In I <sup>2</sup> C mode, AD0 acts as a hardware address pin used in conjunction with AD1 to determine the software address for the device on the I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                                          |

| A5                                                 | SCLK/SCL                                  | Multifunction Pin. In serial interface mode, data is clocked into the shift register on the falling edge of SCLK. SCLK operates at clock speeds up to 30 MHz.                                                                                                                                                                                                                                                                                                    |

|                                                    |                                           | In I <sup>2</sup> C mode, the SCL pin clocks data into the device. The data transfer rate in I <sup>2</sup> C mode is compatible with both 100 kHz and 400 kHz operating modes.                                                                                                                                                                                                                                                                                  |

| A6, B6, D6                                         | DV <sub>DD1</sub> to<br>DV <sub>DD3</sub> | Logic Power Supply. Guaranteed operating range is 2.7 V to 5.5 V. Decouple these pins with 0.1 $\mu F$ ceramic and 10 $\mu F$ tantalum capacitors to DGND.                                                                                                                                                                                                                                                                                                       |

| A7, B3, B7, D7                                     | DGND                                      | Ground for All Digital Circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A8                                                 | PD                                        | Power-Down (Level Sensitive, Active High). Use PD to place the device in low power mode, where $AI_{DD}$ reduces to 2 $\mu$ A and $DI_{DD}$ to 20 $\mu$ A. In power-down mode, all internal analog circuitry is placed in low power mode, and the analog output is configured as a high impedance output or provides a 100 k $\Omega$ load to ground, depending on how the power-down mode is configured. The serial interface remains active during power-down. |

| A9                                                 | DCEN/AD1                                  | Multifunction Pin. In SPI mode, the DCEN pin acts to enable the daisy-chain function. In I <sup>2</sup> C mode, the AD1 pin acts as a hardware address pin.                                                                                                                                                                                                                                                                                                      |

|                                                    |                                           | Daisy-Chain Select Input (Level Sensitive, Active High). When DCEN is high, this pin is used in conjunction with the SPI/I <sup>2</sup> C pin set high to enable the SPI serial interface in daisy-chain mode.                                                                                                                                                                                                                                                   |

|                                                    |                                           | In I <sup>2</sup> C mode, the AD1 pin acts as a hardware address pin used in conjunction with AD0 to determine the software address for this device on the I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                                 |

## AD5384

| Pin No. | Mnemonic                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10     | LDAC                                  | Load DAC Logic Input (Active Low). If LDAC is taken low while BUSY is inactive (high), the contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |                                       | of the input registers are transferred to the DAC registers, and the DAC outputs are updated. If LDAC is taken low while BUSY is active and internal calculations are taking place, the LDAC event is stored,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                                       | and the DAC registers are updated when BUSY goes inactive. However, any events on LDAC during                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                                       | power-on reset or at RESET are ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A11     | BUSY                                  | Digital CMOS Output. BUSY goes low during internal calculations of the data ( $\times$ 2) loaded to the DAC data register. During this time, the user can continue writing new data to the $\times$ 1, c, and m registers, but no further updates to the DAC registers and DAC outputs can take place. If LDAC is taken low while BUSY is low, this event is stored. BUSY also goes low during power-on reset, and when the BUSY pin is low. During this time, the interface is disabled, and any events on LDAC are ignored.                                                                                                                                                                                     |

|         |                                       | A CLR operation also brings BUSY low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| B1      | VOUT25                                | Buffered Analog Output. The analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. The output is capable of driving an output load of 5 k $\Omega$ to ground. Typical output impedance is 0.5 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B4      | DIN/SDA                               | In serial interface mode, DIN acts as the serial data input. Data must be valid on the falling edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |                                       | In I <sup>2</sup> C mode, this pin is the serial data pin (SDA) operating as an open-drain input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| B5      | SDO                                   | Serial Data Output in Serial Interface Mode. Three- <u>state</u> CMOS output. SDO can be used for daisy-chaining a number of devices together. Data is clocked out on SDO on the rising edge of SCLK, and is valid on the falling edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B8      | SPI/I <sup>2</sup> C                  | Serial Interface Mode Select. This is a multifunction pin. When this pin is high, SPI mode is selected. When this pin is low, $\overline{I^2C}$ is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B9      | RESET                                 | Asynchronous Digital Reset Input (Falling Edge Sensitive). The function of this pin is equivalent to that of the power-on reset generator. When this pin is taken low, the state machine initiates a reset sequence to digitally reset the ×1, m, c, and ×2 registers to their default power-on values. This sequence typically takes 270 µs. The falling edge of RESET initiates the RESET process, and BUSY goes low for the duration, returning high when RESET is complete. While BUSY is low, all interfaces are disabled, and all LDAC pulses are ignored. When BUSY returns high, the device resumes normal operation, and the status of the RESET pin is ignored until the next falling edge is detected. |

| B10     | VOUT22                                | Buffered Analog Output. The analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. The output is capable of driving an output load of 5 k $\Omega$ to ground. Typical output impedance is 0.5 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B12, C1 | VOUT23,<br>VOUT26                     | Buffered Analog Outputs. Each analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. Each output is capable of driving an output load of 5 k $\Omega$ to ground. Typical output impedance is 0.5 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C2, D2  | SIGNAL_GND4                           | Analog Ground Reference Points for Each Group of Eight Output Channels. All SIGNAL_GNDx pins are connected together internally and must be connected to the AGND plane as close as possible to the AD5384.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C12, D1 | VOUT21,<br>VOUT27                     | Buffered Analog Outputs. Each analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. Each output is capable of driving an output load of 5 k $\Omega$ to ground. Typical output impedance is 0.5 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D4, E4  | DAC_GND4                              | Each Group of Eight Channels Contains a DAC_GNDx Pin. This is the ground reference point for the internal 14-bit DAC. Connect these pins to the AGND plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D5      | AGND4                                 | Analog Ground Reference Point. Each group of eight channels contains an AGND pin. Connect all AGND pins externally to the AGND plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D8      | AGND3                                 | Analog Ground Reference Point. Each group of eight channels contains an AGND pin. Connect all AGND pins externally to the AGND plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D9, E9  | DAC_GND3                              | Each Group of Eight Channels Contains a DAC_GNDx Pin. This is the ground reference point for the internal 14-bit DAC. Connect these pins to the AGND plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D11     | VOUT20                                | Buffered Analog Output. The analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. The output is capable of driving an output load of 5 k $\Omega$ to ground.<br>Typical output impedance is 0.5 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D12, E1 | AV <sub>DD3</sub> , AV <sub>DD4</sub> | Analog Supply Pins. Each group of eight channels has a separate AV <sub>DDx</sub> pin. Short these pins internally and decouple them with a 0.1 $\mu$ F ceramic capacitor and a 10 $\mu$ F tantalum capacitor. Operating range is 4.5 V to 5.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| E2, F2  | SIGNAL_GND1                           | Analog Ground Reference Points for Each Group of Eight Output Channels. All SIGNAL_GNDx pins are connected together internally and must be connected to the AGND plane as close as possible to the AD5384.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## **Data Sheet**

| Pin No.                      | Mnemonic                                                   | Description                                                                                                                                                                                                                                                                                                    |

|------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E11, E12                     | VOUT17,<br>VOUT19                                          | Buffered Analog Outputs. Each analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. Each output is capable of driving an output load of 5 k $\Omega$ to ground. Typical output impedance is 0.5 $\Omega$ .                                                                      |

| F1                           | REF_GND                                                    | Ground Reference Point for the Internal Reference.                                                                                                                                                                                                                                                             |

| F4, G4                       | DAC_GND1                                                   | Each Group of Eight Channels Contains a DAC_GNDx Pin. This is the ground reference point for the internal 14-bit DAC. Connect these pins to the AGND plane.                                                                                                                                                    |

| F9, G9                       | SIGNAL_GND3                                                | Analog Ground Reference Points for Each Group of Eight Output Channels. All SIGNAL_GNDx pins are connected together internally and must be connected to the AGND plane as close as possible to the AD5384.                                                                                                     |

| F11, F12, G1,<br>G2, G11     | VOUT16,<br>VOUT18,<br>VOUT28,<br>VOUT29,<br>VOUT15         | Buffered Analog Outputs. Each analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. Each output is capable of driving an output load of 5 k $\Omega$ to ground.<br>Typical output impedance is 0.5 $\Omega$ .                                                                   |

| G12                          | AV <sub>DD2</sub>                                          | Analog Supply Pin. Each group of eight channels has a separate AV <sub>DDx</sub> pin. Short these pins internally and decouple them with a 0.1 $\mu$ F ceramic capacitor and a 10 $\mu$ F tantalum capacitor. Operating range is 4.5 V to 5.5 V.                                                               |

| H1                           | REF_OUT/<br>REF_IN                                         | Common REF_OUT/REF_IN pin. The default for this pin is a reference input (REF_IN). When the internal reference is selected, this pin is the reference output (REF_OUT). If the application requires an external reference, apply it to this pin. The control register enables/disables the internal reference. |

| H2                           | VOUT31                                                     | Buffered Analog Output. The analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. The output is capable of driving an output load of 5 k $\Omega$ to ground. Typical output impedance is 0.5 $\Omega$ .                                                                         |

| H4, J4                       | DAC_GND5                                                   | Each Group of Eight Channels Contains a DAC_GNDx Pin. This is the ground reference point for the internal 14-bit DAC. Connect these pins to the AGND plane.                                                                                                                                                    |

| H9, J9                       | SIGNAL_GND2                                                | Analog Ground Reference Points for Each Group of Eight Output Channels. All SIGNAL_GNDx pins are connected together internally and must be connected to the AGND plane as close as possible to the AD5384.                                                                                                     |

| H11, H12                     | VOUT13,<br>VOUT14                                          | Buffered Analog Outputs. Each analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. Each output is capable of driving an output load of 5 k $\Omega$ to ground. Typical output impedance is 0.5 $\Omega$ .                                                                      |

| J1                           | AV <sub>DD1</sub>                                          | Analog Supply Pin. Each group of eight channels has a separate AV <sub>DDx</sub> pin. Short these pins internally and decouple them with a 0.1 $\mu$ F ceramic capacitor and a 10 $\mu$ F tantalum capacitor. Operating range is 4.5 V to 5.5 V.                                                               |

| J2                           | VOUT30                                                     | Buffered Analog Output. The analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. The output is capable of driving an output load of 5 k $\Omega$ to ground. Typical output impedance is 0.5 $\Omega$ .                                                                         |

| J5                           | AGND1                                                      | Analog Ground Reference Point. Each group of eight channels contains an AGND pin. Connect all AGND pins externally to the AGND plane.                                                                                                                                                                          |

| J6, J7                       | DAC_GND2                                                   | Each Group of Eight Channels Contains a DAC_GNDx Pin. This is the ground reference point for the internal 14-bit DAC. Connect these pins to the AGND plane.                                                                                                                                                    |

| J8                           | AGND2                                                      | Analog Ground Reference Point. Each group of eight channels contains an AGND pin. Connect all AGND pins externally to the AGND plane.                                                                                                                                                                          |

| J11, J12, K1,<br>K2, K12, L1 | VOUT12,<br>VOUT11,<br>VOUT0,<br>VOUT1,<br>VOUT10,<br>VOUT2 | Buffered Analog Outputs. Each analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. Each output is capable of driving an output load of 5 k $\Omega$ to ground. Typical output impedance is 0.5 $\Omega$ .                                                                      |

| L3, L4                       | SIGNAL_GND5                                                | Analog Ground Reference Points for Each Group of Eight Output Channels. All SIGNAL_GNDx pins are connected together internally and must be connected to the AGND plane as close as possible to the AD5384.                                                                                                     |

| L5                           | AGND5                                                      | Analog Ground Reference Point. Each group of eight channels contains an AGND pin. Connect<br>all AGND pins externally to the AGND plane.                                                                                                                                                                       |

## AD5384

| Pin No.                                    | Mnemonic                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L6, L7, L8, L9,<br>L10, L12, M2,<br>M3, M4 | VOUT6,<br>VOUT32,<br>VOUT34,<br>VOUT36,<br>VOUT38,<br>VOUT9,<br>VOUT3,<br>VOUT4,<br>VOUT5 | Buffered Analog Outputs. Each analog output is driven by a rail-to-rail output amplifier operating at a gain of 2. Each output is capable of driving an output load of 5 k $\Omega$ to ground.<br>Typical output impedance is 0.5 $\Omega$ .                                                                                                                                                                                                                                                                               |

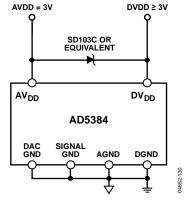

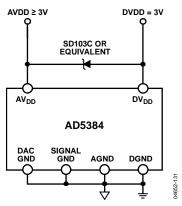

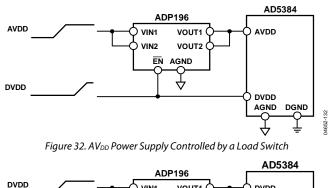

| M5                                         | AV <sub>DD5</sub>                                                                         | Analog Supply Pin. Each group of eight channels has a separate $AV_{DDx}$ pin. Short these pins internally and decouple them with a 0.1 $\mu$ F ceramic capacitor and a 10 $\mu$ F tantalum capacitor. Operating range is 4.5 V to 5.5 V.                                                                                                                                                                                                                                                                                  |