# 2-/4-/8-Channel, 1 MSPS, Ultralow Power, 12-Bit SAR ADC

# AD7091R-2/AD7091R-4/AD7091R-8

### **FEATURES**

**Data Sheet**

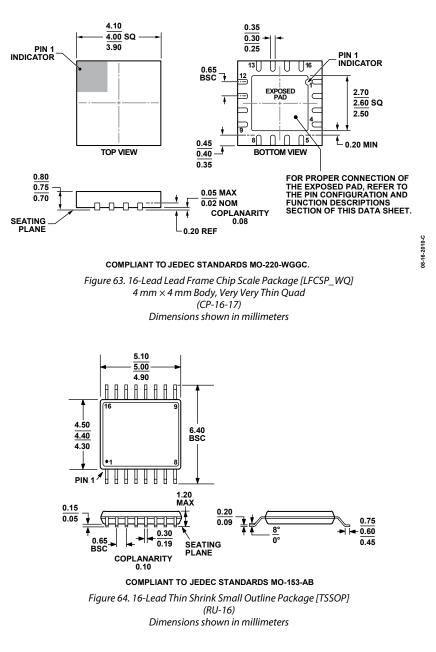

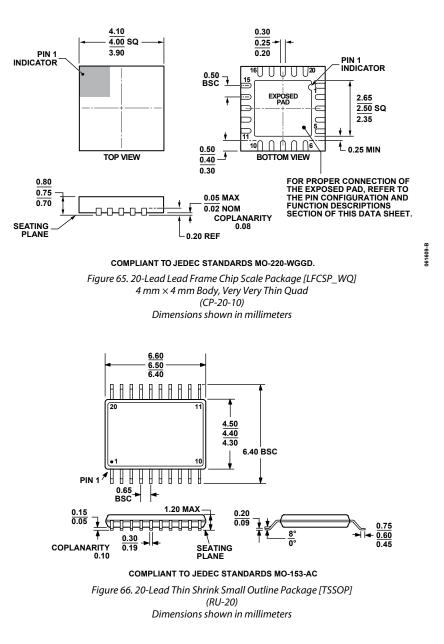

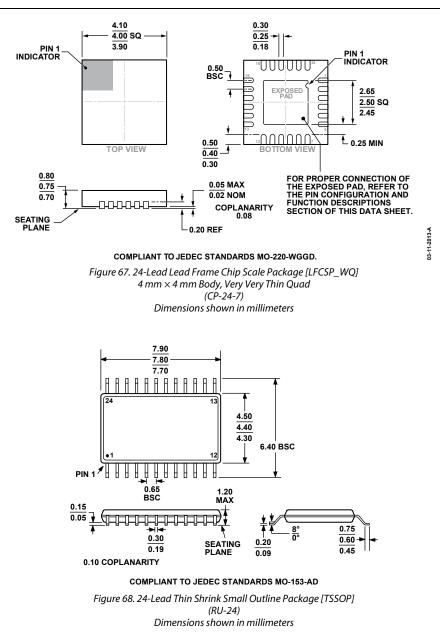

Ultralow system power Flexible power/throughput rate management Normal mode 1.4 mW at 1 MSPS Power-down mode 550 nA typical at VDD = 5.25 V 435 nA typical at V<sub>DD</sub> = 3 V Programmable ALERT interrupt pin (4-/8-channel models) **High performance** 1 MSPS throughput with no latency/pipeline delay SNR: 70 dB typical at 10 kHz input frequency THD: -80 dB typical at 10 kHz input frequency INL: ±0.7 LSB typical, ±1.0 LSB maximum Small system footprint On-chip accurate 2.5 V reference, 5 ppm/°C typical drift MUX<sub>OUT</sub>/ADC<sub>IN</sub> to allow single buffer amplifier Daisv-chain mode 16-lead, 20-lead, and 24-lead 4 mm × 4 mm LFCSP packages 16-lead, 20-lead, and 24-lead TSSOP packages Easy to use SPI/QSPI<sup>™</sup>/MICROWIRE<sup>™</sup>/DSP compatible digital interface Integrated programmable channel sequencer BUSY indication available (4-/8-channel models) Built in features for control and monitoring applications GPOx pins available (4-/8-channel models) Wide operating range Temperature range: -40°C to +125°C Specified for VDD of 2.7 V to 5.25 V

#### APPLICATIONS

Rev. C

Battery-powered systems Personal digital assistants Medical instruments Mobile communications Instrumentation and control systems Data acquisition systems Optical sensors Diagnostic/monitoring functions

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change withhout notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

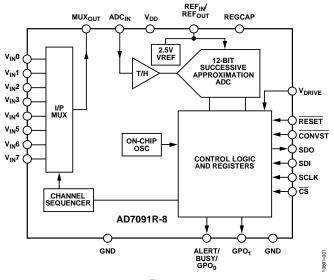

### FUNCTIONAL BLOCK DIAGRAM

#### Figure 1.

#### **GENERAL DESCRIPTION**

The AD7091R-2/AD7091R-4/AD7091R-8 family is a multichannel 12-bit, ultralow power, successive approximation analog-todigital converter (ADC) that is available in two, four, or eight analog input channel options. The AD7091R-2/AD7091R-4/ AD7091R-8 operate from a single 2.7 V to 5.25 V power supply and are capable of achieving a sampling rate of 1 MSPS.

The AD7091R-2/AD7091R-4/AD7091R-8 family offers up to eight single-ended analog input channels with a channel sequencer that allows a preprogrammed selection of channels to be converted sequentially. The AD7091R-2/AD7091R-4/ AD7091R-8 also feature an on-chip conversion clock, an on-chip accurate 2.5 V reference, and a high speed serial interface.

The AD7091R-2/AD7091R-4/AD7091R-8 have a serial port interface (SPI) that allows data to be read after the conversion while achieving a 1 MSPS throughput rate. The conversion process and data acquisition are controlled using the CONVST pin.

The AD7091R-2/AD7091R-4/AD7091R-8 use advanced design techniques to achieve ultralow power dissipation at high throughput rates. They also feature flexible power management options. An on-chip configuration register allows the user to set up different operating conditions. These include power management, alert functionality, busy indication, channel sequencing, and general-purpose output pins. The MUX<sub>OUT</sub> and ADC<sub>IN</sub> pins allow signal conditioning of the multiplexer output prior to acquisition by the ADC.

# TABLE OF CONTENTS

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| Functional Block Diagram1                    |

| General Description                          |

| Revision History                             |

| Specifications                               |

| Timing Specifications                        |

| Absolute Maximum Ratings7                    |

| Thermal Resistance                           |

| ESD Caution7                                 |

| Pin Configurations and Function Descriptions |

| Typical Performance Characteristics          |

| Terminology                                  |

| Theory of Operation19                        |

| Circuit Information19                        |

| Converter Operation19                        |

| ADC Transfer Function19                      |

| Reference                                    |

| Power Supply20                               |

| Device Reset                                 |

| Typical Connection Diagram20                 |

| Analog Input                                 |

| Driver Amplifier Choice21                    |

| Registers                                    |

### **REVISION HISTORY**

| 12/15—Rev. B to Rev. C          |      |

|---------------------------------|------|

| Change to the Reference Section | . 19 |

#### 11/14—Rev. A to Rev. B

| • • • • • • • • • • • • • • • • • • • •                      |

|--------------------------------------------------------------|

| Added Endnote 1 3                                            |

| Added Total Power Dissipation (Normal Mode) of 0.080 mW 4    |

| Changes to Table 25                                          |

| Added Device Reset Section and Figure 43; Renumbered         |

| Sequentially 20                                              |

| Added Power-On Device Initialization Section and Figure 5333 |

| 7/14—Rev. 0 to Rev. A                                        |

| Added 16-Lead LFCSP, 20-Lead LFCSP, and                      |

| 24-Lead LFCSPUniversal                                       |

| Changes to Features Section 1                                |

| Changes to General Description Section 1                     |

| Changes to Table 1                                           |

| Changes to Table 47                                          |

| Added Figure 6; Renumbered Sequentially8                     |

| Addressing Registers                 | 23 |

|--------------------------------------|----|

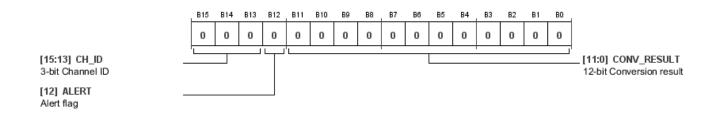

| Conversion Result Register           | 24 |

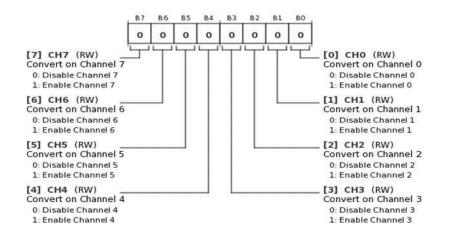

| Channel Register                     | 25 |

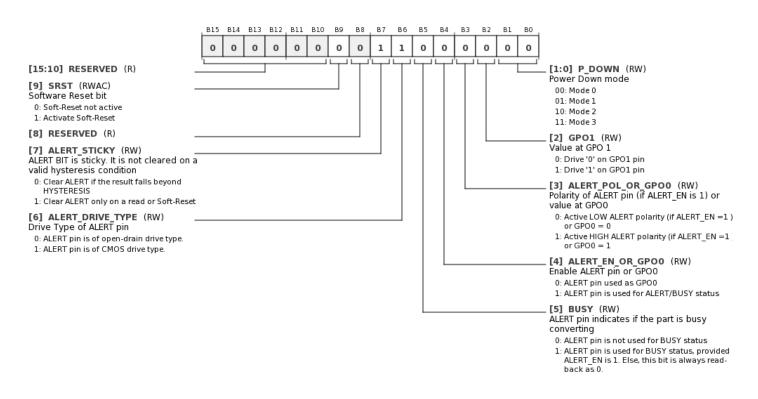

| Configuration Register               | 26 |

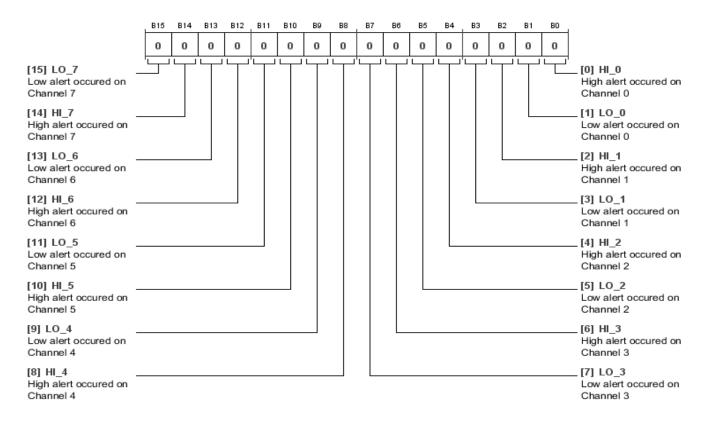

| Alert Indication Register            | 28 |

| Channel x Low Limit Register         | 30 |

| Channel x High Limit Register        | 30 |

| Channel x Hysteresis Register        | 30 |

| Serial Port Interface                | 31 |

| Reading Conversion Result            | 31 |

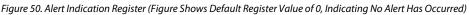

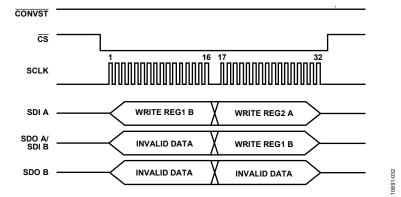

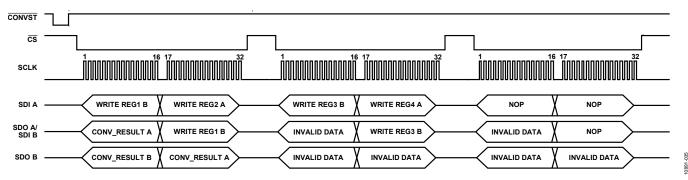

| Writing Data to the Registers        | 31 |

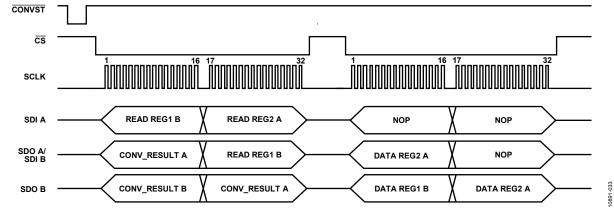

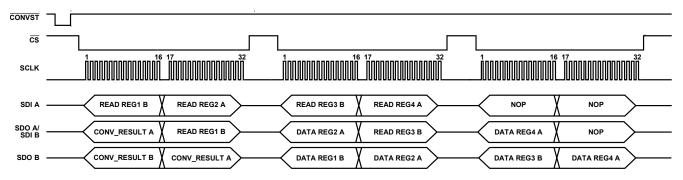

| Reading Data from the Registers      | 31 |

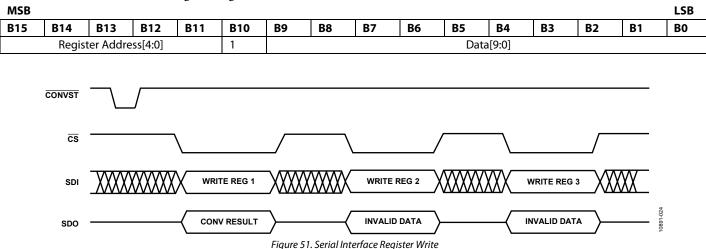

| Power-On Device Initialization       | 33 |

| Modes of Operation                   | 34 |

| Normal Mode                          | 34 |

| Power-Down Mode                      | 34 |

| ALERT (AD7091R-4 and AD7091R-8 Only) | 35 |

| BUSY (AD7091R-4 and AD7091R-8 Only)  | 35 |

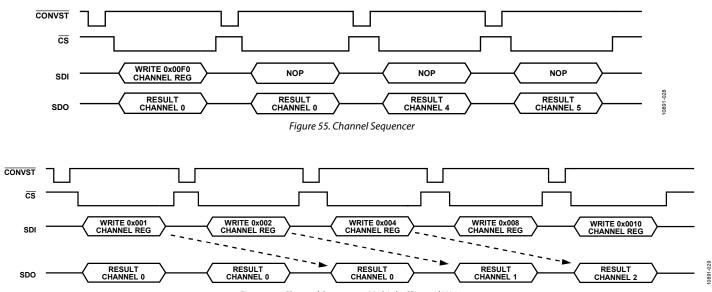

| Channel Sequencer                    | 36 |

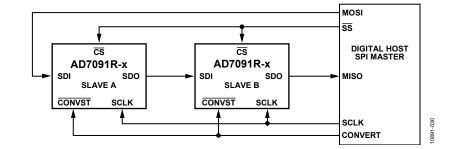

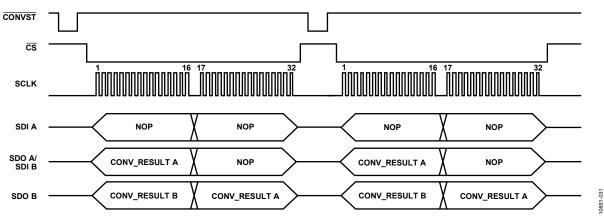

| Daisy Chain                          | 37 |

| Outline Dimensions                   | 39 |

| Ordering Guide                       | 42 |

| Changes to Table 5                                        | 8  |

|-----------------------------------------------------------|----|

| -                                                         |    |

| Added Figure 8                                            |    |

| Changes to Table 6                                        |    |

| Added Figure 10                                           | 11 |

| Changes to Table 7                                        | 11 |

| Added Power Supply Section and Table 8; Renumbered        |    |

| Sequentially                                              | 20 |

| Added Driver Amplifier Choice Section and Table 9         | 21 |

| Changes to Table 16                                       | 26 |

| Changed Serial Interface Section to Serial Port Interface |    |

| Section                                                   | 31 |

| Changes to Figure 52                                      | 33 |

| Updated Outline Dimensions                                | 38 |

| Changes to Ordering Guide                                 | 41 |

| 5 5                                                       |    |

12/13—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{DD}$  = 2.7 V to 5.25 V,  $V_{DRIVE}$  = 1.8 V to 5.25 V,  $V_{REF}$  = 2.5 V internal reference,  $f_{SAMPLE}$  = 1 MSPS,  $f_{SCLK}$  = 50 MHz,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Table 1.                                     |                                                |                               | _          |                               | 1      |

|----------------------------------------------|------------------------------------------------|-------------------------------|------------|-------------------------------|--------|

| Parameter                                    | Test Conditions/Comments                       | Min                           | Тур        | Мах                           | Unit   |

| DYNAMIC PERFORMANCE                          | $f_{IN} = 10 \text{ kHz}$ sine wave            |                               |            |                               |        |

| Signal-to-Noise Ratio (SNR)                  |                                                | 66.5                          | 70         |                               | dB     |

| Signal-to-Noise-and-Distortion (SINAD) Ratio |                                                | 65.5                          | 69         |                               | dB     |

| Total Harmonic Distortion (THD)              |                                                |                               | -80        |                               | dB     |

| Spurious-Free Dynamic Range (SFDR)           | $f_{IN} = 1 \text{ kHz}$ sine wave             |                               | -81        |                               | dB     |

| Channel-to-Channel Isolation                 |                                                |                               | -95        |                               | dB     |

| Aperture Delay                               |                                                |                               | 5          |                               | ns     |

| Aperture Jitter                              |                                                |                               | 40         |                               | ps     |

| Full Power Bandwidth                         | At –3 dB                                       |                               | 1.5        |                               | MHz    |

|                                              | At –0.1 dB                                     |                               | 1.2        |                               | MHz    |

| DC ACCURACY                                  |                                                |                               |            |                               |        |

| Resolution                                   |                                                | 12                            |            |                               | Bits   |

| Integral Nonlinearity (INL)                  | $V_{DD} \ge 3.0 \text{ V}$                     | -1                            | ±0.7       | +1                            | LSB    |

|                                              | $V_{DD} \ge 2.7 V$                             | -1.25                         | ±0.8       | +1.25                         | LSB    |

| Differential Nonlinearity (DNL)              | Guaranteed no missing codes to 12 bits         | -0.9                          | ±0.3       | +0.9                          | LSB    |

| Offset Error                                 | $T_A = 25^{\circ}C$                            | -1.5                          | 0.2        | +1.5                          | mV     |

| Offset Error Matching                        | $T_A = 25^{\circ}C$                            | -1.5                          | 0.2        | +1.5                          | mV     |

| Offset Error Drift                           |                                                |                               | 2          |                               | ppm/°C |

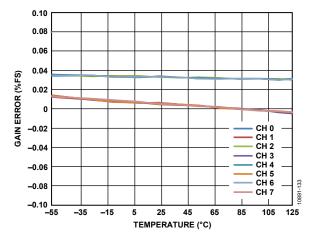

| Gain Error                                   | $T_A = 25^{\circ}C$                            | -0.1                          | 0.0        | +0.1                          | % FS   |

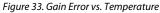

| Gain Error Matching                          | $T_A = 25^{\circ}C$                            | -0.1                          | 0.0        | +0.1                          | % FS   |

| Gain Error Drift                             |                                                |                               | 2          |                               | ppm/°C |

| ANALOG INPUT                                 |                                                |                               |            |                               |        |

| Input Voltage Range <sup>1</sup>             | At ADC <sub>IN</sub>                           | 0                             |            | VREF                          | V      |

| DC Leakage Current                           |                                                | -1                            |            | +1                            | μA     |

| Input Capacitance <sup>2</sup>               | During acquisition phase                       |                               | 10         |                               | pF     |

|                                              | Outside acquisition phase                      |                               | 1.5        |                               | pF     |

| Multiplexer On Resistance                    | $V_{DD} = 5.0 V$                               |                               | 50         |                               | Ω      |

|                                              | $V_{DD} = 2.5 V$                               |                               | 100        |                               | Ω      |

| VOLTAGE REFERENCE INPUT/OUTPUT               |                                                |                               |            |                               |        |

| REF <sub>OUT</sub> <sup>3</sup>              | Internal reference output, $T_A = 25^{\circ}C$ | 2.49                          | 2.5        | 2.51                          | V      |

| REF <sub>IN</sub> <sup>3</sup>               | External reference input                       | 1.0                           |            | V <sub>DD</sub>               | V      |

| Drift                                        |                                                |                               | 5          |                               | ppm/°C |

| Power-On Time                                | $C_{REF} = 2.2 \ \mu F$                        |                               | 50         |                               | ms     |

| LOGIC INPUTS                                 | •                                              |                               |            |                               |        |

| Input High Voltage (V <sub>H</sub> )         |                                                | $0.7 \times V_{\text{DRIVE}}$ |            |                               | v      |

| Input Low Voltage (V <sub>IL</sub> )         |                                                |                               |            | $0.3 \times V_{\text{DRIVE}}$ | v      |

| Input Current (I <sub>IN</sub> )             | Typically 10 nA, $V_{IN} = 0 V$ or $V_{DRIVE}$ | -1                            |            | +1                            | μA     |

| LOGIC OUTPUTS                                |                                                | 1                             |            |                               |        |

| Output High Voltage (Vон)                    | $I_{\text{SOURCE}} = 200  \mu \text{A}$        | V <sub>DRIVE</sub> – 0.2      |            |                               | v      |

| Output Low Voltage (Vol.)                    | $I_{\text{SINK}} = 200 \mu\text{A}$            |                               |            | 0.4                           | v      |

| Floating State Leakage Current               |                                                | -1                            |            | +1                            | μA     |

| Output Coding                                |                                                |                               | nt (natura |                               | P      |

| Parameter                             | Test Conditions/Comments                                                               | Min | Тур   | Max   | Unit |

|---------------------------------------|----------------------------------------------------------------------------------------|-----|-------|-------|------|

| CONVERSION RATE                       |                                                                                        |     |       |       |      |

| Conversion Time                       |                                                                                        |     |       | 600   | ns   |

| Transient Response                    | Full-scale step input                                                                  |     |       | 400   | ns   |

| Throughput Rate                       |                                                                                        |     |       | 1     | MSPS |

| POWER REQUIREMENTS                    |                                                                                        |     |       |       |      |

| V <sub>DD</sub>                       |                                                                                        | 2.7 |       | 5.25  | V    |

| V <sub>DRIVE</sub>                    | Specified performance                                                                  | 2.7 |       | 5.25  | V    |

| V <sub>DRIVE</sub> Range <sup>4</sup> | Functional                                                                             | 1.8 |       | 5.25  | V    |

| IDD                                   | $V_{IN} = 0 V$                                                                         |     |       |       |      |

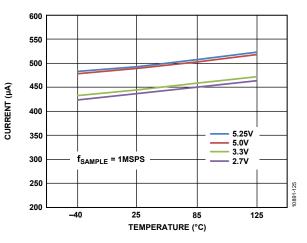

| Normal Mode—Static⁵                   | $V_{DD} = 5.25 V$                                                                      |     | 22    | 50    | μΑ   |

|                                       | $V_{DD} = 3 V$                                                                         |     | 21.6  | 46    | μΑ   |

| Normal Mode—Operational               | $V_{DD} = 5.25 \text{ V},  \text{f}_{\text{SAMPLE}} = 1  \text{MSPS}$                  |     | 500   | 570   | μΑ   |

|                                       | $V_{DD} = 3 V$ , $f_{SAMPLE} = 1 MSPS$                                                 |     | 450   | 530   | μΑ   |

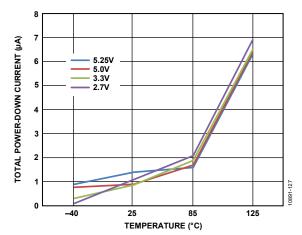

| Power-Down Mode                       | $V_{DD} = 5.25 V$                                                                      |     | 0.550 | 17    | μΑ   |

|                                       | $V_{DD} = 5.25 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$   |     | 0.550 | 6     | μΑ   |

|                                       | $V_{DD} = 3 V$                                                                         |     | 0.435 | 15    | μΑ   |

| I <sub>DRIVE</sub>                    | $V_{IN} = 0 V$                                                                         |     |       |       |      |

| Normal Mode—Static <sup>6</sup>       | $V_{DRIVE} = 5.25 V$                                                                   |     | 2     | 4     | μΑ   |

|                                       | $V_{DRIVE} = 3 V$                                                                      |     | 1     | 3.5   | μΑ   |

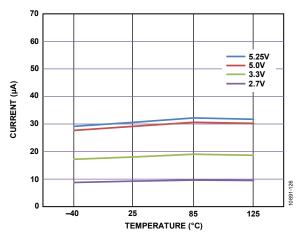

| Normal Mode—Operational               | $V_{DRIVE} = 5.25 V$ , $f_{SAMPLE} = 1 MSPS$                                           |     | 30    | 70    | μΑ   |

|                                       | $V_{DRIVE} = 3 V, f_{SAMPLE} = 1 MSPS$                                                 |     | 10    | 15    | μΑ   |

| Power-Down Mode                       | $V_{DRIVE} = 5.25 V$                                                                   |     |       | 1     | μΑ   |

|                                       | $V_{DRIVE} = 3 V$                                                                      |     |       | 1     | μΑ   |

| Total Power Dissipation <sup>7</sup>  | $V_{IN} = 0 V$                                                                         |     |       |       |      |

| Normal Mode—Static                    | $V_{DD} = V_{DRIVE} = 5.25 V$                                                          |     | 0.130 | 0.290 | mW   |

|                                       | $V_{DD} = V_{DRIVE} = 3 V$                                                             |     | 0.070 | 0.149 | mW   |

| Normal Mode—Operational               | $V_{DD} = V_{DRIVE} = 5.25 V$ , $f_{SAMPLE} = 1 MSPS$                                  |     | 2.8   | 3.4   | mW   |

|                                       | $V_{DD} = V_{DRIVE} = 3 V$ , $f_{SAMPLE} = 1 MSPS$                                     |     | 1.4   | 1.7   | mW   |

|                                       | $V_{\text{DD}} = V_{\text{DRIVE}} = 3 \text{ V},  f_{\text{SAMPLE}} = 100 \text{ SPS}$ |     | 0.080 |       | mW   |

| Power-Down Mode                       | $V_{DD} = 5.25 V$                                                                      |     | 3     | 95    | μW   |

|                                       | $V_{DD} = 5.25 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$   |     | 3     | 33    | μW   |

|                                       | $V_{DD} = V_{DRIVE} = 3 V$                                                             |     | 1.4   | 50    | μW   |

$^{\rm 1}$  Multiplexer input voltage should not exceed V\_{DD}.

<sup>2</sup> Sample tested during initial release to ensure compliance.

<sup>3</sup> When referring to a single function of a multifunction pin in the parameters, only the portion of the pin name that is relevant to the specification is listed. For full pin

names of multifunction pins, refer to the Pin Configurations and Function Descriptions section. <sup>4</sup> Device is functional and meets dynamic performance/dc accuracy specifications with  $V_{DRIVE}$  down to 1.8 V, but the device is not capable of achieving a throughput of 1 MSPS.

<sup>5</sup> SCLK operates in burst mode, and  $\overline{CS}$  idles high. With a free running SCLK and  $\overline{CS}$  pulled low, the I<sub>DD</sub> static current is increased by 30 µA typical at V<sub>DD</sub> = 5.25 V. <sup>6</sup> SCLK operates in burst mode, and  $\overline{CS}$  idles high. With a free running SCLK and  $\overline{CS}$  pulled low, the I<sub>DRIVE</sub> static current is increased by 32 µA typical at V<sub>DRIVE</sub> = 5.25 V. <sup>7</sup> Total power dissipation includes contributions from V<sub>DD</sub>, V<sub>DRIVE</sub>, and REF<sub>IN</sub> (see Note 2).

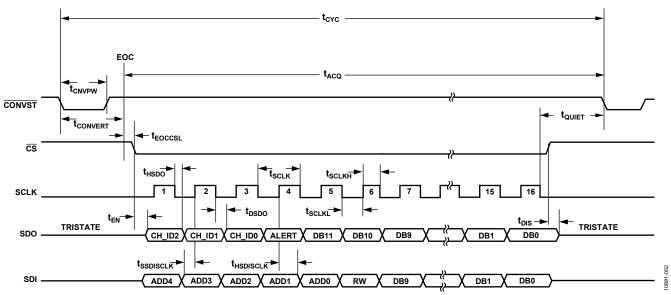

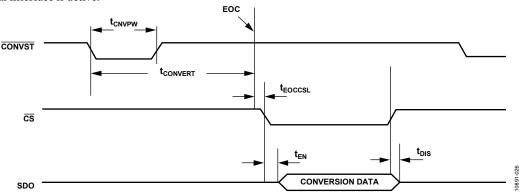

### TIMING SPECIFICATIONS

$V_{\text{DD}}$  = 2.7 V to 5.25 V,  $V_{\text{DRIVE}}$  = 1.8 V to 5.25 V,  $T_{\text{A}}$  =  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$  , unless otherwise noted.

#### Table 2.

| Parameter                                               | Symbol                      | Min  | Тур | Max | Unit |

|---------------------------------------------------------|-----------------------------|------|-----|-----|------|

| Conversion Time: CONVST Falling Edge to Data Available  | <b>t</b> <sub>CONVERT</sub> |      |     | 600 | ns   |

| Acquisition Time                                        | t <sub>ACQ</sub>            | 400  |     |     | ns   |

| Time Between Conversions (Normal Mode)                  | t <sub>cyc</sub>            | 1000 |     |     | ns   |

| CONVST Pulse Width                                      | <b>t</b> <sub>CNVPW</sub>   | 10   |     | 500 | ns   |

| SCLK Period (Normal Mode)                               | <b>t</b> sclk               |      |     |     |      |

| V <sub>DRIVE</sub> Above 2.7 V                          |                             | 16   |     |     | ns   |

| V <sub>DRIVE</sub> Above 1.8 V                          |                             | 22   |     |     | ns   |

| SCLK Period (Chain Mode)                                | <b>t</b> sclk               |      |     |     |      |

| V <sub>DRIVE</sub> Above 2.7 V                          |                             | 20   |     |     | ns   |

| V <sub>DRIVE</sub> Above 1.8 V                          |                             | 25   |     |     | ns   |

| SCLK Low Time                                           | tsclkl                      | 6    |     |     | ns   |

| SCLK High Time                                          | <b>t</b> sclkh              | 6    |     |     | ns   |

| SCLK Falling Edge to Data Remains Valid                 | t <sub>HSDO</sub>           | 5    |     |     | ns   |

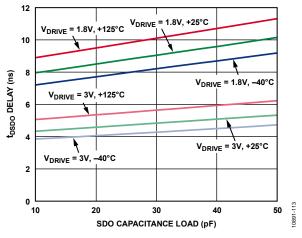

| SCLK Falling Edge to Data Valid Delay                   | t <sub>DSDO</sub>           |      |     |     |      |

| VDRIVE Above 4.5 V                                      |                             |      |     | 12  | ns   |

| V <sub>DRIVE</sub> Above 3.3 V                          |                             |      |     | 13  | ns   |

| VDRIVE Above 2.7 V                                      |                             |      |     | 14  | ns   |

| V <sub>DRIVE</sub> Above 1.8 V                          |                             |      |     | 20  | ns   |

| End of Conversion to CS Falling Edge                    | <b>t</b> eoccsl             | 5    |     |     | ns   |

| CS Low to SDO Enabled                                   | t <sub>EN</sub>             |      |     | 5   | ns   |

| CS High or Last SCLK Falling Edge to SDO High Impedance | t <sub>DIS</sub>            |      |     | 5   | ns   |

| SDI Data Setup Time Prior to SCLK Rising Edge           | <b>t</b> ssdisclk           | 5    |     |     | ns   |

| SDI Data Hold Time After SCLK Rising Edge               | <b>t</b> hsdisclk           | 2    |     |     | ns   |

| Last SCLK Falling Edge to Next CONVST Falling Edge      | <b>t</b> quiet              | 50   |     |     | ns   |

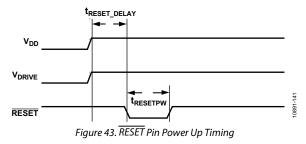

| RESET Pulse Width                                       | t <sub>resetpw</sub>        | 10   |     |     | ns   |

| RESET Pulse Delay Upon Power Up                         | treset_delay                | 50   |     |     | ns   |

| Time Between Conversions (Power On Software Reset)      | t <sub>cyc_reset</sub>      | 2    |     |     | μs   |

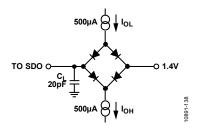

Figure 2. Load Circuit for Digital Interface Timing

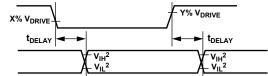

NOTES

<sup>1</sup>FOR V<sub>DRIVE</sub> ≤ 3.0V, X = 90 AND Y = 10; FOR V<sub>DRIVE</sub> > 3.0V, X = 70 AND Y = 30. <sup>2</sup>MINIMUM V<sub>IH</sub> AND MAXIMUM V<sub>IL</sub> USED. SEE SPECIFICATIONS FOR DIGITAL INPUTS PARAMETER IN TABLE 2.

Figure 3. Voltage Levels for Timing

### Timing Diagram

Figure 4. Serial Port Timing

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Parameter                                             | Rating                               |

|-------------------------------------------------------|--------------------------------------|

| V <sub>DD</sub> to GND                                | –0.3 V to +7 V                       |

| V <sub>DRIVE</sub> to GND                             | –0.3 V to +7 V                       |

| Analog Input Voltage to GND                           | $-0.3V$ to $V_{\text{REF}}+0.3V$     |

| Digital Input <sup>1</sup> Voltage to GND             | -0.3 V to V <sub>DRIVE</sub> + 0.3 V |

| Digital Output <sup>2</sup> Voltage to GND            | -0.3 V to V <sub>DRIVE</sub> + 0.3 V |

| Input Current to Any Pin Except Supplies <sup>3</sup> | ±10 mA                               |

| Operating Temperature Range                           | -40°C to +125°C                      |

| Storage Temperature Range                             | -65°C to +150°C                      |

| Junction Temperature                                  | 150°C                                |

| ESD                                                   |                                      |

| Human Body Model (HBM)                                | 1.5 kV                               |

| Field Induced Charged Device Model<br>(FICDM)         | 500 V                                |

<sup>1</sup> The digital input pins include the following:  $\overline{\text{RESET}}$ ,  $\overline{\text{CONVST}}$ , SDI, SCLK, and  $\overline{\text{CS}}$ .

$^{\rm 2}$  The digital output pins include the following: SDO, GPO1, and ALERT/BUSY/GPO0.

<sup>3</sup> Transient currents of up to 100 mA do not cause SCR latch-up.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 4. Thermal Resistance

| Package Type  | θ」Α    | θις   | Unit |

|---------------|--------|-------|------|

| 24-Lead LFCSP | 47.3   | 27.78 | °C/W |

| 24-Lead TSSOP | 73.54  | 14.94 | °C/W |

| 20-Lead LFCSP | 49.05  | 29.18 | °C/W |

| 20-Lead TSSOP | 84.29  | 18.43 | °C/W |

| 16-Lead LFCSP | 50.58  | 29.64 | °C/W |

| 16-Lead TSSOP | 106.03 | 28.31 | °C/W |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality. .....

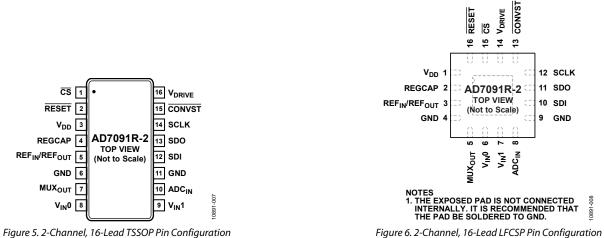

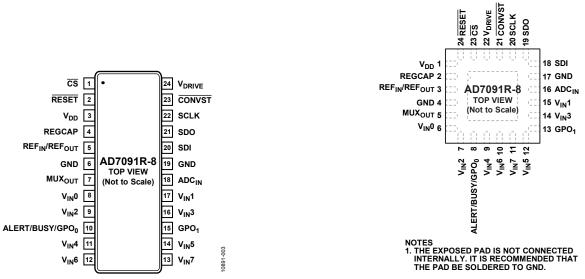

## **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

| tion | Figure 6. 2-Channel, 16 |

|------|-------------------------|

|      |                         |

| Pin No.           |       |                    |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-------------------|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TSSOP             | LFCSP | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 1                 | 15    | CS                 | Chip Select Input. When $\overline{CS}$ is held low, the serial bus enables, and $\overline{CS}$ frames the output data on the SPI.                                                                                                                                                                                                                       |  |  |  |  |

| 2                 | 16    | RESET              | Reset. Logic input.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 3                 | 1     | V <sub>DD</sub>    | wer Supply Input. The V_DD range is from 2.7 V to 5.25 V. Decouple this supply pin to GND.                                                                                                                                                                                                                                                                |  |  |  |  |

| 4                 | 2     | REGCAP             | Decoupling Capacitor Pin for Voltage Output from Internal Regulator. Decouple this output pin separately to GND using a 1.0 $\mu\text{F}$ capacitor.                                                                                                                                                                                                      |  |  |  |  |

| 5                 | 3     | REFIN/REFOUT       | Voltage Reference Output, 2.5 V. Decouple this pin to GND. Typical recommended decoupling capacitor value is 2.2 $\mu$ F. The user can either access the internal 2.5 V reference or overdrive the internal reference with the voltage applied to this pin. The reference voltage range for an externally applied reference is 1.0 V to V <sub>DD</sub> . |  |  |  |  |

| 6, 11             | 4, 9  | GND                | Chip Ground Pins. These pins are the ground reference point for all circuitry on the AD7091R-2.                                                                                                                                                                                                                                                           |  |  |  |  |

| 7                 | 5     | MUX <sub>OUT</sub> | Multiplexer Output. The output of the multiplexer appears at this pin. If no external filtering or buffering is required, tie this pin directly to the ADC <sub>IN</sub> pin; otherwise, tie the output of the conditioning network to the ADC <sub>IN</sub> pin.                                                                                         |  |  |  |  |

| 8                 | 6     | V <sub>IN</sub> 0  | Analog Input 0. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |

| 9                 | 7     | V <sub>IN</sub> 1  | Analog Input 1. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |

| 10                | 8     | ADC <sub>IN</sub>  | ADC Input. This pin allows access to the on-chip track-and-hold. If no external filtering or buffering is required, tie this pin directly to the $MUX_{OUT}$ pin; otherwise tie the input of the conditioning network to the $MUX_{OUT}$ pin.                                                                                                             |  |  |  |  |

| 12                | 10    | SDI                | Serial Data Input Bus. This input provides the data written to the on-chip control registers. Data clocks into the registers on the falling edge of the SCLK input. Provide data MSBs first.                                                                                                                                                              |  |  |  |  |

| 13                | 11    | SDO                | Serial Data Output Bus. The conversion output data is supplied to this pin as a serial data stream. The bits are clocked out on the falling edge of the SCLK input, and 13 SCLKs are required to access the data. The data is provided MSB first.                                                                                                         |  |  |  |  |

| 14                | 12    | SCLK               | Serial Clock. This pin acts as the serial clock input.                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 15                | 13    | CONVST             | Convert Start Input Signal. Edge triggered logic input. The falling edge of CONVST places the track-<br>and-hold mode into hold mode and initiates a conversion.                                                                                                                                                                                          |  |  |  |  |

| 16                | 14    | Vdrive             | Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates. Connect decoupling capacitors between V_DRIVE and GND. Typical recommended values are 10 $\mu$ F and 0.1 $\mu$ F. The voltage range on this pin is 1.8 V to 5.25 V and may be different to the voltage range at V_DD.                       |  |  |  |  |

| Not<br>applicable | 17    | EPAD               | Exposed Pad. The exposed pad is not connected internally. It is recommended that the pad be soldered to GND.                                                                                                                                                                                                                                              |  |  |  |  |

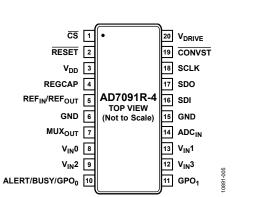

#### Table 6. 4-Channel, 20-Lead LFCSP and 20-Lead TSSOP Pin Function Descriptions

| Pin N | lo.   |                                       |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|-------|-------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TSSOP | LFCSP | Mnemonic                              | Description                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 1     | 19    | <u>CS</u>                             | Chip Select Input. When $\overline{CS}$ is held low, the serial bus enables, and $\overline{CS}$ frames the output data on the SPI.                                                                                                                                                                                                                       |  |  |  |  |  |

| 2     | 20    | RESET                                 | Reset. Logic input.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 3     | 1     | V <sub>DD</sub>                       | Power Supply Input. The $V_{DD}$ range is from 2.7 V to 5.25 V. Decouple this supply pin to GND.                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 4     | 2     | REGCAP                                | Decoupling Capacitor Pin for Voltage Output from Internal Regulator. Decouple this output pin separately to GND using a 1.0 $\mu F$ capacitor.                                                                                                                                                                                                            |  |  |  |  |  |

| 5     | 3     | REF <sub>IN</sub> /REF <sub>OUT</sub> | Voltage Reference Output, 2.5 V. Decouple this pin to GND. Typical recommended decoupling capacitor value is 2.2 $\mu$ F. The user can either access the internal 2.5 V reference or overdrive the internal reference with the voltage applied to this pin. The reference voltage range for an externally applied reference is 1.0 V to V <sub>DD</sub> . |  |  |  |  |  |

| 6, 15 | 4, 13 | GND                                   | Chip Ground Pins. These pins are the ground reference point for all circuitry on the AD7091R-4.                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 7     | 5     | MUX <sub>OUT</sub>                    | Multiplexer Output. The output of the multiplexer appears at this pin. If no external filtering or buffering is required, tie this pin directly to the ADC $_{\mathbb{N}}$ pin; otherwise, tie the output of the conditioning network to the ADC $_{\mathbb{N}}$ pin.                                                                                     |  |  |  |  |  |

| 8     | 6     | V <sub>IN</sub> 0                     | Analog Input 0. Single-ended analog input. The analog input range is 0 V to $V_{\text{REF}}$ .                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 9     | 7     | V <sub>IN</sub> 2                     | Analog Input 2. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 10    | 8     | ALERT/BUSY/GPO <sub>0</sub>           | Alert Output Pin (ALERT). This is a multifunction pin determined by the configuration register.<br>When functioning as ALERT, this pin is a logic output indicating that a conversion result has<br>fallen outside the limit of the register settings.                                                                                                    |  |  |  |  |  |

|       |       |                                       | When the ALERT/BUSY/GPO $_0$ pin is configured as a BUSY output, use this pin to indicate when a conversion is taking place.                                                                                                                                                                                                                              |  |  |  |  |  |

|       |       |                                       | The pin can also function as a general-purpose digital output.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 11    | 9     | GPO <sub>1</sub>                      | General-Purpose Digital Output.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 12    | 10    | V <sub>IN</sub> 3                     | Analog Input 3. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 13    | 11    | V <sub>IN</sub> 1                     | Analog Input 1. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 14    | 12    | ADC <sub>IN</sub>                     | ADC Input. This pin allows access to the on-chip track-and-hold. If no external filtering or buffering is required, tie this pin directly to the $MUX_{OUT}$ pin; otherwise, tie the input of the conditioning network to the $MUX_{OUT}$ pin.                                                                                                            |  |  |  |  |  |

| 16    | 14    | SDI                                   | Serial Data Input Bus. This input provides data written to the on-chip control registers. Data clocks into the registers on the falling edge of the SCLK input. Provide data MSB first.                                                                                                                                                                   |  |  |  |  |  |

| 17    | 15    | SDO                                   | Serial Data Output Bus. The conversion output data is supplied to this pin as a serial data stream. The bits are clocked out on the falling edge of the SCLK input, and 13 SCLKs are required to access the data. The data is provided MSB first.                                                                                                         |  |  |  |  |  |

| Pin N             | 0.    |          |                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP             | LFCSP | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                               |

| 18                | 16    | SCLK     | Serial Clock. This pin acts as the serial clock input.                                                                                                                                                                                                                                                                                                    |

| 19                | 17    | CONVST   | Convert Start Input Signal. Edge triggered logic input. The falling edge of CONVST places the track-and-hold mode into hold mode and initiates a conversion.                                                                                                                                                                                              |

| 20                | 18    | Vdrive   | Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates. Connect decoupling capacitors between V <sub>DRVE</sub> and GND. Typical recommended values are 10 $\mu$ F and 0.1 $\mu$ F. The voltage range on this pin is 1.8 V to 5.25 V and may be different to the voltage range at V <sub>DD</sub> . |

| Not<br>applicable | 21    | EPAD     | Exposed Pad. The exposed pad is not connected internally. It is recommended that the pad be soldered to GND.                                                                                                                                                                                                                                              |

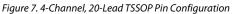

#### Figure 9. 8-Channel, 24-Lead TSSOP Pin Configuration

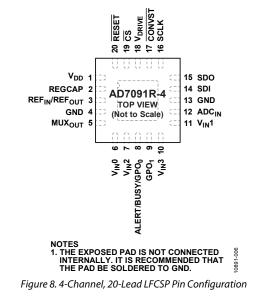

#### Figure 10. 8-Channel, 24-Lead LFCSP Pin Configuration

10891-004

#### Table 7. 8-Channel, 24-Lead LFCSP and 24-Lead TSSOP Pin Function Descriptions

| Pin N | lo.   |                                       |                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|-------|-------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TSSOP | LFCSP | Mnemonic                              | Description                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 1     | 23    | <u>CS</u>                             | Chip Select Input. When CS is held low, the serial bus enables, and CS frames the output data on the SPI.                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 2     | 24    | RESET                                 | Reset. Logic input.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 3     | 1     | V <sub>DD</sub>                       | Power Supply Input. The $V_{DD}$ range is from 2.7 V to 5.25 V. Decouple this supply pin to GND.                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 4     | 2     | REGCAP                                | Decoupling Capacitor Pin for Voltage Output from Internal Regulator. Decouple this output pin separately to GND using a 1.0 $\mu F$ capacitor.                                                                                                                                                                                                            |  |  |  |  |  |  |

| 5     | 3     | REF <sub>IN</sub> /REF <sub>OUT</sub> | Voltage Reference Output, 2.5 V. Decouple this pin to GND. Typical recommended decoupling capacitor value is 2.2 $\mu$ F. The user can either access the internal 2.5 V reference or overdrive the internal reference with the voltage applied to this pin. The reference voltage range for an externally applied reference is 1.0 V to V <sub>DD</sub> . |  |  |  |  |  |  |

| 6, 19 | 4, 17 | GND                                   | Chip Ground Pins. These pins are the ground reference point for all circuitry on the AD7091R-8.                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 7     | 5     | MUX <sub>OUT</sub>                    | Multiplexer Output. The output of the multiplexer appears at this pin. If no external filtering or buffering is required, tie this pin directly to the ADC $_{\mathbb{N}}$ pin; otherwise, tie the output of the conditioning network to the ADC $_{\mathbb{N}}$ pin.                                                                                     |  |  |  |  |  |  |

| 8     | 6     | V <sub>IN</sub> 0                     | Analog Input 0. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 9     | 7     | V <sub>IN</sub> 2                     | Analog Input 2. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 10    | 8     | ALERT/BUSY/GPO <sub>0</sub>           | Alert Output Pin (ALERT). This is a multifunction pin determined by the configuration register.<br>When functioning as ALERT, this pin is a logic output indicating that a conversion result has<br>fallen outside the limit of the register settings.                                                                                                    |  |  |  |  |  |  |

|       |       |                                       | When the ALERT/BUSY/GPO $_0$ pin is configured as a BUSY output, use this pin to indicate when a conversion is taking place.                                                                                                                                                                                                                              |  |  |  |  |  |  |

|       |       |                                       | The pin can also function as a general-purpose digital output.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 11    | 9     | V <sub>IN</sub> 4                     | Analog Input 4. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 12    | 10    | V <sub>IN</sub> 6                     | Analog Input 6. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 13    | 11    | V <sub>IN</sub> 7                     | Analog Input 7. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 14    | 12    | V <sub>IN</sub> 5                     | Analog Input 5. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 15    | 13    | GPO <sub>1</sub>                      | General-Purpose Digital Output.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 16    | 14    | V <sub>IN</sub> 3                     | Analog Input 3. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 17    | 15    | V <sub>IN</sub> 1                     | Analog Input 1. Single-ended analog input. The analog input range is 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 18    | 16    | ADC <sub>IN</sub>                     | ADC Input. This pin allows access to the on-chip track-and-hold. If no external filtering or buffering is required, tie this pin directly to the $MUX_{OUT}$ pin; otherwise, tie the input of the conditioning network to the $MUX_{OUT}$ pin.                                                                                                            |  |  |  |  |  |  |

| Pin N             | о.    |                    |                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP             | LFCSP | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                  |

| 20                | 18    | SDI                | Serial Data Input Bus. Data to be written to the on-chip control registers is provided on this input.<br>Data is clocked into the registers on the falling edge of the SCLK input. Provide data MSB first.                                                                                                                                   |

| 21                | 19    | SDO                | Serial Data Output Bus. The conversion output data is supplied to this pin as a serial data stream. The bits are clocked out on the falling edge of the SCLK input, and 13 SCLKs are required to access the data. The data is provided MSB first.                                                                                            |

| 22                | 20    | SCLK               | Serial Clock. This pin acts as the serial clock input.                                                                                                                                                                                                                                                                                       |

| 23                | 21    | CONVST             | Convert Start Input Signal. Edge triggered logic input. The falling edge of CONVST places the track-and-hold mode into hold mode and initiates a conversion.                                                                                                                                                                                 |

| 24                | 22    | V <sub>DRIVE</sub> | Logic Power Supply Input. The voltage supplied at this pin determines at what voltage the interface operates. Connect decoupling capacitors between $V_{DRIVE}$ and GND. Typical recommended values are 10 $\mu$ F and 0.1 $\mu$ F. The voltage range on this pin is 1.8 V to 5.25 V and may be different to the voltage range at $V_{DD}$ . |

| Not<br>applicable | 25    | EPAD               | Exposed Pad. The exposed pad is not connected internally. It is recommended that the pad be soldered to GND.                                                                                                                                                                                                                                 |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

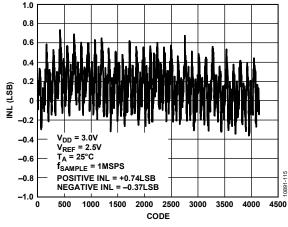

Figure 11. Integral Nonlinearity vs. Code

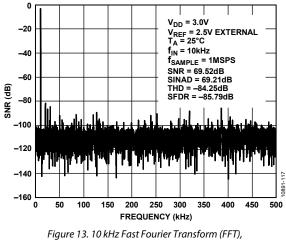

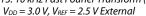

Figure 14. Differential Nonlinearity vs. Code

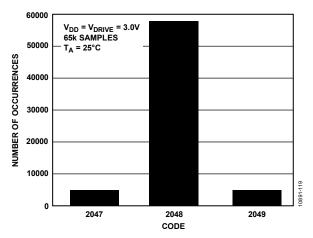

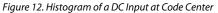

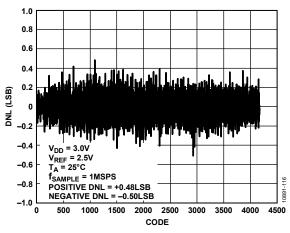

Figure 15. Histogram of a DC Input at Code Transition

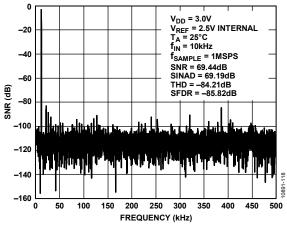

Figure 16. 10 kHz FFT,  $V_{DD} = 3.0 V$ ,  $V_{REF} = 2.5 V$  Internal

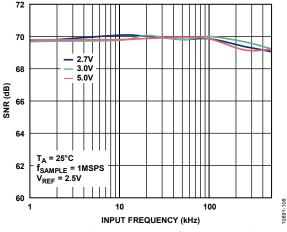

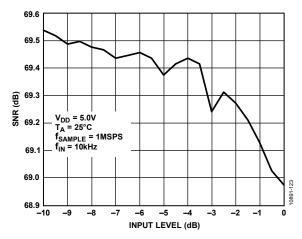

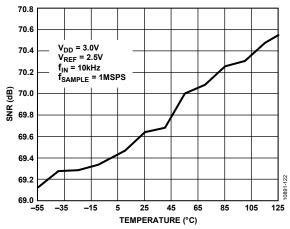

Figure 17. SNR vs. Analog Input Frequency for Various Supply Voltages

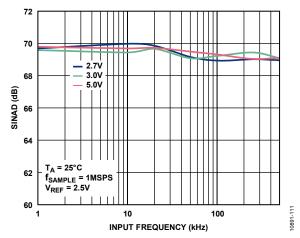

Figure 18. SINAD vs. Analog Input Frequency for Various Supply Voltages

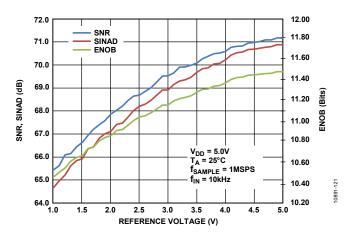

Figure 19. SNR, SINAD, and ENOB vs. Reference Voltage

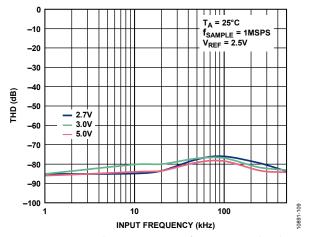

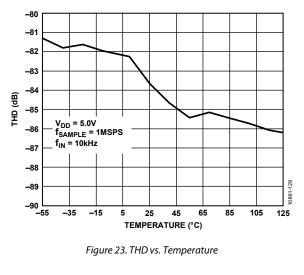

Figure 20. THD vs. Analog Input Frequency for Various Supply Voltages

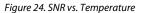

Figure 25. Operating Current vs. Throughput

Figure 26. Operational  $I_{DD}$  Supply Current vs. Temperature for Various  $V_{DD}$  Supply Voltages

Figure 27. Operational I<sub>DRIVE</sub> Supply Current vs. Temperature for Various V<sub>DRIVE</sub> Supply Voltages

Figure 28. Total Power-Down Current vs. Temperature for Various Supplies

Figure 29. t<sub>DSDO</sub> Delay vs. SDO Capacitance Load and Supply

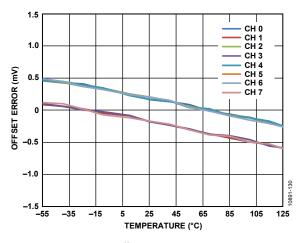

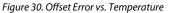

Figure 31. Offset Error Match vs. Temperature

Figure 34. Gain Error Match vs. Temperature

## **Data Sheet**

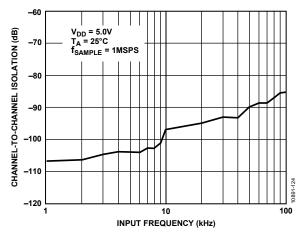

Figure 35. Channel-to-Channel Isolation vs. Input Frequency

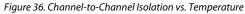

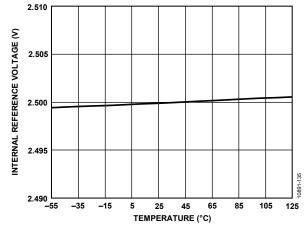

Figure 39. Internal Reference Voltage vs. Temperature

## **TERMINOLOGY**

#### Integral Nonlinearity (INL)

INL is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function. For the AD7091R-2/AD7091R-4/AD7091R-8, the endpoints of the transfer function are zero scale, a point ½ LSB below the first code transition, and full scale, a point ½ LSB above the last code transition.

#### Differential Nonlinearity (DNL)

DNL is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### **Offset Error**

The offset error is the deviation of the first code transition  $(00 \dots 000 \text{ to } 00 \dots 001)$  from the ideal (such as GND + 0.5 LSB).

#### **Offset Error Match**

Offset error match is the difference in offset error between any two input channels.

#### **Gain Error**

For the AD7091R-2/AD7091R-4/AD7091R-8, the gain error is the deviation of the last code transition (111 ... 110 to 111 ... 111) from the ideal (such as  $V_{REF} - 1.5$  LSB) after the offset error has been adjusted out.

#### **Gain Error Match**

Gain error match is the difference in gain error between any two input channels.

### **Transient Response Time**

The track-and-hold amplifier returns to track mode after the end of conversion. The track-and-hold acquisition time is the time required for the output of the track-and-hold amplifier to reach its final value, within  $\pm 0.5$  LSB, after the end of conversion. See the Serial Port Interface section for more details.

#### Signal-to-Noise-and-Distortion (SINAD) Ratio

SINAD is the measured ratio of signal-to-noise-and-distortion at the output of the ADC. The signal is the rms amplitude of the fundamental. Noise is the sum of all nonfundamental signals up to half the sampling frequency ( $f_s/2$ ), excluding dc.

The ratio is dependent on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical SINAD ratio for an ideal N-bit converter with a sine wave input is given by

SINAD = (6.02N + 1.76) dB

Thus, for a 12-bit converter, the SINAD ratio is 74 dB.

#### **Channel-to-Channel Isolation**

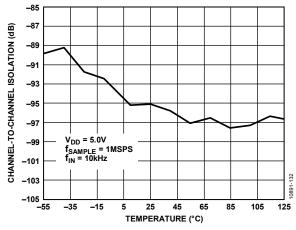

Channel-to-channel isolation is a measure of the level of crosstalk between the selected channel and all of the other channels. It is measured by applying a full-scale, 10 kHz sine wave signal to all unselected input channels and determining the degree to which the signal attenuates in the selected channel that has a dc signal applied to it. Figure 35 shows the worst case across all channels for the AD7091R-2/AD7091R-4/AD7091R-8.

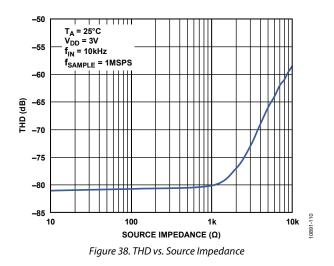

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of harmonics to the fundamental. For the AD7091R-2/AD7091R-4/AD7091R-8, it is defined as

$$THD(dB) = 20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

where:

$V_1$  is the rms amplitude of the fundamental.  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$ , and  $V_6$  are the rms amplitudes of the second through the sixth harmonic.

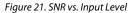

#### Spurious-Free Dynamic Range (SFDR)

SFDR is the difference, in decibels, between the rms amplitude of the input signal and the peak spurious signal.

### THEORY OF OPERATION CIRCUIT INFORMATION

The AD7091R-2/AD7091R-4/AD7091R-8 are 12-bit, fast (1 MSPS), ultralow power, single-supply ADCs. The devices operate from a 2.7 V to 5.25 V supply. The AD7091R-2/AD7091R-4/AD7091R-8 are capable of throughput rates of 1 MSPS.

The AD7091R-2/AD7091R-4/AD7091R-8 provide an on-chip, track-and-hold ADC and a serial interface housed in a 16-lead, 20-lead, or 24-lead TSSOP or LFCSP package, which offers considerable space-saving advantages over alternative solutions. The serial clock input accesses data from the device. The clock for the successive approximation ADC is generated internally. The reference voltage for the AD7091R-2/AD7091R-4/AD7091R-8 is provided externally, or it is generated internally by an accurate on-chip reference source. The analog input range for the AD7091R-2/AD7091R-4/AD7091R-8 is 0 V to V<sub>REF</sub>.

The AD7091R-2/AD7091R-4/AD7091R-8 also feature a powerdown option to save power between conversions. The power-down feature is implemented across the standard serial interface as described in the Modes of Operation section.

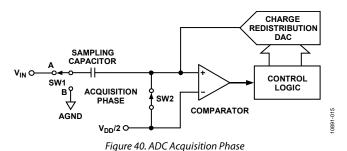

#### **CONVERTER OPERATION**

The AD7091R-2/AD7091R-4/AD7091R-8 are successive approximation ADCs based on a charge redistribution digitalto-analog converter (DAC). Figure 40 and Figure 41 show simplified schematics of the ADC. Figure 40 shows the ADC during its acquisition phase. When SW2 is closed and SW1 is in Position A, the comparator is held in a balanced condition, and the sampling capacitor acquires the signal on  $V_{\rm IN}$ .

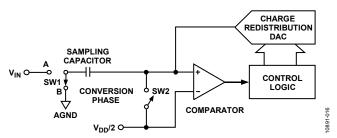

Figure 41. ADC Conversion Phase

When the ADC starts a conversion, SW2 opens and SW1 moves to Position B, causing the comparator to become unbalanced (see Figure 41). Using the control logic, the charge redistribution DAC adds and subtracts fixed amounts of charge from the sampling capacitor to bring the comparator back into a balanced condition. When the SAR decisions are made, the comparator inputs are rebalanced. From these SAR decisions, the control logic generates the ADC output code.

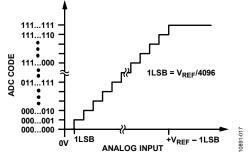

#### **ADC TRANSFER FUNCTION**

The output coding of the AD7091R-2/AD7091R-4/AD7091R-8 is straight binary. The designed code transitions occur midway between successive integer LSB values, such as  $\frac{1}{2}$  LSB,  $\frac{1}{2}$  LSB, and so on. The LSB size for the AD7091R-2/AD7091R-4/AD7091R-8 is V<sub>REF</sub>/4096. The ideal transfer characteristic for the AD7091R-2/AD7091R-4/AD7091R-8 is shown in Figure 42.

*Figure 42. AD7091R-2/AD7091R-4/AD7091R-8 Transfer Characteristic*

### REFERENCE

The AD7091R-2/AD7091R-4/AD7091R-8 can operate with either the internal 2.5 V on-chip reference or an externally applied reference. The logic state of the P\_DOWN LSB bit in the configuration register determines whether the internal reference is used. The internal reference is selected for the ADCs when the P\_DOWN LSB bit is set to 1.

When the P\_DOWN LSB bit is set to 0, supply an external reference in the range of 1.0 V to  $V_{DD}$  through the REF<sub>IN</sub>/REF<sub>OUT</sub> pin. At power-up, the internal reference disables by default.

The internal reference circuitry consists of a 2.5 V band gap reference and a reference buffer. When operating the AD7091R-2/AD7091R-4/AD7091R-8 in internal reference mode, the 2.5 V internal reference is available at the REF<sub>IN</sub>/REF<sub>OUT</sub> pin, which is typically decoupled to GND using a 2.2  $\mu$ F capacitor. It is recommended to buffer the internal reference before applying it elsewhere in the system.

The reference buffer requires 50 ms to power up and charge the 2.2  $\mu$ F decoupling capacitor during the power-up time.

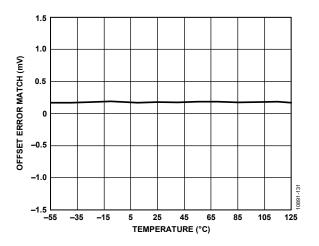

### **POWER SUPPLY**

The AD7091R-2/AD7091R-4/AD7091R-8 use two power supply pins: a core supply ( $V_{DD}$ ) and a digital input/output interface supply ( $V_{DRIVE}$ ).  $V_{DRIVE}$  allows direct interface with any logic between 1.8 V and 5.25 V. To reduce the number of supplies needed,  $V_{DRIVE}$  and  $V_{DD}$  can be tied together depending upon the logic levels of the system. Additionally, the AD7091R-2/ AD7091R-4/AD7091R-8 are insensitive to power supply variation over a wide frequency range, as shown in Figure 32. AD7091R-2/ AD7091R-4/AD7091R-8 operation is independent of power supply sequencing between  $V_{DRIVE}$  and  $V_{DD}$ .

The AD7091R-2/AD7091R-4/AD7091R-8 power down automatically at the end of each conversion phase; therefore, the power scales linearly with the sampling rate. The automatic power-down feature makes the AD7091R-2/AD7091R-4/ AD7091R-8 devices ideal for low sampling rates (of even a few hertz) and battery-powered applications.

Table 8. Recommended Power Management Devices<sup>1</sup>

| Product | Description                                       |

|---------|---------------------------------------------------|

| ADP7102 | 20 V, 300 mA, low noise, CMOS LDO                 |

| ADM7160 | Ultralow noise, 200 mA linear regulator           |

| ADP162  | Ultralow quiescent current, CMOS linear regulator |

<sup>1</sup> For the latest recommended power management devices, see the AD7091R-2/ AD7091R-4/AD7091R-8 product pages.

### **DEVICE RESET**

Upon power up, a reset pulse of at least 10 ns in width must be provided on the RESET pin to ensure proper initialization of the device. Failure to apply the reset pulse may result in a device malfunction. See Figure 43 for reset pulse timing relative to power supply establishment. If the system has a limited number of digital pins and one cannot be allocated to the reset pin of the ADC, a software reset may be issued in place of the hardware reset signal (see the Power-On Device Initialization section).

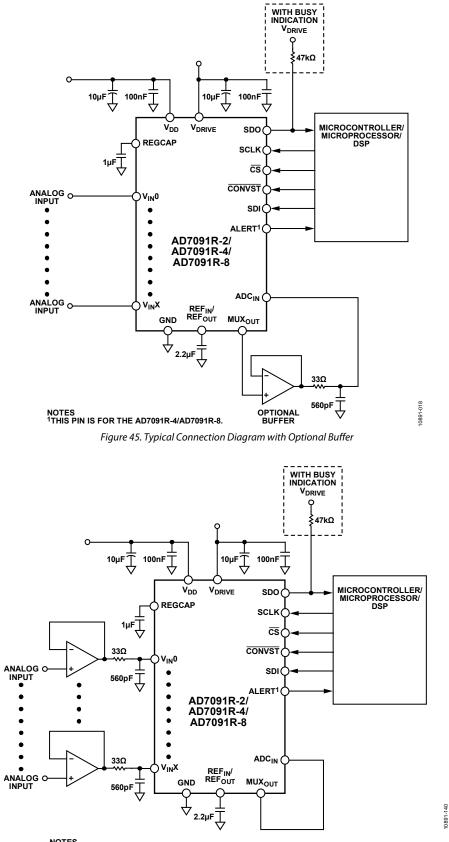

#### **TYPICAL CONNECTION DIAGRAM**

# Figure 45 shows a typical connection diagram for the AD7091R-2/AD7091R-4/AD7091R-8.

Connect a positive power supply in the 2.7 V to 5.25 V range to the V<sub>DD</sub> pin. Typical values for these decoupling capacitors are 0.1  $\mu$ F and 10  $\mu$ F. Place these capacitors near the device pins. Take care to decouple the REF<sub>IN</sub>/REF<sub>OUT</sub> pin to achieve specified performance. The typical value for the REF<sub>IN</sub>/REF<sub>OUT</sub> capacitor is 2.2  $\mu$ F, which provides an analog input range of 0 V to V<sub>REF</sub>. The typical value for the regulator bypass (REGCAP) decoupling capacitor is 1.0  $\mu$ F. The voltage applied to the V<sub>DRIVE</sub> input controls the voltage of the serial interface; therefore, connect this pin to the supply voltage of the microprocessor. Set V<sub>DRIVE</sub> in the 1.8 V to 5.25 V range. Typical values for the V<sub>DRIVE</sub> decoupling capacitors are 0.1  $\mu$ F and 10  $\mu$ F. The conversion result is output in a 16-bit word with the MSBs first.

When an externally applied reference is required, disable the internal reference using the configuration register. Choose the externally applied reference voltage in the 1.0 V to 5.25 V  $V_{DD}$  range and connect it to the REF<sub>IN</sub>/REF<sub>OUT</sub> pin.

For applications where power consumption is a concern, use the power-down mode of the ADC to improve power performance. See the Modes of Operation section for additional details.

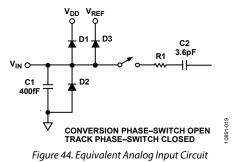

### **ANALOG INPUT**

Figure 44 shows an equivalent circuit of the analog input structure of the AD7091R-2/AD7091R-4/AD7091R-8. The two diodes, D1 and D2, provide ESD protection for the analog input. Take care to ensure that the analog input signal never exceeds the supply rails by more than 300 mV because this causes these diodes to become forward-biased and start conducting current into the substrate. These diodes can conduct a maximum of 10 mA without causing irreversible damage to the device.

The C1 capacitor in Figure 44 is typically about 400 fF and can primarily be attributed to pin capacitance. The R1 resistor is a lumped component composed of the on resistance of a switch. This resistor is typically about 500  $\Omega$ . The C2 capacitor is the ADC sampling capacitor and typically has a capacitance of 3.6 pF.

In applications where harmonic distortion and signal-to-noise ratio are critical, drive the analog inputs from low impedance sources. Large source impedances significantly affect the ac performance of the ADC that can necessitate using input buffer amplifiers, as shown in Figure 45. The choice of the op amp is a function of the particular application.

When no amplifiers are used to drive the analog input, limit the source impedance to low values. The maximum source impedance depends on the amount of THD that can be tolerated. The THD increases as the source impedance increases and performance degrades.

## Data Sheet

Use an external filter on the analog input signal paths to the AD7091R-2/AD7091R-4/AD7091R-8  $V_{\rm INX}$  pins to achieve the specified performance. This filter can be a one-pole low-pass RC filter, or similar.

Connect the MUX<sub>OUT</sub> pin directly to the ADC<sub>IN</sub> pin. Insert a buffer amplifier in the path, if desired. When sequencing channels, do not place a filter between MUX<sub>OUT</sub> and the input to any buffering because doing so leads to crosstalk. If buffering is not employed, do not place a filter between MUX<sub>OUT</sub> and ADC<sub>IN</sub> when sequencing channels because doing so leads to crosstalk.

### **DRIVER AMPLIFIER CHOICE**

Although the AD7091R-2/AD7091R-4/AD7091R-8 are easy to drive, a driver amplifier must meet the following requirements: