# 18-Bit, 2.5 LSB INL, 100 kSPS SAR ADC

# AD7678

#### FEATURES

18-bit resolution with no missing codes No pipeline delay (SAR architecture) Differential input range: ±V<sub>REF</sub> (V<sub>REF</sub> up to 5 V) Throughput: 100 kSPS INL: ±2.5 LSB max (±9.5 ppm of full scale) Dynamic range: 103 dB typ (V<sub>REF</sub> = 5 V) S/(N+D): 100 dB typ @ 2 kHz (V<sub>REF</sub> = 5 V) Parallel (18-,16-, or 8-bit bus) and serial 5 V/3 V interface SPI<sup>®</sup>/QSPI<sup>™</sup>/MICROWIRE<sup>™</sup>/DSP compatible On-board reference buffer Single 5 V supply operation Power dissipation: 18 mW @ 100 kSPS 180 μW @ 1 kSPS 48-lead LQFP or 48-lead LFCSP package Pin-to-pin compatible upgrade of AD7674/AD7676/AD7679

#### APPLICATIONS

CT scanners High dynamic data acquisition Geophone and hydrophone sensors  $\Sigma$ - $\Delta$  replacement (low power, multichannel) Instrumentation Spectrum analysis Medical instruments

### **GENERAL DESCRIPTION**

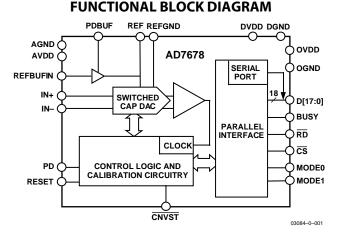

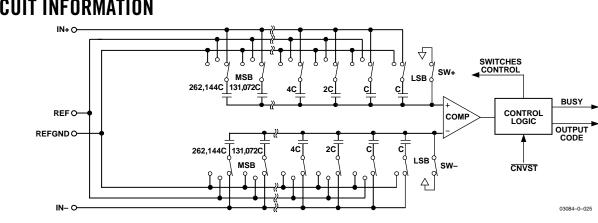

The AD7678 is an 18-bit, 100 kSPS, charge redistribution SAR, fully differential analog-to-digital converter that operates on a single 5 V power supply. The part contains a high speed 18-bit sampling ADC, an internal conversion clock, an internal reference buffer, error correction circuits, and both serial and parallel system interface ports.

The part is available in 48-lead LQFP or 48-lead LFCSP packages with operation specified from -40°C to +85°C.

Figure 1. Functional Block Diagram

#### Table 1. PulSAR Selection

| Type/kSPS                     | 100–250                 | 500-570                        | 800-<br>1000     |

|-------------------------------|-------------------------|--------------------------------|------------------|

| Pseudo-<br>Differential       | AD7651<br>AD7660/AD7661 | AD7650/AD7652<br>AD7664/AD7666 | AD7653<br>AD7667 |

| True Bipolar                  | AD7663                  | AD7665                         | AD7671           |

| True<br>Differential          | AD7675                  | AD7676                         | AD7677           |

| 18-Bit                        | AD7678                  | AD7679                         | AD7674           |

| Multichannel/<br>Simultaneous |                         | AD7654<br>AD7655               |                  |

#### **PRODUCT HIGHLIGHTS**

- High Resolution, Fast Throughput. The AD7678 is a 100 kSPS, charge redistribution, 18-bit SAR ADC (no latency).

- Excellent Accuracy. The AD7678 has a maximum integral nonlinearity of 2.5 LSB with no missing 18-bit codes.

- Serial or Parallel Interface. Versatile parallel (18-, 16-, or 8-bit bus) or 2-wire serial interface arrangement compatible with both 3 V and 5 V logic.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **AD7678\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### EVALUATION KITS

• AD7678 Evaluation Kit

### **DOCUMENTATION**

#### **Application Notes**

- AN-931: Understanding PulSAR ADC Support Circuitry

- AN-932: Power Supply Sequencing

### Data Sheet

• AD7678: 18-Bit, 2.5 LSB INL, 100 kSPS SAR ADC Data Sheet

#### **Product Highlight**

• 8- to 18-Bit SAR ADCs ... From the Leader in High Performance Analog

### REFERENCE MATERIALS

#### **Technical Articles**

• MS-2210: Designing Power Supplies for High Speed ADC

### DESIGN RESOURCES

- AD7678 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all AD7678 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# TABLE OF CONTENTS

| Specifications                              |

|---------------------------------------------|

| Timing Specifications                       |

| Absolute Maximum Ratings7                   |

| ESD Caution7                                |

| Pin Configuration and Function Descriptions |

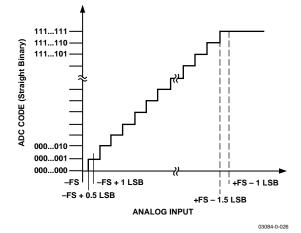

| Definition of Specifications11              |

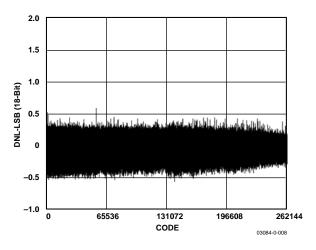

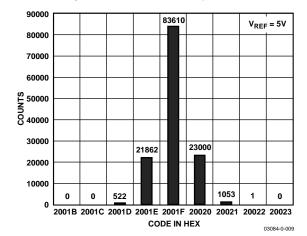

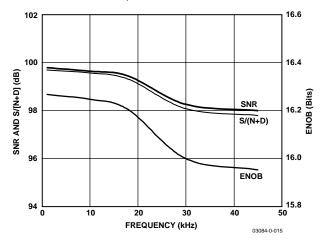

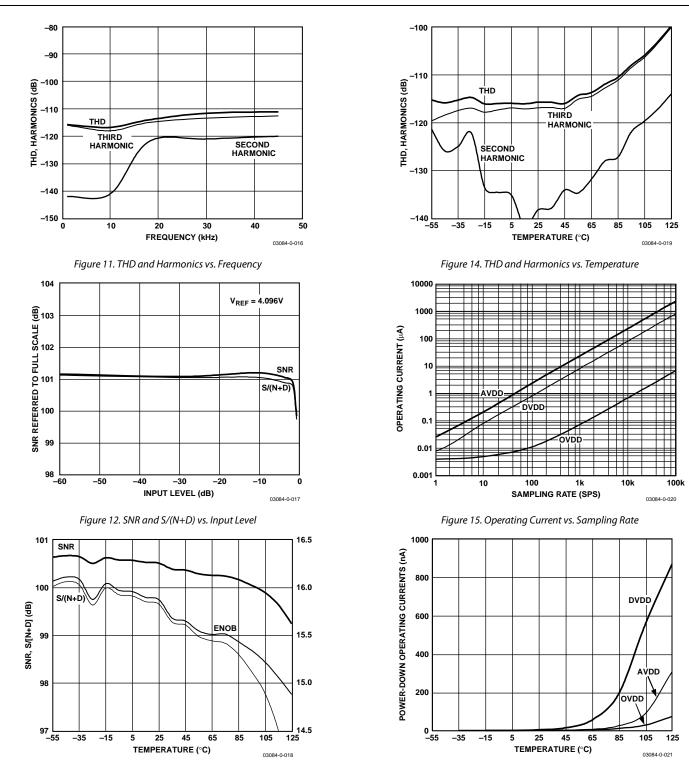

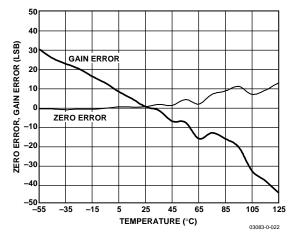

| Typical Performance Characteristics         |

| Circuit Information                         |

| Converter Operation15                       |

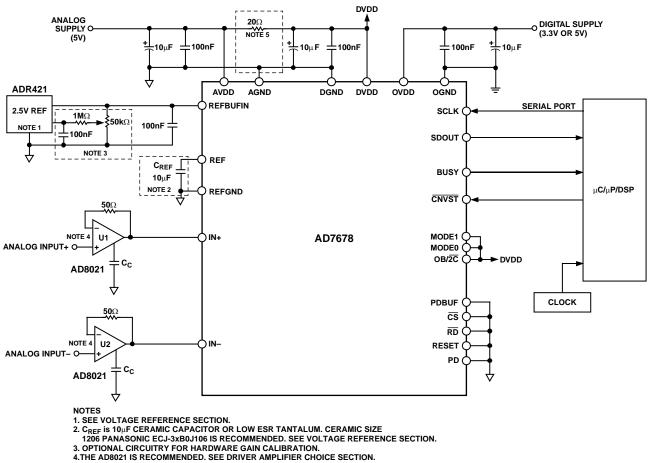

| Typical Connection Diagram17                |

| Power Dissipation versus Throughput19       |

| Conversion Control                          |

| Digital Interface                   | 20 |

|-------------------------------------|----|

| Parallel Interface                  | 20 |

| Serial Interface                    | 20 |

| Master Serial Interface             |    |

| Slave Serial Interface              |    |

| Microprocessor Interfacing          |    |

| Application Hints                   |    |

| Layout                              | 25 |

| Evaluating the AD7678's Performance | 25 |

| Outline Dimensions                  |    |

| Ordering Guide                      |    |

### **REVISION HISTORY**

#### 6/09—Rev. 0 to Rev. A

| Removed Endnote 3 from DC Accuracy; Zero Error, $T_{\mbox{\scriptsize MIN}}$ to |    |

|---------------------------------------------------------------------------------|----|

| T <sub>MAX</sub> Parameter; Table 2                                             | 3  |

| Changes to Endnote 3, Table 2                                                   | 4  |

| Moved ESD Caution                                                               | 7  |

| Changes to Figure 4 and Table 6                                                 | 8  |

| Changes to Evaluating the AD7678's Performance Section                          | 25 |

| Updated Outline Dimensions                                                      | 26 |

| Changes to Ordering Guide                                                       | 26 |

|                                                                                 |    |

8/03—Revision 0: Initial Version

### **SPECIFICATIONS**

Table 2. -40°C to +85°C, V<sub>REF</sub> = 4.096 V, AVDD = DVDD = 5 V, OVDD = 2.7 V to 5.25 V, unless otherwise noted.

| Conditions                                           |                                                                                                                                                                                                  | Тур                                                     | Max                                                     | Unit                                                    |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

|                                                      | 18                                                                                                                                                                                               |                                                         |                                                         | Bits                                                    |

|                                                      |                                                                                                                                                                                                  |                                                         |                                                         |                                                         |

| $V_{\text{I}\text{N}+}-V_{\text{I}\text{N}-}$        | $-V_{REF}$                                                                                                                                                                                       |                                                         | $+V_{\text{REF}}$                                       | V                                                       |

| $V_{IN+}$ , $V_{IN-}$ to AGND                        | -0.1                                                                                                                                                                                             |                                                         | AVDD + 0.1                                              | V                                                       |

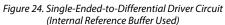

| $f_{IN} = 100 \text{ kHz}$                           |                                                                                                                                                                                                  | 65                                                      |                                                         | dB                                                      |

| 100 kSPS Throughput                                  |                                                                                                                                                                                                  | 4                                                       |                                                         | μA                                                      |

|                                                      |                                                                                                                                                                                                  |                                                         |                                                         |                                                         |

|                                                      |                                                                                                                                                                                                  |                                                         |                                                         |                                                         |

|                                                      |                                                                                                                                                                                                  |                                                         | 10                                                      | μs                                                      |

|                                                      | 0                                                                                                                                                                                                |                                                         | 100                                                     | kSPS                                                    |

|                                                      |                                                                                                                                                                                                  |                                                         |                                                         |                                                         |

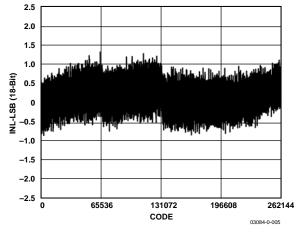

|                                                      | -2.5                                                                                                                                                                                             |                                                         | +2.5                                                    | LSB <sup>2</sup>                                        |

|                                                      | -1                                                                                                                                                                                               |                                                         | +1.75                                                   | LSB                                                     |

|                                                      | 18                                                                                                                                                                                               |                                                         |                                                         | Bits                                                    |

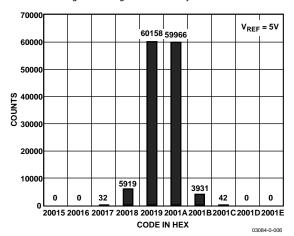

| $V_{REF} = 5 V$                                      |                                                                                                                                                                                                  | 0.7                                                     |                                                         | LSB                                                     |

|                                                      | -40                                                                                                                                                                                              |                                                         | ±40                                                     | LSB                                                     |

|                                                      |                                                                                                                                                                                                  | ±0.5                                                    |                                                         | ppm/°C                                                  |

|                                                      | -0.048                                                                                                                                                                                           | See Note 3                                              | +0.048                                                  | % of FSI                                                |

|                                                      |                                                                                                                                                                                                  | ±1.6                                                    |                                                         | ppm/°C                                                  |

| $AVDD = 5 V \pm 5\%$                                 |                                                                                                                                                                                                  | ±4                                                      |                                                         | LSB                                                     |

|                                                      |                                                                                                                                                                                                  |                                                         |                                                         |                                                         |

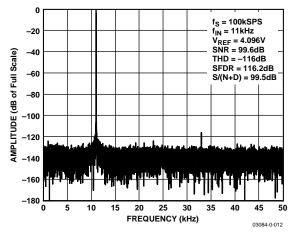

| $f_{IN} = 2 \text{ kHz}, V_{REF} = 5 \text{ V}$      |                                                                                                                                                                                                  | 101                                                     |                                                         | dB <sup>4</sup>                                         |

| $V_{REF} = 4.096 V$                                  | 98                                                                                                                                                                                               | 100                                                     |                                                         | dB                                                      |

| $f_{IN} = 10 \text{ kHz}, V_{REF} = 4.096 \text{ V}$ |                                                                                                                                                                                                  | 99.5                                                    |                                                         | dB                                                      |

| $f_{IN} = 45 \text{ kHz}, V_{REF} = 4.096 \text{ V}$ |                                                                                                                                                                                                  | 98                                                      |                                                         | dB                                                      |

|                                                      |                                                                                                                                                                                                  | 103                                                     |                                                         | dB                                                      |

|                                                      |                                                                                                                                                                                                  | 120                                                     |                                                         | dB                                                      |

|                                                      |                                                                                                                                                                                                  | 117                                                     |                                                         | dB                                                      |

|                                                      |                                                                                                                                                                                                  |                                                         |                                                         | kHz                                                     |

|                                                      |                                                                                                                                                                                                  | 200                                                     |                                                         | KI IZ                                                   |

|                                                      |                                                                                                                                                                                                  | 2                                                       |                                                         | ns                                                      |

|                                                      |                                                                                                                                                                                                  |                                                         |                                                         | ps rms                                                  |

| Full-Scale Step                                      |                                                                                                                                                                                                  | 5                                                       | 85                                                      |                                                         |

|                                                      |                                                                                                                                                                                                  |                                                         |                                                         | μs<br>μs                                                |

|                                                      |                                                                                                                                                                                                  |                                                         | 0.5                                                     | μ <b>3</b>                                              |

| REE                                                  | 3                                                                                                                                                                                                | 1 006                                                   |                                                         | v                                                       |

|                                                      |                                                                                                                                                                                                  |                                                         |                                                         | v                                                       |

|                                                      |                                                                                                                                                                                                  |                                                         |                                                         |                                                         |

| DEERIJEINI                                           |                                                                                                                                                                                                  |                                                         |                                                         |                                                         |

| REFBUFIN                                             | 1.8<br>-1                                                                                                                                                                                        | 2.5                                                     | 2.6<br>+1                                               | V<br>μA                                                 |

| -                                                    | $V_{IN+}, V_{IN-} \text{ to AGND}$ $f_{IN} = 100 \text{ kHz}$ $100 \text{ kSPS Throughput}$ $V_{REF} = 5 \text{ V}$ $AVDD = 5 \text{ V} \pm 5\%$ $f_{IN} = 2 \text{ kHz}, V_{REF} = 5 \text{ V}$ | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

| Parameter                      | Conditions                           | Min      | Тур | Max         | Unit |

|--------------------------------|--------------------------------------|----------|-----|-------------|------|

| DIGITAL INPUTS                 |                                      |          |     |             |      |

| Logic Levels                   |                                      |          |     |             |      |

| VIL                            |                                      | -0.3     |     | +0.8        | V    |

| VIH                            |                                      | 2.0      |     | DVDD + 0.3  | V    |

| lı.                            |                                      | -1       |     | +1          | μA   |

| Ін                             |                                      | -1       |     | +1          | μA   |

| DIGITAL OUTPUTS                |                                      |          |     |             |      |

| Data Format⁵                   |                                      |          |     |             |      |

| Pipeline Delay <sup>6</sup>    |                                      |          |     |             |      |

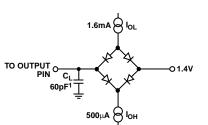

| Vol                            | I <sub>SINK</sub> = 1.6 mA           |          |     | 0.4         | V    |

| Vон                            | $I_{SOURCE} = -500 \ \mu A$          | OVDD – 0 | .6  |             | V    |

| POWER SUPPLIES                 |                                      |          |     |             |      |

| Specified Performance          |                                      |          |     |             |      |

| AVDD                           |                                      | 4.75     | 5   | 5.25        | V    |

| DVDD                           |                                      | 4.75     | 5   | 5.25        | V    |

| OVDD                           |                                      | 2.7      |     | DVDD + 0.37 | V    |

| Operating Current              | 100 kSPS Throughput                  |          |     |             |      |

| AVDD                           | PDBUF High                           |          | 2.6 |             | mA   |

| DVDD <sup>8</sup>              |                                      |          | 1   |             | mA   |

| OVDD <sup>8</sup>              |                                      |          | 40  |             | μΑ   |

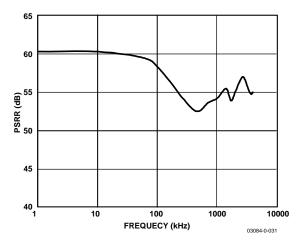

|                                | PDBUF High @ 100 kSPS                |          | 18  | 26          | mW   |

|                                | PDBUF High @ 1 kSPS                  |          | 180 |             | μW   |

|                                | PDBUF Low @ 100 kSPS                 |          | 31  |             | mW   |

| TEMPERATURE RANGE <sup>9</sup> |                                      |          |     |             |      |

| Specified Performance          | T <sub>MIN</sub> to T <sub>MAX</sub> | -40      |     | +85         | °C   |

<sup>&</sup>lt;sup>1</sup> See the Analog Inputs section.

<sup>5</sup> Data format parallel or serial 18-bit.

$<sup>^2</sup>$  LSB means Least Significant Bit. With the ±4.096 V input range, 1 LSB is 31.25  $\mu V.$

<sup>&</sup>lt;sup>3</sup> See the Definition of Specifications section. The nominal gain error is not centered at zero and is -0.029% of FSR. This specification is the deviation from this nominal value. These specifications do not include the error contribution from the external reference, but do include the error contribution from the reference buffer if used. <sup>4</sup> All specifications in dB are referred to a full-scale input, FS. Tested with an input signal at 0.5 dB below full scale, unless otherwise specified.

<sup>&</sup>lt;sup>6</sup> Conversion results are available immediately after completed conversion. <sup>7</sup> The maximum should be the minimum of 5.25 V and DVDD + 0.3 V.

<sup>&</sup>lt;sup>8</sup> Tested in Parallel Reading mode.

<sup>&</sup>lt;sup>9</sup> Contact factory for extended temperature range.

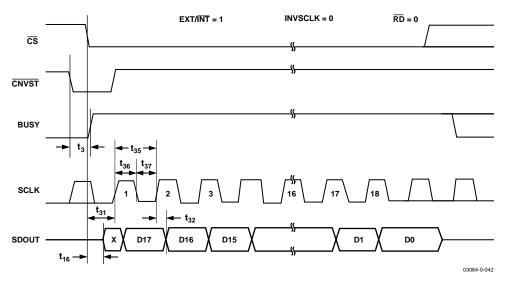

### **TIMING SPECIFICATIONS**

Table 3. -40°C to +85°C, AVDD = DVDD = 5 V, OVDD = 2.7 V to 5.25 V, unless otherwise noted.

| Parameter                                                                     | Symbol                 | Min | Тур         | Max | Unit |

|-------------------------------------------------------------------------------|------------------------|-----|-------------|-----|------|

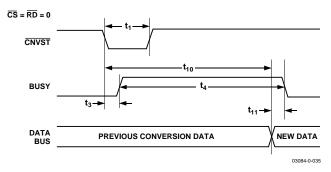

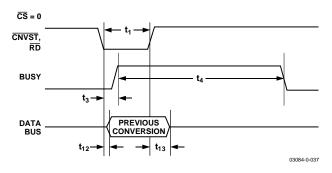

| Refer to Figure 27 and Figure 28                                              | -                      |     | -           |     |      |

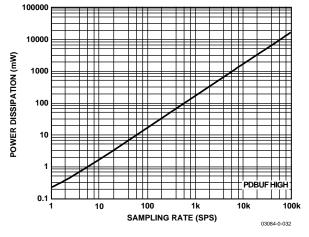

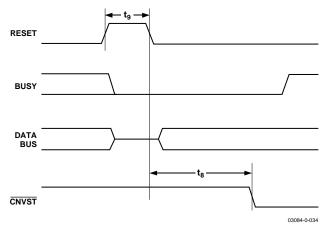

| Convert Pulse Width                                                           | t1                     | 10  |             |     | ns   |

| Time between Conversions                                                      | t <sub>2</sub>         | 10  |             |     | μs   |

| CNVST LOW to BUSY HIGH Delay                                                  | t <sub>3</sub>         |     |             | 35  | ns   |

| BUSY HIGH All Modes Except Master Serial Read after Convert                   | t4                     |     |             | 1.5 | μs   |

| Aperture Delay                                                                | t <sub>5</sub>         |     | 2           |     | ns   |

| End of Conversion to BUSY LOW Delay                                           | t <sub>6</sub>         | 10  |             |     | ns   |

| Conversion Time                                                               | t <sub>7</sub>         |     |             | 1.5 | μs   |

| Acquisition Time                                                              | t <sub>8</sub>         | 8.5 |             |     | μs   |

| RESET Pulsewidth                                                              | t <sub>9</sub>         | 10  |             |     | ns   |

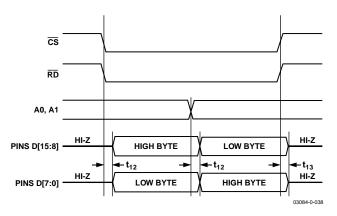

| Refer to Figure 29, Figure 30, and Figure 31 (Parallel Interface Modes)       |                        |     |             |     |      |

| CNVST LOW to Data Valid Delay                                                 | t10                    |     |             | 1.5 | μs   |

| Data Valid to BUSY LOW Delay                                                  | t11                    | 20  |             |     | ns   |

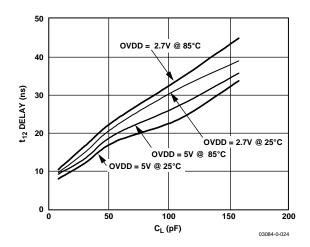

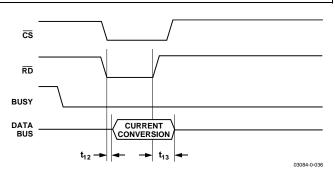

| Bus Access Request to Data Valid                                              | t <sub>12</sub>        |     |             | 45  | ns   |

| Bus Relinquish Time                                                           | t <sub>13</sub>        | 5   |             | 15  | ns   |

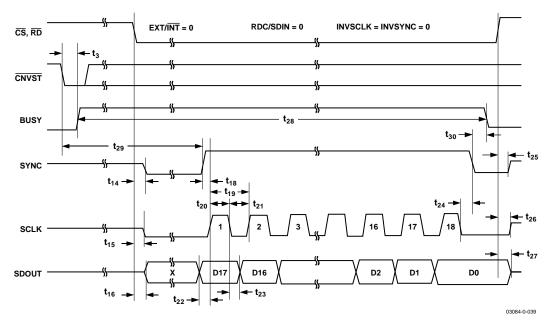

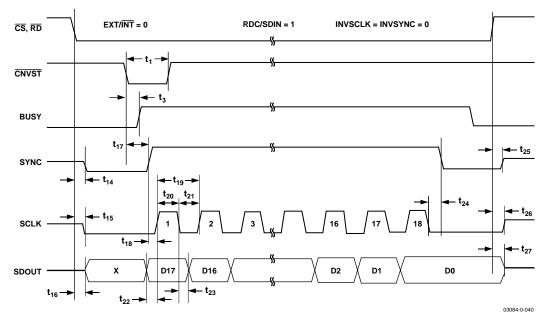

| Refer to Figure 33 and Figure 34 (Master Serial Interface Modes) <sup>1</sup> |                        |     |             |     |      |

| CS LOW to SYNC Valid Delay                                                    | t <sub>14</sub>        |     |             | 10  | ns   |

| CS LOW to Internal SCLK Valid Delay                                           | t15                    |     |             | 10  | ns   |

| CS LOW to SDOUT Delay                                                         | t <sub>16</sub>        |     |             | 10  | ns   |

| CNVST LOW to SYNC Delay                                                       | t <sub>17</sub>        |     | 525         |     | ns   |

| SYNC Asserted to SCLK First Edge Delay <sup>2</sup>                           | t <sub>18</sub>        | 3   |             |     | ns   |

| Internal SCLK Period <sup>2</sup>                                             | <b>t</b> <sub>19</sub> | 25  |             | 40  | ns   |

| Internal SCLK HIGH <sup>2</sup>                                               | t <sub>20</sub>        | 12  |             |     | ns   |

| Internal SCLK LOW <sup>2</sup>                                                | t <sub>21</sub>        | 7   |             |     | ns   |

| SDOUT Valid Setup Time <sup>2</sup>                                           | t <sub>22</sub>        | 4   |             |     | ns   |

| SDOUT Valid Hold Time <sup>2</sup>                                            | t <sub>23</sub>        | 2   |             |     | ns   |

| SCLK Last Edge to SYNC Delay <sup>2</sup>                                     | t <sub>24</sub>        | 3   |             |     | ns   |

| CS HIGH to SYNC HI-Z                                                          | t <sub>25</sub>        |     |             | 10  | ns   |

| CS HIGH to Internal SCLK HI-Z                                                 | t <sub>26</sub>        |     |             | 10  | ns   |

| CS HIGH to SDOUT HI-Z                                                         | t <sub>27</sub>        |     |             | 10  | ns   |

| BUSY HIGH in Master Serial Read after Convert <sup>2</sup>                    | t <sub>28</sub>        |     | See Table 4 |     |      |

| CNVST LOW to SYNC Asserted Delay                                              | t <sub>29</sub>        |     | 1.5         |     | μs   |

| SYNC Deasserted to BUSY LOW Delay                                             | t <sub>30</sub>        |     | 25          |     | ns   |

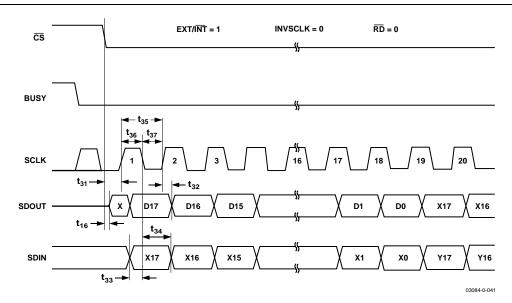

| Refer to Figure 35 and Figure 36 (Slave Serial Interface Modes)               |                        |     |             |     |      |

| External SCLK Setup Time                                                      | t <sub>31</sub>        | 5   |             |     | ns   |

| External SCLK Active Edge to SDOUT Delay                                      | t <sub>32</sub>        | 3   |             | 18  | ns   |

| SDIN Setup Time                                                               | t <sub>33</sub>        | 5   |             |     | ns   |

| SDIN Hold Time                                                                | t <sub>34</sub>        | 5   |             |     | ns   |

| External SCLK Period                                                          | t <sub>35</sub>        | 25  |             |     | ns   |

| External SCLK HIGH                                                            | t <sub>36</sub>        | 10  |             |     | ns   |

| External SCLK LOW                                                             | t <sub>37</sub>        | 10  |             |     | ns   |

<sup>1</sup>In serial interface modes, the SYNC, SCLK, and SDOUT timings are defined with a maximum load C<sub>L</sub> of 10 pF; otherwise, the load is 60 pF maximum. <sup>2</sup>In Serial Master Read during Convert mode. See Table 4 for Serial Master Read after Convert mode.

### Table 4. Serial Clock Timings in Master Read after Convert

| DIVSCLK[1]                            |                 | 0    | 0  | 1   | 1   |      |

|---------------------------------------|-----------------|------|----|-----|-----|------|

| DIVSCLK[0]                            | Symbol          | 0    | 1  | 0   | 1   | Unit |

| SYNC to SCLK First Edge Delay Minimum | t <sub>18</sub> | 3    | 17 | 17  | 17  | ns   |

| Internal SCLK Period Minimum          | t19             | 25   | 60 | 120 | 240 | ns   |

| Internal SCLK Period Maximum          | t <sub>19</sub> | 40   | 80 | 160 | 320 | ns   |

| Internal SCLK HIGH Minimum            | t <sub>20</sub> | 12   | 22 | 50  | 100 | ns   |

| Internal SCLK LOW Minimum             | t <sub>21</sub> | 7    | 21 | 49  | 99  | ns   |

| SDOUT Valid Setup Time Minimum        | t <sub>22</sub> | 4    | 18 | 18  | 18  | ns   |

| SDOUT Valid Hold Time Minimum         | t <sub>23</sub> | 2    | 4  | 30  | 89  | ns   |

| SCLK Last Edge to SYNC Delay Minimum  | t <sub>24</sub> | 3    | 60 | 140 | 300 | ns   |

| Busy High Width Maximum               | t <sub>28</sub> | 2.25 | 3  | 4.5 | 7.5 | μs   |

### ABSOLUTE MAXIMUM RATINGS

Table 5. AD7678 Absolute Maximum Ratings<sup>1</sup>

| Table 5. AD7078 Absolute Maximum Ratings |  |  |  |  |  |

|------------------------------------------|--|--|--|--|--|

| Rating                                   |  |  |  |  |  |

|                                          |  |  |  |  |  |

| AVDD + 0.3 V to                          |  |  |  |  |  |

| AGND – 0.3 V                             |  |  |  |  |  |

|                                          |  |  |  |  |  |

| ±0.3 V                                   |  |  |  |  |  |

|                                          |  |  |  |  |  |

| –0.3 V to +7 V                           |  |  |  |  |  |

| ±7 V                                     |  |  |  |  |  |

| –0.3 V to +7 V                           |  |  |  |  |  |

| –0.3 V to DVDD + 0.3 V                   |  |  |  |  |  |

| 700 mW                                   |  |  |  |  |  |

| 2.5 W                                    |  |  |  |  |  |

| 150°C                                    |  |  |  |  |  |

| –65°C to +150°C                          |  |  |  |  |  |

|                                          |  |  |  |  |  |

| 300°C                                    |  |  |  |  |  |

|                                          |  |  |  |  |  |

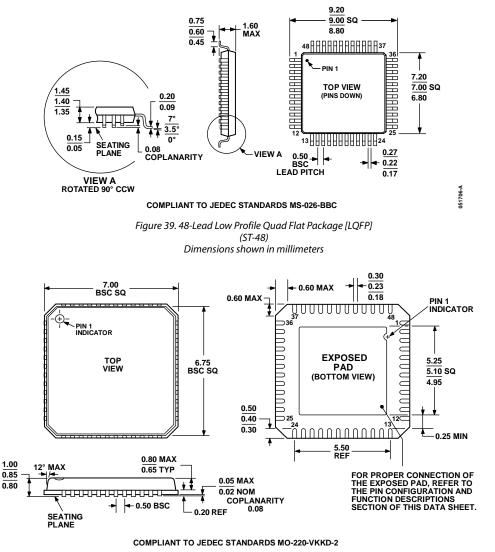

- <sup>2</sup>See Analog Inputs section.

- <sup>3</sup>Specification is for device in free air: 48-Lead LQFP:  $\theta_{JA} = 91^{\circ}C/W$ ,  $\theta_{JC} = 30^{\circ}C/W$ .

- <sup>4</sup> Specification is for device in free air: 48-Lead LFCSP:  $\theta_{JA} = 26^{\circ}C/W$ .

<sup>1</sup>IN SERIAL INTERFACE MODES, THE SYNC, SCLK, AND SDOUT TIMINGS ARE DEFINED WITH A MAXIMUM LOAD C<sub>L</sub> OF 10pF; OTHERWISE, THE LOAD IS 60pF MAXIMUM.

Figure 2. Load Circuit for Digital Interface Timing, SDOUT, SYNC, SCLK Outputs, C<sub>L</sub> = 10 pF

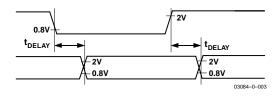

Figure 3. Voltage Reference Levels for Timing

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

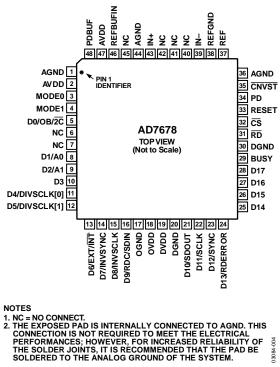

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 4. 48-Lead LQFP and 48-Lead LFCSP (ST-48 and CP-48) Pin Configuration

| _ | Table 6. 1 | Pin | Function | De | escription | <b>S</b> |

|---|------------|-----|----------|----|------------|----------|

|   |            |     |          |    |            |          |

| Pin No.                    | Mnemonic                 | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                  |                              |                                         |                                                                                                                                            |  |  |  |

|----------------------------|--------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1, 44                      | AGND                     | Р                 | Analog Power Ground                                                                                                                                                                                                                                                                                                                                                                            | Analog Power Ground Pin.                                                                                                                                                                                         |                              |                                         |                                                                                                                                            |  |  |  |

| 2, 47                      | AVDD                     | Р                 | Input Analog Power Pins. Nominally 5 V.                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                  |                              |                                         |                                                                                                                                            |  |  |  |

| 3                          | MODE0                    | DI                | Data Output Interface                                                                                                                                                                                                                                                                                                                                                                          | Data Output Interface Mode Selection.                                                                                                                                                                            |                              |                                         |                                                                                                                                            |  |  |  |

| 4                          | MODE1                    | DI                | Data Output Interface                                                                                                                                                                                                                                                                                                                                                                          | e Mode Sele                                                                                                                                                                                                      | ection:                      |                                         |                                                                                                                                            |  |  |  |

|                            |                          |                   | Interface MODE #                                                                                                                                                                                                                                                                                                                                                                               | MODE1                                                                                                                                                                                                            | MODE0                        | Description                             | -                                                                                                                                          |  |  |  |

|                            |                          |                   | 0                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                | 0                            | 18-Bit Interface                        | -                                                                                                                                          |  |  |  |

|                            |                          |                   | 1                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                | 1                            | 16-Bit Interface                        | -                                                                                                                                          |  |  |  |

|                            |                          |                   | 2                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                | 0                            | Byte Interface                          | -                                                                                                                                          |  |  |  |

|                            |                          |                   | 3                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                                                                                                | 1                            | Serial Interface                        | -                                                                                                                                          |  |  |  |

| 5<br>6, 7,<br>40–42,<br>45 | D0/OB/2C                 | DI/O              | When MODE = 0 (18-bit interface mode), this pin is Bit 0 of the parallel port data output bus an data coding is straight binary. In all other modes, this pin allows choice of straight binary/binar complement. When OB/2C is HIGH, the digital output is straight binary; when LOW, the MSB is inverted, resulting in a twos complement output from its internal shift register. No Connect. |                                                                                                                                                                                                                  |                              |                                         |                                                                                                                                            |  |  |  |

| 8                          | D1/A0                    | DI/O              | When MODE = 0 (18-bit interface mode), this pin is Bit 1 of the parallel port data output bus. In all other modes, this input pin controls the form in which data is output, as shown in Table 7.                                                                                                                                                                                              |                                                                                                                                                                                                                  |                              |                                         |                                                                                                                                            |  |  |  |

| 9                          | D2/A1                    | DI/O              |                                                                                                                                                                                                                                                                                                                                                                                                | When MODE = 0 or 1 (18-bit or 16-bit interface mode), this pin is Bit 2 of the parallel port data output bus. In all other modes, this input pin controls the form in which data is output, as shown in Table 7. |                              |                                         |                                                                                                                                            |  |  |  |

| 10                         | D3                       | DO                | In all modes except MODE = 3, this output is used as Bit 3 of the parallel port data output bus. This pin is always an output, regardless of the interface mode.                                                                                                                                                                                                                               |                                                                                                                                                                                                                  |                              |                                         |                                                                                                                                            |  |  |  |

| 11, 12                     | D[4:5]or<br>DIVSCLK[0:1] | DI/O              | When MODE = 3 (seri                                                                                                                                                                                                                                                                                                                                                                            | al mode), E<br>s, part of th                                                                                                                                                                                     | XT/INT is Lo<br>e serial por | OW, and RDC/SDIN<br>t, are used to slow | f the parallel port data output bus.<br>I is LOW (serial master read after<br>down, if desired, the internal serial clock<br>are not used. |  |  |  |

| Pin No. | Mnemonic         | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | D6               | DI/O              | In all modes except MODE = 3, this output is used as Bit 6 of the parallel port data output bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | or EXT/INT       |                   | When MODE = 3 (serial mode), this input, part of the serial port, is used as a digital select input for choosing the internal data clock or an external data clock. With EXT/INT tied LOW, the internal clock is selected on the SCLK output. With EXT/INT set to a logic HIGH, output data is synchronized to an                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | 57               | DI/O              | external clock signal connected to the SCLK input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14      | D7<br>or INVSYNC | DI/O              | In all modes except MODE = 3, this output is used as Bit 7 of the parallel port data output bus.<br>When MODE = 3 (serial mode), this input, part of the serial port, is used to select the active state of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | 5.0              | 51/0              | SYNC signal. When LOW, SYNC is active HIGH. When HIGH, SYNC is active LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15      | D8<br>or INVSCLK | DI/O              | In all modes except MODE = 3, this output is used as Bit 8 of the parallel port data output bus.<br>When MODE = 3 (serial mode), this input, part of the serial port, is used to invert the SCLK signal. It is active in both master and slave modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16      | D9               | DI/O              | In all modes except MODE = 3, this output is used as Bit 9 of the parallel port data output bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

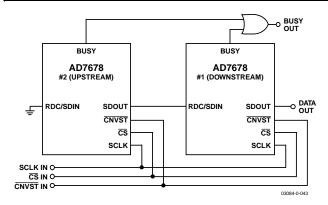

| 10      | or RDC/SDIN      | 01/0              | When $MODE = 3$ (serial mode), this input, part of the serial port, is used as either an external data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         |                  |                   | input or a read mode selection input depending on the state of EXT/INT. When EXT/INT is HIGH,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                  |                   | RDC/SDIN could be used as a data input to daisy-chain the conversion results from two or more ADCs onto a single SDOUT line. The digital data level on SDIN is output on SDOUT with a delay of 18 SCLK periods after the initiation of the read sequence. When EXT/INT is LOW, RDC/SDIN is used to select the                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                  |                   | read mode. When RDC/SDIN is HIGH, the data is output on SDOUT during conversion. When RDC/SDIN is LOW, the data can be output on SDOUT only when the conversion is complete.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17      | OGND             | Р                 | Input/Output Interface Digital Power Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18      | OVDD             | Р                 | Output Interface Digital Power. Nominally at the same supply as the host interface (5 V or 3 V). Should not exceed DVDD by more than 0.3 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19      | DVDD             | Р                 | Digital Power. Nominally at 5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 20      | DGND             | Р                 | Digital Power Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21      | D10<br>or SDOUT  | DO                | In all modes except MODE = 3, this output is used as Bit 10 of the parallel port data output bus.<br>When MODE = 3 (serial mode), this output, part of the serial port, is used as a serial data output<br>synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7678 provides the<br>conversion result, MSB first, from its internal shift register. The data format is determined by the logic<br>level of OB/2C. In serial mode when EXT/INT is LOW, SDOUT is valid on both edges of SCLK. In serial<br>mode when EXT/INT is HIGH and INVSCLK is LOW, SDOUT is updated on the SCLK rising edge and is<br>valid on the next falling edge; if INVSCLK is HIGH, SDOUT is updated on the SCLK falling edge and is<br>valid on the next rising edge. |

| 22      | D11              | DI/O              | In all modes except MODE = 3, this output is used as Bit 11 of the parallel port data output bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | or SCLK          |                   | When MODE = 3 (serial mode), this pin, part of the serial port, is used as a serial data clock input or output, depending upon the logic state of the EXT/INT pin. The active edge where the data SDOUT is updated depends upon the logic state of the INVSCLK pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 23      | D12              | DO                | In all modes except MODE = 3, this output is used as Bit 12 of the parallel port data output bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | or SYNC          |                   | When MODE = 3 (serial mode), this output, part of the serial port, is used as a digital output frame synchronization for use with the internal data clock (EXT/INT = Logic LOW). When a read sequence is initiated and INVSYNC is LOW, SYNC is driven HIGH and remains HIGH while the SDOUT output is valid. When a read sequence is initiated and INVSYNC is HIGH, SYNC is driven LOW and remains LOW while SDOUT output is valid.                                                                                                                                                                                                                                                                                                                                            |

| 24      | D13              | DO                | In all modes except MODE = 3, this output is used as Bit 13 of the parallel port data output bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | or RDERROR       |                   | In MODE = 3 (serial mode) and when EXT/INT is HIGH, this output, part of the serial port, is used as an incomplete read error flag. In slave mode, when a data read is started and not complete when the following conversion is complete, the current data is lost and RDERROR is pulsed high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 25–28   | D[14:17]         | DO                | Bit 14 to Bit 17 of the Parallel Port Data Output Bus. These pins are always outputs regardless of the interface mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 29      | BUSY             | DO                | Busy Output. Transitions HIGH when a conversion is started. Remains HIGH until the conversion is complete and the data is latched into the on-chip shift register. The falling edge of BUSY could be used as a data ready clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 30      | DGND             | Р                 | Must Be Tied to Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

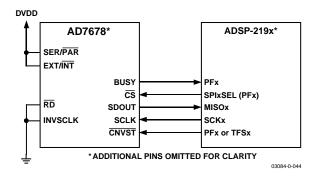

| 31      | RD               | DI                | Read Data. When $\overline{CS}$ and $\overline{RD}$ are both LOW, the interface parallel or serial output bus is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 32      | <u>cs</u>        | DI                | Chip Select. When $\overline{CS}$ and $\overline{RD}$ are both LOW, the interface parallel or serial output bus is enabled. $\overline{CS}$ is also used to gate the external clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 33      | RESET            | DI                | Reset Input. When set to a logic HIGH, reset the AD7678. Current conversion, if any, is aborted. If not used, this pin could be tied to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin No.      | Mnemonic              | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                     |