#### FEATURES

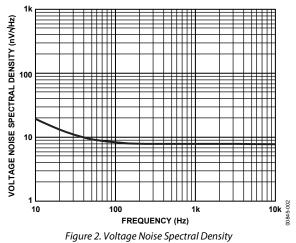

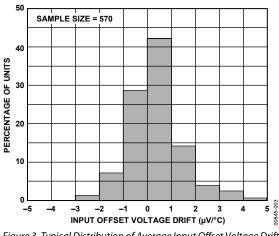

Low power replacement for Burr-Brown OPA111, OPA121 op amps Low noise 3.3 µV p-p maximum, 0.1 Hz to 10 Hz 11 nV/√Hz maximum at 10 kHz 0.6 fA/√Hz at 1 kHz High dc accuracy 500 µV maximum offset voltage 10 µV/°C maximum drift 2 pA maximum input bias current Low power: 1.5 mA maximum supply current

#### APPLICATIONS

Low noise photodiode preamps CT scanners Precision I-to-V converters

#### **GENERAL DESCRIPTION**

The AD795 is a low noise, precision, FET input operational amplifier. It offers both the low voltage noise and low offset drift of a bipolar input op amp and the very low bias current of a FET-input device. The  $10^{14} \Omega$  common-mode impedance insures that input bias current is essentially independent of common-mode voltage and supply voltage variations.

The AD795 has both excellent dc performance and a guaranteed and tested maximum input voltage noise. It features 2 pA maximum input bias current and 500  $\mu V$  maximum offset voltage, along with low supply current of 1.5 mA maximum.

Low Power, Low Noise Precision FET Op Amp AD795

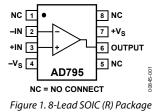

#### CONNECTION DIAGRAM

Furthermore, the AD795 features a guaranteed low input noise of 3.3  $\mu$ V p-p (0.1 Hz to 10 Hz) and a 11 nV/ $\sqrt{Hz}$  maximum noise level at 10 kHz. The AD795 has a fully specified and tested input offset voltage drift of only 10  $\mu$ V/°C maximum.

The AD795 is useful for many high input impedance, low noise applications. The AD795 is rated over the commercial temperature range of  $0^{\circ}$ C to  $+70^{\circ}$ C.

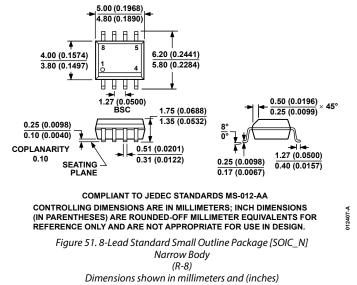

The AD795 is available in an 8-lead SOIC package.

Figure 3. Typical Distribution of Average Input Offset Voltage Drift

Rev. C Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **AD795\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### EVALUATION KITS

• EVAL-OPAMP-1 Evaluation Board

### **DOCUMENTATION**

#### **Application Notes**

- AN-202: An IC Amplifier User's Guide to Decoupling, Grounding, and Making Things Go Right for a Change

- AN-253: Find Op Amp Noise with Spreadsheet

- AN-256: Accurately Testing Op Amp Settling Times

- AN-356: User's Guide to Applying and Measuring Operational Amplifier Specifications

- AN-358: Noise and Operational Amplifier Circuits

- AN-649: Using the Analog Devices Active Filter Design Tool

#### **Data Sheet**

AD795: Low Power, Low Noise Precision FET Op Amp Data Sheet

### TOOLS AND SIMULATIONS $\square$

- Analog Filter Wizard

- Analog Photodiode Wizard

- AD795 SPICE Macro-Model

### DESIGN RESOURCES 🖵

- AD795 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all AD795 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

## TABLE OF CONTENTS

| Features 1                          |

|-------------------------------------|

| Applications1                       |

| Connection Diagram1                 |

| General Description                 |

| Revision History                    |

| Specifications                      |

| Absolute Maximum Ratings 5          |

| Thermal Resistance                  |

| ESD Caution                         |

| Typical Performance Characteristics |

| Minimizing Input Current11          |

| Circuit Board Notes                 |

#### **REVISION HISTORY**

#### 12/09—Rev. B to Rev. C

| Changes to Features Section and General Description Section | on.1 |

|-------------------------------------------------------------|------|

| Changes to Input Bias Current Parameter, Table 1            | 3    |

| Changes to Table 2                                          | 5    |

| Added Thermal Resistance Section                            | 5    |

| Added Table 3; Renumbered Sequentially                      | 5    |

| Changes to Minimizing Input Current Section                 | 11   |

| Changes to Circuit Board Notes Section and Figure 33        | 12   |

| Changes to Input Protection Section                         | 15   |

| Changes to Ordering Guide                                   | 18   |

|                                                             |      |

#### 10/02—Rev. A to Rev. B

| Deleted Plastic Mini-DIP (N) Package    | Universal |

|-----------------------------------------|-----------|

| Edits to Features                       | 1         |

| Edits to Specifications                 |           |

| Edits to Absolute Maximum Ratings       |           |

| Edits to Ordering Guide                 |           |

| Edits to Circuit Board Notes            | 9         |

| Edits to Figure 31                      | 9         |

| Edits to Offset Nulling                 |           |

| Deleted Figure 34                       |           |

| Deleted Low Noise Op Amp Selection Tree |           |

| Updated Outline Dimensions              |           |

| Offset Nulling                                       | 13     |

|------------------------------------------------------|--------|

| AC Response with High Value Source and Feedback Resi | stance |

|                                                      | 14     |

| Overload Issues                                      | 15     |

| Input Protection                                     | 15     |

| Preamplifier Applications                            | 16     |

| Minimizing Noise Contributions                       | 16     |

| Using a T Network                                    | 17     |

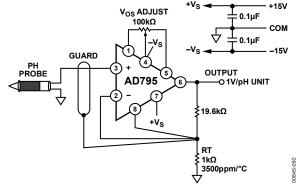

| A pH Probe Buffer Amplifier                          | 17     |

| Outline Dimensions                                   | 18     |

| Ordering Guide                                       | 18     |

## **SPECIFICATIONS**

At +25°C and  $\pm$ 15 V dc, unless otherwise noted.

#### Table 1.

|                                           | AD795JR                                                                                                |                  |                      |      |        |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------|----------------------|------|--------|

| Parameter                                 | <b>Test Conditions/Comments</b>                                                                        | Min              | Тур                  | Max  | Unit   |

| INPUT OFFSET VOLTAGE <sup>1</sup>         |                                                                                                        |                  |                      |      |        |

| Initial Offset                            |                                                                                                        |                  | 100                  | 500  | μV     |

| Offset                                    | T <sub>MIN</sub> – T <sub>MAX</sub>                                                                    |                  | 300                  | 1000 | μV     |

| vs. Temperature                           |                                                                                                        |                  | 3                    | 10   | μV/°C  |

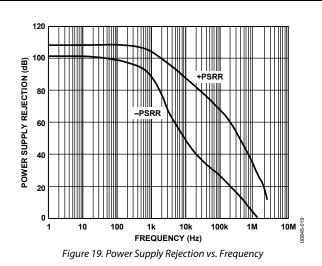

| vs. Supply (PSRR)                         |                                                                                                        | 86               | 110                  |      | dB     |

| vs. Supply (PSRR)                         | T <sub>MIN</sub> – T <sub>MAX</sub>                                                                    | 84               | 100                  |      | dB     |

| INPUT BIAS CURRENT <sup>2</sup>           |                                                                                                        |                  |                      |      |        |

| Either Input                              | $V_{CM} = 0 V$                                                                                         |                  | 1                    | 2    | pА     |

| Either Input at $T_{MAX} = 70^{\circ}C$   | $V_{CM} = 0 V$                                                                                         |                  | 23                   |      | nA     |

| Either Input                              | $V_{CM} = +10 V$                                                                                       |                  | 1                    |      | nA     |

| Offset Current                            | $V_{CM} = 0 V$                                                                                         |                  | 0.1                  | 1.0  | pА     |

| Offset Current at $T_{MAX} = 70^{\circ}C$ | $V_{CM} = 0 V$                                                                                         |                  | 2                    |      | nA     |

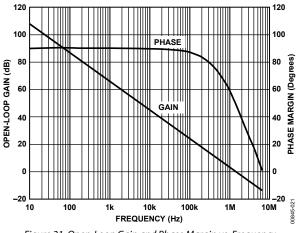

| OPEN-LOOP GAIN                            | $V_0 = \pm 10 V$                                                                                       |                  |                      |      |        |

|                                           | R <sub>L</sub> ≥ 10 kΩ                                                                                 | 110              | 120                  |      | dB     |

|                                           | $R_{\rm L} \ge 10 \ \rm k\Omega$                                                                       | 100              | 108                  |      | dB     |

| INPUT VOLTAGE NOISE                       | 0.1 Hz to 10 Hz                                                                                        |                  | 1.0                  | 3.3  | μV p-p |

|                                           | f = 10  Hz                                                                                             |                  | 20                   | 50   | nV/√Hz |

|                                           | f = 100  Hz                                                                                            |                  | 12                   | 40   | nV/√Hz |

|                                           | f = 1  kHz                                                                                             |                  | 11                   | 17   | nV/√Hz |

|                                           | f = 10  kHz                                                                                            |                  | 9                    | 11   | nV/√Hz |

| INPUT CURRENT NOISE                       | f = 0.1 Hz to 10 Hz                                                                                    |                  | 13                   |      | fA p-p |

| INFOT CORRENT NOISE                       | f = 1  kHz                                                                                             |                  | 0.6                  |      | fA/√Hz |

| FREQUENCY RESPONSE                        |                                                                                                        |                  | 0.0                  |      |        |

| Unity Gain, Small Signal                  | G = -1                                                                                                 |                  | 1.6                  |      | MHz    |

| Full Power Response                       | $V_0 = 20 V p - p, R_L = 2 k\Omega$                                                                    |                  | 16                   |      | kHz    |

| Slew Rate, Unity Gain                     | $V_0 = 20 \text{ V p-p}, R_L = 2 \text{ k}\Omega$<br>$V_0 = 20 \text{ V p-p}, R_L = 2 \text{ k}\Omega$ |                  | 10                   |      | V/µs   |

| SETTLING TIME <sup>3</sup>                | V0 = 20 V p p, n_ = 2 M2                                                                               |                  | Į                    |      | v/µ5   |

| To 0.1%                                   | 10 V step                                                                                              |                  | 10                   |      | 110    |

| To 0.01%                                  | 10 V step                                                                                              |                  | 10                   |      | μs     |

|                                           | 50% overdrive                                                                                          |                  |                      |      | μs     |

| Overload Recovery⁴<br>Total Harmonic      | f = 1  kHz                                                                                             |                  | 2                    |      | μs     |

|                                           |                                                                                                        |                  | 100                  |      | م ہے   |

|                                           | $R1 \ge 10 \text{ k}\Omega, V_0 = 3 \text{ V rms}$                                                     |                  | -108                 |      | dB     |

| INPUT IMPEDANCE                           | V 11V                                                                                                  |                  | 1012112              |      |        |

| Differential                              | $V_{DIFF} = \pm 1 V$                                                                                   |                  | 10 <sup>12</sup>   2 |      | Ω  pF  |

|                                           |                                                                                                        |                  | 1014  2.2            |      | Ω∥pF   |

| INPUT VOLTAGE RANGE                       |                                                                                                        |                  | . 20                 |      |        |

| Differential <sup>5</sup>                 |                                                                                                        |                  | ±20                  |      | V      |

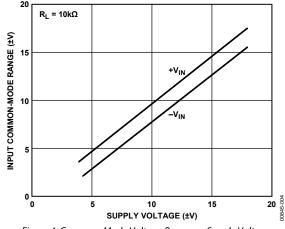

| Common-Mode Voltage                       |                                                                                                        | ±10              | ±11                  |      | V      |

| Over Maximum Operating Temperature        |                                                                                                        | ±10              |                      |      | V      |

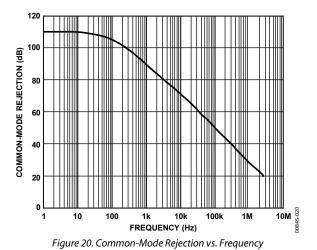

| Common-Mode Rejection Ratio               | $V_{CM} = \pm 10 V$                                                                                    | 90               | 110                  |      | dB     |

|                                           | T <sub>MIN</sub> – T <sub>MAX</sub>                                                                    | 86               | 100                  |      | dB     |

| OUTPUT CHARACTERISTICS                    |                                                                                                        |                  |                      |      |        |

| Voltage                                   | $R_{L} \ge 2 \ k\Omega$                                                                                | $V_{\rm S}-4$    | Vs – 2.5             |      | V      |

|                                           | $T_{MIN} - T_{MAX}$                                                                                    | $V_{\text{S}}-4$ |                      |      | V      |

| Current                                   | $V_{OUT} = \pm 10 V$                                                                                   | ±5               | ±10                  |      | mA     |

|                                           | Short circuit                                                                                          |                  | ±15                  |      | mA     |

|                   |                                 | AD795JR |     |     |      |

|-------------------|---------------------------------|---------|-----|-----|------|

| Parameter         | <b>Test Conditions/Comments</b> | Min     | Тур | Max | Unit |

| POWER SUPPLY      |                                 |         |     |     |      |

| Rated Performance |                                 |         | ±15 |     | V    |

| Operating Range   |                                 | ±4      |     | ±18 | V    |

| Quiescent Current |                                 |         | 1.3 | 1.5 | mA   |

<sup>1</sup> Input offset voltage specifications are guaranteed after 5 minutes of operation at  $T_A = +25^{\circ}$ C. <sup>2</sup> Bias current specifications are guaranteed maximum at either input after 5 minutes of operation at  $T_A = +25^{\circ}$ C. For higher temperature, the current doubles every 10°C. <sup>3</sup> Gain = -1, R1 = 10 k $\Omega$ .

<sup>4</sup> Defined as the time required for the amplifier's output to return to normal operation after removal of a 50% overload from the amplifier input. <sup>5</sup> Defined as the maximum continuous voltage between the inputs such that neither input exceeds ±10 V from ground.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                                             | Rating            |

|-------------------------------------------------------|-------------------|

| Supply Voltage                                        | ±18 V             |

| Internal Power Dissipation (at $T_A = +25^{\circ}C$ ) |                   |

| SOIC Package                                          | 500 mW            |

| Input Voltage                                         | ±Vs               |

| Input Current <sup>1</sup>                            | ±10 mA            |

| Output Short-Circuit Duration                         | Indefinite        |

| Differential Input Voltage                            | $+V_s$ and $-V_s$ |

| Storage Temperature Range (R)                         | –65°C to +125°C   |

| Operating Temperature Range                           |                   |

| AD795J                                                | 0°C to +70°C      |

$^{1}$  Limit input current to 10 mA or less whenever the input signal exceeds the power supply rail by 0.1 V.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered on a 4-layer circuit board for surface-mount packages.

#### Table 3. Thermal Resistance

| Package Type | θ <sub>JA</sub> | Unit |

|--------------|-----------------|------|

| 8-Lead SOIC  | 155             | °C/W |

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

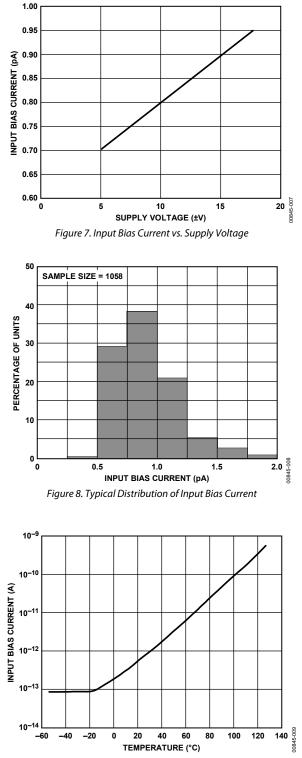

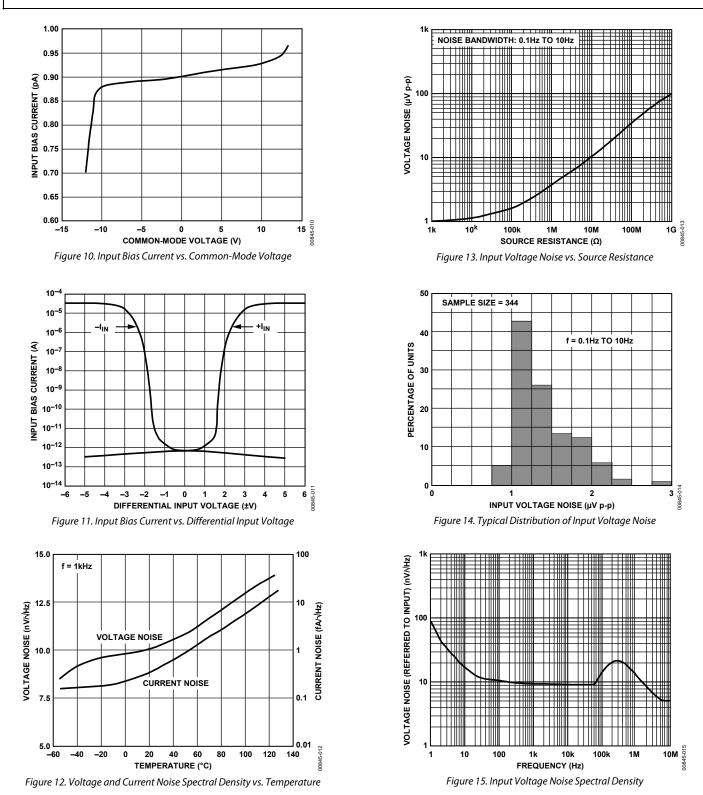

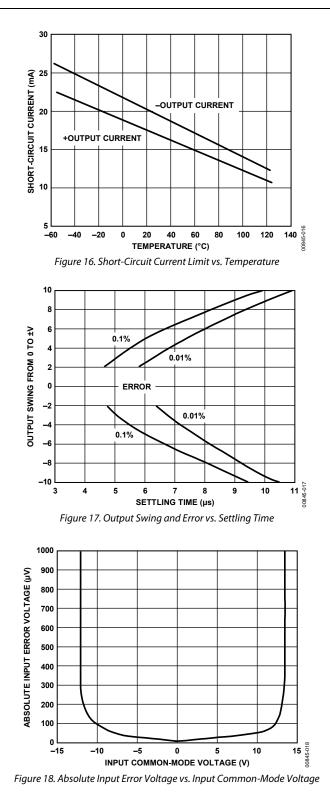

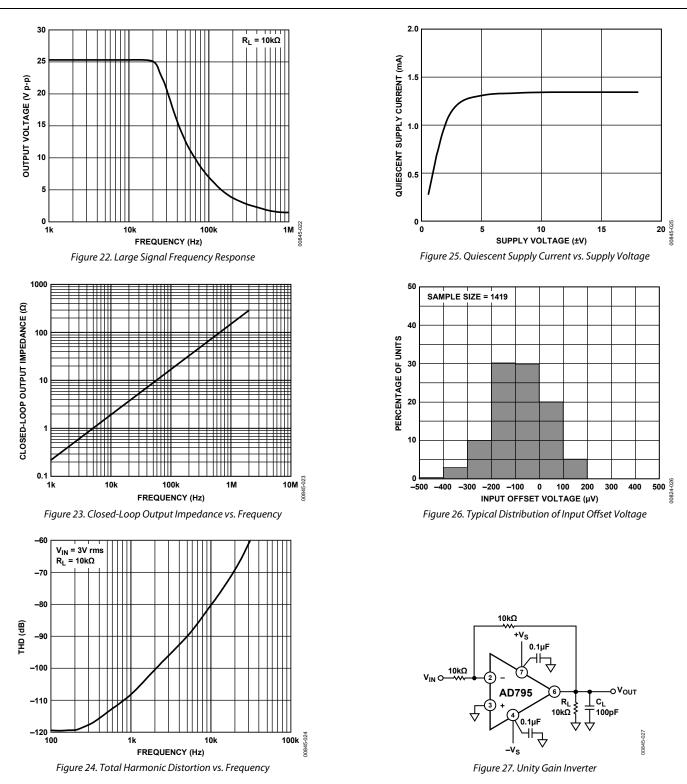

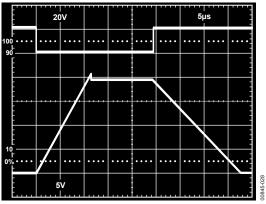

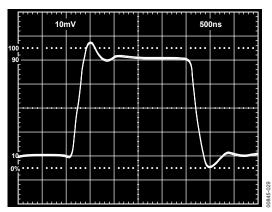

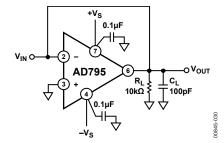

### **TYPICAL PERFORMANCE CHARACTERISTICS**

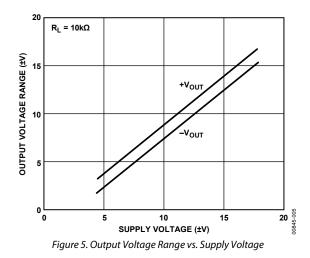

Figure 4. Common-Mode Voltage Range vs. Supply Voltage

Figure 6. Output Voltage Swing vs. Load Resistance

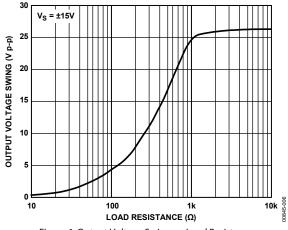

Figure 9. Input Bias Current vs. Temperature

Figure 21. Open-Loop Gain and Phase Margin vs. Frequency

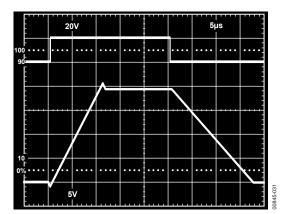

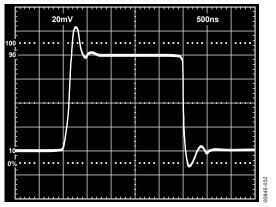

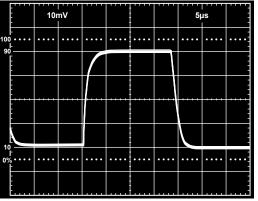

Figure 28. Unity Gain Inverter Large Signal Pulse Response

Figure 29. Unity Gain Inverter Small Signal Pulse Response

Figure 30. Unity Gain Follower

Figure 31. Unity Gain Follower Large Signal Pulse Response

Figure 32. Unity Gain Follower Small Signal Pulse Response

### **MINIMIZING INPUT CURRENT**

The AD795 is guaranteed to 1 pA maximum input current with  $\pm 15$  V supply voltage at room temperature. Careful attention to how the amplifier is used is necessary to maintain this performance.

The amplifier's operating temperature should be kept as low as possible. Like other JFET input amplifiers, the AD795's input current doubles for every 10°C rise in junction temperature

(illustrated in Figure 9). On-chip power dissipation raises the device operating temperature, causing an increase in input current. Reducing supply voltage to cut power dissipation reduces the AD795's input current (see Figure 7). Heavy output loads can also increase junction temperature; maintaining a minimum load resistance of 10 k $\Omega$  is recommended.

### **CIRCUIT BOARD NOTES**

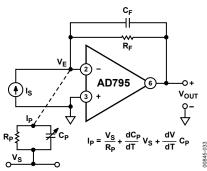

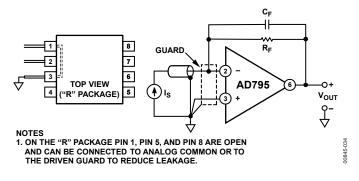

The AD795 is designed for mounting on printed circuit boards (PCBs). Maintaining picoampere resolution in those environments requires a lot of care. Both the board and the amplifier's package have finite resistance. Voltage differences between the input pins and other pins as well as PCB metal traces causes parasitic currents (see Figure 33) larger than the AD795's input current unless special precautions are taken. Two methods of minimizing parasitic leakages include guarding of the input lines and maintaining adequate insulation resistance.

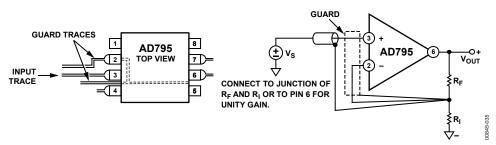

Figure 34 and Figure 35 show the recommended guarding schemes for noninverting and inverting topologies. Pin 1 is not connected, and can be safely connected to the guard. The high impedance input trace should be guarded on both edges for its entire length.

Figure 33. Sources of Parasitic Leakage Currents

Figure 34. Guarding Scheme—Inverter

Figure 35. Guard Scheme—Follower

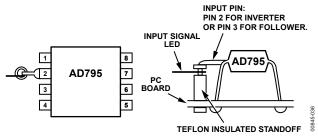

Leakage through the bulk of the circuit board can still occur with the guarding schemes shown in Figure 34 and Figure 35. Standard G10 type PCB material may not have high enough volume resistivity to hold leakages at the sub-picoampere level particularly under high humidity conditions. One option that eliminates all effects of board resistance is shown in Figure 36. The AD795's sensitive input pin (either Pin 2 when connected as an inverter, or Pin 3 when connected as a follower) is bent up and soldered directly to a Teflon<sup>®</sup> insulated standoff. Both the signal input and feedback component leads must also be insulated from the circuit board by Teflon standoffs or low leakage shielded cable.

Figure 36. Input Pin to Insulating Standoff

Contaminants such as solder flux on the board's surface and on the amplifier's package can greatly reduce the insulation resistance between the input pin and those traces with supply or signal voltages. Both the package and the board must be kept clean and dry. An effective cleaning procedure is to first swab the surface with high grade isopropyl alcohol, then rinse it with deionized water and, finally, bake it at 100°C for 1 hour. Polypropylene and polystyrene capacitors should not be subjected to the 100°C bake because they can be damaged at temperatures greater than 80°C.

Other guidelines include making the circuit layout as compact as possible and reducing the length of input lines. Keeping circuit board components rigid and minimizing vibration reduce triboelectric and piezoelectric effects. All precision high impedance circuitry requires shielding from electrical noise and interference. For example, a ground plane should be used under all high value (that is, greater than 1 M $\Omega$ ) feedback resistors. In some cases, a shield placed over the resistors, or even the entire amplifier, may be needed to minimize electrical interference originating from other circuits. Referring to the equation in Figure 33, this coupling can take place in either, or both, of two different forms via time varying fields:

$$\frac{dV}{dT}C_P$$

or by injection of parasitic currents by changes in capacitance due to mechanical vibration:

$$\frac{dCp}{dT}V$$

Both proper shielding and rigid mechanical mounting of components help minimize error currents from both of these sources.

#### **OFFSET NULLING**

The circuit in Figure 37 can be used when the amplifier is used as an inverter. This method introduces a small voltage in series with the amplifier's positive input terminal. The amplifier's input offset voltage drift with temperature is not affected. However, variation of the power supply voltages causes offset shifts.

Figure 37. Alternate Offset Null Circuit for Inverter

## AC RESPONSE WITH HIGH VALUE SOURCE AND FEEDBACK RESISTANCE

Source and feedback resistances greater than  $100 \text{ k}\Omega$  magnifies the effect of input capacitances (stray and inherent to the AD795) on the ac behavior of the circuit. The effects of common-mode and differential input capacitances should be taken into account because the circuit's bandwidth and stability can be adversely affected.

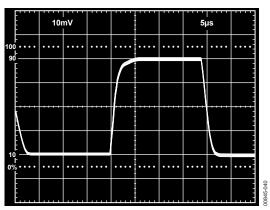

In a follower, the source resistance, Rs, and input commonmode capacitance, Cs (including capacitance due to board and capacitance inherent to the AD795), form a pole that limits circuit bandwidth to  $1/2 \pi$  RsCs. Figure 38 shows the follower pulse response from a 1 M $\Omega$  source resistance with the amplifier's input pin isolated from the board; only the effect of the AD795's input common-mode capacitance is seen.

Figure 38. Follower Pulse Response from 1  $M\Omega$  Source Resistance

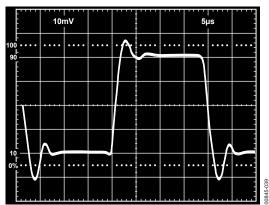

In an inverting configuration, the differential input capacitance forms a pole in the circuit's loop transmission. This can create peaking in the ac response and possible instability. A feedback capacitance can be used to stabilize the circuit. The inverter pulse response with  $R_F$  and  $R_S$  equal to 1 M $\Omega$  and the input pin isolated from the board appears in Figure 39. Figure 40 shows the response of the same circuit with a 1 pF feedback capacitance. Typical differential input capacitance for the AD795 is 2 pF.

Figure 39. Inverter Pulse Response with 1  $M\Omega$  Source and Feedback Resistance

Figure 40. Inverter Pulse Response with 1 M $\Omega$  Source and Feedback Resistance, 1 pF Feedback Capacitance

### **OVERLOAD ISSUES**

Driving the amplifier output beyond its linear region causes some sticking; recovery to normal operation is within 2  $\mu$ s of the input voltage returning within the linear range.

If either input is driven below the negative supply, the amplifier's output is driven high, causing a phenomenon called phase reversal. Normal operation is resumed within 30  $\mu$ s of the input voltage returning within the linear range.

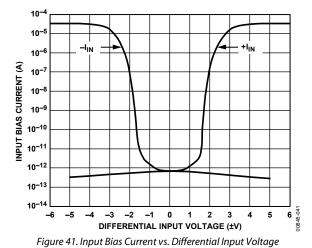

Figure 41 shows the AD795's input bias currents vs. differential input voltage. Picoamp level input current is maintained for differential voltages up to several hundred millivolts. This behavior is only important if the AD795 is in an open-loop application where substantial differential voltages are produced.

### INPUT PROTECTION

The AD795 safely handles any input voltage within the supply voltage range. Some applications may subject the input terminals to voltages beyond the supply voltages. In these cases, the following guidelines should be used to maintain the AD795's functionality and performance.

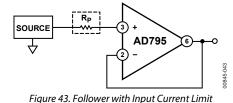

If the inputs are driven more than a 0.5 V below the minus supply, milliamp level currents can be produced through the input terminals. That current should be limited to 10 mA for transient overloads (less than 1 second) and 1 mA for continuous overloads. This can be accomplished with a protection resistor in the input terminal (as shown in Figure 42 and Figure 43). The protection resistor's Johnson noise adds to the amplifier's input voltage noise and impacts the frequency response.

Driving the input terminals above the positive supply causes the input current to increase and limit at 40  $\mu$ A. This condition is maintained until 15 V above the positive supply—any input voltage within this range does not harm the amplifier. Input voltage above this range causes destructive breakdown and should be avoided.

Figure 42. Inverter with Input Current Limit

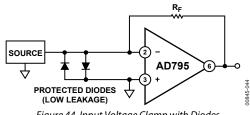

Figure 44 is a schematic of the AD795 as an inverter with an input voltage clamp. Bootstrapping the clamp diodes at the inverting input minimizes the voltage across the clamps and keeps the leakage due to the diodes low. Low leakage diodes (less than 1 pA), such as the FD333s should be used, and should be shielded from light to keep photocurrents from being generated. Even with these precautions, the diodes measurably increase the input current and capacitance.

To achieve the low input bias currents of the AD795, it is not possible to use the same on-chip protection as used in other Analog Devices, Inc., op amps. This makes the AD795 sensitive to handling and precautions should be taken to minimize ESD exposure whenever possible.

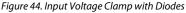

Figure 45. AD795 Used as a Photodiode Preamplifier

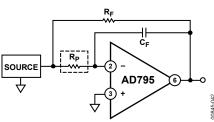

#### **PREAMPLIFIER APPLICATIONS**

The low input current and offset voltage levels of the AD795 together with its low voltage noise make this amplifier an excellent choice for preamplifiers used in sensitive photodiode applications. In a typical preamp circuit, shown in Figure 45, the output of the amplifier is equal to:

$$V_{OUT} = I_D (Rf) = Rp (P) Rf$$

where:

I

I<sub>D</sub> is the photodiode signal current, in amps (A). Rp is the photodiode sensitivity, in amps/watt (A/W). Rf is the value of the feedback resistor, in ohms ( $\Omega$ ). P is the light power incident to photodiode surface, in watts (W).

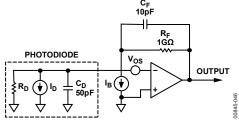

An equivalent model for a photodiode and its dc error sources is shown in Figure 46. The amplifier's input current,  $I_B$ , contributes an output voltage error, which is proportional to the value of the feedback resistor. The offset voltage error,  $V_{os}$ , causes a dark current error due to the photodiode's finite shunt resistance, Rd. The resulting output voltage error,  $V_E$ , is equal to:

$V_E = (1 + Rf/Rd) V_{OS} + Rf I_B$

A shunt resistance on the order of  $10^{9} \Omega$  is typical for a small photodiode. Resistance Rd is a junction resistance, which typically drops by a factor of two for every 10°C rise in temperature. In the AD795, both the offset voltage and drift are low, which helps minimize these errors.

Figure 46. A Photodiode Model Showing DC Error Sources

#### **MINIMIZING NOISE CONTRIBUTIONS**

The noise level limits the resolution obtainable from any preamplifier. The total output voltage noise divided by the feedback resistance of the op amp defines the minimum detectable signal current. The minimum detectable current divided by the photodiode sensitivity is the minimum detectable light power.

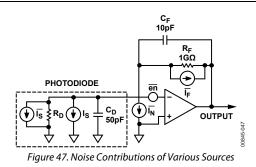

Sources of noise in a typical preamp are shown in Figure 47. The total noise contribution is defined as:

$$\overline{V_{OUT}} = \sqrt{\left(\overline{in}^2 + \overline{if}^2 + \overline{is}^2\right)^2 \left(\frac{Rf}{1 + s(Cf)Rf}\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\left(\frac{(1 + s(Cd)Rd}{1 + s(Cf)Rf}\right)\right)^2\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\right)\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\right)\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\right)\right)^2 + \left(\overline{en}^2 \left(1 + \frac{Rf}{Rd}\right)^2 + \left(\overline{$$

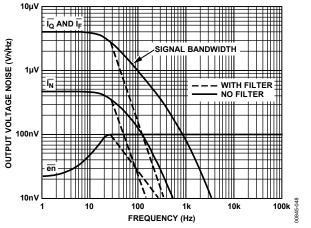

Figure 48, a spectral density vs. frequency plot of each source's noise contribution, shows that the bandwidth of the amplifier's input voltage noise contribution is much greater than its signal bandwidth. In addition, capacitance at the summing junction results in a peaking of noise gain in this configuration. This effect can be substantial when large photodiodes with large shunt capacitances are used. Capacitor Cf sets the signal bandwidth and limits the peak in the noise gain. Each source's rms or root-sum-square contribution to noise is obtained by integrating the sum of the squares of all the noise sources and then by obtaining the square root of this sum. Minimizing the total area under these curves optimizes the preamplifier's overall noise performance.

An output filter with a passband close to that of the signal can greatly improve the preamplifier's signal to noise ratio. The photodiode preamplifier shown in Figure 47, without a bandpass filter, has a total output noise of 50  $\mu$ V rms. Using a 26 Hz single-pole output filter, the total output noise drops to 23  $\mu$ V rms, a factor of 2 improvement with no loss in signal bandwidth.

Figure 48. Voltage Noise Spectral Density of the Circuit of Figure 47 With and Without an Output Filter

#### **USING A T NETWORK**

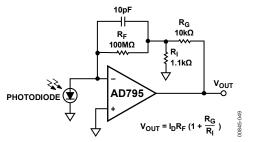

A T network, shown in Figure 49, can be used to boost the effective transimpedance of an I-to-V converter, for a given feedback resistor value. However, amplifier noise and offset voltage contributions are also amplified by the T network gain. A low noise, low offset voltage amplifier, such as the AD795, is needed for this type of application.

Figure 49. Photodiode Preamp Employing a T Network for Added Gain

#### A **bH PROBE BUFFER AMPLIFIER**

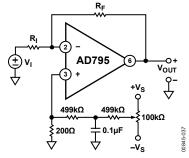

A typical pH probe requires a buffer amplifier, shown in Figure 50, to isolate its  $10^6 \Omega$  to  $10^9 \Omega$  source resistance from external circuitry. The low input current of the AD795 allows the voltage error produced by the bias current and electrode resistance to be minimal. The use of guarding, shielding, high insulation resistance standoffs, and other such standard methods used to

minimize leakage are all needed to maintain the accuracy of this circuit.

The slope of the pH probe transfer function, 50 mV per pH unit at room temperature, has a 3300 ppm/°C temperature coefficient. The buffer of Figure 50 provides an output voltage equal to 1 V/pH unit. Temperature compensation is provided by resistor RT, which is a special temperature compensation resistor, Part Number Q81, 1 k $\Omega$ , 1%, 3500 ppm/°C, available from Tel Labs, Inc.

Figure 50. pH Probe Amplifier

### **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description | Package Option |

|--------------------|-------------------|---------------------|----------------|

| AD795JR            | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| AD795JR-REEL       | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| AD795JR-REEL7      | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| AD795JRZ           | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| AD795JRZ-REEL      | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

| AD795JRZ-REEL7     | 0°C to +70°C      | 8-Lead SOIC_N       | R-8            |

<sup>1</sup> Z= RoHS Compliant Part.

## NOTES

## NOTES

©2002-2009 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D00845-0-12/09(C)

Rev. C | Page 20 of 20

www.analog.com