# 2.5 $\Omega$ , 1.8 V to 5.5 V, ±2.5 V Triple/Quad SPDT Switches in Chip Scale Packages

## ADG786/ADG788

#### **FEATURES**

1.8 V to 5.5 V Single Supply  $\pm 2.5$  V Dual Supply 2.5  $\Omega$  On Resistance 0.5  $\Omega$  On Resistance Flatness 100 pA Leakage Currents 19 ns Switching Times Triple SPDT: ADG786 Quad SPDT: ADG788 20-Lead 4 mm × 4 mm Chip Scale Packages Low Power Consumption TTL/CMOS-Compatible Inputs For Functionally-Equivalent Devices in 16-Lead TSSOP Packages, See ADG733/ADG734 Qualified for automotive applications

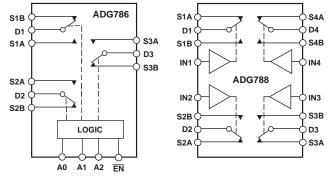

#### FUNCTIONAL BLOCK DIAGRAMS

SWITCHES SHOWN FOR A LOGIC "1" INPUT

#### APPLICATIONS Data Acquisition Systems

Communication Systems Relay Replacement Audio and Video Switching Battery-Powered Systems

#### **GENERAL DESCRIPTION**

The ADG786 and ADG788 are low voltage, CMOS devices comprising three independently selectable SPDT (single pole, double throw) switches and four independently selectable SPDT switches respectively.

Low power consumption and operating supply range of 1.8 V to 5.5 V and dual  $\pm 2.5$  V make the ADG786 and ADG788 ideal for battery powered, portable instruments and many other applications. All channels exhibit break-before-make switching action preventing momentary shorting when switching channels. An  $\overline{\rm EN}$  input on the ADG786 is used to enable or disable the device. When disabled, all channels are switched OFF.

These multiplexers are designed on an enhanced submicron process that provides low power dissipation yet gives high switching speed, very low on resistance, high signal bandwidths and low leakage currents. On resistance is in the region of a few ohms, is closely matched between switches and very flat over the full signal range. These parts can operate equally well in either direction and have an input signal range which extends to the supplies.

The ADG786 and ADG788 are available in small 20-lead chip scale packages.

#### **PRODUCT HIGHLIGHTS**

- 1. Small 20-Lead 4 mm  $\times$  4 mm Chip Scale Packages (CSP).

- 2. Single/Dual Supply Operation. The ADG786 and ADG788 are fully specified and guaranteed with 3 V  $\pm$  10% and 5 V  $\pm$  10% single supply rails, and  $\pm$ 2.5 V  $\pm$  10% dual supply rails.

- 3. Low On Resistance (2.5  $\Omega$  typical).

- 4. Low Power Consumption (<0.01  $\mu$ W).

- 5. Guaranteed Break-Before-Make Switching Action.

Rev. C

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2001–2015 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## $\label{eq:additional} ADG786/ADG788-SPECIFICATIONS^{1} (V_{DD} = 5 \ \text{V} \pm 10\%, \ \text{V}_{SS} = 0 \ \text{V}, \ \text{GND} = 0 \ \text{V}, \ \text{unless otherwise noted.})$

|                                                         | B V       | ersion                 |              |                                                                     |

|---------------------------------------------------------|-----------|------------------------|--------------|---------------------------------------------------------------------|

| Parameter                                               | +25°C     | -40°C<br>to +85°C      | Unit         | Test Conditions/Comments                                            |

| ANALOG SWITCH                                           |           |                        |              |                                                                     |

| Analog Signal Range                                     |           | 0 V to V <sub>DD</sub> | V            |                                                                     |

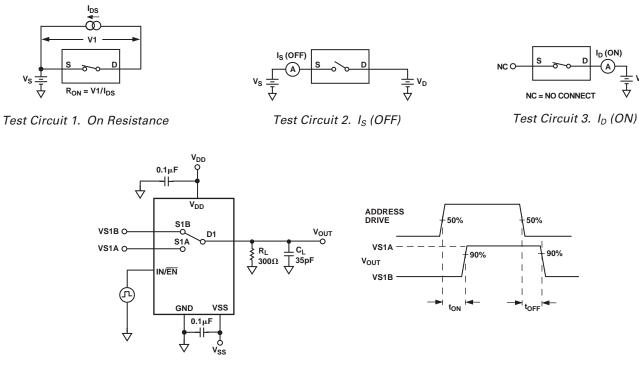

| On Resistance (R <sub>ON</sub> )                        | 2.5       | 55                     | Ω typ        | $V_{S} = 0 V$ to $V_{DD}$ , $I_{DS} = 10 mA$ ;                      |

|                                                         | 4.5       | 5.0                    | $\Omega$ max | Test Circuit 1                                                      |

| On-Resistance Match between                             |           | 0.1                    | Ω typ        | $V_{S} = 0 V$ to $V_{DD}$ , $I_{DS} = 10 mA$                        |

| Channels ( $\Delta R_{ON}$ )                            |           | 0.4                    | $\Omega$ max |                                                                     |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> )         | 0.5       |                        | Ω typ        | $V_{S} = 0 V$ to $V_{DD}$ , $I_{DS} = 10 mA$                        |

|                                                         |           | 1.2                    | $\Omega$ max |                                                                     |

| LEAKAGE CURRENTS                                        |           |                        |              | $V_{DD} = 5.5 V$                                                    |

| Source OFF Leakage I <sub>S</sub> (OFF)                 | ±0.01     |                        | nA typ       | $V_D = 4.5 \text{ V}/1 \text{ V}, V_S = 1 \text{ V}/4.5 \text{ V};$ |

| -                                                       | ±0.1      | $\pm 0.3$              | nA max       | Test Circuit 2                                                      |

| Channel ON Leakage I <sub>D</sub> , I <sub>S</sub> (ON) | ±0.01     |                        | nA typ       | $V_D = V_S = 1 V$ , or 4.5 V;                                       |

|                                                         | $\pm 0.1$ | $\pm 0.5$              | nA max       | Test Circuit 3                                                      |

| DIGITAL INPUTS                                          |           |                        |              |                                                                     |

| Input High Voltage, V <sub>INH</sub>                    |           | 2.4                    | V min        |                                                                     |

| Input Low Voltage, V <sub>INL</sub>                     |           | 0.8                    | V max        |                                                                     |

| Input Current                                           |           |                        |              |                                                                     |

| I <sub>INL</sub> or I <sub>INH</sub>                    | 0.005     |                        | μA typ       | $V_{IN} = V_{INL}$ or $V_{INH}$                                     |

|                                                         |           | $\pm 0.1$              | µA max       |                                                                     |

| C <sub>IN</sub> , Digital Input Capacitance             | 4         |                        | pF typ       |                                                                     |

| DYNAMIC CHARACTERISTICS <sup>2</sup>                    |           |                        |              |                                                                     |

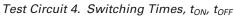

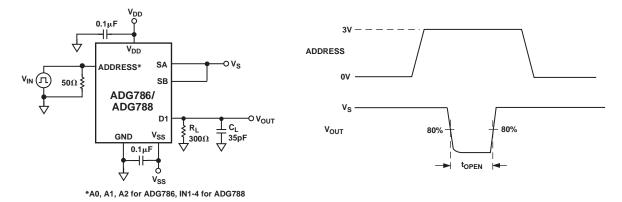

| t <sub>ON</sub>                                         | 19        |                        | ns typ       | $R_L = 300 \ \Omega, \ C_L = 35 \ pF;$                              |

|                                                         |           | 34                     | ns max       | $V_{S1A} = 3 V$ , $V_{S1B} = 0 V$ , Test Circuit 4                  |

| t <sub>OFF</sub>                                        | 7         |                        | ns typ       | $R_L = 300 \Omega, C_L = 35 pF;$                                    |

|                                                         |           | 12                     | ns max       | $V_{\rm S} = 3$ V, Test Circuit 4                                   |

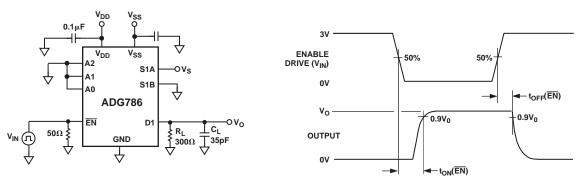

| ADG786 $t_{ON}(\overline{EN})$                          | 20        |                        | ns typ       | $R_L = 300 \Omega, C_L = 35 pF;$                                    |

|                                                         |           | 40                     | ns max       | $V_{\rm S} = 3$ V, Test Circuit 5                                   |

| $t_{OFF}(\overline{EN})$                                | 7         | 10                     | ns typ       | $R_L = 300 \Omega, C_L = 35 pF;$                                    |

| Ducal Defens Male The Delay                             | 10        | 12                     | ns max       | $V_S = 3 V$ , Test Circuit 5                                        |

| Break-Before-Make Time Delay, $t_D$                     | 13        | 1                      | ns typ       | $R_L = 300 \Omega$ , $C_L = 35 pF$ ;                                |

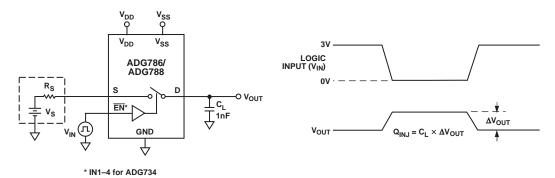

| Charge Injection                                        | + 2       | 1                      | ns min       | $V_{\rm S} = 3$ V, Test Circuit 6                                   |

| Charge Injection                                        | ±3        |                        | pC typ       | $V_S = 2 V, R_S = 0 \Omega, C_L = 1 nF;$<br>Test Circuit 7          |

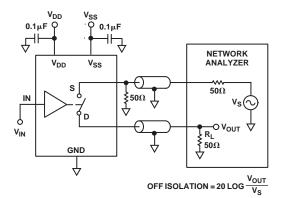

| Off Isolation                                           | -80       |                        | dB typ       | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;                    |

|                                                         | -00       |                        | un tyh       | $R_L = 30.32, C_L = 3. pr^2, r = 1. Wi112,$<br>Test Circuit 8       |

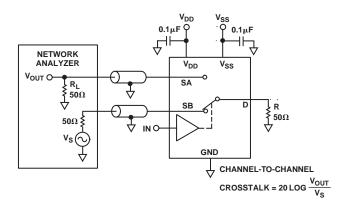

| Channel-to-Channel Crosstalk                            | -80       |                        | dB typ       | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;                    |

|                                                         |           |                        | J I          | Test Circuit 9                                                      |

| -3 dB Bandwidth                                         | 160       |                        | MHz typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , Test Circuit 10                  |

| C <sub>s</sub> (OFF)                                    | 11        |                        | pF typ       | f = 1 MHz                                                           |

| $C_{\rm D}, C_{\rm S}$ (ON)                             | 34        |                        | pF typ       | f = 1 MHz                                                           |

| POWER REQUIREMENTS                                      |           |                        |              | $V_{DD} = 5.5 V$                                                    |

| I <sub>DD</sub>                                         | 0.001     |                        | μA typ       | Digital Inputs = 0 V or 5.5 V                                       |

|                                                         |           | 1.0                    | µA max       |                                                                     |

NOTES <sup>1</sup>Temperature range is as follows: B Version:  $-40^{\circ}$ C to  $+85^{\circ}$ C. <sup>2</sup>Guaranteed by design, not subject to production test.

Specifications subject to change without notice.

$SPECIFICATIONS^{1} (V_{DD} = 3 V \pm 10\%, V_{SS} = 0 V, GND = 0 V, unless otherwise noted.)$

|                                                         | B Ve    | ersion<br>-40°C           |              |                                                                                             |

|---------------------------------------------------------|---------|---------------------------|--------------|---------------------------------------------------------------------------------------------|

| Parameter                                               | +25°C   | to +85°C                  | Unit         | Test Conditions/Comments                                                                    |

| ANALOG SWITCH                                           |         |                           |              |                                                                                             |

| Analog Signal Range                                     |         | $0 \text{ V}$ to $V_{DD}$ | V            |                                                                                             |

| On Resistance (R <sub>ON</sub> )                        | 6       |                           | Ω typ        | $V_{S} = 0 V$ to $V_{DD}$ , $I_{DS} = 10 mA$ ;                                              |

|                                                         | 11      | 12                        | $\Omega$ max | Test Circuit 1                                                                              |

| On-Resistance Match between                             |         | 0.1                       | Ω typ        | $V_{\rm S} = 0$ V to $V_{\rm DD}$ , $I_{\rm DS} = 10$ mA                                    |

| Channels ( $\Delta R_{ON}$ )                            |         | 0.5                       | $\Omega$ max |                                                                                             |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> )         |         | 3                         | Ω typ        | $V_{\rm S}$ = 0 V to $V_{\rm DD}$ , $I_{\rm DS}$ = 10 mA                                    |

| LEAKAGE CURRENTS                                        |         |                           |              | $V_{DD} = 3.3 V$                                                                            |

| Source OFF Leakage I <sub>S</sub> (OFF)                 | ±0.01   |                           | nA typ       | $V_{\rm S} = 3 \text{ V}/1 \text{ V}, V_{\rm D} = 1 \text{ V}/3 \text{ V};$                 |

|                                                         | ±0.1    | $\pm 0.3$                 | nA max       | Test Circuit 2                                                                              |

| Channel ON Leakage I <sub>D</sub> , I <sub>S</sub> (ON) | ±0.01   |                           | nA typ       | $V_{\rm S} = V_{\rm D} = 1 \text{ V or } 3 \text{ V};$                                      |

|                                                         | ±0.1    | $\pm 0.5$                 | nA max       | Test Circuit 3                                                                              |

| DIGITAL INPUTS                                          |         |                           |              |                                                                                             |

| Input High Voltage, V <sub>INH</sub>                    |         | 2.0                       | V min        |                                                                                             |

| Input Low Voltage, V <sub>INL</sub>                     |         | 0.8                       | V max        |                                                                                             |

| Input Current                                           |         |                           |              |                                                                                             |

| I <sub>INL</sub> or I <sub>INH</sub>                    | 0.005   |                           | μA typ       | $V_{IN} = V_{INL}$ or $V_{INH}$                                                             |

|                                                         |         | $\pm 0.1$                 | μA max       |                                                                                             |

| C <sub>IN</sub> , Digital Input Capacitance             | 4       |                           | pF typ       |                                                                                             |

| DYNAMIC CHARACTERISTICS <sup>2</sup>                    |         |                           |              |                                                                                             |

| t <sub>ON</sub>                                         | 28      |                           | ns typ       | $R_L = 300 \Omega, C_L = 35 pF;$                                                            |

|                                                         |         | 55                        | ns max       | $V_{S1A} = 2 V$ , $V_{S1B} = 0 V$ , Test Circuit 4                                          |

| t <sub>OFF</sub>                                        | 9       |                           | ns typ       | $R_L = 300 \Omega$ , $C_L = 35 pF$ ;                                                        |

|                                                         |         | 16                        | ns max       | $V_S = 2 V$ , Test Circuit 4                                                                |

| ADG786 $t_{ON}(\overline{EN})$                          | 29      |                           | ns typ       | $R_L = 300 \Omega$ , $C_L = 35 pF$ ;                                                        |

|                                                         |         | 60                        | ns max       | $V_S = 2 V$ , Test Circuit 5                                                                |

| $t_{OFF}(\overline{EN})$                                | 9       |                           | ns typ       | $R_L = 300 \Omega, C_L = 35 pF;$                                                            |

|                                                         |         | 16                        | ns max       | $V_S = 2 V$ , Test Circuit 5                                                                |

| Break-Before-Make Time Delay, $t_D$                     | 22      |                           | ns typ       | $R_{L} = 300 \Omega, C_{L} = 35 pF;$                                                        |

|                                                         |         | 1                         | ns min       | $V_{\rm S} = 2$ V, Test Circuit 6                                                           |

| Charge Injection                                        | $\pm 3$ |                           | pC typ       | $V_{\rm S} = 1 \text{ V},  \text{R}_{\rm S} = 0  \Omega,  \text{C}_{\rm L} = 1  \text{nF};$ |

| Off Isolation                                           | 80      |                           | dD tree      | Test Circuit 7<br>$P_{r} = 50 \Omega_{r} C_{r} = 5 pE_{r} f = 1 MHz$                        |

| UII ISOIAUOII                                           | -80     |                           | dB typ       | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;<br>Test Circuit 8                          |

| Channel-to-Channel Crosstalk                            | -80     |                           | dB typ       | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;                                            |

| Chamier-to-Chamier Crosstark                            | -00     |                           | up typ       | Test Circuit 9                                                                              |

| -3 dB Bandwidth                                         | 160     |                           | MHz typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , Test Circuit 10                                          |

| C <sub>S</sub> (OFF)                                    | 11      |                           | pF typ       | f = 1  MHz                                                                                  |

| $C_D, C_S$ (ON)                                         | 34      |                           | pF typ       | f = 1 MHz                                                                                   |

| POWER REQUIREMENTS                                      |         |                           |              | $V_{DD} = 3.3 \text{ V}$                                                                    |

| I <sub>DD</sub>                                         | 0.001   |                           | μA typ       | Digital Inputs = $0 \text{ V or } 3.3 \text{ V}$                                            |

| עע                                                      |         | 1.0                       | $\mu A max$  | 0                                                                                           |

NOTES

<sup>1</sup>Temperature ranges are as follows: B Version: -40 °C to +85 °C. <sup>2</sup>Guaranteed by design, not subject to production test.

Specifications subject to change without notice.

## ADG786/ADG788-SPECIFICATIONS<sup>1</sup>

DUAL SUPPLY ( $V_{DD}$  = +2.5 V ± 10%,  $V_{SS}$  = -2.5 V ± 10%, GND = 0 V, unless otherwise noted.)

|                                                         | B V                     | ersion                             |               |                                                                                            |

|---------------------------------------------------------|-------------------------|------------------------------------|---------------|--------------------------------------------------------------------------------------------|

| Parameter                                               | +25°C                   | -40°C<br>to +85°C                  | Unit          | Test Conditions/Comments                                                                   |

| ANALOG SWITCH                                           |                         |                                    |               |                                                                                            |

| Analog Signal Range                                     |                         | V <sub>SS</sub> to V <sub>DD</sub> | V             |                                                                                            |

| On Resistance (R <sub>ON</sub> )                        | 2.5                     | . 33                               | Ωtyp          | $V_{S} = V_{SS}$ to $V_{DD}$ , $I_{DS} = 10$ mA;                                           |

|                                                         | 4.5                     | 5.0                                | $\Omega \max$ | Test Circuit 1                                                                             |

| On-Resistance Match between                             | 1.0                     | 0.1                                | $\Omega$ typ  | $V_{\rm S} = V_{\rm SS}$ to $V_{\rm DD}$ , $I_{\rm DS} = 10$ mA                            |

| Channels ( $\Delta R_{ON}$ )                            |                         | 0.4                                | $\Omega \max$ | $V_{5} = V_{55} v_{0} v_{DD}, v_{D5} = v_{0} v_{0} v_{1}$                                  |

| On-Resistance Flatness ( $R_{FLAT(ON)}$ )               | 0.5                     | 0.1                                | $\Omega$ typ  | $V_{S} = V_{SS}$ to $V_{DD}$ , $I_{DS} = 10$ mA                                            |

| Off resistance Flatness (RFLAT(ON))                     | 0.0                     | 1.2                                | $\Omega \max$ | $V_{S} = V_{SS} V_{S} V_{DD}, V_{DS} = V_{O} V_{M} V_{DS}$                                 |

| LEAKAGE CURRENTS                                        |                         |                                    |               | $V_{DD} = +2.75 \text{ V}, V_{SS} = -2.75 \text{ V}$                                       |

| Source OFF Leakage I <sub>s</sub> (OFF)                 | ±0.01                   |                                    | nA typ        | $V_{\rm S} = +2.25 \text{ V/}-1.25 \text{ V}, V_{\rm D} = -1.25 \text{ V/}+2.25 \text{ V}$ |

| bource off Leanage is (011)                             | $\pm 0.01$<br>$\pm 0.1$ | $\pm 0.3$                          | nA max        | Test Circuit 2                                                                             |

| Channel ON Leakage I <sub>D</sub> , I <sub>S</sub> (ON) | ±0.01                   | ±0.0                               | nA typ        | $V_{\rm S} = V_{\rm D} = +2.25 \text{ V/}-1.25 \text{ V}$ , Test Circuit 3                 |

| Channel Old Leakage 1D, 15 (Old)                        | $\pm 0.01$<br>$\pm 0.1$ | $\pm 0.5$                          | nA max        | $v_{\rm S} = v_{\rm D} = + \omega \omega v_{\rm F} + 1.20 v_{\rm S}$ rest encure of        |

|                                                         | ±0.1                    | ±0.0                               | III Y IIIUX   |                                                                                            |

| DIGITAL INPUTS                                          |                         | 1 7                                |               |                                                                                            |

| Input High Voltage, V <sub>INH</sub>                    |                         | 1.7                                | V min         |                                                                                            |

| Input Low Voltage, V <sub>INL</sub>                     |                         | 0.7                                | V max         |                                                                                            |

| Input Current                                           | 0.007                   |                                    | <b>A</b> .    | <b>X</b> 7 <b>X</b> 7 <b>X</b> 7                                                           |

| I <sub>INL</sub> or I <sub>INH</sub>                    | 0.005                   |                                    | μA typ        | $V_{IN} = V_{INL}$ or $V_{INH}$                                                            |

|                                                         |                         | ±0.1                               | µA max        |                                                                                            |

| C <sub>IN</sub> , Digital Input Capacitance             | 4                       |                                    | pF typ        |                                                                                            |

| DYNAMIC CHARACTERISTICS <sup>2</sup>                    |                         |                                    |               |                                                                                            |

| t <sub>ON</sub>                                         | 21                      |                                    | ns typ        | $R_L = 300 \Omega, C_L = 35 pF;$                                                           |

|                                                         |                         | 35                                 | ns max        | $V_{S1A} = 1.5 V, V_{S1B} = 0 V, Test Circuit 4$                                           |

| t <sub>OFF</sub>                                        | 10                      |                                    | ns typ        | $R_L = 300 \Omega$ , $C_L = 35 pF$ ;                                                       |

|                                                         |                         | 16                                 | ns max        | $V_{\rm S} = 1.5$ V, Test Circuit 4                                                        |

| ADG786 $t_{ON}(\overline{EN})$                          | 21                      |                                    | ns typ        | $R_{L} = 300 \Omega, C_{L} = 35 pF;$                                                       |

|                                                         |                         | 40                                 | ns max        | $V_{\rm S} = 1.5$ V, Test Circuit 5                                                        |

| $t_{OFF}(\overline{EN})$                                | 10                      |                                    | ns typ        | $R_L = 300 \Omega$ , $C_L = 35 pF$ ;                                                       |

|                                                         |                         | 16                                 | ns max        | $V_{\rm S} = 1.5$ V, Test Circuit 5                                                        |

| Break-Before-Make Time Delay, t <sub>D</sub>            | 13                      |                                    | ns typ        | $R_L = 300 \Omega$ , $C_L = 35 pF$ ;                                                       |

|                                                         |                         | 1                                  | ns min        | $V_{\rm S} = 1.5$ V, Test Circuit 6                                                        |

| Charge Injection                                        | $\pm 5$                 |                                    | pC typ        | $V_{S} = 0 V, R_{S} = 0 \Omega, C_{L} = 1 nF;$                                             |

|                                                         |                         |                                    |               | Test Circuit 7                                                                             |

| Off Isolation                                           | -80                     |                                    | dB typ        | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;                                           |

|                                                         |                         |                                    | 01            | Test Circuit 8                                                                             |

| Channel-to-Channel Crosstalk                            | -80                     |                                    | dB typ        | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;                                           |

|                                                         |                         |                                    |               | Test Circuit 9                                                                             |

| -3 dB Bandwidth                                         | 160                     |                                    | MHz typ       | $R_L = 50 \Omega$ , $C_L = 5 pF$ , Test Circuit 10                                         |

| C <sub>S</sub> (OFF)                                    | 11                      |                                    | pF typ        | f = 1 MHz                                                                                  |

| $C_D, C_S$ (ON)                                         | 34                      |                                    | pF typ        | f = 1 MHz                                                                                  |

| POWER REQUIREMENTS                                      |                         |                                    |               | $V_{DD} = +2.75 \text{ V}$                                                                 |

| I <sub>DD</sub>                                         | 0.001                   |                                    | μA typ        | Digital Inputs = $0 \text{ V}$ or 2.75 V                                                   |

|                                                         | -                       | 1.0                                | $\mu A max$   |                                                                                            |

| I <sub>SS</sub>                                         | 0.001                   |                                    | μA typ        | $V_{SS} = -2.75 \text{ V}$                                                                 |

| -,1,1                                                   | 0.001                   | 1.0                                | $\mu A max$   | Digital Inputs = $0 \text{ V}$ or 2.75 V                                                   |

NOTES

<sup>1</sup>Temperature range is as follows: B Version: -40 °C to +85 °C. <sup>2</sup>Guaranteed by design, not subject to production test.

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| $(T_A = 25^{\circ}C \text{ unless otherwise noted})$                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$ to $V_{SS}$                                                                                                                                   |

| $V_{DD}$ to GND $\ldots \ldots \ldots$ |

| $V_{SS}$ to GND $\ldots$ +0.3 V to -3.5 V                                                                                                              |

| Analog Inputs <sup>2</sup> $V_{SS}$ – 0.3 V to $V_{DD}$ + 0.3 V or                                                                                     |

| 30 mA, Whichever Occurs First                                                                                                                          |

| Digital Inputs <sup>2</sup> $-0.3$ V to V <sub>DD</sub> + 0.3 V or                                                                                     |

| 30 mA, Whichever Occurs First                                                                                                                          |

| Peak Current, S or D 100 mA                                                                                                                            |

| (Pulsed at 1 ms, 10% Duty Cycle max)                                                                                                                   |

| Continuous Current, S or D 30 mA                                                                                                                       |

| Operating Temperature Range                                                                                                                            |

| Industrial (A, B Versions)40°C to +85°C                                                                                                                |

| Storage Temperature Range                    |

|----------------------------------------------|

| Junction Temperature 150°C                   |

| 20 Lead CSP, $\theta_{JA}$ Thermal Impedance |

| Lead Temperature, Soldering (10 sec) 300°C   |

| IR Reflow, Peak Temperature 220°C            |

| NOTES                                        |

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.

maximum rating may be applied at any one time. <sup>2</sup>Overvoltages at A, EN, IN, S, or D will be clamped by internal diodes. Current should be limited to the maximum ratings given.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADG786/ADG788 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

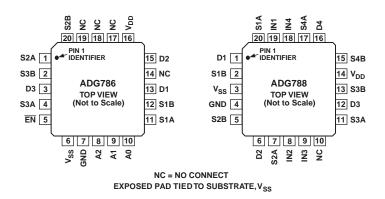

#### PIN CONFIGURATIONS

| A2 | A1 | A0 | ĒN | ON Switch              |

|----|----|----|----|------------------------|

| X  | X  | Х  | 1  | None                   |

| 0  | 0  | 0  | 0  | D1-S1A, D2-S2A, D3-S3A |

| 0  | 0  | 1  | 0  | D1-S1B, D2-S2A, D3-S3A |

| 0  | 1  | 0  | 0  | D1-S1A, D2-S2B, D3-S3A |

| 0  | 1  | 1  | 0  | D1-S1B, D2-S2B, D3-S3A |

| 1  | 0  | 0  | 0  | D1-S1A, D2-S2A, D3-S3B |

| 1  | 0  | 1  | 0  | D1-S1B, D2-S2A, D3-S3B |

| 1  | 1  | 0  | 0  | D1-S1A, D2-S2B, D3-S3B |

| 1  | 1  | 1  | 0  | D1-S1B, D2-S2B, D3-S3B |

#### Table I. ADG786 Truth Table

#### Table II. ADG788 Truth Table

| Logic | Switch A | Switch B |

|-------|----------|----------|

| 0     | OFF      | ON       |

| 1     | ON       | OFF      |

#### TERMINOLOGY

| V <sub>DD</sub>          | Most Positive Power Supply Potential                                                                                                             |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub>          | Most Negative Power Supply in a Dual Supply Application. In single supply applications, this should be tied to ground close to the device.       |

| I <sub>DD</sub>          | Positive Supply Current                                                                                                                          |

| I <sub>SS</sub>          | Negative Supply Current                                                                                                                          |

| GND                      | Ground (0 V) Reference                                                                                                                           |

| S                        | Source Terminal. May be an input or output                                                                                                       |

| D                        | Drain Terminal. May be an input or output                                                                                                        |

| IN                       | Logic Control Input                                                                                                                              |

| $V_D$ ( $V_S$ )          | Analog Voltage on Terminals D, S                                                                                                                 |

| R <sub>ON</sub>          | Ohmic Resistance between D and S                                                                                                                 |

| $\Delta R_{ON}$          | On Resistance Match between Any Two Channels, i.e., R <sub>ON</sub> max – R <sub>ON</sub> min.                                                   |

| R <sub>FLAT(ON)</sub>    | Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over the specified analog signal range. |

| I <sub>S</sub> (OFF)     | Source Leakage Current with the Switch "OFF"                                                                                                     |

| $I_D$ , $I_S$ (ON)       | Channel Leakage Current with the Switch "ON"                                                                                                     |

| V <sub>INL</sub>         | Maximum Input Voltage for Logic "0"                                                                                                              |

| V <sub>INH</sub>         | Minimum Input Voltage for Logic "1"                                                                                                              |

| $I_{INL}(I_{INH})$       | Input Current of the Digital Input                                                                                                               |

| C <sub>S</sub> (OFF)     | "OFF" Switch Source Capacitance. Measured with reference to ground.                                                                              |

| $C_D, C_S(ON)$           | "ON" Switch Capacitance. Measured with reference to ground.                                                                                      |

| C <sub>IN</sub>          | Digital Input Capacitance                                                                                                                        |

| t <sub>ON</sub>          | Delay time measured between the 50% and 90% points of the digital inputs and the switch "ON" condition.                                          |

| t <sub>OFF</sub>         | Delay time measured between the 50% and 90% points of the digital input and the switch "OFF" condition.                                          |

| $t_{ON}(\overline{EN})$  | Delay time between the 50% and 90% points of the $\overline{\rm EN}$ digital input and the switch "ON" condition.                                |

| $t_{OFF}(\overline{EN})$ | Delay time between the 50% and 90% points of the $\overline{\mathrm{EN}}$ digital input and the switch "OFF" condition.                          |

| t <sub>OPEN</sub>        | "OFF" time measured between the 80% points of both switches when switching from one address state to another.                                    |

| Charge                   | A measure of the glitch impulse transferred Injection from the digital input to the analog output during switching.                              |

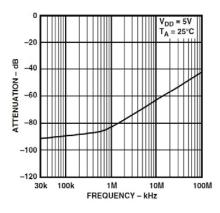

| Off Isolation            | A measure of unwanted signal coupling through an "OFF" switch.                                                                                   |

| Crosstalk                | A measure of unwanted signal that is coupled through from one channel to another as a result of parasitic capacitance.                           |

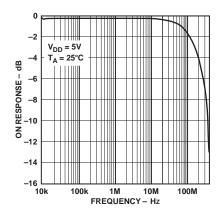

| On Response              | The Frequency Response of the "ON" Switch                                                                                                        |

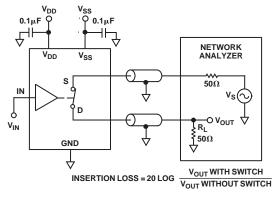

| Insertion Loss           | The Loss Due to the ON Resistance of the Switch.                                                                                                 |

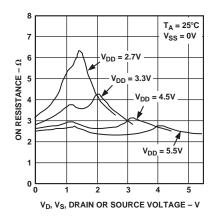

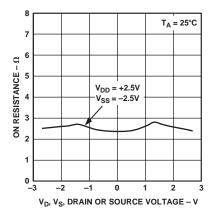

## Typical Performance Characteristics- ADG786/ADG788

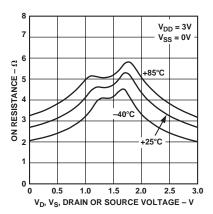

TPC 1. On Resistance as a Function of  $V_D(V_S)$  for Single Supply

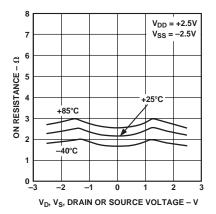

TPC 2. On Resistance as a Function of  $V_D(V_S)$  for Dual Supply

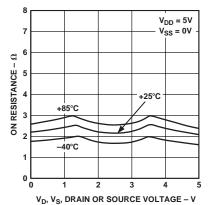

TPC 4. On Resistance as a Function of  $V_D(V_S)$  for Different Temperatures, Single Supply

TPC 5. On Resistance as a Function of  $V_D(V_S)$  for Different Temperatures, Dual Supply

TPC 3. On Resistance as a Function of  $V_D(V_S)$  for Different Temperatures, Single Supply

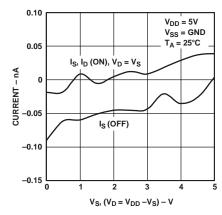

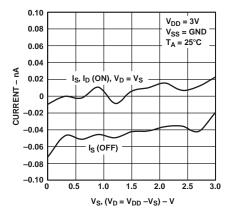

TPC 6. Leakage Currents as a Function of  $V_D(V_S)$

TPC 7. Leakage Currents as a Function of  $V_D(V_S)$

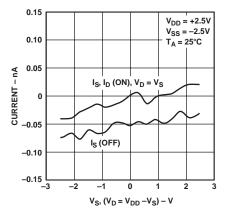

TPC 8. Leakage Currents as a Function of  $V_D(V_S)$

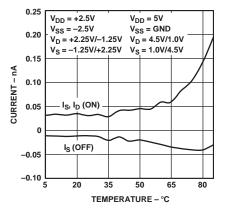

*TPC 9. Leakage Currents as a Function of Temperature*

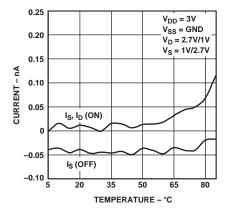

*TPC 10. Leakage Currents as a Function of Temperature*

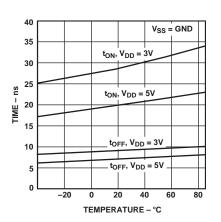

TPC 11.  $t_{ON}/t_{OFF}$  Times vs. Temperature

TPC 12. On Response vs. Frequency

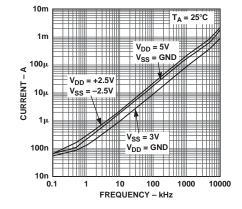

TPC 13. Input Current, I<sub>DD</sub> vs. Switching Frequency

TPC 14. Off Isolation vs. Frequency

TPC 15. Crosstalk vs. Frequency

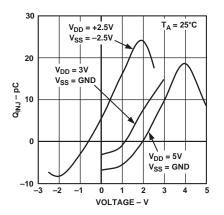

*TPC 16. Charge Injection vs. Source Voltage*

### **Test Circuits**

Test Circuit 5. Enable Delay,  $t_{ON}$  ( $\overline{EN}$ ),  $t_{OFF}$  ( $\overline{EN}$ )

Test Circuit 6. Break-Before-Make Delay, t<sub>OPEN</sub>

Test Circuit 7. Charge Injection

Test Circuit 8. OFF Isolation

Test Circuit 9. Channel-to-Channel Crosstalk

Test Circuit 10. Bandwidth

#### **Power Supply Sequencing**

When using CMOS devices, care must be taken to ensure correct power supply sequencing. Incorrect sequencing can result in the device being subjected to stresses beyond those maximum ratings listed in the data sheet. Digital and analog inputs should be applied to the device after supplies and ground. In dual supply applications, if digital and analog inputs may be applied prior to  $V_{DD}$  and  $V_{SS}$  supplies, the addition of a Schottky diode connected between  $V_{SS}$  and GND will ensure that the device powers on correctly. For single supply applications,  $V_{SS}$  should be tied to GND as close to the device as possible.

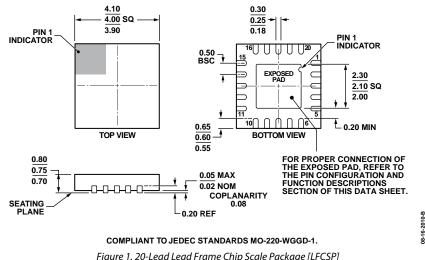

### **OUTLINE DIMENSIONS**

Figure 1. 20-Lead Lead Frame Chip Scale Package [LFCSP] 4 mm × 4 mm Body and 0.75 mm Package Height (CP-20-6) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature Range | Package Description                           | Package Option |

|-----------------------|-------------------|-----------------------------------------------|----------------|

| ADG786BCPZ            | -40°C to +85°C    | 20-Lead Lead Frame Chip Scale Package [LFCSP] | CP-20-6        |

| ADG786BCPZ-REEL7      | -40°C to +85°C    | 20-Lead Lead Frame Chip Scale Package [LFCSP] | CP-20-6        |

| ADG786WBCPZ-REEL7     | -40°C to +85°C    | 20-Lead Lead Frame Chip Scale Package [LFCSP] | CP-20-6        |

| ADG788BCPZ            | -40°C to +85°C    | 20-Lead Lead Frame Chip Scale Package [LFCSP] | CP-20-6        |

| ADG788BCPZ-REEL       | -40°C to +85°C    | 20-Lead Lead Frame Chip Scale Package [LFCSP] | CP-20-6        |

| ADG788BCPZ-REEL7      | -40°C to +85°C    | 20-Lead Lead Frame Chip Scale Package [LFCSP] | CP-20-6        |

| EVAL-ADG788EBZ        |                   | Evaluation Board                              |                |

$^{1}$  Z = RoHS Compliant Part.

$^{2}$  W = Qualified for Automotive Applications.

#### **AUTOMOTIVE PRODUCTS**

The ADG786W models are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that these automotive models may have specifications that differ from the commercial models; therefore, designers should review the Specifications section of this data sheet carefully. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

#### **REVISION HISTORY**

#### 9/15-Rev. B to Rev. C

| Change to Functional Block Diagrams1 |

|--------------------------------------|

| Updated Outline Dimensions11         |

| Changes to Ordering Guide11          |

#### 10/13—Rev. A to Rev. B

| Changed Off Isolation from -72 dB to -80 dB and Channel-to- |

|-------------------------------------------------------------|

| Channel Crosstalk from -67 dB to -80 dB (Throughout)2       |

| Changes to TPC 14 and TPC 158                               |

| 8/12—Rev. 0 to Rev. A             |     |

|-----------------------------------|-----|

| Updated Outline Dimensions        | .11 |

| Changes to Ordering Guide         | .11 |

| Added Automotive Products Section | .11 |

|                                   |     |

7/01—Revision 0: Initial Version

©2001–2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D02381-0-9/15(C)

Rev. C | Page 11