# 2 MHz, Synchronous Boost DC-to-DC Converter

Data Sheet ADP1607

#### **FEATURES**

Up to 96% efficiency

0.8 V to V<sub>OUT</sub> input voltage range

Low 0.9 V input start-up voltage

1.8 V to 3.3 V output voltage range

23 μA quiescent current

Fixed PWM and light load PFM mode options

Synchronous rectification

True shutdown output Isolation

Internal soft start, compensation, and current limit

2 mm × 2 mm, 6-lead LFCSP

Compact solution size

#### **APPLICATIONS**

1-cell and 2-cell alkaline and NiMH/NiCd powered devices Portable audio players, instruments, and medical devices Solar cell applications Miniature hard disk power supplies Power LED status indicators

#### **GENERAL DESCRIPTION**

The ADP1607 is a high efficiency, synchronous, fixed frequency, step-up dc-to-dc switching converter with an adjustable output voltage between 1.8 V and 3.3 V for use in portable applications.

The 2 MHz operating frequency enables the use of small footprint, low profile external components. Additionally, the synchronous rectification, internal compensation, internal fixed current limit, and current mode architecture allow for excellent transient response and a minimal external part count.

Other key features include fixed PWM and light load PFM mode options, true output isolation, thermal shutdown (TSD), and logic controlled enable. Available in a lead-free, thin, 6-lead LFCSP package, the ADP1607 is ideal for providing efficient power conversion in portable devices.

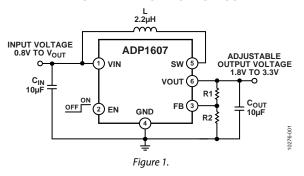

#### TYPICAL APPLICATION CIRCUIT

# **ADP1607\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖳

View a parametric search of comparable parts.

# **EVALUATION KITS**

- ADP1606/ADP1607 Evaluation Board

- · ADP1607 Evaluation Board

# **DOCUMENTATION**

# **Data Sheet**

ADP1606/ADP1607: 2 MHz, Sychronous Boost DC-to-DC Conveters Data Sheet

# TOOLS AND SIMULATIONS $\Box$

ADIsimPower<sup>™</sup> Voltage Regulator Design Tool

# REFERENCE DESIGNS 🖵

CN0372

# DESIGN RESOURCES 🖵

- ADP1607 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

# **DISCUSSIONS**

View all ADP1607 EngineerZone Discussions.

# SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

# **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

# DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

10/12—Revision 0: Initial Version

| Features1                                             |

|-------------------------------------------------------|

| Applications1                                         |

| General Description1                                  |

| Typical Application Circuit                           |

| Revision History2                                     |

| Specifications                                        |

| Absolute Maximum Ratings4                             |

| Thermal Operating Ranges4                             |

| Thermal Resistance                                    |

| ESD Caution                                           |

| Pin Configuration and Function Descriptions5          |

| Typical Performance Characteristics                   |

| Theory of Operation                                   |

| REVISION HISTORY                                      |

| 12/13—Rev. B to Rev. C                                |

| Changes to Figure 219                                 |

| 7/13—Rev. A to Rev. B                                 |

| Changes to Captions for Figure 22 and Figure 23       |

| 12/12—Rev. 0 to Rev. A                                |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |

| Overview                      | 10 |

|-------------------------------|----|

| Enable/Shutdown               | 10 |

| Modes of Operation            | 10 |

| Internal Control Features     | 11 |

| Applications Information      | 12 |

| Setting the Output Voltage    | 12 |

| Inductor Selection            | 12 |

| Choosing the Input Capacitor  | 13 |

| Choosing the Output Capacitor | 13 |

| Layout Guidelines             | 14 |

| Outline Dimensions            | 15 |

| Ordering Guide                | 15 |

# **SPECIFICATIONS**

$V_{\rm IN} = V_{\rm EN} = 1.2 \text{ V}, V_{\rm OUT} = 3.3 \text{ V}$  at  $T_{\rm A} = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$  for minimum/maximum specifications, and  $T_{\rm A} = 25 ^{\circ}\text{C}$  for typical specifications, unless otherwise noted.1

Table 1.

| Parameter                                  | Symbol              | Test Conditions/Comments                                                                             | Min    | Тур   | Max       | Unit |

|--------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------|--------|-------|-----------|------|

| SUPPLY                                     |                     |                                                                                                      |        |       |           |      |

| Minimum Start-Up Voltage <sup>2</sup>      |                     | $R_{MIN} = 22 \Omega$                                                                                | 0.9    |       |           | V    |

| Operating Input Voltage Range <sup>3</sup> | V <sub>IN</sub>     |                                                                                                      | 0.8    |       | $V_{OUT}$ | V    |

| Shutdown Current                           | I <sub>QSD</sub>    | $V_{EN} = GND, V_{OUT} = GND, T_A = -40^{\circ}C \text{ to } +45^{\circ}C^4$                         |        | 0.06  | 0.67      | μΑ   |

| Quiescent Current                          |                     | Nonswitching, measured on VOUT, auto operating mode part only                                        |        |       |           |      |

|                                            |                     | $T_A = -40^{\circ}\text{C to } +45^{\circ}\text{C}$                                                  |        | 23    | 29        | μΑ   |

|                                            |                     | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                  |        | 23    | 40        | μΑ   |

|                                            |                     | Measured on VIN                                                                                      |        |       |           |      |

|                                            |                     | $T_A = -40$ °C to $+45$ °C                                                                           |        | 6     | 11        | μΑ   |

|                                            |                     | $T_A = -40$ °C to $+85$ °C                                                                           |        | 6     | 14.6      | μΑ   |

| Soft Start Time                            |                     |                                                                                                      |        | 1.3   |           | ms   |

| SWITCH                                     |                     |                                                                                                      |        |       |           |      |

| Current Limit                              | I <sub>CL</sub>     |                                                                                                      | 0.8    | 1     | 1.3       | Α    |

| NMOS On Resistance                         | R <sub>DSON_N</sub> | $I_{SW} = 500 \text{ mA}$                                                                            |        | 116   | 165       | mΩ   |

| PMOS On Resistance                         | $R_{DSON\_P}$       | $I_{SW} = 500 \text{ mA}$                                                                            |        | 155   | 225       | mΩ   |

| SW Leakage Current                         |                     | $V_{SW} = 1.2 \text{ V}, V_{OUT} = 0 \text{ V}, T_A = -40^{\circ}\text{C to } +45^{\circ}\text{C}^4$ |        | 0.18  | 2         | μΑ   |

| OSCILLATOR                                 |                     |                                                                                                      |        |       |           |      |

| Switching Frequency                        | f <sub>SW</sub>     |                                                                                                      | 1.8    | 2     | 2.2       | MHz  |

| Maximum Duty Cycle                         | D <sub>MAX</sub>    |                                                                                                      | 85     | 90    |           | %    |

| OUTPUT                                     |                     |                                                                                                      |        |       |           |      |

| VOUT Range                                 | Vout                |                                                                                                      | 1.8    |       | 3.3       | V    |

| FB Pin Voltage                             | $V_{FB}$            | PWM mode                                                                                             | 1.2338 | 1.259 | 1.2842    | V    |

| FB Pin Current                             | I <sub>FB</sub>     | $V_{FB} = 1.26 \text{ V}$                                                                            |        | 0.1   | 0.25      | μΑ   |

| EN/MODE LOGIC                              |                     |                                                                                                      |        |       |           |      |

| Input Voltage Threshold Low                | VIL                 |                                                                                                      |        |       | 0.25      | V    |

| Input Voltage Threshold High               | V <sub>IH</sub>     |                                                                                                      | 0.8    |       |           | V    |

| EN/MODE Leakage Current                    |                     | $V_{EN} = GND \text{ or VIN, } V_{OUT} = 0 \text{ V}$                                                |        | 0.001 | 0.25      | μΑ   |

| THERMAL SHUTDOWN <sup>5</sup>              |                     |                                                                                                      |        |       |           |      |

| Thermal Shutdown Threshold                 |                     |                                                                                                      |        | 150   |           | °C   |

| Thermal Shutdown Hysteresis                |                     |                                                                                                      |        | 15    |           | °C   |

<sup>&</sup>lt;sup>1</sup> All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC). Specifications are subject to change without notice. <sup>2</sup> Guaranteed by design, but not production tested. VIN can never exceed VOUT once the ADP1607 is enabled. <sup>3</sup> Minimum value is characterized by design. Maximum value is characterized on the bench.

<sup>&</sup>lt;sup>4</sup>This parameter is the semiconductor leakage current. The semiconductor leakage current doubles with every 10°C increase in temperature. The maximum limit follows the same trend over temperature.

<sup>&</sup>lt;sup>5</sup> Thermal shutdown protection is only active in PWM mode.

# **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                            | Rating                 |

|--------------------------------------|------------------------|

| VIN, VOUT to GND                     | -0.3 V to +3.6 V       |

| FB to GND                            | -0.3 V to +1.4 V       |

| EN, SW to GND (when VIN ≥ VOUT)      | -0.3 V to VIN + 0.3 V  |

| EN, SW to GND (when VIN < VOUT)      | -0.3 V to VOUT + 0.3 V |

| EPAD to GND                          | -0.3  V to + 0.3  V    |

| Operating Ambient Temperature Range  | −40°C to +85°C         |

| Operating Junction Temperature Range | −40°C to +90°C         |

| Storage Temperature Range            | −65°C to +150°C        |

| Soldering Conditions                 | JEDEC J-STD-020        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Absolute maximum ratings apply individually only, not in combination.

## THERMAL OPERATING RANGES

The ADP1607 can be damaged when the junction temperature limits are exceeded. The maximum operating junction temperature ( $T_{J(MAX)}$ ) takes precedence over the maximum operating ambient temperature ( $T_{A(MAX)}$ ). Monitoring ambient temperature does not guarantee that the junction temperature ( $T_J$ ) is within the specified temperature limits.

In applications with high power dissipation and poor PCB thermal resistance, the maximum ambient temperature may need to be derated. In applications with moderate power dissipation and low PCB thermal resistance, the maximum ambient temperature can exceed the maximum limit as long as the junction temperature is within specification limits.

The junction temperature  $T_J$  of the device is dependent on the ambient temperature  $(T_A)$ , the power dissipation of the device  $(P_D)$ , and the junction-to-ambient thermal resistance of the package  $(\theta_{JA})$ . Maximum junction temperature  $(T_J)$  is calculated from the ambient temperature  $(T_A)$  and power dissipation  $(P_D)$  using the following formula:

$$T_J = T_A + (P_D \times \theta_{JA})$$

#### THERMAL RESISTANCE

Junction-to-ambient thermal resistance  $(\theta_{JA})$  of the package is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages. The junction-to-ambient thermal resistance is highly dependent on the application and board layout. In applications where high maximum power dissipation exists, attention to thermal board design is required. The value of  $\theta_{JA}$  may vary, depending on PCB material, layout, and environmental conditions.

$\theta_{JA}$  and  $\theta_{JC}$  (junction to case) are determined according to JESD51-9 on a 4-layer PCB with natural convection cooling and the exposed pad soldered to the board with thermal vias.

Table 3.

| Package Type | θ <sub>JA</sub> | θις | Unit |

|--------------|-----------------|-----|------|

| 6-Lead LFCSP | 66.06           | 4.3 | °C/W |

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

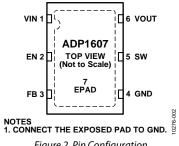

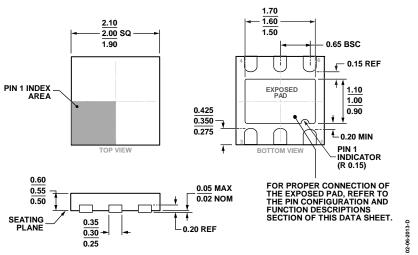

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                        |

|---------|----------|----------------------------------------------------------------------------------------------------|

| 1       | VIN      | Analog and Power Supply Pin.                                                                       |

| 2       | EN       | Shutdown Control Pin. Drive EN high to turn on the synchronous boost, drive EN low to turn it off. |

| 3       | FB       | Output Voltage Feedback Pin.                                                                       |

| 4       | GND      | Analog and Power Ground Pin.                                                                       |

| 5       | SW       | Drain Connection for NMOS and PMOS Power Switches.                                                 |

| 6       | VOUT     | Output Voltage and Source Connection of PMOS Power Switch.                                         |

| 7       | EPAD     | Exposed Pad. Connect to GND.                                                                       |

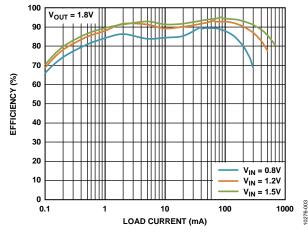

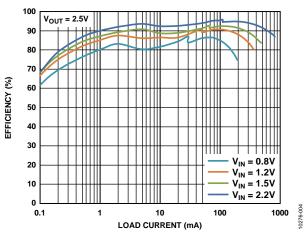

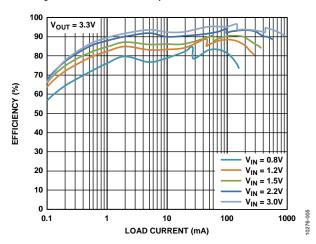

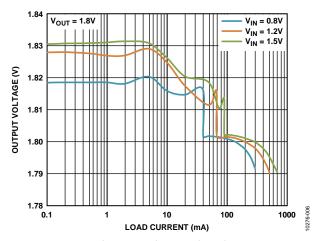

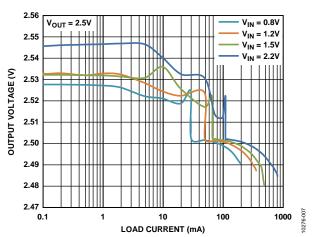

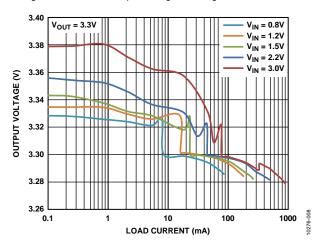

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{\rm IN}=1.2~V,~V_{\rm OUT}=3.3~V,~L=2.2~\mu H~(DCR_{\rm MAX}=66~m\Omega,~VLF302512MT-2R2M),~C_{\rm IN}=10~\mu F,~C_{\rm OUT}=10~\mu F~(10~V,~20\%,~LMK107BJ106MALT),~V_{\rm EN}=V_{\rm IN},~and~T_{\rm A}=25^{\circ}C,~unless~otherwise~noted.$

Figure 3. Auto Mode Efficiency vs. Load Current,  $V_{OUT} = 1.8 \text{ V}$

Figure 4. Auto Mode Efficiency vs. Load Current,  $V_{OUT} = 2.5 V$

Figure 5. Auto Mode Efficiency vs. Load Current,  $V_{OUT} = 3.3 \text{ V}$

Figure 6. Auto Mode Output Voltage Load Regulation,  $V_{OUT} = 1.8 \text{ V}$

Figure 7. Auto Mode Output Voltage Load Regulation,  $V_{OUT} = 2.5 \text{ V}$

Figure 8. Auto Mode Output Voltage Load Regulation,  $V_{OUT} = 3.3 \text{ V}$

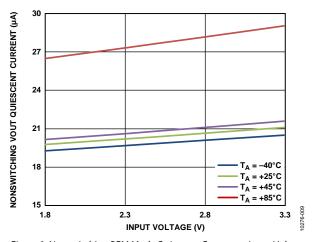

Figure 9. Nonswitching PFM Mode Quiescent Current vs. Input Voltage

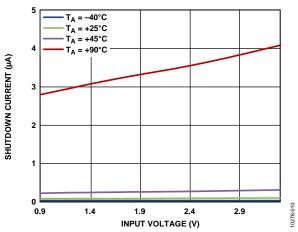

Figure 10. Shutdown Current vs. Input Voltage

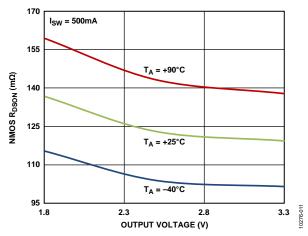

Figure 11. NMOS Drain-to-Source On Resistance

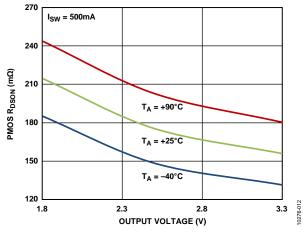

Figure 12. PMOS Drain-to-Source On Resistance

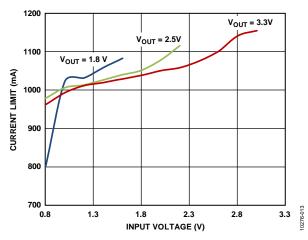

Figure 13. Switch Current Limit vs. Input Voltage

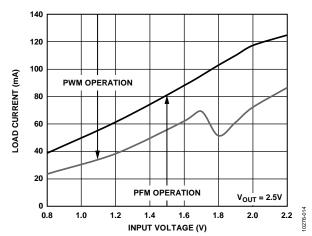

Figure 14. Auto Mode Transition Thresholds

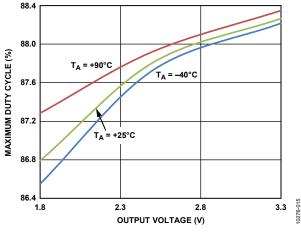

Figure 15. Maximum Duty Cycle vs. Output Voltage

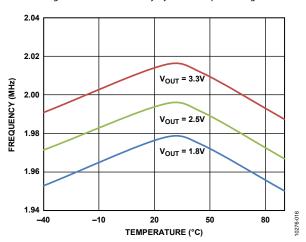

Figure 16. Frequency vs. Temperature

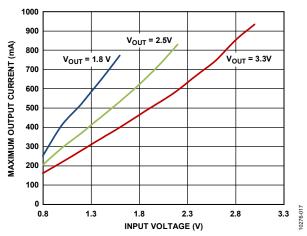

Figure 17. Maximum Output Current vs. Input Voltage

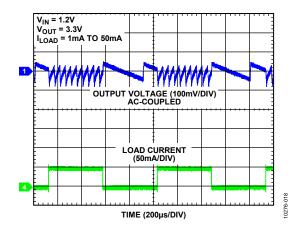

Figure 18. PFM Mode Load Transient Response (Auto Mode Part)

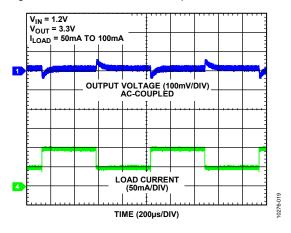

Figure 19. PWM Mode Load Transient Response (Fixed PWM Mode Part)

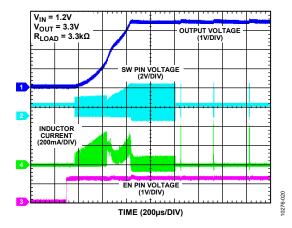

Figure 20. Startup,  $R_{LOAD} = 3.3 \text{ k}\Omega$

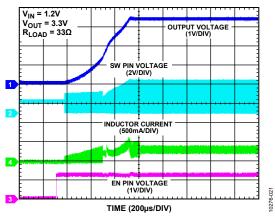

Figure 21. Startup,  $R_{LOAD} = 33 \Omega$

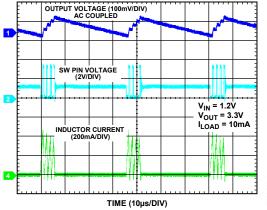

Figure 22. Typical PFM Mode Operation,  $I_{LOAD} = 10 \text{ mA}$

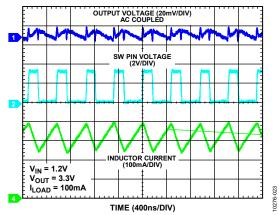

Figure 23. Typical PWM Mode Operation, I<sub>LOAD</sub> = 100 mA

# THEORY OF OPERATION

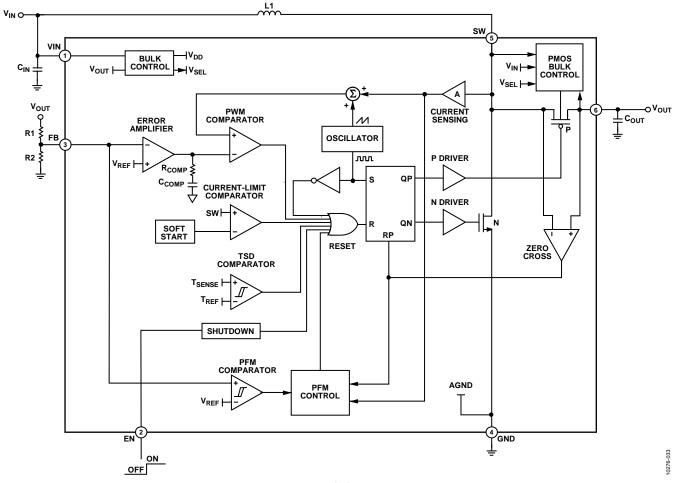

Figure 24. Block Diagram

# **OVERVIEW**

The ADP1607 is a high efficiency, synchronous, fixed frequency, step-up dc-to-dc switching converter with an adjustable output voltage between 1.8 V and 3.3 V for use in portable applications.

The 2 MHz operating frequency enables the use of small footprint, low profile external components. Additionally, the synchronous rectification, internal compensation, internal fixed current limit, and current-mode architecture allow for excellent transient response and a minimal external part count. Other key features include fixed PWM and light load PFM mode options, true output isolation, thermal shutdown (TSD), and logic controlled enable.

# **ENABLE/SHUTDOWN**

The EN input turns the ADP1607 on or off. Connect EN to GND or logic low to shut down the part and reduce the current consumption to 0.06  $\mu A$  (typical). Connect EN to VIN or logic high to enable the part. Do not exceed  $V_{\rm IN}$ . Do not leave this pin floating.

# **MODES OF OPERATION**

The ADP1607 is available in a fixed PWM mode only option for noise sensitive applications or in an auto PFM-to-PWM transitioning mode option to optimize power at light loads.

#### Pulse-Width Modulation (PWM) Mode

The PWM version of the ADP1607 utilizes a current-mode PWM control scheme to force the part to maintain a fixed 2 MHz fixed frequency while regulating the output voltage over all load conditions. The auto mode version of the ADP1607 operates in PWM for higher load currents. In PWM, the output voltage is monitored at the FB pin through the external resistive voltage divider. The voltage at FB is compared to the internal 1.259 V reference by the internal error amplifier. This current-mode PWM regulation system allows fast transient response and tight output voltage regulation. PWM mode operation results in lower efficiencies than PFM mode at light loads.

#### **Auto Mode**

Auto mode is a power-saving feature that forces the auto version of the ADP1607 to switch between PFM and PWM in response to output load changes. The auto version of the ADP1607

operates in PFM mode for light load currents and switches to PWM mode for medium and heavy load currents.

# Pulse Frequency Modulation (PFM)

When the auto mode version of the ADP1607 is operating under light load conditions, the effective switching frequency and supply current are decreased and varied using PFM to regulate the output voltage. This results in improved efficiencies and lower quiescent currents. In PFM mode, the converter only switches when necessary to keep the output voltage between the PFM comparator high output voltage threshold and the lower sleep mode exit voltage threshold. Switching stops when the upper PFM limit is reached and resumes when the lower sleep mode exit threshold is reached.

When  $V_{\rm OUT}$  exceeds the upper PFM threshold, switching stops and the part enters sleep mode. In sleep mode, the ADP1607 is mostly shut down, significantly reducing the quiescent current. The output voltage is then discharged by the load until the output voltage reaches the lower sleep mode exit threshold. After crossing the lower sleep mode exit threshold, switching resumes and the process repeats.

#### **Mode Transition**

The auto mode version of the ADP1607 switches automatically between PFM and PWM modes to maintain optimal efficiency. Switching to PFM allows the converter to save power by supplying the lighter load current with fewer switching cycles. The mode transition point depends on the operating conditions. See Figure 14 for typical transition levels for  $V_{\rm OUT} = 2.5~\rm V$ . Hysteresis exists in the transition point to prevent instability and decreased efficiencies that may result if the converter oscillates between PFM and PWM for a fixed input voltage and load current.

The output voltage in PWM can be above or below the PFM voltage of that part.

#### INTERNAL CONTROL FEATURES

## **Input to Output Isolation**

While in shutdown, the ADP1607 manages the voltage of the bulk of the PMOS to force it off and internally isolate the path from the input to output. This allows the output to drop to ground, reducing the current consumption of the application in shutdown.

#### Soft Start

The ADP1607 soft start sequence is designed for optimal control of the part. When EN goes high, or when the part recovers from a TSD, the start-up sequence begins. The output voltage increases through a sequence of stages to ensure that the internal circuitry is powered up in the correct order as the output voltage rises to its final value.

#### **Current Limit**

The ADP1607 is designed with a fixed 1 A typical current limit that does not vary with duty cycle.

# **Synchronous Rectification**

In addition to the N-channel MOSFET switch, the ADP1607 has a P-channel MOSFET switch to build the synchronous rectifier. The synchronous rectifier improves efficiency, especially for heavy load currents, and reduces cost and board space by eliminating the need for an external Schottky diode.

#### **Compensation**

The PWM control loop of the ADP1607 is internally compensated to deliver maximum performance with no additional external components. The ADP1607 is designed to work with 2.2  $\mu$ H chip inductors and 10  $\mu$ F ceramic capacitors. Other values may reduce performance and/or stability.

# Thermal Shutdown (TSD) Protection

The ADP1607 includes thermal shutdown (TSD) protection when the part is in PWM mode only. If the die temperature exceeds 150°C (typical), the TSD protection activates and turns off the power devices. They remain off until the die temperature falls below 135°C (typical), at which point the converter restarts.

# APPLICATIONS INFORMATION

## **SETTING THE OUTPUT VOLTAGE**

The ADP1607 can be configured for output voltages between 1.8 V and 3.3 V. The output voltage is set by a resistor voltage divider, R1, from the output voltage (V<sub>OUT</sub>) to the 1.259 V feedback input at FB and R2 from FB to GND (see Figure 24). Resistances between 100 k $\Omega$  and 1 M $\Omega$  are recommended.

For larger R1 and R2 values, the voltage drop due to the FB pin current ( $I_{\text{FB}}$ ) on R1 becomes proportionally significant and needs to be factored in.

To account for the effect of  $I_{FB}$  for all values of R1 and R2, use the following equation to determine R1 and R2 for the desired  $V_{\rm OUT}$ :

$$V_{OUT} = \left(1 + \frac{RI}{R2}\right)V_{FB} + I_{FB}(RI) \tag{1}$$

where:

$V_{FB} = 1.259 \text{ V}$ , typical

$I_{FB} = 0.1 \, \mu A$ , typical

## INDUCTOR SELECTION

The ADP1607 is designed with a 2 MHz operating frequency enabling the use of small chip inductors ideal for use in applications with limited solution size constraints. The ADP1607 is designed for optimal performance with 2.2  $\mu H$  inductors, which have favorable saturation currents and lower series resistances for their given physical size.

To ensure stable and efficient performance with the ADP1607, care should be taken to select a compatible inductor with a sufficient current rating, saturation current, and low dc resistance (DCR.)

The maximum rated rms current of the inductor must be greater than the maximum input current to the regulator. Likewise, the saturation current of the chosen inductor must be able to support the peak inductor current (the maximum input current plus half the inductor ripple current) of the application.

The inductor ripple current ( $\Delta I_L$ ) in steady state continuous mode can be calculated as

$$\Delta I_L = \frac{V_{IN} \times D}{L \times f_{SW}} \tag{2}$$

where:

*D* is the duty cycle of the application.

*L* is the inductor value.

fsw is the switching frequency of the ADP1607.

The switch duty cycle (D) is determined by the input ( $V_{IN}$ ) and output ( $V_{OUT}$ ) voltages with the following equation:

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}} \tag{3}$$

Inductors with a low DCR minimize power loss and improve efficiency. DCR values below 100 m $\Omega$  are recommended.

**Table 5. Suggested Inductors**

|              |                          | Inductance | DCR (mΩ) | Current    | Saturation  |                                   |         |

|--------------|--------------------------|------------|----------|------------|-------------|-----------------------------------|---------|

| Manufacturer | Part Number              | (μH)       | Тур      | Rating (A) | Current (A) | Size $(L \times W \times H)$ (mm) | Package |

| TDK          | MLP2016S2R2M             | 2.2 ± 20%  | 110      | 1.20       |             | 2.00 × 1.60 × 1.00                | 0806    |

|              | MLP2520S2R2S             | 2.2 ± 20%  | 110      | 1.20       | 1.20        | $2.50 \times 2.00 \times 1.00$    | 1008    |

|              | VLF252012MT-2R2M         | 2.2 ± 20%  | 57       | 1.67       | 1.04        | $2.50 \times 2.00 \times 1.00$    | 1008    |

|              | VLF302510MT-2R2M         | 2.2 ± 20%  | 70       | 1.23       | 1.37        | $3.00 \times 2.50 \times 1.00$    |         |

|              | VLF302515MT-2R2M         | 2.2 ± 20%  | 42       | 2.71       | 1.57        | $3.00 \times 2.50 \times 1.40$    |         |

| Murata       | LQM2HPN2R2MG0            | 2.2 ± 20%  | 80       | 1.30       |             | 2.50 × 2.00 × 0.90                | 1008    |

|              | LQH32PN2R2NNC            | 2.2 ± 30%  | 64       | 1.85       |             | $3.20 \times 2.50 \times 1.55$    | 1210    |

| Wurth        | 74479787222              | 2.2 ± 20%  | 80       | 1.50       | 0.70        | 2.50 × 2.00 × 1.00                | 1008    |

|              | 7440430022               | 2.2 ± 30%  | 23       | 2.50       | 2.35        | $4.80 \times 48.0 \times 2.80$    |         |

| Taiyo Yuden  | BRC2012T2R2MD            | 2.2 ± 20%  | 110      | 1.00       | 1.10        | 2.00 × 1.25 × 1.40                | 0805    |

| Toko         | MDT2520-CR2R2M           | 2.2 ± 20%  | 90       | 1.35       |             | 2.50 × 2.00 × 1.00                | 1008    |

|              | DEM2810C (1224AS-H-2R2M) | 2.2 ± 20%  | 85       | 1.10       | 1.40        | $3.20 \times 3.00 \times 1.00$    |         |

|              | DEM2815C (1226AS-H-2R2M) | 2.2 ± 20%  | 43       | 1.40       | 2.20        | $3.20 \times 3.00 \times 1.50$    |         |

| Coilcraft    | XFL3012-222              | 2.2 ± 20%  | 81       | 1.9        | 1.6         | 3.00 × 3.00 × 1.20                | 1212    |

|              | XFL4020-222              | 2.2 ± 10%  | 21       | 8.0        | 3.1         | $4.00 \times 4.00 \times 2.10$    | 1515    |

#### **CHOOSING THE INPUT CAPACITOR**

The ADP1607 requires a 10  $\mu$ F or greater input bypass capacitor ( $C_{\rm IN}$ ) between VIN and GND to supply transient currents while maintaining a constant input voltage. The value of the input capacitor can be increased without any limit for smaller input voltage ripple and better input voltage filtering. The capacitor must have a 4 V or higher voltage rating to support the maximum input operating voltage. It is recommended that  $C_{\rm IN}$  be placed as close to the ADP1607 as possible.

Different types of capacitors can be considered, but for battery-powered applications, the best choice is the multilayer ceramic capacitor, due to its small size, low equivalent series resistance (ESR), and low equivalent series inductance (ESL). X5R or X7R dielectrics are recommended. Y5V capacitors should not be used due to their variation in capacitance over temperature. Alternatively, use a high value, medium ESR capacitor in parallel with a  $0.1~\mu F$  low ESR capacitor.

## **CHOOSING THE OUTPUT CAPACITOR**

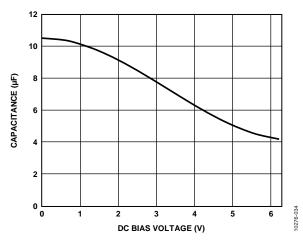

The ADP1607 also requires a 10  $\mu F$  output capacitor ( $C_{\text{OUT}}$ ) to maintain the output voltage and supply current to the load. The output capacitor supplies the current to the load when the N-channel switch is turned on. Similar to  $C_{\text{IN}}$ , a 4 V or greater, low ESR, X5R or X7R ceramic capacitor is recommended for  $C_{\text{OUT}}$ . When choosing the output capacitor, it is also important to account for the loss of capacitance due to output voltage dc bias. This may result in using a capacitor with a higher rated voltage to achieve the desired capacitance value. See Figure 25 for an example of how the capacitance of a 10  $\mu F$  ceramic capacitor changes with the dc bias voltage.

Figure 25. Typical Ceramic Capacitor Performance

The value and characteristics of the output capacitor greatly affect the output voltage ripple, transient performance, and stability of the regulator. The output voltage ripple ( $\Delta V_{OUT}$ ) in continuous operation is calculated as follows:

$$\Delta V_{OUT} = \frac{Q_C}{C_{OUT}} = \frac{I_{OUT} \times t_{ON}}{C_{OUT}}$$

(4)

where

$Q_C$  is the charge removed from the capacitor.  $t_{ON}$  is the on time of the N-channel switch.  $C_{OUT}$  is the effective output capacitance.  $I_{OUT}$  is the output load current.

$$t_{ON} = \frac{D}{f_{SW}} \tag{5}$$

and,

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}} \tag{6}$$

As shown in the duty cycle and output ripple voltage equations, the output voltage ripple increases with the load current.

# LAYOUT GUIDELINES

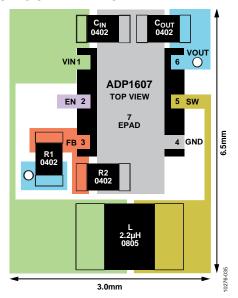

Figure 26. ADP1607 Recommended Layout Showing the Smallest Footprint

For high efficiency, good regulation, and stability, a well-designed printed circuit board layout is required.

Use the following guidelines when designing printed circuit boards (also see Figure 24 for a block diagram and Figure 2 for a pin configuration).

- Keep the low ESR input capacitor, C<sub>IN</sub>, close to VIN and GND. This minimizes noise injected into the part from board parasitic inductance.

- Keep the high current path from C<sub>IN</sub> through the L1 inductor to SW as short as possible.

- Place the feedback resistors, R1 and R2, as close to FB as

possible to prevent noise pickup. Connect the ground of

the feedback network directly to an AGND plane that

makes a Kelvin connection to the GND pin.

- Avoid routing high impedance traces from feedback resistors near any node connected to SW or near the inductor to prevent radiated noise injection.

- Keep the low ESR output capacitor, C<sub>OUT</sub>, close to VOUT and GND. This minimizes noise injected into the part from board parasitic inductance.

- Connect Pin 7 (EPAD) and GND to a large copper plane for proper heat dissipation.

# **OUTLINE DIMENSIONS**

Figure 27. 6-Lead Lead Frame Chip Scale Package [LFCSP\_UD] 2.00 mm × 2.00 mm Body, Ultra Thin, Dual Lead (CP-6-3) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1</sup> | Output<br>Voltage | Operating<br>Modes | Temperature<br>Range | Package Description                                    | Package<br>Option | Branding |

|--------------------|-------------------|--------------------|----------------------|--------------------------------------------------------|-------------------|----------|

| ADP1607ACPZN-R7    | Adjustable        | Auto               | -40°C to +85°C       | 6-Lead LFCSP UD                                        | CP-6-3            | LJ5      |

| ADP1607ACPZN001-R7 | Adjustable        | PWM                | -40°C to +85°C       | 6-Lead LFCSP UD                                        | CP-6-3            | LJ1      |

| ADP1607-EVALZ      |                   | Auto               |                      | Evaluation Board, Automatic PFM/PWM<br>Switching Modes |                   |          |

| ADP1607-001-EVALZ  |                   | PWM                |                      | Evaluation Board, PWM Mode Only                        |                   |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

**NOTES**