# ANALOG Synchronous Guitent-Mode with DEVICES Constant On-Time, PWM Buck Controller

**Data Sheet**

ADP1872/ADP1873

#### **FEATURES**

Power input voltage as low as 2.75 V to 20 V Bias supply voltage range: 2.75 V to 5.5 V Minimum output voltage: 0.6 V 0.6 V reference voltage with ±1.0% accuracy **Supports all N-channel MOSFET power stages** Available in 300 kHz, 600 KHz, and 1.0 MHz options No current-sense resistor required Power saving mode (PSM) for light loads (ADP1873 only) Resistor-programmable current-sense gain Thermal overload protection **Short-circuit protection Precision enable input** Integrated bootstrap diode for high-side drive 140 µA shutdown supply current Starts into a precharged load

#### **APPLICATIONS**

Telecom and networking systems Mid to high end servers **Set-top boxes DSP** core power supplies

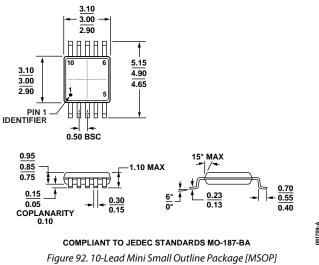

Small, 10-lead MSOP package

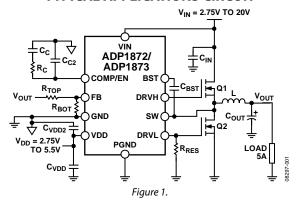

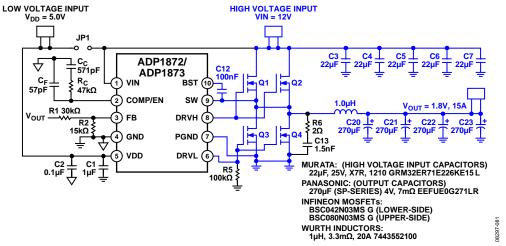

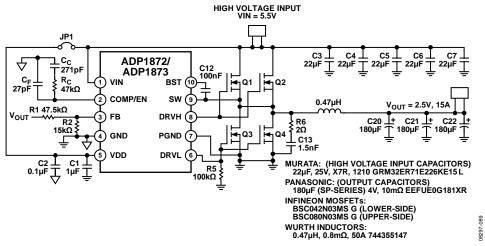

#### TYPICAL APPLICATIONS CIRCUIT

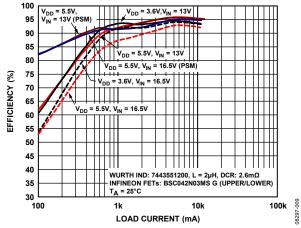

Figure 2. ADP1872 Efficiency vs. Load Current ( $V_{OUT} = 1.8 \text{ V}$ , 300 kHz)

#### **GENERAL DESCRIPTION**

The ADP1872/ADP1873 are versatile current-mode, synchronous step-down controllers that provide superior transient response, optimal stability, and current limit protection by using a constant on-time, pseudo-fixed frequency with a programmable currentsense gain, current-control scheme. In addition, these devices offer optimum performance at low duty cycles by using valley currentmode control architecture. This allows the ADP1872/ADP1873 to drive all N-channel power stages to regulate output voltages as low as 0.6 V.

The ADP1873 is the power saving mode (PSM) version of the device and is capable of pulse skipping to maintain output regulation while achieving improved system efficiency at light loads (see the Power Saving Mode (PSM) Version (ADP1873) section for more information).

Available in three frequency options (300 kHz, 600 kHz, and 1.0 MHz, plus the PSM option), the ADP1872/ADP1873 are well suited for a wide range of applications. These ICs not only operate from a 2.75 V to 5.5 V bias supply, but can also accept a power input as high as 20 V.

In addition, an internally fixed, soft start period is included to limit input in-rush current from the input supply during startup and to provide reverse current protection during soft start for a precharged output. The low-side current-sense, current-gain scheme and integration of a boost diode, along with the PSM/forced pulsewidth modulation (PWM) option, reduce the external part count and improve efficiency.

The ADP1872/ADP1873 operate over the -40°C to +125°C junction temperature range and are available in a 10-lead MSOP.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

| TABLE OF CONTENTS                                                               |                                                         |

|---------------------------------------------------------------------------------|---------------------------------------------------------|

| Features1                                                                       | Timer Operation                                         |

| Applications1                                                                   | Pseudo-Fixed Frequency22                                |

| Typical Applications Circuit                                                    | Applications Information23                              |

| General Description                                                             | Feedback Resistor Divider23                             |

| Revision History                                                                | Inductor Selection                                      |

| Specifications                                                                  | Output Ripple Voltage ( $\Delta V_{RR}$ )               |

| Absolute Maximum Ratings 5                                                      | Output Capacitor Selection23                            |

| Thermal Resistance                                                              | Compensation Network24                                  |

| Boundary Condition5                                                             | Efficiency Consideration                                |

| ESD Caution                                                                     | Input Capacitor Selection26                             |

| Pin Configuration and Function Descriptions 6                                   | Thermal Considerations                                  |

| Typical Performance Characteristics                                             | Design Example                                          |

| ADP1872/ADP1873 Block Digram                                                    | External Component Recommendations                      |

| Theory of Operation                                                             | Layout Considerations                                   |

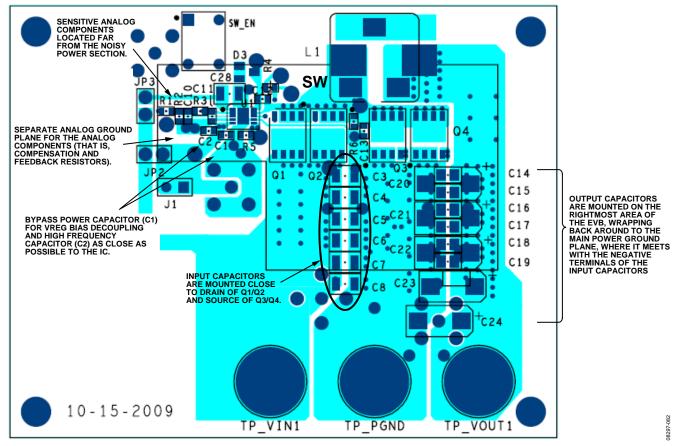

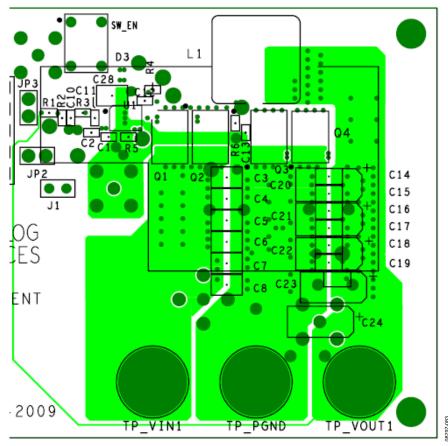

| Startup                                                                         | IC Section (Left Side of Evaluation Board)              |

| •                                                                               |                                                         |

| Soft Start                                                                      | Power Section                                           |

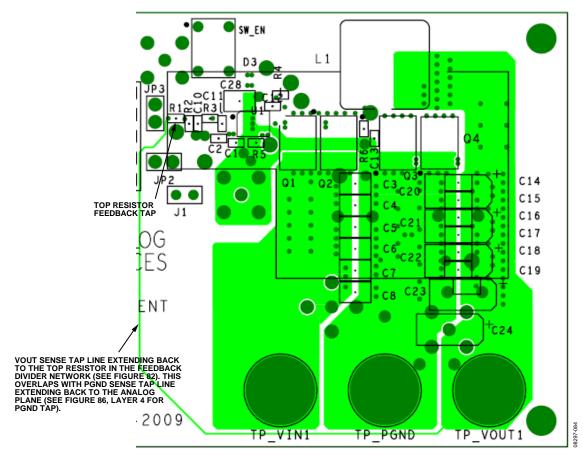

| Precision Enable Circuitry                                                      | Differential Sensing                                    |

| Undervoltage Lockout                                                            | Typical Application Circuits                            |

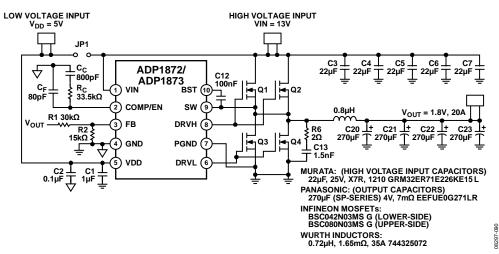

| Thermal Shutdown                                                                | Dual-Input, 300 kHz High Current Application Circuit 38 |

| Programming Resistor (RES) Detect Circuit19                                     | Single-Input, 600 kHz Application Circuit               |

| Valley Current-Limit Setting19                                                  | Dual-Input, 300 kHz High Current Application Circuit 39 |

| Hiccup Mode During Short Circuit20                                              | Outline Dimensions                                      |

| Synchronous Rectifier21                                                         | Ordering Guide40                                        |

| Power Saving Mode (PSM) Version (ADP1873)21                                     |                                                         |

| REVISION HISTORY                                                                |                                                         |

| 7/12—Rev. A to Rev. B                                                           | Changes to Table 9                                      |

| Changed $R_{\rm ON}$ = 15 $m\Omega/100~k\Omega$ Valley Current Level Value from | Changes to Figure 82                                    |

| 7.5 to 3.87; Table 6                                                            | Changes to Figure 84                                    |

| Changes to Ordering Guide                                                       | Changes to Figure 84                                    |

| 3/10—Rev. 0 to Rev. A                                                           | Changes to Figure 86                                    |

| Changes to Figure 11                                                            | Changes to Differential Sensing Section and Figure 88   |

| Changes to Table 1                                                              | Changes to Figure 89 and Figure 90                      |

| Changes to Table 25                                                             | Changes to Figure 91                                    |

| Changes to Figure 59 Caption and Figure 60 Caption 16                           | Updated Outline Dimensions                              |

| Changes to Figure 64                                                            | 10/09—Revision 0: Initial Version                       |

| Changes to Timer Operation Section                                              |                                                         |

| Changes to Table 723                                                            |                                                         |

## **SPECIFICATIONS**

All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC). VDD = 5 V, BST – SW = 5 V, VIN = 13 V. The specifications are valid for  $T_J = -40^{\circ}$ C to +125°C, unless otherwise specified.

Table 1.

| Parameter                                          | Symbol                     | Conditions                                                                                                                 | Min   | Тур  | Max   | Unit |

|----------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| POWER SUPPLY CHARACTERISTICS                       |                            |                                                                                                                            |       |      |       |      |

| High Input Voltage Range                           | VIN                        | ADP1872ARMZ-0.3/ADP1873ARMZ-0.3 (300 kHz)                                                                                  | 2.75  | 12   | 20    | ٧    |

|                                                    |                            | ADP1872ARMZ-0.6/ADP1873ARMZ-0.6 (600 kHz)                                                                                  | 2.75  | 12   | 20    | V    |

|                                                    |                            | ADP1872ARMZ-1.0/ADP1873ARMZ-1.0 (1.0 MHz)                                                                                  | 3.0   | 12   | 20    | V    |

| Low Input Voltage Range                            | VDD                        | $C_{IN} = 1 \mu F$ to PGND, $C_{IN} = 0.22 \mu F$ to GND                                                                   |       |      |       |      |

| , ,                                                |                            | ADP1872ARMZ-0.3/ADP1873ARMZ-0.3 (300 kHz)                                                                                  | 2.75  | 5    | 5.5   | V    |

|                                                    |                            | ADP1872ARMZ-0.6/ADP1873ARMZ-0.6 (600 kHz)                                                                                  | 2.75  | 5    | 5.5   | ٧    |

|                                                    |                            | ADP1872ARMZ-1.0/ADP1873ARMZ-1.0 (1.0 MHz)                                                                                  | 3.0   | 5    | 5.5   | ٧    |

| Quiescent Current                                  | IQ DD + IQ BST             | FB = 1.5 V, no switching                                                                                                   |       | 1.1  |       | mA   |

| Shutdown Current                                   | $I_{DD, SD} + I_{BST, SD}$ | COMP/EN < 285 mV                                                                                                           |       | 140  | 215   | μΑ   |

| Undervoltage Lockout                               | UVLO                       | Rising VDD (See Figure 34 for temperature variation)                                                                       |       | 2.65 |       | v    |

| UVLO Hysteresis                                    |                            | Falling VDD from operational state                                                                                         |       | 190  |       | mV   |

| SOFT START                                         |                            | , J                                                                                                                        |       |      |       |      |

| Soft Start Period                                  |                            | See Figure 57                                                                                                              |       | 3.0  |       | ms   |

| ERROR AMPLIFER                                     |                            |                                                                                                                            |       |      |       |      |

| FB Regulation Voltage                              | $V_{FB}$                   | T <sub>J</sub> = 25°C                                                                                                      |       | 600  |       | mV   |

| 3                                                  |                            | $T_{J} = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                      | 595.5 | 600  | 605.4 | mV   |

|                                                    |                            | $T_{J} = -40^{\circ}\text{C to} + 125^{\circ}\text{C}$                                                                     | 594.2 | 600  | 606.5 | mV   |

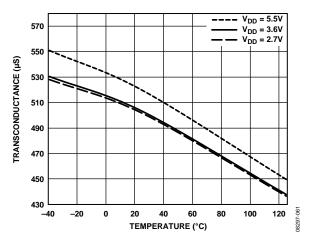

| Transconductance                                   | G <sub>M</sub>             |                                                                                                                            | 300   | 515  | 730   | μs   |

| FB Input Leakage Current                           | I <sub>FB, LEAK</sub>      | FB = 0.6 V, COMP/EN = released                                                                                             |       | 1    | 50    | nA   |

| CURRENT-SENSE AMPLIFIER GAIN                       |                            | ,                                                                                                                          |       |      |       |      |

| Programming Resistor (RES) Value from DRVL to PGND |                            | $RES = 47 \text{ k}\Omega \pm 1\%$                                                                                         | 2.7   | 3    | 3.3   | V/V  |

|                                                    |                            | $RES = 22 k\Omega \pm 1\%$                                                                                                 | 5.5   | 6    | 6.5   | V/V  |

|                                                    |                            | RES = none                                                                                                                 | 11    | 12   | 13    | V/V  |

|                                                    |                            | $RES = 100 \text{ k}\Omega \pm 1\%$                                                                                        | 22    | 24   | 26    | V/V  |

| SWITCHING FREQUENCY                                |                            | Typical values measured at 50% time points with 0 nF at DRVH and DRVL; maximum values are guaranteed by bench evaluation 1 |       |      |       |      |

| ADP1872ARMZ-0.3/<br>ADP1873ARMZ-0.3 (300 kHz)      |                            | guaranteed by bench evaluation                                                                                             |       | 300  |       | kHz  |

| On-Time                                            |                            | $VIN = 5 \text{ V}, V_{OUT} = 2 \text{ V}, T_J = 25^{\circ}\text{C}$                                                       | 1120  | 1200 | 1280  | ns   |

| Minimum On-Time                                    |                            | VIN = 20 V                                                                                                                 |       | 145  | 190   | ns   |

| Minimum Off-Time                                   |                            | 84% duty cycle (maximum)                                                                                                   |       | 320  | 385   | ns   |

| ADP1872ARMZ-0.6/<br>ADP1873ARMZ-0.6 (600 kHz)      |                            |                                                                                                                            |       | 600  |       | kHz  |

| On-Time                                            |                            | $VIN = 5 \text{ V}, V_{OUT} = 2 \text{ V}, T_J = 25^{\circ}\text{C}$                                                       | 500   | 520  | 580   | ns   |

| Minimum On-Time                                    |                            | VIN = 20 V, V <sub>OUT</sub> = 0.8 V                                                                                       |       | 82   | 110   | ns   |

| Minimum Off-Time                                   |                            | 65% duty cycle (maximum)                                                                                                   |       | 320  | 385   | ns   |

| ADP1872ARMZ-1.0/<br>ADP1873ARMZ-1.0 (1.0 MHz)      |                            |                                                                                                                            |       | 1.0  |       | MHz  |

| On-Time                                            |                            | VIN = 5 V, V <sub>OUT</sub> = 2 V, T <sub>J</sub> = 25°C                                                                   | 285   | 312  | 340   | ns   |

| Minimum On-Time                                    |                            | VIN = 20 V                                                                                                                 |       | 60   | 85    | ns   |

| Minimum Off-Time                                   |                            | 45% duty cycle (maximum)                                                                                                   |       | 320  | 385   | ns   |

| Parameter                           | Symbol                   | Conditions                                                                                                     | Min  | Тур  | Max  | Unit |

|-------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|------|

| OUTPUT DRIVER CHARACTERISTICS       |                          |                                                                                                                |      |      |      |      |

| High-Side Driver                    |                          |                                                                                                                |      |      |      |      |

| Output Source Resistance            |                          | I <sub>SOURCE</sub> = 1.5 A, 100 ns, positive pulse (0 V to 5 V)                                               |      | 2    | 3.5  | Ω    |

| Output Sink Resistance              |                          | $I_{SINK} = 1.5 \text{ A}$ , 100 ns, negative pulse (5 V to 0 V)                                               |      | 8.0  | 2    | Ω    |

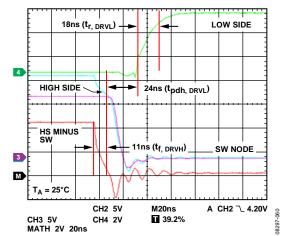

| Rise Time <sup>2</sup>              | t <sub>r, DRVH</sub>     | BST – SW = 4.4 V, $C_{IN}$ = 4.3 nF (see Figure 59)                                                            |      | 25   |      | ns   |

| Fall Time <sup>2</sup>              | t <sub>f, DRVH</sub>     | $BST - SW = 4.4 \text{ V}$ , $C_{IN} = 4.3 \text{ nF}$ (see Figure 60)                                         |      | 11   |      | ns   |

| Low-Side Driver                     |                          |                                                                                                                |      |      |      |      |

| Output Source Resistance            |                          | I <sub>SOURCE</sub> = 1.5 A, 100 ns, positive pulse (0 V to 5 V)                                               |      | 1.7  | 3    | Ω    |

| Output Sink Resistance              |                          | $I_{SINK} = 1.5 \text{ A}$ , 100 ns, negative pulse (5 V to 0 V)                                               |      | 0.75 | 2    | Ω    |

| Rise Time <sup>2</sup>              | t <sub>r, DRVL</sub>     | VDD = 5.0 V, C <sub>IN</sub> = 4.3 nF (see Figure 60)                                                          |      | 18   |      | ns   |

| Fall Time <sup>2</sup>              | t <sub>f, DRVL</sub>     | $VDD = 5.0 \text{ V, } C_{IN} = 4.3 \text{ nF (see Figure 59)}$                                                |      | 16   |      | ns   |

| Propagation Delays                  |                          |                                                                                                                |      |      |      |      |

| DRVL Fall to DRVH Rise <sup>2</sup> | t <sub>tpdh</sub> , DRVH | BST – SW = 4.4 V (see Figure 59)                                                                               |      | 22   |      | ns   |

| DRVH Fall to DRVL Rise <sup>2</sup> | t <sub>tpdh</sub> , DRVL | BST – SW = 4.4 V (see Figure 60)                                                                               |      | 24   |      | ns   |

| SW Leakage Current                  | I <sub>SW, LEAK</sub>    | BST = 25 V, SW = 20 V, VDD = 5.5 V                                                                             |      |      | 110  | μΑ   |

| Integrated Rectifier                |                          |                                                                                                                |      |      |      |      |

| Channel Impedance                   |                          | $I_{SINK} = 10 \text{ mA}$                                                                                     |      | 22   |      | Ω    |

| PRECISION ENABLE THRESHOLD          |                          |                                                                                                                |      |      |      |      |

| Logic High Level                    |                          | VIN = 2.9 V to 20 V, VDD = 2.75 V to 5.5 V                                                                     | 235  | 285  | 330  | mV   |

| Enable Hysteresis                   |                          | VIN = 2.9 V to 20 V, VDD = 2.75 V to 5.5 V                                                                     |      | 35   |      | mV   |

| COMP VOLTAGE                        |                          |                                                                                                                |      |      |      |      |

| COMP Clamp Low Voltage              | V <sub>COMP</sub> (LOW)  | From disable state, release COMP/EN pin to enable device $(2.75 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V})$ | 0.47 |      |      | V    |

| COMP Clamp High Voltage             | V <sub>COMP</sub> (HIGH) | $(2.75 \text{ V} \le \text{VDD} \le 5.5 \text{ V})$                                                            |      |      | 2.55 | V    |

| COMP Zero Current Threshold         | $V_{COMP\_ZCT}$          | $(2.75 \text{ V} \le \text{VDD} \le 5.5 \text{ V})$                                                            |      | 1.15 |      | V    |

| THERMAL SHUTDOWN                    | T <sub>TMSD</sub>        |                                                                                                                |      |      |      |      |

| Thermal Shutdown Threshold          |                          | Rising temperature                                                                                             |      | 155  |      | °C   |

| Thermal Shutdown Hysteresis         |                          |                                                                                                                |      | 15   |      | °C   |

| Hiccup Current Limit Timing         |                          |                                                                                                                |      | 6    |      | ms   |

<sup>&</sup>lt;sup>1</sup> The maximum specified values are with the closed loop measured at 10% to 90% time points (see Figure 59 and Figure 60), C<sub>GATE</sub> = 4.3 nF and upper- and lower-side MOSFETs being Infineon BSC042N03MS G.

<sup>2</sup> Not automatic test equipment (ATE) tested.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                      | Rating                  |

|------------------------------------------------|-------------------------|

| VDD to GND                                     | -0.3 V to +6 V          |

| VIN to PGND                                    | −0.3 V to +28 V         |

| FB, COMP/EN to GND                             | -0.3 V to (VDD + 0.3 V) |

| DRVL to PGND                                   | -0.3 V to (VDD + 0.3 V) |

| SW to PGND                                     | −0.3 V to +28 V         |

| SW to PGND                                     | −2 V pulse (20 ns)      |

| BST to SW                                      | -0.6 V to (VDD + 0.3 V) |

| BST to PGND                                    | -0.3 V to +28 V         |

| DRVH to SW                                     | −0.3 V to VDD           |

| PGND to GND                                    | ±0.3 V                  |

| Operating Junction Temperature<br>Range        | -40°C to +125°C         |

| Storage Temperature Range                      | −65°C to +150°C         |

| Soldering Conditions                           | JEDEC J-STD-020         |

| Maximum Soldering Lead<br>Temperature (10 sec) | 300°C                   |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Absolute maximum ratings apply individually only, not in combination. Unless otherwise specified, all other voltages are referenced to PGND.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 3. Thermal Resistance**

| Package Type                   | θја   | Unit |

|--------------------------------|-------|------|

| θ <sub>JA</sub> (10-Lead MSOP) |       |      |

| 2-Layer Board                  | 213.1 | °C/W |

| 4-Layer Board                  | 171.7 | °C/W |

#### **BOUNDARY CONDITION**

In determining the values given in Table 2 and Table 3, natural convection was used to transfer heat to a 4-layer evaluation board.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                      |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VIN      | High Input Voltage. Connect VIN to the drain of the upper-side MOSFET.                                                                                                                                                                                                           |

| 2       | COMP/EN  | Output of the Internal Error Amplifier/IC Enable. When this pin functions as EN, applying 0 V to this pin disables the IC.                                                                                                                                                       |

| 3       | FB       | Noninverting Input of the Internal Error Amplifier. This is the node where the feedback resistor is connected.                                                                                                                                                                   |

| 4       | GND      | Analog Ground Reference Pin of the IC. All sensitive analog components should be connected to this ground plane (see the Layout Considerations Section).                                                                                                                         |

| 5       | VDD      | Bias Voltage Supply for the ADP1872/ADP1873 Controller (Includes the Output Gate Drivers). A bypass capacitor of 1 $\mu$ F directly from this pin to PGND and a 0.1 $\mu$ F across VDD and GND are recommended.                                                                  |

| 6       | DRVL     | Drive Output for the External Lower Side, N-Channel MOSFET. This pin also serves as the current-sense gain setting pin (see Figure 68).                                                                                                                                          |

| 7       | PGND     | Power GND. Ground for the lower side gate driver and lower side, N-channel MOSFET.                                                                                                                                                                                               |

| 8       | DRVH     | Drive Output for the External Upper Side, N-Channel MOSFET.                                                                                                                                                                                                                      |

| 9       | SW       | Switch Node Connection.                                                                                                                                                                                                                                                          |

| 10      | BST      | Bootstrap for the Upper Side MOSFET Gate Drive Circuitry. An internal boot rectifier (diode) is connected between VDD and BST. A capacitor from BST to SW is required. An external Schottky diode can also be connected between VDD and BST for increased gate drive capability. |

### TYPICAL PERFORMANCE CHARACTERISTICS

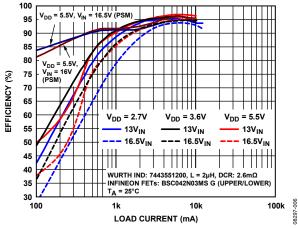

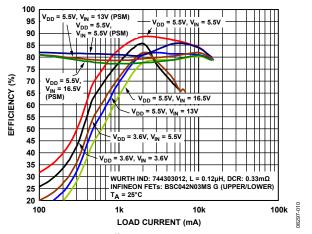

Figure 4. Efficiency—300 kHz,  $V_{OUT} = 0.8 V$

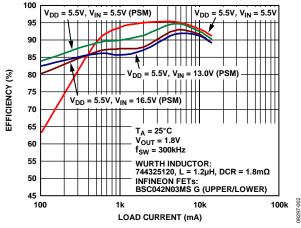

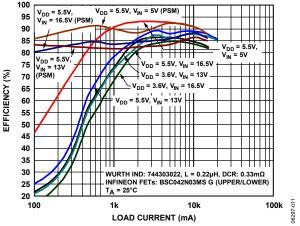

Figure 5. Efficiency—300 kHz,  $V_{OUT} = 1.8 \text{ V}$

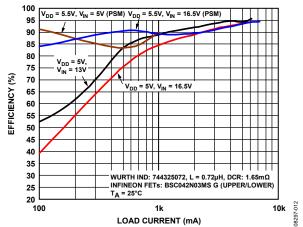

Figure 6. Efficiency—300 kHz, V<sub>OUT</sub> = 7 V

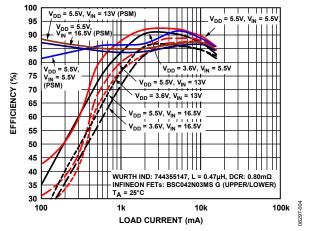

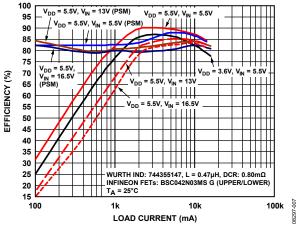

Figure 7. Efficiency—600 kHz,  $V_{OUT} = 0.8 \text{ V}$

Figure 8. Efficiency—600 kHz,  $V_{OUT} = 1.8 \text{ V}$

Figure 9. Efficiency—600 kHz, V<sub>OUT</sub> = 5 V

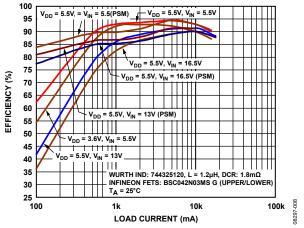

Figure 10. Efficiency—1.0 MHz,  $V_{OUT} = 0.8 \text{ V}$

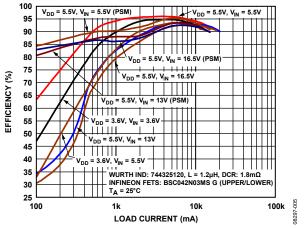

Figure 11. Efficiency—1.0 MHz, V<sub>OUT</sub> = 1.8 V

Figure 12. Efficiency—1.0 MHz,  $V_{OUT} = 4 V$

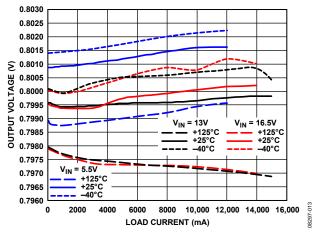

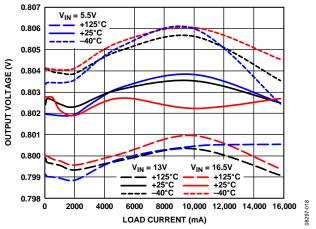

Figure 13. Output Voltage Accuracy—300 kHz, Vout = 0.8 V

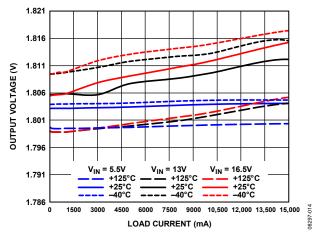

Figure 14. Output Voltage Accuracy—300 kHz, V<sub>OUT</sub> = 1.8 V

Figure 15. Output Voltage Accuracy—300 kHz, Vout = 7 V

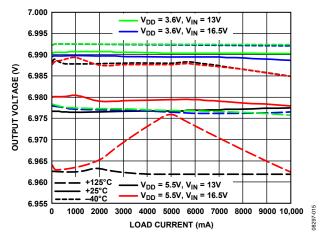

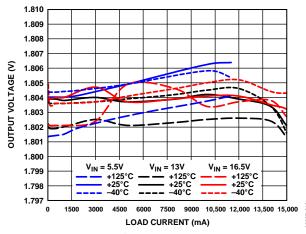

Figure 16. Output Voltage Accuracy—600 kHz, Vout = 1.8 V

Figure 17. Output Voltage Accuracy—600 kHz, V<sub>OUT</sub> = 5 V

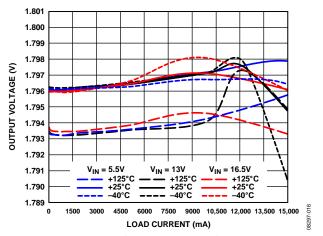

Figure 18. Output Voltage Accuracy—1 MHz,  $V_{OUT} = 0.8 \text{ V}$

Figure 19. Output Voltage Accuracy—1.0 MHz, V<sub>OUT</sub> = 1.8 V

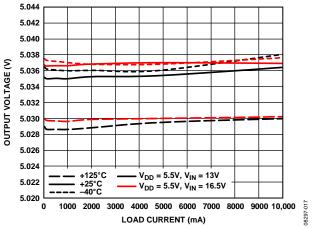

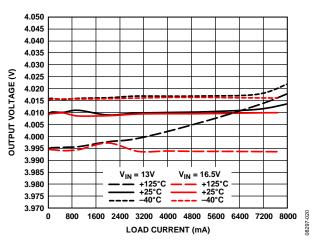

Figure 20. Output Voltage Accuracy—1.0 MHz,  $V_{OUT} = 4 V$

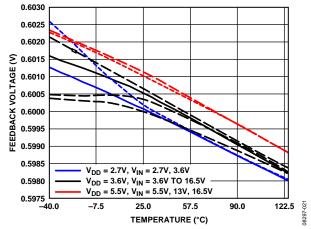

Figure 21. Feedback Voltage vs. Temperature

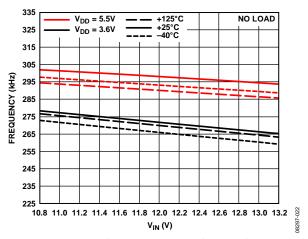

Figure 22. Switching Frequency vs. High Input Voltage,  $300 \, \text{kHz}, \pm 10\% \, \text{of} \, 12 \, \text{V}$

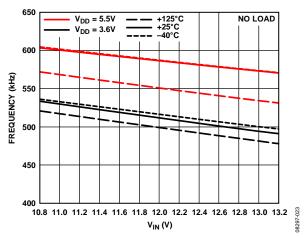

Figure 23. Switching Frequency vs. High Input Voltage, 600 kHz,  $V_{\text{OUT}} = 1.8 \text{ V}$ ,  $\pm 10\% \text{ of } 12 \text{ V}$

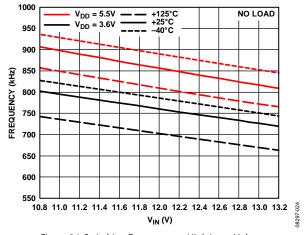

Figure 24. Switching Frequency vs. High Input Voltage,  $1.0 \, \text{MHz}, \pm 10\% \, \text{of} \, 12 \, \text{V}$

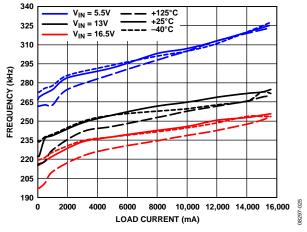

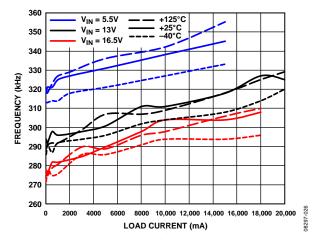

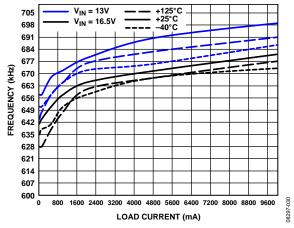

Figure 25. Frequency vs. Load Current, 300 kHz,  $V_{OUT} = 0.8 \text{ V}$

Figure 26. Frequency vs. Load Current, 300 kHz,  $V_{OUT} = 1.8 \text{ V}$

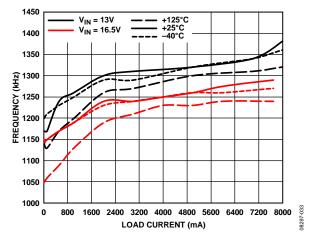

Figure 27. Frequency vs. Load Current, 300 kHz,  $V_{OUT} = 7 V$

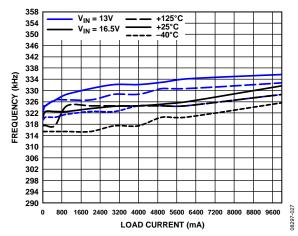

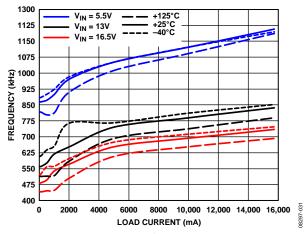

Figure 28. Frequency vs. Load Current, 600 kHz,  $V_{OUT} = 0.8 \text{ V}$

Figure 29. Frequency vs. Load Current, 600 kHz,  $V_{OUT} = 1.8 \text{ V}$

Figure 30. Frequency vs. Load Current, 600 kHz,  $V_{OUT} = 5 V$

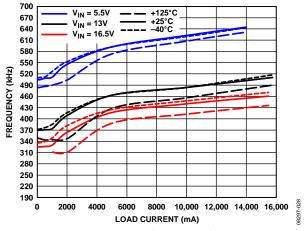

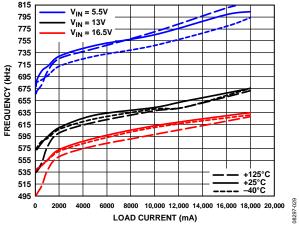

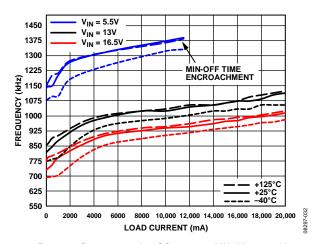

Figure 31. Frequency vs. Load Current,  $V_{OUT} = 1.0 \text{ MHz}$ , 0.8 V

Figure 32. Frequency vs. Load Current, 1.0 MHz,  $V_{OUT} = 1.8 \text{ V}$

Figure 33. Frequency vs. Load Current, 1.0 MHz,  $V_{OUT} = 4 V$

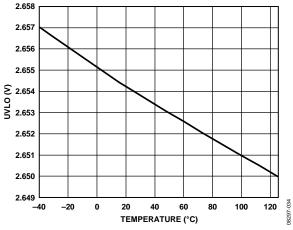

Figure 34. UVLO vs. Temperature

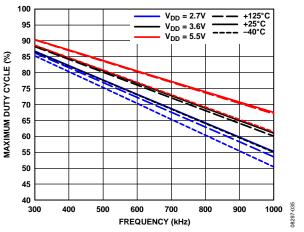

Figure 35. Maximum Duty Cycle vs. Frequency

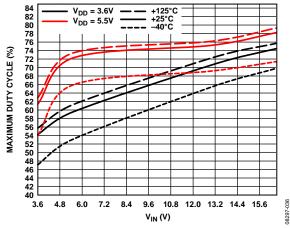

Figure 36. Maximum Duty Cycle vs. High Voltage Input (V<sub>IN</sub>)

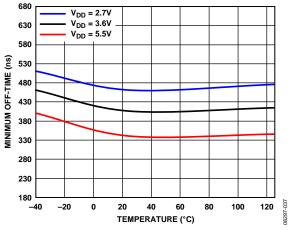

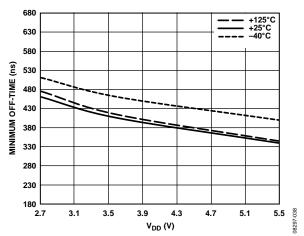

Figure 37. Minimum Off-Time vs. Temperature

Figure 38. Minimum Off-Time vs. V<sub>DD</sub> (Low Input Voltage)

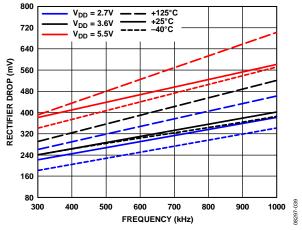

Figure 39. Internal Rectifier Drop vs. Frequency

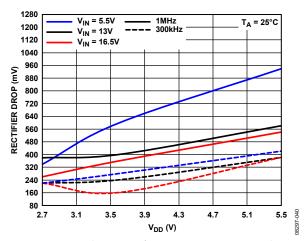

Figure 40. Internal Boost Rectifier Drop vs. V<sub>DD</sub> (Low Input Voltage) over VIN Variation

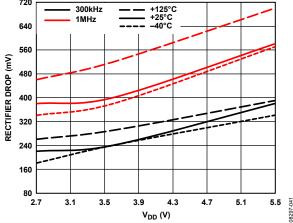

Figure 41. Internal Boost Rectifier Drop vs. V<sub>DD</sub>

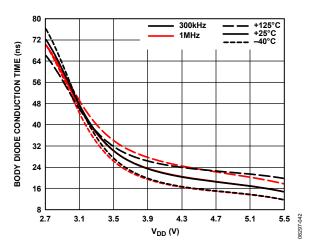

Figure 42. Lower Side MOSFET Body Conduction Time vs.  $V_{\rm DD}$  (Low Input Voltage)

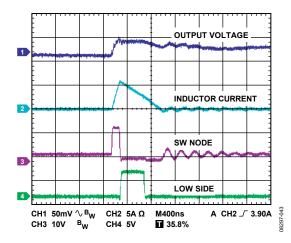

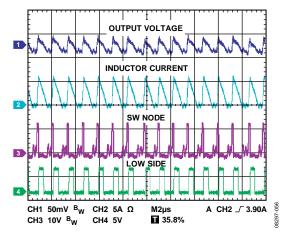

Figure 43. Power Saving Mode (PSM) Operational Waveform, 100 mA

Figure 44. PSM Waveform at Light Load, 500 mA

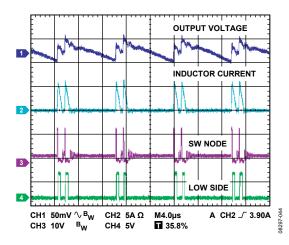

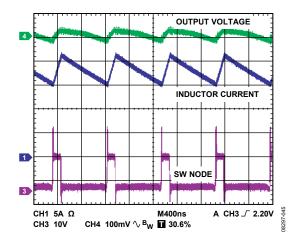

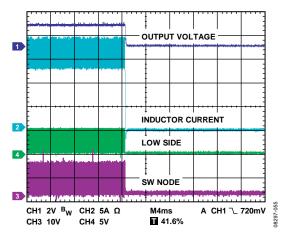

Figure 45. CCM Operation at Heavy Load, 18 A (See Figure 91 for Application Circuit)

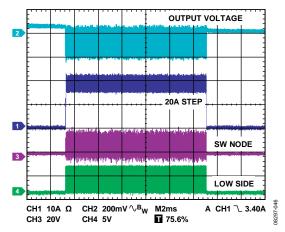

Figure 46. Load Transient Step—PSM Enabled, 20 A (See Figure 91 Application Circuit)

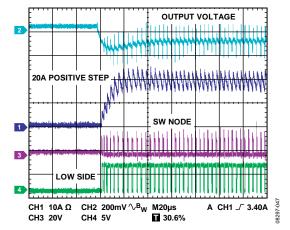

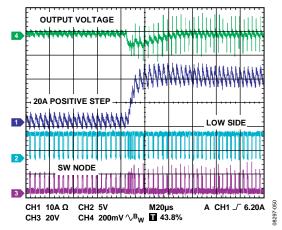

Figure 47. Positive Step During Heavy Load Transient Behavior—PSM Enabled, 20 A,  $V_{OUT} = 1.8 V$  (See Figure 91 Application Circuit)

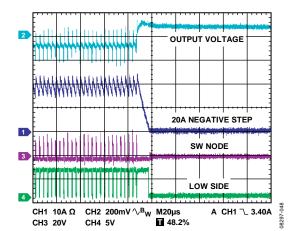

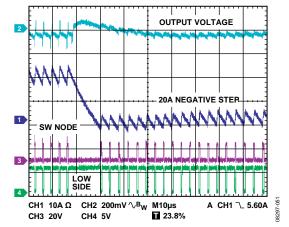

Figure 48. Negative Step During Heavy Load Transient Behavior—PSM Enabled, 20 A (See Figure 91 Application Circuit)

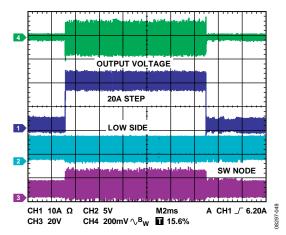

Figure 49. Load Transient Step—Forced PWM at Light Load, 20 A (See Figure 91 Application Circuit)

Figure 50. Positive Step During Heavy Load Transient Behavior—Forced PWM at Light Load, 20 A,  $V_{OUT} = 1.8 \text{ V}$  (See Figure 91 Application Circuit)

Figure 51. Negative Step During Heavy Load Transient Behavior—Forced PWM at Light Load, 20 A (See Figure 91 Application Circuit)

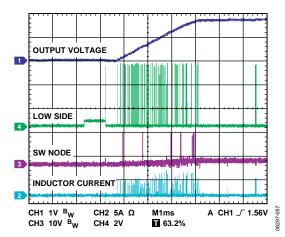

Figure 52. Output Short-Circuit Behavior Leading to Hiccup Mode

Figure 53. Magnified Waveform During Hiccup Mode

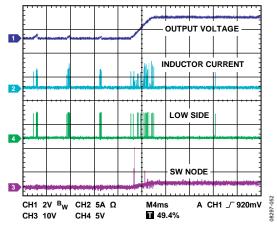

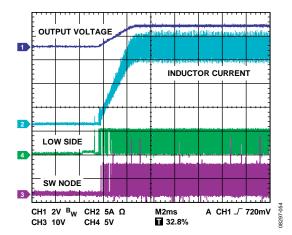

Figure 54. Start-Up Behavior at Heavy Load, 18 A, 300 kHz (See Figure 91 Application Circuit)

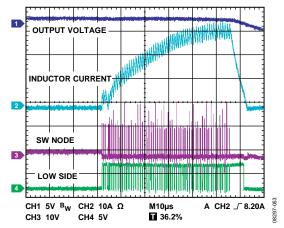

Figure 55. Power-Down Waveform During Heavy Load

Figure 56. Output Voltage Ripple Waveform During PSM Operation at Light Load, 2 A

Figure 57. Soft Start and RES Detect Waveform

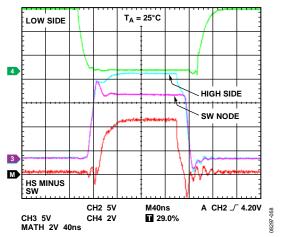

Figure 58. Output Drivers and SW Node Waveforms

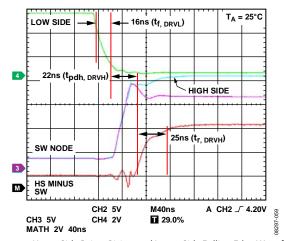

Figure 59. Upper Side Driver Rising and Lower Side Falling Edge Waveforms  $(C_{GATE} = 4.3 \text{ nF (Upper/Lower Side MOSFET)}, Q_{TOTAL} = 27 \text{ nC } (V_{GS} = 4.4 \text{ V } (Q1), V_{GS} = 5 \text{ V } (Q3))$

Figure 60. Upper Side Driver Falling and Lower Side Rising Edge Waveforms  $(C_{GATE} = 4.3 \text{ nF (Upper/Lower Side MOSFET)}, Q_{TOTAL} = 27 \text{ nC } (V_{GS} = 4.4 \text{ V } (Q1), V_{GS} = 5 \text{ V } (Q3))$

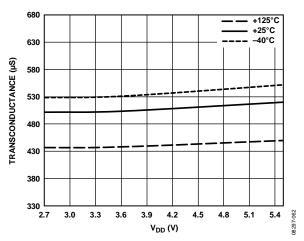

Figure 61. Transconductance (G<sub>M</sub>) vs. Temperature

Figure 62. Transconductance (G<sub>M</sub>) vs. V<sub>DD</sub>

Figure 63. Quiescent Current vs.  $V_{DD}$  (VIN = 13 V)

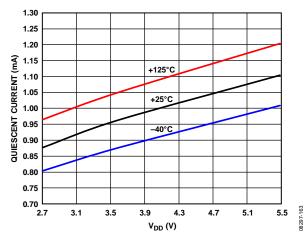

## ADP1872/ADP1873 BLOCK DIGRAM

Figure 64. ADP1872/ADP1873 Block Diagram

#### THEORY OF OPERATION

The ADP1872/ADP1873 are versatile current-mode, synchronous step-down controllers that provide superior transient response, optimal stability, and current limit protection by using a constant on-time, pseudo-fixed frequency with a programmable current-sense gain, current-control scheme. In addition, these devices offer optimum performance at low duty cycles by using valley current-mode control architecture. This allows the ADP1872/ADP1873 to drive all N-channel power stages to regulate output voltages as low as 0.6 V.

#### **STARTUP**

The ADP1872/ADP1873 have an input low voltage pin (VDD) for biasing and supplying power for the integrated MOSFET drivers. A bypass capacitor should be located directly across the VDD (Pin 5) and PGND (Pin 7) pins. Included in the power-up sequence is the biasing of the current-sense amplifier, the current-sense gain circuit (see the Programming Resistor (RES) Detect Circuit section), the soft start circuit, and the error amplifier.

The current-sense blocks provide valley current information (see the Programming Resistor (RES) Detect Circuit section) and are a variable of the compensation equation for loop stability (see the Compensation Network section). The valley current information is extracted by forcing 0.4 V across the DRVL output and the PGND pin, which generates a current depending on the resistor across DRVL and PGND in a process performed by the RES detect circuit. The current through the resistor is used to set the current-sense amplifier gain. This process takes approximately 800 µs, after which the drive signal pulses appear at the DRVL and DRVH pins synchronously and the output voltage begins to rise in a controlled manner through the soft start sequence.

The rise time of the output voltage is determined by the soft start and error amplifier blocks (see the Soft Start section). At the beginning of a soft start, the error amplifier charges the external compensation capacitor, causing the COMP/EN pin to rise above the enable threshold of 285 mV, thus enabling the ADP1872/ADP1873.

#### **SOFT START**

The ADP1872/ADP1873 have digital soft start circuitry, which involves a counter that initiates an incremental increase in current, by 1  $\mu$ A, via a current source on every cycle through a fixed internal capacitor. The output tracks the ramping voltage by producing PWM output pulses to the upper side MOSFET. The purpose is to limit the in-rush current from the high voltage input supply (VIN) to the output (Vout).

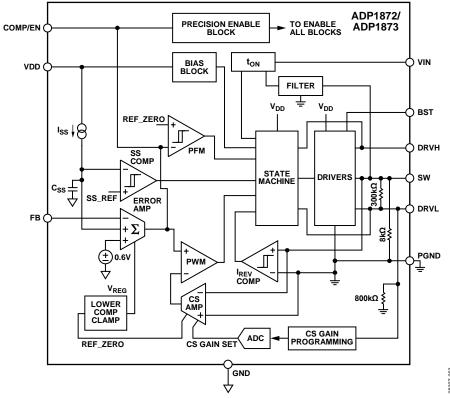

#### PRECISION ENABLE CIRCUITRY

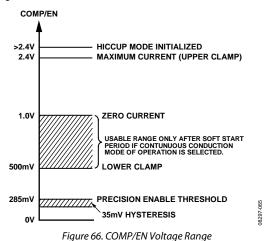

The ADP1872/ADP1873 employ precision enable circuitry. The enable threshold is 285 mV typical with 35 mV of hysteresis. The devices are enabled when the COMP/EN pin is released, allowing the error amplifier output to rise above the enable threshold (see Figure 65). Grounding this pin disables the ADP1872/ADP1873, reducing the supply current of the devices to approximately 140  $\mu A$ . For more information, see Figure 66.

Figure 65. Release COMP/EN Pin to Enable the ADP1872/ADP1873

#### **UNDERVOLTAGE LOCKOUT**

The undervoltage lockout (UVLO) feature prevents the part from operating both the upper side and lower side MOSFETs at extremely low or undefined input voltage (VDD) ranges. Operation at an undefined bias voltage may result in the incorrect propagation of signals to the high-side power switches. This, in turn, results in invalid output behavior that can cause damage to the output devices, ultimately destroying the device tied at the output. The UVLO level has been set at 2.65 V (nominal).

#### THERMAL SHUTDOWN

The thermal shutdown is a self-protection feature to prevent the IC from damage due to a very high operating junction temperature. If the junction temperature of the device exceeds 155°C, the part enters the thermal shutdown state. In this state, the device shuts off both the upper side and lower side MOSFETs and disables the entire controller immediately, thus reducing the power consumption of the IC. The part resumes operation after the junction temperature of the part cools to less than 140°C.

#### PROGRAMMING RESISTOR (RES) DETECT CIRCUIT

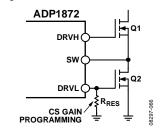

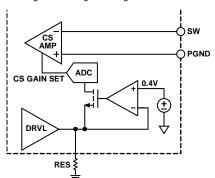

Upon startup, one of the first blocks to become active is the RES detect circuit. This block powers up before soft start begins. It forces a 0.4 V reference value at the DRVL output (see Figure 67) and is programmed to identify four possible resistor values: 47 k $\Omega$ , 22 k $\Omega$ , open, and 100 k $\Omega$ .

The RES detect circuit digitizes the value of the resistor at the DRVL pin (Pin 6). An internal ADC outputs a 2-bit digital code that is used to program four separate gain configurations in the current-sense amplifier (see Figure 68). Each configuration corresponds to a current-sense gain (A<sub>CS</sub>) of 3 V/V, 6 V/V, 12 V/V, 24 V/V, respectively (see Table 5 and Table 6). This variable is used for the valley current-limit setting, which sets up the appropriate current-sense gain for a given application and sets the compensation necessary to achieve loop stability (see the Valley Current-Limit Setting and Compensation Network sections).

Figure 67. Programming Resistor Location

Figure 68. RES Detect Circuit for Current-Sense Gain Programming

Table 5. Current-Sense Gain Programming

|                | 0 0                   |

|----------------|-----------------------|

| Resistor       | A <sub>cs</sub> (V/V) |

| 47 kΩ          | 3                     |

| 22 kΩ          | 6                     |

| Open<br>100 kΩ | 12                    |

| 100 kΩ         | 24                    |

#### **VALLEY CURRENT-LIMIT SETTING**

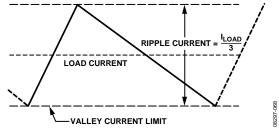

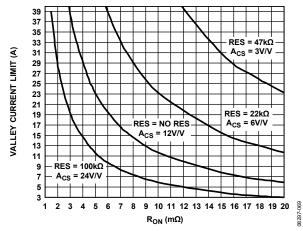

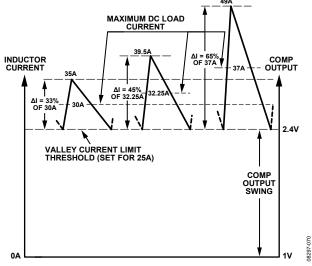

The architecture of the ADP1872/ADP1873 is based on valley current-mode control. The current limit is determined by three components: the  $R_{\text{ON}}$  of the lower side MOSFET, the error amplifier output voltage swing (COMP), and the current-sense gain. The COMP range is internally fixed at 1.4~V. The current-sense gain is programmable via an external resistor at the DRVL pin (see the Programming Resistor (RES) Detect Circuit section). The  $R_{\text{ON}}$  of the lower side MOSFET can vary over temperature and usually has a positive  $T_{\text{C}}$  (meaning that it increases with temperature); therefore, it is recommended to program the current-sense gain resistor based on the rated  $R_{\text{ON}}$  of the MOSFET at  $125^{\circ}\text{C}$ .

Because the ADP1872/ADP1873 are based on valley current control, the relationship between  $I_{\text{CLIM}}$  and  $I_{\text{LOAD}}$  is

$$I_{CLIM} = I_{LOAD} \times \left(1 - \frac{K_I}{2}\right)$$

where

$I_{CLIM}$  is the desired valley current limit.

$I_{LOAD}$  is the current load.

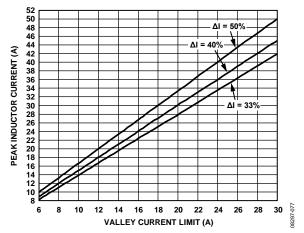

$K_I$  is the ratio between the inductor ripple current and the desired average load current (see Figure 10). Establishing  $K_I$  helps to determine the inductor value (see the Inductor Selection section), but in most cases,  $K_I = 0.33$ .

Figure 69. Valley Current Limit to Average Current Relation

When the desired valley current limit ( $I_{\text{CLIM}}$ ) has been determined, the current-sense gain can be calculated by

$$I_{CLIM} = \frac{1.4 \text{ V}}{A_{CS} \times R_{ON}}$$

where:

$A_{CS}$  is the current-sense gain multiplier (see Table 5 and Table 6).  $R_{ON}$  is the channel impedance of the lower side MOSFET.

Although the ADP1872/ADP1873 have only four discrete current-sense gain settings for a given  $R_{\rm ON}$  variable, Table 6 and Figure 70 outline several available options for the valley current setpoint based on various  $R_{\rm ON}$  values.

Table 6. Valley Current Limit Program<sup>1</sup>

|             | Valley Current Level     |                          |                           |                           |  |  |  |  |

|-------------|--------------------------|--------------------------|---------------------------|---------------------------|--|--|--|--|

| Ron         | 47 kΩ                    | 22 kΩ                    | Open                      | 100 kΩ                    |  |  |  |  |

| $(m\Omega)$ | $A_{CS} = 3 \text{ V/V}$ | $A_{CS} = 6 \text{ V/V}$ | $A_{CS} = 12 \text{ V/V}$ | $A_{CS} = 24 \text{ V/V}$ |  |  |  |  |

| 1.5         |                          |                          |                           | 38.9                      |  |  |  |  |

| 2           |                          |                          |                           | 29.2                      |  |  |  |  |

| 2.5         |                          |                          |                           | 23.3                      |  |  |  |  |

| 3           |                          |                          | 39.0                      | 19.5                      |  |  |  |  |

| 3.5         |                          |                          | 33.4                      | 16.7                      |  |  |  |  |

| 4.5         |                          |                          | 26.0                      | 13                        |  |  |  |  |

| 5           |                          |                          | 23.4                      | 11.7                      |  |  |  |  |

| 5.5         |                          |                          | 21.25                     | 10.6                      |  |  |  |  |

| 10          |                          | 23.3                     | 11.7                      | 5.83                      |  |  |  |  |

| 15          | 31.0                     | 15.5                     | 7.75                      | 3.87                      |  |  |  |  |

| 18          | 26.0                     | 13.0                     | 6.5                       | 3.25                      |  |  |  |  |

<sup>&</sup>lt;sup>1</sup> Refer to Figure 70 for more information and a graphical representation.

Figure 70. Valley Current-Limit Value vs. R<sub>ON</sub> of the Lower Side MOSFET for Each Programming Resistor (RES)

The valley current limit is programmed as outlined in Table 6 and Figure 70. The inductor chosen must be rated to handle the peak current, which is equal to the valley current from Table 6 plus the peak-to-peak inductor ripple current (see the Inductor Selection section). In addition, the peak current value must be used to compute the worst-case power dissipation in the MOSFETs (see Figure 71).

Figure 71. Valley Current-Limit Threshold in Relation to Inductor Ripple Current

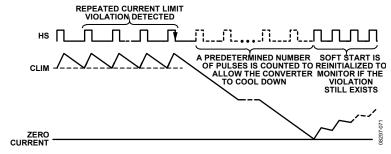

#### HICCUP MODE DURING SHORT CIRCUIT

A current-limit violation occurs when the current across the source and drain of the lower side MOSFET exceeds the current-limit setpoint. When 32 current-limit violations are detected, the controller enters idle mode and turns off the MOSFETs for 6 ms, allowing the converter to cool down. Then, the controller re-establishes soft start and begins to cause the output to ramp up again (see Figure 72). While the output ramps up, COMP is monitored to determine if the violation is still present. If it is still present, the idle event occurs again, followed by the full-chip power-down sequence. This cycle continues until the violation no longer exists. If the violation disappears, the converter is allowed to switch normally, maintaining regulation.

Figure 72. Idle Mode Entry Sequence Due to Current-Limit Violations

#### SYNCHRONOUS RECTIFIER

The ADP1872/ADP1873 employ an internal lower side MOSFET driver to drive the external upper side and lower side MOSFETs. The synchronous rectifier not only improves overall conduction efficiency but also ensures proper charging to the bootstrap capacitor located at the upper side driver input. This is beneficial during startup to provide sufficient drive signal to the external upper side MOSFET and attain fast turn-on response, which is essential for minimizing switching losses. The integrated upper and lower side MOSFET drivers operate in complementary fashion with built-in anticross conduction circuitry to prevent unwanted shoot-through current that may potentially damage the MOSFETs or reduce efficiency as a result of excessive power loss.

#### **POWER SAVING MODE (PSM) VERSION (ADP1873)**

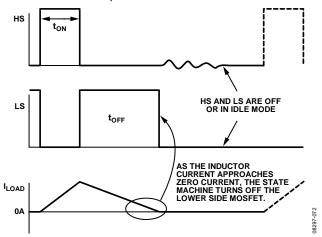

The power saving mode version of the ADP1872 is the ADP1873. The ADP1873 operates in the discontinuous conduction mode (DCM) and pulse skips at light load to midload currents. It outputs pulses as necessary to maintain output regulation. Unlike the continuous conduction mode (CCM), DCM operation prevents negative current, thus allowing improved system efficiency at light loads. Current in the reverse direction through this pathway, however, results in power dissipation and therefore a decrease in efficiency.

Figure 73. Discontinuous Mode of Operation (DCM)

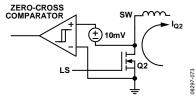

To minimize the chance of negative inductor current buildup, an on-board, zero-cross comparator turns off all upper side and lower side switching activities when the inductor current approaches the zero current line, causing the system to enter idle mode, where the upper side and lower side MOSFETs are turned off. To ensure idle mode entry, a 10 mV offset, connected in series at the SW node, is implemented (see Figure 74).

Figure 74. Zero-Cross Comparator with 10 mV of Offset

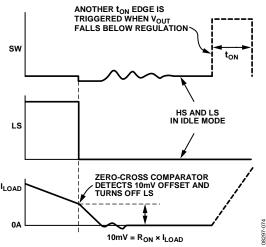

As soon as the forward current through the lower side MOSFET decreases to a level where

$$10 \text{ mV} = I_{Q2} \times R_{ON(Q2)}$$

the zero-cross comparator (or I<sub>REV</sub> comparator) emits a signal to turn off the lower side MOSFET. From this point, the slope of the inductor current ramping down becomes steeper (see Figure 75) as the body diode of the lower side MOSFET begins to conduct current and continues conducting current until the remaining energy stored in the inductor has been depleted.

Figure 75. 10 mV Offset to Ensure Prevention of Negative Inductor Current

The system remains in idle mode until the output voltage drops below regulation. A PWM pulse is then produced, turning on the upper side MOSFET to maintain system regulation. The ADP1873 does not have an internal clock; therefore, it switches purely as a hysteretic controller, as described in this section.

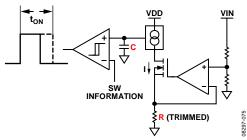

#### **TIMER OPERATION**

The ADP1872/ADP1873 employ a constant on-time architecture, which provides a variety of benefits, including improved load and line transient response when compared with a constant (fixed) frequency current-mode control loop of comparable loop design. The constant on-time timer, or  $t_{\rm ON}$  timer, senses the high input voltage (VIN) and the output voltage (V\_{OUT}) using SW waveform information to produce an adjustable one-shot PWM pulse that varies the on-time of the upper side MOSFET in response to dynamic changes in input voltage, output voltage, and load current conditions to maintain regulation. It then generates an on-time ( $t_{\rm ON}$ ) pulse that is inversely proportional to  $V_{\rm IN}$ .

$$t_{ON} = K \times \frac{V_{OUT}}{VIN}$$

where *K* is a constant that is trimmed using an RC timer product for the 300 kHz, 600 kHz, and 1.0 MHz frequency options.

Figure 76. Constant On-Time Timer

The constant on-time (ton) is not strictly constant because it varies with VIN and  $V_{\text{OUT}}$ . However, this variation occurs in such a way as to keep the switching frequency virtually independent of VIN and Vout.

The ton timer uses a feedforward technique, applied to the constant on-time control loop, making it pseudo-fixed frequency to a first order. Second-order effects, such as dc losses in the external power MOSFETs (see the Efficiency Consideration section), cause some variation in frequency vs. load current and line voltage. These effects are shown in Figure 22 to Figure 33. The variations in frequency are much reduced compared with the variations generated when the feedforward technique is not used.

The feedforward technique establishes the following relationship:

$$f_{SW} = 1/K$$

where f<sub>SW</sub> is the controller switching frequency (300 kHz, 600 kHz, and 1.0 MHz).

The ton timer senses VIN and Vout to minimize frequency variation with VIN and V<sub>OUT</sub> as previously explained. This provides a pseudo-fixed frequency, see the Pseudo-Fixed Frequency section for additional information. To allow headroom for VIN/Vout sensing, the following two equations must be adhered to. For typical applications where V<sub>DD</sub> is 5 V, these equations are not relevant; however, for lower VDD, care may be required.

$V_{DD} \ge VIN/8 + 1.5$

$V_{DD} \ge V_{OUT}/4$

#### **PSEUDO-FIXED FREOUENCY**

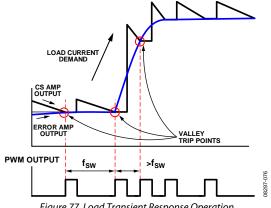

The ADP1872/ADP1873 employ a constant on-time control scheme. During steady state operation, the switching frequency stays relatively constant, or pseudo-fixed. This is due to the oneshot  $t_{\mathrm{ON}}$  timer that produces a high-side PWM pulse with a fixed duration, given that external conditions such as input voltage, output voltage, and load current are also at steady state. During load transients, the frequency momentarily changes for the duration of the transient event so that the output comes back within regulation quicker than if the frequency were fixed or if it were to remain unchanged. After the transient event is complete, the frequency returns to a pseudo-fixed value to a first-order.

To illustrate this feature more clearly, this section describes one such load transient event—a positive load step—in detail. During load transient events, the high-side driver output pulse width stays relatively consistent from cycle to cycle; however, the off-time (DRVL on-time) dynamically adjusts according to the instantaneous changes in the external conditions mentioned.

When a positive load step occurs, the error amplifier (out of phase of the output, V<sub>OUT</sub>) produces new voltage information at its output (COMP). In addition, the current-sense amplifier senses new inductor current information during this positive load transient event. The error amplifier's output voltage reaction is compared to the new inductor current information that sets the start of the next switching cycle. Because current information is produced from valley current sensing, it is sensed at the down ramp of the inductor current, whereas the voltage loop information is sensed through the counter action upswing of the error amplifier's output (COMP).

The result is a convergence of these two signals (see Figure 77), which allows an instantaneous increase in switching frequency during the positive load transient event. In summary, a positive load step causes V<sub>OUT</sub> to transient down, which causes COMP to transient up and therefore shortens the off time. This resulting increase in frequency during a positive load transient helps to quickly bring V<sub>OUT</sub> back up in value and within the regulation window.

Similarly, a negative load step causes the off time to lengthen in response to  $V_{\text{OUT}}$  rising. This effectively increases the inductor demagnetizing phase, helping to bring V<sub>OUT</sub> to within regulation. In this case, the switching frequency decreases, or experiences a foldback, to help facilitate output voltage recovery.

Because the ADP1872/ADP1873 has the ability to respond rapidly to sudden changes in load demand, the recovery period in which the output voltage settles back to its original steady state operating point is much quicker than it would be for a fixed-frequency equivalent. Therefore, using a pseudo-fixed frequency, results in significantly better load transient performance than using a fixed frequency.

Figure 77. Load Transient Response Operation

#### APPLICATIONS INFORMATION

#### **FEEDBACK RESISTOR DIVIDER**

The required resistor divider network can be determine for a given  $V_{\text{OUT}}$  value because the internal band gap reference ( $V_{\text{REF}}$ ) is fixed at 0.6 V. Selecting values for  $R_T$  and  $R_B$  determines the minimum output load current of the converter. Therefore, for a given value of  $R_B$ , the  $R_T$  value can be determined by

$$R_T = R_B \times \frac{(V_{OUT} - 0.6 \text{ V})}{0.6 \text{ V}}$$

#### INDUCTOR SELECTION

The inductor value is inversely proportional to the inductor ripple current. The peak-to-peak ripple current is given by

$$\Delta I_L = K_I \times I_{LOAD} \approx \frac{I_{LOAD}}{3}$$

where  $K_I$  is typically 0.33.

The equation for the inductor value is given by

$$L = \frac{(VIN - V_{OUT})}{\Delta I_L \times f_{SW}} \times \frac{V_{OUT}}{VIN}$$

where:

VIN is the high voltage input.

$V_{OUT}$  is the desired output voltage.

$f_{SW}$  is the controller switching frequency (300 kHz, 600 kHz, and 1.0 MHz).

When selecting the inductor, choose an inductor saturation rating that is above the peak current level and then calculate the inductor current ripple (see the Valley Current-Limit Setting section and Figure 78).

Figure 78. Peak Current vs. Valley Current Threshold for 33%, 40%, and 50% of Inductor Ripple Current

**Table 7. Recommended Inductors**

| L<br>(µH) | DCR<br>(mΩ) | I <sub>SAT</sub> (A) | Dimensions<br>(mm) | Manufacturer     | Model No.   |

|-----------|-------------|----------------------|--------------------|------------------|-------------|

| 0.12      | 0.33        | 55                   | 10.2 × 7           | Würth Elektronic | 744303012   |

| 0.22      | 0.33        | 30                   | 10.2 × 7           | Würth Elektronic | 744303022   |

| 0.47      | 0.8         | 50                   | 14.2 × 12.8        | Würth Elektronic | 744355147   |

| 0.72      | 1.65        | 35                   | 10.5 × 10.2        | Würth Elektronic | 744325072   |

| 0.9       | 1.6         | 28                   | 13 × 12.8          | Würth Elektronic | 744355090   |

| 1.2       | 1.8         | 25                   | $10.5 \times 10.2$ | Würth Elektronic | 744325120   |

| 1.0       | 3.3         | 20                   | $10.5 \times 10.2$ | Würth Elektronic | 7443552100  |

| 1.4       | 3.2         | 24                   | 14 × 12.8          | Würth Elektronic | 744318180   |

| 2.0       | 2.6         | 22                   | 13.2 × 12.8        | Würth Elektronic | 7443551200  |

| 0.8       |             | 27.5                 |                    | Sumida           | CEP125U-0R8 |

#### **OUTPUT RIPPLE VOLTAGE (ΔV<sub>RR</sub>)**

The output ripple voltage is the ac component of the dc output voltage during steady state. For a ripple error of 1.0%, the output capacitor value needed to achieve this tolerance can be determined using the following equation. (Note that an accuracy of 1.0% is only possible during steady state conditions, not during load transients.)

$$\Delta V_{RR} = (0.01) \times V_{OUT}$$

#### **OUTPUT CAPACITOR SELECTION**

The primary objective of the output capacitor is to facilitate the reduction of the output voltage ripple; however, the output capacitor also assists in the output voltage recovery during load transient events. For a given load current step, the output voltage ripple generated during this step event is inversely proportional to the value chosen for the output capacitor. The speed at which the output voltage settles during this recovery period depends on where the crossover frequency (loop bandwidth) is set. This crossover frequency is determined by the output capacitor, the equivalent series resistance (ESR) of the capacitor, and the compensation network.

To calculate the small signal voltage ripple (output ripple voltage) at the steady state operating point, use the following equation:

$$C_{OUT} = \Delta I_L \times \left( \frac{1}{8 \times f_{SW} \times \left[ \Delta V_{RIPPLE} - (\Delta I_L \times ESR) \right]} \right)$$

where *ESR* is the equivalent series resistance of the output capacitors.

To calculate the output load step, use the following equation:

$$C_{OUT} = 2 \times \frac{\Delta I_{LOAD}}{f_{SW} \times (\Delta V_{DROOP} - (\Delta I_{LOAD} \times ESR))}$$

where  $\Delta V_{DROOP}$  is the amount that  $V_{OUT}$  is allowed to deviate for a given positive load current step ( $\Delta I_{LOAD}$ ).

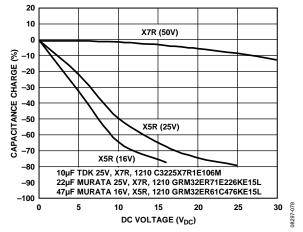

Ceramic capacitors are known to have low ESR. However, the trade-off of using X5R technology is that up to 80% of its capacitance may be lost due to derating because the voltage applied across the capacitor is increased (see Figure 79). Although X7R series capacitors can also be used, the available selection is limited to only up to 22  $\mu E$ .

Figure 79. Capacitance vs. DC Voltage Characteristics for Ceramic Capacitors

Electrolytic capacitors satisfy the bulk capacitance requirements for most high current applications. Because the ESR of electrolytic capacitors is much higher than that of ceramic capacitors, when using electrolytic capacitors, several MLCCs should be mounted in parallel to reduce the overall series resistance.

#### **COMPENSATION NETWORK**

Due to its current-mode architecture, the ADP1872/ADP1873 require Type II compensation. To determine the component values needed for compensation (resistance and capacitance values), it is necessary to examine the converter's overall loop gain (H) at the unity gain frequency ( $f_{\rm SW}/10$ ) when H = 1 V/V.

$$H = 1 \text{ V/V} = G_M \times G_{CS} \times \frac{V_{OUT}}{V_{RFF}} \times Z_{COMP} \times Z_{FILT}$$

Examining each variable at high frequency enables the unity gain transfer function to be simplified to provide expressions for the  $R_{\text{COMP}}$  and  $C_{\text{COMP}}$  component values.

#### Output Filter Impedance (Z<sub>FILT</sub>)

Examining the filter's transfer function at high frequencies simplifies to

$$Z_{FILTER} = \frac{1}{sC_{OUT}}$$

at the crossover frequency (s =  $2\pi f_{CROSS}$ ).

#### Error Amplifier Output Impedance (Z<sub>COMP</sub>)

Assuming  $C_{C2}$  is significantly smaller than  $C_{COMP}$ ,  $C_{C2}$  can be omitted from the output impedance equation of the error amplifier. The transfer function simplifies to

$$Z_{COMP} = \frac{R_{COMP} (f_{CROSS} + f_{ZERO})}{f_{CROSS}}$$

and

$$f_{CROSS} = \frac{1}{12} \times f_{SW}$$

where  $f_{ZERO}$ , the zero frequency, is set to be  $1/4^{th}$  of the crossover frequency for the ADP1872.

#### Error Amplifier Gain (G<sub>M</sub>)

The error amplifier gain (transconductance) is

$$G_M = 500 \mu A/V$$

#### Current-Sense Loop Gain (G<sub>CS</sub>)

The current-sense loop gain is

$$G_{CS} = \frac{1}{A_{CS} \times R_{ON}} \text{ (A/V)}$$

where:

$A_{CS}$  (V/V) is programmable for 3 V/V, 6 V/V, 12 V/V, and 24 V/V (see the Programming Resistor (RES) Detect Circuit and Valley Current-Limit Setting sections).

$R_{ON}$  is the channel impedance of the lower side MOSFET.

#### **Crossover Frequency**

The crossover frequency is the frequency at which the overall loop (system) gain is 0 dB (H = 1 V/V). It is recommended for current-mode converters, such as the ADP1872, that the user set the crossover frequency between  $1/10^{th}$  and  $1/15^{th}$  of the switching frequency.

$$f_{CROSS} = \frac{1}{12} f_{SW}$$

The relationship between C<sub>COMP</sub> and f<sub>ZERO</sub> (zero frequency) is

$$f_{ZERO} = \frac{1}{2\pi \times R_{COMP} \times C_{COMP}}$$

The zero frequency is set to 1/4<sup>th</sup> of the crossover frequency. Combining all of the above parameters results in

$$R_{COMP} = \frac{f_{CROSS}}{f_{CROSS} + f_{ZERO}} \times \frac{2\pi f_{CROSS} C_{OUT}}{G_M G_{CS}} \times \frac{V_{OUT}}{V_{REF}}$$

$$C_{COMP} = \frac{1}{2 \times \pi \times R_{COMP} \times f_{ZEPO}}$$

#### **EFFICIENCY CONSIDERATION**

One of the important criteria to consider in constructing a dc-to-dc converter is efficiency. By definition, efficiency is the ratio of the output power to the input power. For high power applications at load currents up to 20 A, the following are important MOSFET parameters that aid in the selection process:

- V<sub>GS (TH)</sub>: the MOSFET support voltage applied between the gate and the source.

- R<sub>DS (ON)</sub>: the MOSFET on resistance during channel conduction.

- Q<sub>G</sub>: the total gate charge

- C<sub>N1</sub>: the input capacitance of the upper side switch

- $C_{N2}$ : the input capacitance of the lower side switch

The following are the losses experienced through the external component during normal switching operation:

- Channel conduction loss (both the MOSFETs)

- MOSFET driver loss

- MOSFET switching loss

- Body diode conduction loss (lower side MOSFET)

- Inductor loss (copper and core loss)

#### **Channel Conduction Loss**

During normal operation, the bulk of the loss in efficiency is due to the power dissipated through MOSFET channel conduction. Power loss through the upper side MOSFET is directly proportional to the duty cycle (D) for each switching period, and the power loss through the lower side MOSFET is directly proportional to 1 – D for each switching period. The selection of MOSFETs is governed by the amount of maximum dc load current that the converter is expected to deliver. In particular, the selection of the lower side MOSFET is dictated by the maximum load current because a typical high current application employs duty cycles of less than 50%. Therefore, the lower side MOSFET is in the on state for most of the switching period.

$$P_{\mathit{NI, N2\,(CL)}} = \left[D \times R_{\mathit{NI\,(ON)}} + (1-D) \times R_{\mathit{N2\,(ON)}}\right] \times \ I_{\mathit{LOAD}}^2$$

#### **MOSFET Driver Loss**

Other dissipative elements are the MOSFET drivers. The contributing factors are the dc current flowing through the driver during operation and the QGATE parameter of the external MOSFETs.

$$\begin{split} P_{DR(LOSS)} = & \left[ V_{DR} \times \left( f_{SW} C_{upperFET} V_{DR} + I_{BIAS} \right) \right] + \\ & \left[ V_{DD} \times \left( f_{SW} C_{lowerFET} V_{DD} + I_{BIAS} \right) \right] \end{split}$$

where

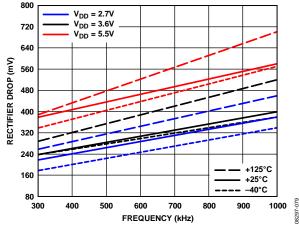

$C_{upperFET}$  is the input gate capacitance of the upper-side MOSFET.  $C_{lowerFET}$  is the input gate capacitance of the lower-side MOSFET.  $V_{DR}$  is the driver bias voltage (that is, the low input voltage (V<sub>DD</sub>) minus the rectifier drop (see Figure 80)).

$I_{BIAS}$  is the dc current flowing into the upper- and lower-side drivers.  $V_{DD}$  is the bias voltage.

Figure 80. Internal Rectifier Voltage Drop vs. Switching Frequency

#### **MOSFET Switching Loss**

The SW node transitions due to the switching activities of the upper side and lower side MOSFETs. This causes removal and replenishing of charge to and from the gate oxide layer of the MOSFET, as well as to and from the parasitic capacitance associated with the gate oxide edge overlap and the drain and source terminals. The current that enters and exits these charge paths presents additional loss during these transition times. This can be approximately quantified by using the following equation, which represents the time in which charge enters and exits these capacitive regions.

$$t_{SW-TRANS} = R_{GATE} \times C_{TOTAL}$$

where:

$R_{GATE}$  is the gate input resistance of the MOSFET.  $C_{TOTAL}$  is the  $C_{GD} + C_{GS}$  of the external MOSFET used.

The ratio of this time constant to the period of one switching cycle is the multiplying factor to be used in the following expression:

$$P_{SW(LOSS)} = \frac{t_{SW-TRANS}}{t_{SW}} \times I_{LOAD} \times VIN \times 2$$

or

$$P_{SW(LOSS)} = f_{SW} \times R_{GATE} \times C_{TOTAL} \times I_{LOAD} \times VIN \times 2$$

#### **Body Diode Conduction Loss**

The ADP1872/ADP1873 employ anticross conduction circuitry that prevents the upper side and lower side MOSFETs from conducting current simultaneously. This overlap control is beneficial, avoiding large current flow that may lead to irreparable damage to the external components of the power stage. However, this blanking period comes with the trade-off of a diode conduction loss occurring immediately after the MOSFETs change states and continuing well into idle mode. The amount of loss through the body diode of the lower side MOSFET during the antioverlap state is given by

$$P_{\textit{BODY(LOSS)}} = \frac{t_{\textit{BODY(LOSS)}}}{t_{\textit{SW}}} \times I_{\textit{LOAD}} \times V_{\textit{F}} \times 2$$

where:

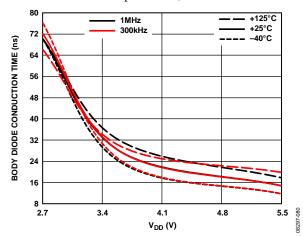

$t_{BODY(LOSS)}$  is the body conduction time (refer to Figure 81 for dead time periods).

$t_{SW}$  is the period per switching cycle.

$V_F$  is the forward drop of the body diode during conduction. (Refer to the selected external MOSFET data sheet for more information about the  $V_F$  parameter.)

Figure 81. Body Diode Conduction Time vs. Low Voltage Input (VDD)

#### **Inductor Loss**

During normal conduction mode, further power loss is caused by the conduction of current through the inductor windings, which have dc resistance (DCR). Typically, larger sized inductors have smaller DCR values.

The inductor core loss is a result of the eddy currents generated within the core material. These eddy currents are induced by the changing flux, which is produced by the current flowing through the windings. The amount of inductor core loss depends on the core material, the flux swing, the frequency, and the core volume. Ferrite inductors have the lowest core losses, whereas powdered iron inductors have higher core losses. It is recommended to use shielded ferrite core material type inductors with the ADP1872/ADP1873 for a high current, dc-to-dc switching application to achieve minimal loss and negligible electromagnetic interference (EMI).

$$P_{DCR (LOSS)} = DCR \times I_{LOAD}^2 + Core Loss$$

#### INPUT CAPACITOR SELECTION

The goal in selecting an input capacitor is to reduce or to minimize input voltage ripple and to reduce the high frequency source impedance, which is essential for achieving predictable loop stability and transient performance.

The problem with using bulk capacitors, other than their physical geometries, is their large equivalent series resistance (ESR) and large equivalent series inductance (ESL). Aluminum electrolytic capacitors have such high ESR that they cause undesired input voltage ripple magnitudes and are generally not effective at high switching frequencies.

If bulk capacitors are to be used, it is recommended to use multi-layered ceramic capacitors (MLCC) in parallel due to their low ESR values. This dramatically reduces the input voltage ripple amplitude as long as the MLCCs are mounted directly across the drain of the upper side MOSFET and the source terminal of the lower side MOSFET (see the Layout Considerations section). Improper placement and mounting of these MLCCs may cancel their effectiveness due to stray inductance and an increase in trace impedance.

$$\boldsymbol{I}_{CIN,RMS} = \boldsymbol{I}_{LOAD,MAX} \times \frac{\sqrt{\boldsymbol{V}_{OUT} \times \left(\boldsymbol{VIN} - \boldsymbol{V}_{OUT}\right)}}{\boldsymbol{V}_{OUT}}$$

The maximum input voltage ripple and maximum input capacitor rms current occur at the end of the duration of 1-D while the upper side MOSFET is in the off state. The input capacitor rms current reaches its maximum at time D. When calculating the maximum input voltage ripple, account for the ESR of the input capacitor as follows:

$$V_{MAX, RIPPLE} = V_{RIPP} + (I_{LOAD, MAX} \times ESR)$$

where:

$V_{\it RIPP}$  is usually 1% of the minimum voltage input.

*I<sub>LOAD, MAX* is the maximum load current.</sub>

*ESR* is the equivalent series resistance rating of the input capacitor used.

Inserting  $V_{\text{MAX,RIPPLE}}$  into the charge balance equation to calculate the minimum input capacitor requirement gives

$$C_{IN,min} = \frac{I_{LOAD, MAX}}{V_{MAX, RIPPLE}} \times \frac{D(1-D)}{f_{SW}}$$

or

$$C_{IN,min} = \frac{I_{LOAD, MAX}}{4 f_{SW} V_{MAX, RIPPLE}}$$

where D = 50%.

#### THERMAL CONSIDERATIONS

The ADP1872/ADP1873 are used for dc-to-dc, step down, high current applications that have an on-board controller and on-board MOSFET drivers. Because applications may require up to 20 A of load current delivery and be subjected to high ambient temperature surroundings, the selection of external upper side and lower side MOSFETs must be associated with careful thermal consideration to not exceed the maximum allowable junction temperature of 125°C. To avoid permanent or irreparable damage if the junction temperature reaches or exceeds 155°C, the part enters thermal shutdown, turning off both external MOSFETs, and does not re-enable until the junction temperature cools to 140°C (see the Thermal Shutdown section).

The maximum junction temperature allowed for the ADP1872/ADP1873 ICs is  $125^{\circ}$ C. This means that the sum of the ambient temperature ( $T_{\text{R}}$ ) and the rise in package temperature ( $T_{\text{R}}$ ), which is caused by the thermal impedance of the package and the internal power dissipation, should not exceed  $125^{\circ}$ C, as dictated by

$$T_I = T_R \times T_A$$

where:

$T_I$  is the maximum junction temperature.

$T_R$  is the rise in package temperature due to the power dissipated from within.

$T_A$  is the ambient temperature.

The rise in package temperature is directly proportional to its thermal impedance characteristics. The following equation represents this proportionality relationship:

$$T_R = \theta_{IA} \times P_{DR (LOSS)}$$

where:

$\theta_{JA}$  is the thermal resistance of the package from the junction to the outside surface of the die, where it meets the surrounding air.  $P_{DR \; (LOSS)}$  is the overall power dissipated by the IC.

The bulk of the power dissipated is due to the gate capacitance of the external MOSFETs. The power loss equation of the MOSFET drivers (see the MOSFET Driver Loss section in the Efficiency Consideration section) is

$$P_{DR (LOSS)} = [V_{DR} \times (f_{SW}C_{upperFET}V_{DR} + I_{BIAS})] + [V_{DD} \times (f_{SW}C_{lowerFET}V_{DD} + I_{BIAS})]$$

where

$C_{upperFET}$  is the input gate capacitance of the upper side MOSFET.  $C_{lowerFET}$  is the input gate capacitance of the lower side MOSFET.  $I_{BLAS}$  is the dc current (2 mA) flowing into the upper side and lower side drivers.

$V_{DR}$  is the driver bias voltage (that is, the low input voltage ( $V_{DD}$ ) minus the rectifier drop (see Figure 80)).

$V_{DD}$  is the bias voltage

For example, if the external MOSFET characteristics are  $\theta_{JA}$  (10-lead MSOP) = 171.2°C/W,  $f_{SW}$  = 300 kHz,  $I_{BIAS}$  = 2 mA,  $C_{upperFET}$  = 3.3 nF,  $C_{lowerFET}$  = 3.3 nF,  $V_{DR}$  = 5.12 V, and  $V_{DD}$  = 5.5 V, then the power loss is

$$P_{DR (LOSS)} = [V_{DR} \times (f_{SW}C_{upperFET}V_{DR} + I_{BIAS})] + [V_{DD} \times (f_{SW}C_{lowerFET}V_{DD} + I_{BIAS})]$$

$$= [5.12 \times (300 \times 10^{3} \times 3.3 \times 10^{-9} \times 5.12 + 0.002)] + [5.5 \times (300 \times 10^{3} \times 3.3 \times 10^{-9} \times 5.5 + 0.002)]$$

$$= 77.13 \text{ mW}$$

The rise in package temperature is

$$T_R = \theta_{JA} \times P_{DR (LOSS)}$$

= 171.2°C × 77.13 mW

= 13.2°C

Assuming a maximum ambient temperature environment of 85°C, the junction temperature is

$$T_J = T_R \times T_A = 13.2$$

°C + 85°C = 98.2°C

which is below the maximum junction temperature of 125°C.

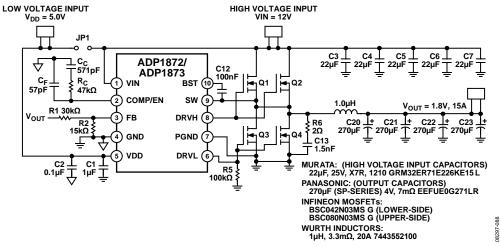

#### **DESIGN EXAMPLE**

The ADP1872/ADP1873 are easy to use, requiring only a few design criteria. For example, the example outlined in this section uses only four design criteria:  $V_{\text{OUT}} = 1.8 \text{ V}$ ,  $I_{\text{LOAD}} = 15 \text{ A}$  (pulsing), VIN = 12 V (typical), and  $f_{\text{SW}} = 300 \text{ kHz}$ .

#### **Input Capacitor**

The maximum input voltage ripple is usually 1% of the minimum input voltage (11.8 V  $\times$  0.01 = 120 mV).

$$\begin{split} &V_{RIPP} = 120 \text{ mV} \\ &V_{MAX, RIPPLE} = V_{RIPP} - (I_{LOAD, MAX} \times ESR) \\ &= 120 \text{ mV} - (15 \text{ A} \times 0.001) = 45 \text{ mV} \\ &C_{IN, min} = \frac{I_{LOAD, MAX}}{4f_{SW}V_{MAX, RIPPLE}} = \frac{15 \text{ A}}{4 \times 300 \times 10^3 \times 105 \text{ mV}} \\ &= 120 \text{ uF} \end{split}$$

Choose five 22  $\mu F$  ceramic capacitors. The overall ESR of five 22  $\mu F$  ceramic capacitors is less than 1 m  $\Omega.$

$$I_{RMS} = I_{LOAD}/2 = 7.5 \text{ A}$$

$P_{CIN} = (I_{RMS})^2 \times ESR = (7.5 \text{A})^2 \times 1 \text{ m}\Omega = 56.25 \text{ mW}$

#### Inductor

Determining inductor ripple current amplitude:

$$\Delta I_L \approx \frac{I_{LOAD}}{3} = 5 \text{ A}$$

so calculating for the inductor value

$$\begin{split} L &= \frac{(V_{IN,\,MAX} - V_{OUT})}{\Delta I_L \times f_{SW}} \times \frac{V_{OUT}}{V_{IN,\,MAX}} \\ &= \frac{(13.2 \text{ V} - 1.8 \text{ V})}{5 \text{ V} \times 300 \times 10^3} \times \frac{1.8 \text{ V}}{13.2 \text{ V}} \\ &= 1.03 \text{ } \mu\text{H} \end{split}$$

The inductor peak current is approximately

$$15 A + (5 A \times 0.5) = 17.5 A$$

Therefore, an appropriate inductor selection is 1.0  $\mu$ H with DCR = 3.3 m $\Omega$  (7443552100) from Table 7 with peak current handling of 20 A.

$$P_{DCR(LOSS)} = DCR \times I_{LOAD}^2$$

= 0.003 × (15 A)<sup>2</sup> = 675 mW

#### **Current Limit Programming**

The valley current is approximately

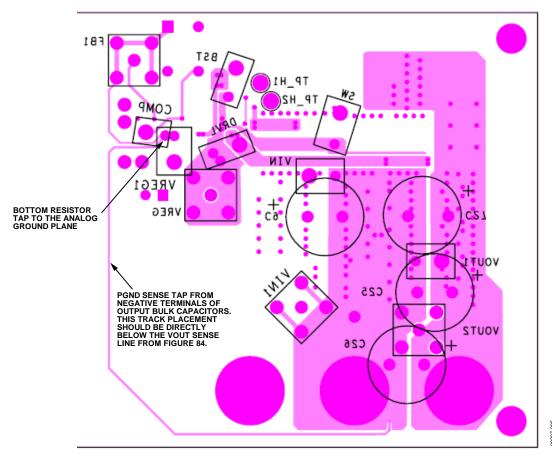

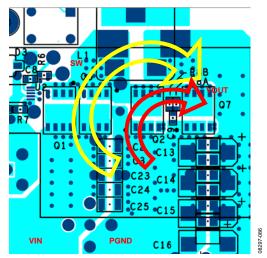

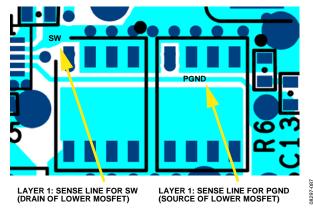

$$15 \text{ A} - (5 \text{ A} \times 0.5) = 12.5 \text{ A}$$