# Integrated Video Decoder and HDMI Receiver

# ADV7482

#### **FEATURES**

#### Analog input

- Worldwide NTSC/PAL/SECAM color demodulation support with autodetection

- One 10-bit ADC, 4× oversampling for CVBS, Y/C, and YPbPr 8 analog video input channels with on-chip antialiasing filter

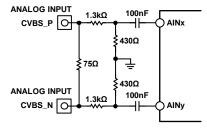

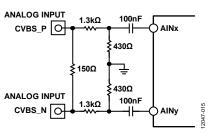

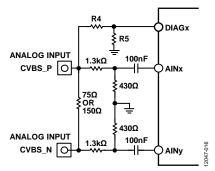

Fully differential, pseudo differential, and single-ended CVBS video input support

- STB diagnostics on differential video inputs

- CVBS (composite), Y/C (S-Video), and YPbPr (component) video input support

- Fast switching capability between analog inputs Adaptive contrast enhancement (ACE)

- Excellent common-mode noise rejection capabilities

- Rovi (Macrovision) copy protection detection

- Up to 4 V common-mode input range solution Vertical blanking interval (VBI) data slicer

- High-Definition Multimedia Interface (HDMI) capable receiver

- HDCP authentication and decryption support

- 162 MHz maximum pixel clock frequency, allowing HDTV formats up to 1080p and display resolutions up to UXGA (1600 × 1200 at 60 Hz)

- HDCP repeater support, up to 25 KSVs supported Integrated CEC controller, CEC 1.4 compatible Adaptive TMDS equalizer

- 5 V detect and Hot Plug assert

Component video processor

Any-to-any 3 × 3 color space conversion (CSC) matrix Contrast/brightness/hue/saturation video adjustment Timing adjustments controls for horizontal sync (HS)/vertical sync (VS)/data enable (DE) timing Video mute function Serial digital audio output interface HDMI audio extraction support

- Advanced audio muting feature

- I<sup>2</sup>S-compatible, left justified and right justified audio output modes

- 8-channel TDM output mode available

- 2 Mobile Industry Processor Interface (MIPI) Camera Serial Interface 2 (CSI-2) transmitters

- 4-lane transmitter with 4 lanes, 2 lanes, and 1 lane muxing options for HDMI/SDP/digital input port sources

- 1-lane transmitter for standard definition processor (SDP) sources

- 8-bit digital input/output port

- General

- 2-wire serial microprocessor unit (MPU) interface (I<sup>2</sup>C compatible)

- -40°C to +85°C temperature grade

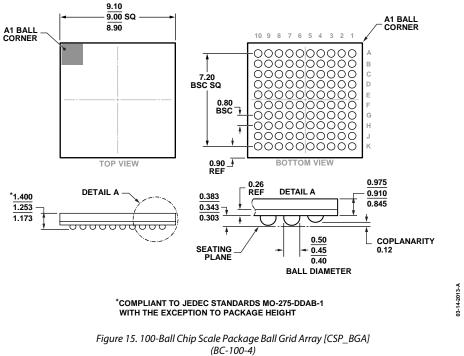

- 100-ball, 9 mm  $\times$  9 mm, RoHS-compliant CSP\_BGA package Qualified for automotive applications

#### **APPLICATIONS**

- **Portable devices**

- Automotive infotainment (head unit and rear seat entertainment systems)

- HDMI repeaters and video switches

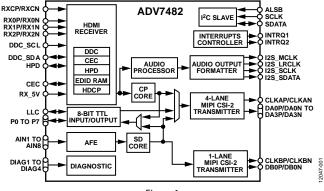

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

**Document Feedback**

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

#### One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# **ADV7482\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### **DOCUMENTATION**

### **Application Notes**

AN-1337: Design Considerations for Connecting Analog Devices Video Decoders to MIPI CSI-2 Receivers

#### **Data Sheet**

ADV7482: Integrated Video Decoder and HDMI Receiver Data Sheet

### TOOLS AND SIMULATIONS $\square$

ADV7482 Required Settings

### DESIGN RESOURCES

- ADV7482 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all ADV7482 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| Functional Block Diagram                    | 1  |

| Revision History                            | 2  |

| General Description                         | 3  |

| Detailed Functional Block Diagram           | 4  |

| Specifications                              | 5  |

| Electrical Characteristics                  | 5  |

| Analog Video Specifications                 | 7  |

| MIPI Video Output Specifications            | 8  |

| Analog Specifications                       | 8  |

| Timing Specifications                       | 9  |

| Absolute Maximum Ratings                    | 12 |

| Thermal Resistance                          | 12 |

| ESD Caution                                 | 12 |

| Pin Configuration and Function Descriptions | 13 |

### Power Supply Recommendation ......16 Power-Up Sequence ...... 16 Thoery of Operation ...... 17 Component Processor ...... 17 Analog Front End...... 17 8-Bit Digital Input/Output Port ...... 19

### **REVISION HISTORY**

6/14—Revision 0: Initial Version

# **GENERAL DESCRIPTION**

The ADV7482 is an integrated video decoder and HDMI<sup>®</sup> receiver, targeted at connectivity enabled head units requiring a wired, uncompressed digital audio/video link from smartphones, and other consumer electronics devices to support streaming and integration of cloud-based multimedia content and applications into an automotive infotainment system.

The ADV7482 HDMI capable receiver supports a maximum pixel clock frequency of 162 MHz, allowing HDTV formats up to 1080p, and display resolutions up to UXGA (1600 × 1200 at 60 Hz). The device integrates a consumer electronics control (CEC) controller that supports the capability discovery and control (CDC) feature. The HDMI input port has dedicated 5 V detect and Hot Plug<sup>∞</sup> assert pins.

The HDMI receiver includes an adaptive transition minimized differential signaling (TMDS) equalizer that ensures robust operation of the interface with long cables.

The ADV7482 contains a component processor (CP) that processes the video signals from the HDMI receiver. It provides features such as contrast, brightness, and saturation adjustments, as well as free run and timing adjustment controls for HS/VS/DE timing.

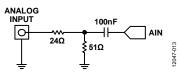

The ADV7482 analog front end (AFE) comprises a single high speed, 10-bit analog-to-digital converter (ADC) that digitizes the analog video signal before applying it to the SDP.

The eight analog video inputs can accept single-ended, pseudo differential, and fully differential composite video signals, as well as S-Video and YPbPr video signals, supporting a wide range of consumer and automotive video sources.

Short to battery (STB) events can be detected on differential input video signals. STB protection is provided by ac coupling the input video signals. The ADV7482, in combination with an external resistor divider, provides a common-mode input range of 4 V, enabling the removal of large signal common-mode transients present on the video lines.

The automatic gain control (AGC) and clamp restore circuitry allow an input video signal up to 1.0 V p-p at the analog video input pins of the ADV7482. Alternatively, the AGC and clamp restore circuitry can be bypassed for manual settings.

The SDP of the ADV7482 is capable of decoding a large selection of analog baseband video signals in composite, S-Video, and component formats. The SDP supports worldwide NTSC, PAL, and SECAM standards.

The ADV7482 features an 8-bit digital input/output port, supporting input and output video resolutions up to 720p/1080i in both the 8-bit interleaved 4:2:2 SDR and DDR modes.

To enable glueless interfacing of these video input sources to the latest generation of infotainment system on chips (SoCs), the ADV7482 features two MIPI<sup>®</sup> CSI-2 transmitters. The four-lane transmitter provides four data lanes, two data lanes, and one data lane muxing options, and can be used to output video from the HDMI receiver, the SDP, and the digital input port. The single-lane transmitter can be used to output video from the SDP only.

The ADV7482 offers a flexible audio output port for audio data extracted from HDMI streams. The HDMI receiver has advanced audio functionality, such as a mute controller that prevents audible extraneous noise in the audio output. Additionally, the ADV7482 can be set to output time division multiplexing (TDM) serial audio, which allows the transmission of eight multiplexed serial audio channels on a single audio output interface port.

The ADV7482 is programmed via a 2-wire, serial, bidirectional port (I<sup>2</sup>C compatible).

Fabricated in an advanced CMOS process, the ADV7482 is available in a 9 mm  $\times$  9 mm, RoHS-compliant, 100-ball CSP\_BGA package and is specified over the -40°C to +85°C temperature range.

The ADV7482 is offered in automotive and industrial versions.

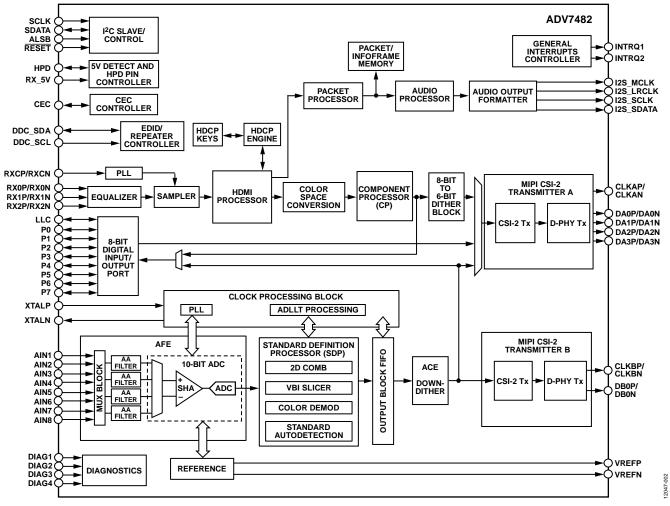

# DETAILED FUNCTIONAL BLOCK DIAGRAM

Figure 2.

# **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

AVDD = 1.71 V to 1.89 V, DVDD = 1.71 V to 1.89 V, PVDD = 1.71 V to 1.89 V, MVDD = 1.71 V to 1.89 V, CVDD = 1.71 V to 1.89 V, DVDDIO = 3.14 V to 3.46 V, and TVDD = 3.14 V to 3.46 V, specified at operating temperature range, unless otherwise noted.

| Table 1.                                                 | Court of           |                                                                                                                                |      | -    | N4   | 11.1     |

|----------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| Parameter                                                | Symbol             | Test Conditions/Comments                                                                                                       | Min  | Тур  | Max  | Unit     |

| STATIC PERFORMANCE                                       |                    |                                                                                                                                |      |      |      |          |

| Resolution (Each ADC)                                    | N                  |                                                                                                                                |      |      | 10   | Bits     |

| Integral Nonlinearity                                    | INL                | CVBS mode                                                                                                                      |      | 2    |      | LSB      |

| Differential Nonlinearity                                | DNL                | CVBS mode                                                                                                                      |      | ±0.6 |      | LSB      |

| DIGITAL INPUTS <sup>1</sup>                              |                    | SCLK, SDATA, RESET, ALSB, LLC, and P0 to P7                                                                                    |      |      |      |          |

| Input High Voltage                                       | VIH                | DVDDIO = 3.14 V to 3.46 V                                                                                                      | 2    |      |      | V        |

| Input Low Voltage                                        | VIL                | DVDDIO = 3.14 V to 3.46 V                                                                                                      |      |      | 0.8  | V        |

| Input Leakage Current                                    | l <sub>iN</sub>    |                                                                                                                                | -10  |      | +10  | μΑ       |

| Input Capacitance <sup>2</sup>                           | CIN                |                                                                                                                                |      |      | 10   | pF       |

| CRYSTAL INPUT                                            |                    |                                                                                                                                |      |      |      |          |

| Input High Voltage                                       | VIH                | XTALP                                                                                                                          | 1.2  |      |      | V        |

| Input Low Voltage                                        | VIL                | XTALP                                                                                                                          |      |      | 0.4  | V        |

| DIGITAL OUTPUTS <sup>1</sup>                             |                    | LLC, P0 to P7, I2S_MCLK, I2S_SCLK, I2S_LRCLK,<br>I2S_SDATA, SDATA, INTRQ1 and INTRQ2 (when<br>configured to drive when active) |      |      |      |          |

| Output High Voltage                                      | VOH                | DVDDIO = $3.14$ V to $3.46$ V and $I_{SOURCE} = 0.4$ mA                                                                        | 2.4  |      |      | V        |

| Output Low Voltage                                       | Vol                | DVDDIO = $3.14$ V to $3.46$ V and $I_{SINK} = 3.2$ mA                                                                          |      |      | 0.4  | V        |

| High Impedance Leakage Current                           | ILEAK              |                                                                                                                                |      | 10   |      | μA       |

| Output Capacitance <sup>2</sup>                          | COUT               |                                                                                                                                |      |      | 20   | pF       |

| POWER REQUIREMENTS                                       |                    |                                                                                                                                |      |      |      |          |

| Digital Power Supply                                     | D <sub>VDD</sub>   |                                                                                                                                | 1.71 | 1.8  | 1.89 | v        |

| HDMI Terminator Supply                                   | T <sub>VDD</sub>   |                                                                                                                                | 3.14 | 3.3  | 3.46 | v        |

| HDMI Comparator Supply                                   | CVDD               |                                                                                                                                | 1.71 | 1.8  | 1.89 | v        |

| PLL Power Supply                                         | P <sub>VDD</sub>   |                                                                                                                                | 1.71 | 1.8  | 1.89 | v        |

| MIPI Transmitters Power Supply                           | Mydd               |                                                                                                                                | 1.71 | 1.8  | 1.89 | v        |

| Digital Input/Output Power Supply <sup>1</sup>           | D <sub>VDDIO</sub> | 3.3 V operation                                                                                                                | 3.14 | 3.3  | 3.46 | v        |

| Analog Power Supply                                      | Avdd               |                                                                                                                                | 1.71 | 1.8  | 1.89 | v        |

| CURRENT CONSUMPTION <sup>1, 2, 3, 4</sup>                |                    |                                                                                                                                |      |      |      | <u> </u> |

| Digital Supply Current                                   | IDVDD              |                                                                                                                                |      |      | 279  | mA       |

| Single-Ended CVBS Input                                  | 10000              |                                                                                                                                |      | 74.5 | 217  | mA       |

| Fully Differential and Pseudo Differential<br>CVBS Input |                    |                                                                                                                                |      | 74.7 |      | mA       |

| Y/C Input                                                |                    |                                                                                                                                |      | 71.3 |      | mA       |

| YPbPr Input                                              |                    |                                                                                                                                |      | 72.8 |      | mA       |

| HDMI Input                                               |                    |                                                                                                                                |      | 68.1 |      | mA       |

| 8-Bit Digital Input                                      |                    |                                                                                                                                |      | 32.5 |      | mA       |

| HDMI Terminator Supply Current                           | I <sub>TVDD</sub>  |                                                                                                                                |      |      | 40   | mA       |

| Single-Ended CVBS Input                                  | .1000              |                                                                                                                                |      | 0.7  |      | mA       |

| Fully Differential and Pseudo Differential<br>CVBS Input |                    |                                                                                                                                |      | 0.7  |      | mA       |

| Y/C Input                                                |                    |                                                                                                                                |      | 0.7  |      | mA       |

| YPbPr Input                                              |                    |                                                                                                                                |      | 0.7  |      | mA       |

| HDMI Input                                               |                    |                                                                                                                                |      | 35   |      | mA       |

| 8-Bit Digital Input                                      |                    |                                                                                                                                |      | 0.7  |      | mA       |

| Parameter                                                | Symbol                 | Test Conditions/Comments | Min | Тур  | Max | Unit |

|----------------------------------------------------------|------------------------|--------------------------|-----|------|-----|------|

| HDMI Comparator Supply Current                           | ICVDD                  |                          |     |      | 92  | mA   |

| Single-Ended CVBS Input                                  |                        |                          |     | 0.1  |     | mA   |

| Fully Differential and Pseudo Differential<br>CVBS Input |                        |                          |     | 0.1  |     | mA   |

| Y/C Input                                                |                        |                          |     | 0.1  |     | mA   |

| YPbPr Input                                              |                        |                          |     | 0.1  |     | mA   |

| HDMI Input                                               |                        |                          |     | 63.9 |     | mA   |

| 8-Bit Digital Input                                      |                        |                          |     | 0.1  |     | mA   |

| PLL Supply Current                                       | I <sub>PVDD</sub>      |                          |     |      | 52  | mA   |

| Single-Ended CVBS Input                                  |                        |                          |     | 37.5 |     | mA   |

| Fully Differential and Pseudo Differential<br>CVBS Input |                        |                          |     | 37.5 |     | mA   |

| Y/C Input                                                |                        |                          |     | 37.7 |     | mA   |

| YPbPr Input                                              |                        |                          |     | 37.7 |     | mA   |

| HDMI Input                                               |                        |                          |     | 29.2 |     | mA   |

| 8-Bit Digital Input                                      |                        |                          |     | 27.9 |     | mA   |

| MIPI Transmitters Supply Current                         | I <sub>MVDD</sub>      |                          |     |      | 77  | mA   |

| Single-Ended CVBS Input                                  |                        |                          |     | 23.3 |     | mA   |

| Fully Differential and Pseudo Differential<br>CVBS Input |                        |                          |     | 23.3 |     | mA   |

| Y/C Input                                                |                        |                          |     | 23.2 |     | mA   |

| YPbPr Input                                              |                        |                          |     | 23.2 |     | mA   |

| HDMI Input                                               |                        |                          |     | 45.7 |     | mA   |

| 8-Bit Digital Input                                      |                        |                          |     | 38.1 |     | mA   |

| Digital Input/Output Supply Current                      | I <sub>DVDDIO</sub>    |                          |     |      | 78  | mA   |

| Single-Ended CVBS Input                                  |                        |                          |     | 0.2  |     | mA   |

| Fully Differential and Pseudo Differential<br>CVBS Input |                        |                          |     | 0.2  |     | mA   |

| Y/C Input                                                |                        |                          |     | 0.2  |     | mA   |

| YPbPr Input                                              |                        |                          |     | 0.2  |     | mA   |

| HDMI Input                                               |                        |                          |     | 3.6  |     | mA   |

| 8-Bit Digital Input                                      |                        |                          |     | 0.2  |     | mA   |

| Analog Supply Current                                    | I <sub>AVDD</sub>      |                          |     |      | 93  | mA   |

| Single-Ended CVBS Input                                  |                        |                          |     | 51.9 |     | mA   |

| Fully Differential and Pseudo Differential<br>CVBS Input |                        |                          |     | 70   |     | mA   |

| Y/C Input                                                |                        |                          |     | 63   |     | mA   |

| YPbPr Input                                              |                        |                          |     | 78.5 |     | mA   |

| HDMI Input                                               |                        |                          |     | 0.1  |     | mA   |

| 8-Bit Digital Input                                      |                        |                          |     | 0.1  |     | mA   |

| POWER-DOWN CURRENTS <sup>2, 5</sup>                      |                        |                          |     |      |     |      |

| Digital Supply                                           | I <sub>DVDD_PD</sub>   |                          |     | 0.2  |     | mA   |

| HDMI Terminator Supply                                   | I <sub>TVDD_PD</sub>   |                          |     | 0.4  |     | mA   |

| HDMI Comparator Supply                                   | I <sub>CVDD_PD</sub>   |                          |     | 0.1  |     | mA   |

| PLL Supply                                               | IPVDD_PD               |                          |     | 0.1  |     | mA   |

| MIPI Transmitters Supply                                 | I <sub>MVDD_PD</sub>   |                          |     | 0.1  |     | mA   |

| Digital Input/Output Supply                              | I <sub>DVDDIO_PD</sub> |                          |     | 0.2  |     | mA   |

| Analog Supply                                            | I <sub>AVDD_PD</sub>   |                          |     | 0.1  |     | mA   |

| Total Power Dissipation in Power-Down<br>Mode            |                        |                          |     | 4    |     | mW   |

<sup>1</sup> The 8-bit digital input/output port is only available when the DVDDIO supply is between 3.14 V and 3.46 V. <sup>2</sup> Guaranteed by lab characterization.

<sup>3</sup> Typical current consumption values are recorded with nominal voltage supply levels (including DVDDIO = 3.3 V), Philips test pattern, and at room temperature. <sup>4</sup> Maximum current consumption values are recorded with maximum rated voltage supply levels (including DVDDIO = 3.46 V), MoireX video pattern for analog inputs,

pseudorandom test pattern for digital inputs, and at worst-case temperature. <sup>5</sup> Typical power-down current consumption values are recorded with nominal voltage supply levels (including DVDDIO = 3.3 V) at room temperature.

### ANALOG VIDEO SPECIFICATIONS

AVDD = 1.71 V to 1.89 V, DVDD = 1.71 V to 1.89 V, PVDD = 1.71 V to 1.89 V, MVDD = 1.71 V to 1.89 V, CVDD = 1.71 V to 1.89 V, DVDDIO = 3.14 V to 3.46 V, and TVDD = 3.14 V to 3.46 V, specified at operating temperature range, unless otherwise noted.

#### Table 2.

| Parameter                                      | Symbol | Test Conditions/Comments        | Min | Тур  | Max | Unit    |

|------------------------------------------------|--------|---------------------------------|-----|------|-----|---------|

| NONLINEAR SPECIFICATIONS <sup>1, 2</sup>       |        |                                 |     |      |     |         |

| Differential Phase                             | DP     | CVBS input, modulated five-step |     | 0.9  |     | Degrees |

| Differential Gain                              | DG     | CVBS input, modulated five-step |     | 0.5  |     | %       |

| Luma Nonlinearity                              | LNL    | CVBS input, five-step           |     | 2.0  |     | %       |

| NOISE SPECIFICATIONS                           |        |                                 |     |      |     |         |

| Signal-to-Noise Ratio, Unweighted <sup>2</sup> | SNR    | Luma ramp                       |     | 57.1 |     | dB      |

|                                                |        | Luma flat field                 |     | 58   |     | dB      |

| Analog Front-End Crosstalk <sup>3</sup>        |        |                                 |     | 60   |     | dB      |

| Common-Mode Rejection Ratio <sup>2, 4</sup>    | CMRR   |                                 |     | 73   |     | dB      |

| LOCK TIME SPECIFICATIONS                       |        |                                 |     |      |     |         |

| Horizontal Lock Range <sup>3</sup>             |        |                                 | -5  |      | +5  | %       |

| Vertical Lock Range <sup>3</sup>               |        |                                 | 40  |      | 70  | Hz      |

| Subcarrier Lock Range <sup>3</sup>             | fsc    |                                 |     | ±1.3 |     | kHz     |

| Color Lock-In Time <sup>3</sup>                |        |                                 |     | 60   |     | Lines   |

| Synchronization Depth Range <sup>3</sup>       |        |                                 | 20  |      | 200 | %       |

| Color Burst Range <sup>3</sup>                 |        |                                 | 5   |      | 200 | %       |

| Fast Switch Speed <sup>2, 5</sup>              |        |                                 |     | 100  |     | ms      |

<sup>1</sup> These specifications apply to all CVBS input types, as well as to single-ended and differential CVBS inputs.

<sup>2</sup> Guaranteed by lab characterization.

<sup>3</sup> Guaranteed by design.

<sup>4</sup> The CMRR of this circuit design is critically dependent on the external resistor matching its inputs. This measurement was performed with 0.1% tolerant resistors, a common-mode voltage of 1 V, and a common-mode frequency of 10 kHz.

<sup>5</sup> The time it takes the ADV7482 to switch from one analog input (single ended or differential) to another, for example, switching from AIN1 to AIN2.

### **MIPI VIDEO OUTPUT SPECIFICATIONS**

AVDD = 1.71 V to 1.89 V, DVDD = 1.71 V to 1.89 V, PVDD = 1.71 V to 1.89 V, MVDD = 1.71 V to 1.89 V, CVDD = 1.71 V to 1.89 V, DVDDIO = 3.14 V to 3.46 V, and TVDD = 3.14 V to 3.46 V, specified at operating temperature range, unless otherwise noted.

The ADV7482 MIPI CSI-2 transmitters conform to the MIPI D-PHY Version 1.00.00 specification by characterization. The clock lane of the ADV7482 remains in high speed (HS) mode even when the data lane enters low power (LP) mode. For this reason, some measurements on the clock lane that pertain to low power mode are not applicable. Unless otherwise stated, all high speed measurements were performed with the ADV7482 operating with a nominal 1 Gbps output data rate.

| Parameter                                       | Symbol          | Min       | Тур | Max       | Unit   |  |

|-------------------------------------------------|-----------------|-----------|-----|-----------|--------|--|

| UNIT INTERVAL <sup>1</sup>                      | UI              | 1         |     | 12.5      | ns     |  |

| DATA LANE LP Tx DC SPECIFICATIONS <sup>2</sup>  |                 |           |     |           |        |  |

| Thevenin Output                                 |                 |           |     |           |        |  |

| High Level                                      | V <sub>OH</sub> | 1.1       | 1.2 | 1.3       | V      |  |

| Low Level                                       | Vol             | -50       | 0   | +50       | mV     |  |

| CLOCK LANE LP Tx DC SPECIFICATIONS <sup>2</sup> |                 |           |     |           |        |  |

| Thevenin Output                                 |                 |           |     |           |        |  |

| High Level                                      | V <sub>OH</sub> | 1.1       | 1.2 | 1.3       | V      |  |

| Low Level                                       | Vol             | -50       | 0   | +50       | mV     |  |

| DATA LANE HS TX SIGNALING REQUIREMENTS          |                 |           |     |           |        |  |

| High Speed Differential Voltage Swing           | <b> V</b> 1     | 140       | 200 | 270       | mV p-p |  |

| Differential Voltage Mismatch                   |                 |           |     | 10        | mV     |  |

| Single-Ended Output High Voltages               |                 |           |     | 360       | mV     |  |

| Static Common-Mode Voltage Level                |                 | 150       | 200 | 250       | mV     |  |

| CLOCK LANE HS Tx SIGNALING REQUIREMENTS         |                 |           |     |           |        |  |

| High Speed Differential Voltage Swing           | V <sub>2</sub>  | 140       | 200 | 270       | mV p-p |  |

| Differential Voltage Mismatch                   |                 |           |     | 10        | mV     |  |

| Single-Ended Output High Voltages               |                 |           |     | 360       | mV     |  |

| Static Common-Mode Voltage Level                |                 | 150       | 200 | 250       | mV     |  |

| HS Tx CLOCK TO DATA LANE TIMING REQUIREMENTS    |                 |           |     |           |        |  |

| Data to Clock Skew                              |                 | 0.35 × UI |     | 0.65 × UI | ns     |  |

<sup>1</sup> Guaranteed by design.

<sup>2</sup> These measurements were performed with  $C_{LOAD} = 50 \text{ pF}$ .

#### ANALOG SPECIFICATIONS

AVDD = 1.71 V to 1.89 V, DVDD = 1.71 V to 1.89 V, PVDD = 1.71 V to 1.89 V, MVDD = 1.71 V to 1.89 V, CVDD = 1.71 V to 1.89 V, DVDDIO = 3.14 V to 3.46 V, and TVDD = 3.14 V to 3.46 V, specified at operating temperature range, unless otherwise noted.

| Parameter                | <b>Test Conditions/Comments</b> | Min | Тур  | Max | Unit |

|--------------------------|---------------------------------|-----|------|-----|------|

| CLAMP CIRCUITRY          |                                 |     |      |     |      |

| External Clamp Capacitor | Required by design              |     | 0.1  |     | μF   |

| Large Clamp              |                                 |     |      |     |      |

| Source Current           |                                 |     | 0.32 |     | mA   |

| Sink Current             |                                 |     | 0.32 |     | mA   |

| Fine Clamp               |                                 |     |      |     |      |

| Source Current           |                                 |     | 7    |     | μΑ   |

| Sink Current             |                                 |     | 7    |     | μA   |

### TIMING SPECIFICATIONS

AVDD = 1.71 V to 1.89 V, DVDD = 1.71 V to 1.89 V, PVDD = 1.71 V to 1.89 V, MVDD = 1.71 V to 1.89 V, CVDD = 1.71 V to 1.89 V, DVDDIO = 3.14 V to 3.46 V, and TVDD = 3.14 V to 3.46 V, specified at operating temperature range, unless otherwise noted.

| Parameter                                          | Symbol          | Test Conditions                                      | Min  | Тур      | Max    | Unit            |

|----------------------------------------------------|-----------------|------------------------------------------------------|------|----------|--------|-----------------|

| CLOCK AND CRYSTAL                                  | -               |                                                      |      |          |        |                 |

| Nominal Frequency <sup>1</sup>                     |                 | Required by design                                   |      | 28.63636 |        | MHz             |

| Frequency Stability <sup>1</sup>                   |                 | Required by design                                   |      |          | ±50    | ppm             |

| Input LLC Clock Frequency<br>Range <sup>2, 3</sup> |                 | DVDDIO = 3.14 V to 3.46 V                            | 13.5 |          | 148.5  | MHz             |

| Output LLC Clock Frequency<br>Range <sup>2,3</sup> |                 | DVDDIO = 3.14 V to 3.46 V                            | 13.5 |          | 148.5  | MHz             |

| I2S_SCLK Frequency <sup>3</sup>                    |                 |                                                      |      |          | 12.288 | MHz             |

| I2S_MCLK Frequency <sup>3</sup>                    |                 |                                                      |      |          | 24.576 | MHz             |

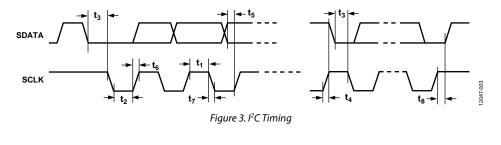

| I <sup>2</sup> C PORT                              |                 |                                                      |      |          |        |                 |

| SCLK Frequency                                     |                 |                                                      |      |          | 400    | kHz             |

| SCLK Minimum Pulse Width High                      | t1              |                                                      | 0.6  |          |        | μs              |

| SCLK Minimum Pulse Width Low                       | t <sub>2</sub>  |                                                      | 1.3  |          |        | μs              |

| Hold Time (Start Condition)                        | t <sub>3</sub>  |                                                      | 0.6  |          |        | μs              |

| Setup Time (Start Condition)                       | t4              |                                                      | 0.6  |          |        | μs              |

| SDATA Setup Time                                   | t₅              |                                                      | 100  |          |        | ns              |

| SCLK and SDATA Rise Times                          | t <sub>6</sub>  |                                                      |      |          | 300    | ns              |

| SCLK and SDATA Fall Times                          | t <sub>7</sub>  |                                                      |      |          | 300    | ns              |

| Setup Time (Stop Condition)                        | t <sub>8</sub>  |                                                      |      | 0.6      |        | μs              |

| RESET FEATURE                                      |                 |                                                      |      |          |        |                 |

| RESET Pulse Width <sup>1</sup>                     |                 |                                                      | 5    |          |        | ms              |

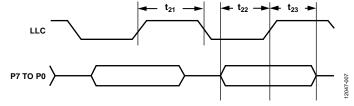

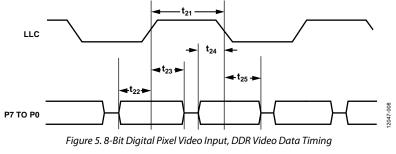

| 8-BIT DIGITAL INPUT PORT <sup>2</sup>              |                 | DVDDIO = 3.14 V to 3.46 V                            |      |          |        |                 |

| LLC High Time <sup>3</sup>                         | t <sub>21</sub> |                                                      | 45   |          | 55     | % duty<br>cycle |

| LLC Low Time <sup>3</sup>                          |                 |                                                      | 45   |          | 55     | % duty<br>cycle |

| SDR and DDR Modes Setup Time                       | t <sub>22</sub> | Data latched on rising edge                          | 1    |          |        | ns              |

| SDR and DDR Modes Hold Time                        | t <sub>23</sub> | Data latched on rising edge                          | 1    |          |        | ns              |

| DDR Mode Setup Time                                | t <sub>24</sub> | Data latched on falling edge                         | 1    |          |        | ns              |

| DDR Mode Hold Time                                 | t <sub>25</sub> | Data latched on falling edge                         | 1    |          |        | ns              |

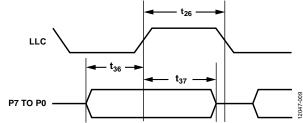

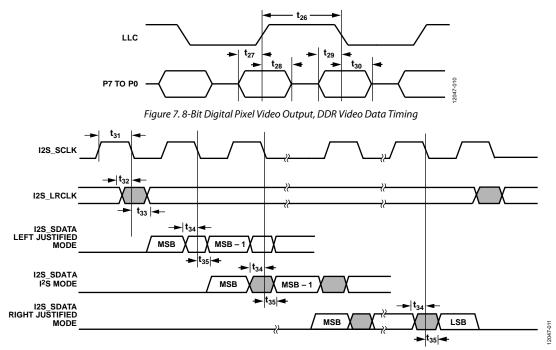

| 8-BIT DIGITAL OUTPUT PORT <sup>2</sup>             |                 | DVDDIO = 3.14 V to 3.46 V                            |      |          |        |                 |

| LLC High Time                                      | t <sub>26</sub> |                                                      | 40   |          | 60     | % duty<br>cycle |

| LLC Low Time                                       |                 |                                                      | 40   |          | 60     | % duty<br>cycle |

| SDR Modes Setup Time <sup>4, 5</sup>               | t <sub>36</sub> | At P0 to P7 output pin, data latched on rising edge  | 1.98 |          |        | ns              |

| SDR Modes Hold Time <sup>4, 5</sup>                | t <sub>37</sub> | At P0 to P7 output pin, data latched on rising edge  | 2.50 |          |        | ns              |

| DDR Modes Setup Time <sup>4, 5</sup>               | t <sub>27</sub> | At P0 to P7 output pin, data latched on rising edge  | 1.66 |          |        | ns              |

| DDR Modes Hold Time <sup>4, 5</sup>                | t <sub>28</sub> | At P0 to P7 output pin, data latched on rising edge  | 3.52 |          |        | ns              |

| DDR Mode Setup TIme <sup>4, 5</sup>                | t <sub>29</sub> | At P0 to P7 output pin, data latched on falling edge | 1.71 |          |        | ns              |

| DDR Modes Hold Time <sup>4, 5</sup>                | t <sub>30</sub> | At P0 to P7 output pin, data latched on falling edge | 3.17 |          |        | ns              |

| Parameter                          | Symbol          | Test Conditions                              | Min | Typ Max | Unit            |

|------------------------------------|-----------------|----------------------------------------------|-----|---------|-----------------|

| I <sup>2</sup> S PORT, MASTER MODE |                 |                                              |     |         |                 |

| I2S_SCLK High Time                 | t <sub>31</sub> |                                              | 45  | 55      | % duty<br>cycle |

| I2S_SCLK Low Time                  |                 |                                              | 45  | 55      | % duty<br>cycle |

| I2S_LRCLK Data Transition Time     | t <sub>32</sub> | End of valid data to I2S_SCLK falling edge   |     | 10      | ns              |

|                                    | t <sub>33</sub> | I2S_SCLK falling edge to start of valid data |     | 10      | ns              |

| I2S_SDATA Data Transition Time     | t <sub>34</sub> | End of valid data to I2S_SCLK falling edge   |     | 5       | ns              |

|                                    | t <sub>35</sub> | I2S_SCLK falling edge to start of valid data |     | 5       | ns              |

<sup>1</sup> Required by design.

<sup>2</sup> The 8-bit digital input/output port is only available when the DVDDIO supply is between 3.14 V and 3.46 V. <sup>3</sup> Guaranteed by design. <sup>4</sup> These specifications only apply when the LLC\_DLL\_PHASE[4:0] (IO Map, Register 0x0C[4:0]) is set to 00000. <sup>5</sup> Guaranteed by lab characterization.

#### **Timing Diagrams**

Figure 4. 8-Bit Digital Pixel Video Input, SDR Video Data Timing

Figure 6. 8-Bit Digital Pixel Video Output, SDR Video Data Timing

Figure 8. I<sup>2</sup>S Timing

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

| Tuble 0.                                           |                                  |

|----------------------------------------------------|----------------------------------|

| Parameter                                          | Rating                           |

| TVDD, DVDDIO to GND                                | 4 V                              |

| AVDD, PVDD, MVDD, DVDD, CVDD<br>to GND             | 2.2 V                            |

| CVDD to DVDD                                       | –0.3 V to +0.3 V                 |

| MVDD to DVDD                                       | –0.3 V to +0.3 V                 |

| PVDD to DVDD                                       | –0.3 V to +0.3 V                 |

| AVDD to DVDD                                       | –0.3 V to +0.3 V                 |

| Digital Inputs Voltage to GND                      | GND – 0.3 V to DVDDIO +<br>0.3 V |

| Digital Outputs Voltage to GND                     | GND – 0.3 V to DVDDIO +<br>0.3 V |

| Analog Inputs to GND                               | –0.3 V to AVDD + 0.3 V           |

| XTALN and XTALP to GND                             | –0.3 V to PVDD + 0.3 V           |

| HDMI Digital Inputs Voltage to<br>GND              | –0.3 V to CVDD + 0.3 V           |

| 5 V Tolerant Inputs Voltage to GND <sup>1, 2</sup> | –0.3 V to +5.5 V                 |

| Maximum Junction Temperature<br>(TJ max)           | 125°C                            |

| Storage Temperature Range                          | –65°C to +150°C                  |

| Infrared Reflow Soldering<br>(20 sec)              | 260°C                            |

<sup>1</sup> The following inputs are 3.3 V inputs but are 5 V tolerant: DDC\_SCL, DDC\_SDA, HPD, RX\_5V, and CEC.

<sup>2</sup> The following inputs are 1.8 V inputs but are 5 V tolerant: DIAG1, DIAG2, DIAG3, and DIAG4.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

To reduce power consumption when using the ADV7482, turn off unused sections of the device.

Due to printed circuit board (PCB) metal variation, and, therefore, variation in PCB heat conductivity, the value of  $\theta_{JA}$  may differ for various PCBs.

The most efficient measurement solution is achieved using the package surface temperature to estimate the die temperature. This eliminates the variance associated with the  $\theta_{JA}$  value.

Do not exceed the maximum junction temperature  $(T_J max)$  of 125°C. The following equation calculates the junction temperature  $(T_J)$  using the measured package surface temperature and applies only when no heat sink is used on the device under test (DUT):

$$T_J = T_S + (\Psi_{JT} \times W_{TOTAL})$$

where:

$T_s$  is the package surface temperature (°C).

$\Psi_{TT}$  = 0.81°C/W for the 100-ball CSP\_BGA (based on 2s2p test board defined by JEDEC standards.

$W_{TOTAL} = (PVDD \times I_{PVDD}) + (TVDD \times I_{TVDD}) - P_{UpStream} + (CVDD \times I_{CVDD}) + (AVDD \times I_{AVDD}) + (DVDD \times I_{DVDD}) + (DVDDIO \times I_{DVDDO}) + (MVDD \times I_{MVDD})$

where  $P_{UpStream}$  is the quantity of TVDD power consumed on the upstream HDMI transmitter.  $P_{UpStream}$  can be estimated to be around 110 mW for a nominal HDMI transmitter.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

|    | 1                                                 | 2             | 3             | 4            | 5     | 6    | 7    | 8       | 9     | 10    | _        |

|----|---------------------------------------------------|---------------|---------------|--------------|-------|------|------|---------|-------|-------|----------|

| A  | GND                                               | I2S_<br>SDATA | GND           | RX2P         | RX1P  | RX0P | RXCP | DDC_SCL | DNC   | GND   | A        |

| в  | MVDD                                              | I2S_<br>SCLK  | CVDD          | RX2N         | RX1N  | RXON | RXCN | DDC_SDA | HPD   | GND   | в        |

| с  | CLKAN                                             | CLKAP         | I2S_<br>LRCLK | I2S_<br>MCLK | TEST2 | TVDD | CEC  | RX_5V   | AIN7  | AIN8  | с        |

| D  | DAON                                              | DA0P          | TEST3         | DVDD         | GND   | GND  | GND  | DIAG4   | AIN5  | AIN6  | D        |

| E  | DA1N                                              | DA1P          | INTRQ2        | GND          | GND   | GND  | AVDD | DIAG3   | AIN3  | AIN4  | E        |

| F  | DA2N                                              | DA2P          | INTRQ1        | GND          | GND   | GND  | GND  | VREFN   | AIN1  | AIN2  | F        |

| G  | DA3N                                              | DA3P          | TEST          | DVDD         | GND   | GND  | GND  | VREFP   | DIAG1 | DIAG2 | G        |

| н  | DB0N                                              | DB0P          | DVDDIO        | P1           | P4    | DNC  | DNC  | RESET   | PVDD  | GND   | н        |

| J  | CLKBN                                             | CLKBP         | MVDD          | P2           | P5    | P7   | DNC  | SCLK    | XTALN | XTALP | J        |

| к  | GND                                               | MVDD          | P0            | P3           | P6    | LLC  | DNC  | SDATA   | ALSB  | GND   | ĸ        |

| _  | 1                                                 | 2             | 3             | 4            | 5     | 6    | 7    | 8       | 9     | 10    | 2047-012 |

| DI | DNC = DO NOT CONNECT. LEAVE THIS PIN UNCONNECTED. |               |               |              |       |      |      |         |       |       |          |

|    |                                                   |               |               | <b>-</b> ·   | 0.0'  | c c  |      |         |       |       |          |

Figure 9. Pin Configuration

### Table 7. Pin Function Descriptions

| Pin No. | Mnemonic  | Туре          | Description                                                                                                                                                        |

|---------|-----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1      | GND       | Ground        | Ground.                                                                                                                                                            |

| A2      | I2S_SDATA | Output        | I2S Audio Output.                                                                                                                                                  |

| A3      | GND       | Ground        | Ground.                                                                                                                                                            |

| A4      | RX2P      | HDMI          | HDMI Digital Input Channel 2.                                                                                                                                      |

| A5      | RX1P      | HDMI          | HDMI Digital Input Channel 1.                                                                                                                                      |

| A6      | RXOP      | HDMI          | HDMI Digital Input Channel 0.                                                                                                                                      |

| A7      | RXCP      | HDMI          | HDMI Input Clock.                                                                                                                                                  |

| A8      | DDC_SCL   | HDMI          | HDCP Slave Serial Clock.                                                                                                                                           |

| A9      | DNC       | Miscellaneous | Do Not Connect. Leave this pin unconnected.                                                                                                                        |

| A10     | GND       | Ground        | Ground.                                                                                                                                                            |

| B1      | MVDD      | Power         | MIPI Supply Voltage (1.8 V).                                                                                                                                       |

| B2      | I2S_SCLK  | Output        | Audio Serial Clock.                                                                                                                                                |

| B3      | CVDD      | Power         | HDMI Comparator Supply Voltage (1.8 V). This is the supply for the HDMI sensitive analog circuitry. Blocks on this supply include the TMDS PLL and the equalizers. |

| B4      | RX2N      | HDMI          | HDMI Digital Input Channel 2 Complement.                                                                                                                           |

| B5      | RX1N      | HDMI          | HDMI Digital Input Channel 1 Complement.                                                                                                                           |

| B6      | RXON      | HDMI          | HDMI Digital Input Channel 0 Complement.                                                                                                                           |

| B7      | RXCN      | HDMI          | HDMI Input Clock Complement.                                                                                                                                       |

| B8      | DDC_SDA   | HDMI          | HDCP Slave Serial Data.                                                                                                                                            |

| B9      | HPD       | HDMI          | HDMI Hot Plug Assert.                                                                                                                                              |

| B10     | GND       | Ground        | Ground.                                                                                                                                                            |

| Pin No.   | Mnemonic     | Туре          | Description                                                                             |

|-----------|--------------|---------------|-----------------------------------------------------------------------------------------|

| C1        | CLKAN        | Output        | MIPI Transmitter A Negative Output Clock.                                               |

| C2        | CLKAP        | Output        | MIPI Transmitter A Positive Output Clock.                                               |

| C3        | I2S_LRCLK    | Output        | Audio Left/Right Clock.                                                                 |

| C4        | I2S_MCLK     | Output        | Audio Master Clock Output.                                                              |

| C5        | TEST2        | Miscellaneous | Test Pin 2. Pull down via a large pull-down resistor to ground.                         |

| C6        | TVDD         | Power         | HDMI Terminator Supply Voltage (3.3 V).                                                 |

| C0<br>C7  | CEC          | HDMI          | CEC Channel.                                                                            |

| C7<br>C8  | RX_5V        | HDMI          | HDMI 5 V Detect. A large pull-down resistor (100 k $\Omega$ , typical) to               |

|           |              |               | ground must be connected to this pin.                                                   |

| C9        | AIN7         | Input         | Analog Video Input Channel.                                                             |

| C10       | AIN8         | Input         | Analog Video Input Channel.                                                             |

| D1        | DA0N         | Output        | MIPI Transmitter A Negative Data Output.                                                |

| D2        | DA0P         | Output        | MIPI Transmitter A Positive Data Output.                                                |

| D3        | TEST3        | Miscellaneous | Test Pin 3. Pull up to DVDDIO via a pull-up resistor (4.7 k $\Omega$ ).                 |

| D4        | DVDD         | Power         | Digital Supply Voltage (1.8 V).                                                         |

| D5        | GND          | Ground        | Ground.                                                                                 |

| D6        | GND          | Ground        | Ground.                                                                                 |

| D7        | GND          | Ground        | Ground.                                                                                 |

| D8        | DIAG4        | Input         | Analog Video Diagnostic Input. This input is 5 V tolerant.                              |

| D9        | AIN5         | Input         | Analog Video Input Channel.                                                             |

| D10       | AIN6         | Input         | Analog Video Input Channel.                                                             |

| E1        | DA1N         | Output        | MIPI Transmitter A Negative Data Output.                                                |

| E2        | DA1P         | Output        | MIPI Transmitter A Positive Data Output.                                                |

| E3        | INTRQ2       | Output        | Interrupt Request Output.                                                               |

| E4        | GND          | Ground        | Ground.                                                                                 |

| E5        | GND          | Ground        | Ground.                                                                                 |

| E6        | GND          | Ground        | Ground.                                                                                 |

| E7        | AVDD         | Power         | Analog Supply Voltage (1.8 V).                                                          |

| E8        | DIAG3        | Input         | Analog Video Diagnostic Input. This input is 5 V tolerant.                              |

| E9        | AIN3         | Input         | Analog Video Inguistic input, mis input is 5 v tolerant.<br>Analog Video Input Channel. |

| E10       | AIN4         |               | Analog Video Input Channel.                                                             |

| E10<br>F1 | DA2N         | Input         | MIPI Transmitter A Negative Data Output.                                                |

|           | DA2N<br>DA2P | Output        |                                                                                         |

| F2        | INTRO1       | Output        | MIPI Transmitter A Positive Data Output.                                                |

| F3        |              | Output        | Interrupt Request Output.                                                               |

| F4        | GND          | Ground        | Ground.                                                                                 |

| F5        | GND          | Ground        | Ground.                                                                                 |

| F6        | GND          | Ground        | Ground.                                                                                 |

| F7        | GND          | Ground        | Ground.                                                                                 |

| F8        | VREFN        | Output        | Internal Voltage Reference Output.                                                      |

| F9        | AIN1         | Input         | Analog Video Input Channel.                                                             |

| F10       | AIN2         | Input         | Analog Video Input Channel.                                                             |

| G1        | DA3N         | Output        | MIPI Transmitter A Negative Data Output.                                                |

| G2        | DA3P         | Output        | MIPI Transmitter A Positive Data Output.                                                |

| G3        | TEST         | Miscellaneous | Do Not Connect. Leave this pin unconnected.                                             |

| G4        | DVDD         | Power         | Digital Supply Voltage (1.8 V).                                                         |

| G5        | GND          | Ground        | Ground.                                                                                 |

| G6        | GND          | Ground        | Ground.                                                                                 |

| G7        | GND          | Ground        | Ground.                                                                                 |

| G8        | VREFP        | Output        | Internal Voltage Reference Output.                                                      |

| G9        | DIAG1        | Input         | Analog Video Diagnostic Input. This input is 5 V tolerant.                              |

| G10       | DIAG2        | Input         | Analog Video Diagnostic Input. This input is 5 V tolerant.                              |

| Pin No. | Mnemonic | Туре          | Description                                                                                                                                                                                                                                                                                                     |  |

|---------|----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| H1      | DBON     | Output        | MIPI Transmitter B Negative Data Output.                                                                                                                                                                                                                                                                        |  |

| H2      | DB0P     | Output        | MIPI Transmitter B Positive Data Output.                                                                                                                                                                                                                                                                        |  |

| H3      | DVDDIO   | Power         | Digital Input/Output Supply Voltage (3.3 V).                                                                                                                                                                                                                                                                    |  |

| H4      | P1       | Input/Output  | Video Pixel Input/Output Port.                                                                                                                                                                                                                                                                                  |  |

| H5      | P4       | Input/Output  | Video Pixel Input/Output Port.                                                                                                                                                                                                                                                                                  |  |

| H6      | DNC      | Miscellaneous | Do Not Connect. Leave this pin unconnected.                                                                                                                                                                                                                                                                     |  |

| H7      | DNC      | Miscellaneous | Do Not Connect. Leave this pin unconnected.                                                                                                                                                                                                                                                                     |  |

| H8      | RESET    | Input         | System Reset Input, Active Low. A minimum low reset pulse of 5 ms is required to reset the chip.                                                                                                                                                                                                                |  |

| H9      | PVDD     | Power         | PLL Supply Voltage (1.8 V).                                                                                                                                                                                                                                                                                     |  |

| H10     | GND      | Ground        | Ground.                                                                                                                                                                                                                                                                                                         |  |

| J1      | CLKBN    | Output        | MIPI Transmitter B Negative Output Clock.                                                                                                                                                                                                                                                                       |  |

| J2      | CLKBP    | Output        | MIPI Transmitter B Positive Output Clock.                                                                                                                                                                                                                                                                       |  |

| J3      | MVDD     | Power         | MIPI Supply Voltage (1.8 V).                                                                                                                                                                                                                                                                                    |  |

| J4      | P2       | Input/Output  | Video Pixel Input/Output Port.                                                                                                                                                                                                                                                                                  |  |

| J5      | P5       | Input/Output  | Video Pixel Input/Output Port.                                                                                                                                                                                                                                                                                  |  |

| J6      | P7       | Input/Output  | Video Pixel Input/Output Port.                                                                                                                                                                                                                                                                                  |  |

| J7      | DNC      | Miscellaneous | Do Not Connect. Leave this pin unconnected.                                                                                                                                                                                                                                                                     |  |

| J8      | SCLK     | Input         | I <sup>2</sup> C Port Serial Clock Input.                                                                                                                                                                                                                                                                       |  |

| 9       | XTALN    | Output        | Crystal Output. This pin must be connected to the 28.63636 MHz crystal or not connected if an external 1.8 V, 28.63636 MHz clock oscillator is used. In crystal mode, the crystal must be a fundamental crystal.                                                                                                |  |

| J10     | XTALP    | Input         | Crystal Input or External Clock Input. This pin must be connected<br>to the 28.63636 MHz crystal or connected to an external 1.8 V,<br>28.63636 MHz clock oscillator if a clock oscillator is used. In crystal<br>mode, the crystal must be a fundamental crystal.                                              |  |

| K1      | GND      | Ground        | Ground.                                                                                                                                                                                                                                                                                                         |  |

| K2      | MVDD     | Power         | MIPI Supply Voltage (1.8 V).                                                                                                                                                                                                                                                                                    |  |

| K3      | P0       | Input/Output  | Video Pixel Input/Output Port.                                                                                                                                                                                                                                                                                  |  |

| K4      | P3       | Input/Output  | Video Pixel Input/Output Port.                                                                                                                                                                                                                                                                                  |  |

| K5      | P6       | Input/Output  | Video Pixel Input/Output Port.                                                                                                                                                                                                                                                                                  |  |

| K6      | LLC      | Input/Output  | Line Locked Clock. Input/output clock for the pixel data.                                                                                                                                                                                                                                                       |  |

| K7      | DNC      | Miscellaneous | Do Not Connect. Leave this pin unconnected.                                                                                                                                                                                                                                                                     |  |

| K8      | SDATA    | Input/Output  | l <sup>2</sup> C Port Serial Data Input/Output.                                                                                                                                                                                                                                                                 |  |

| К9      | ALSB     | Input         | Main I <sup>2</sup> C Address Selection Pin. This pin selects the main I <sup>2</sup> C address (IO Map I <sup>2</sup> C address) for the part. When ALSB is set to Logic 0, the IO Map I <sup>2</sup> C write address is 0xE0; when ALSB is set to Logic 1, the IO Map I <sup>2</sup> C write address is 0xE2. |  |

| K10     | GND      | Ground        | Ground.                                                                                                                                                                                                                                                                                                         |  |

# POWER SUPPLY RECOMMENDATION POWER-UP SEQUENCE

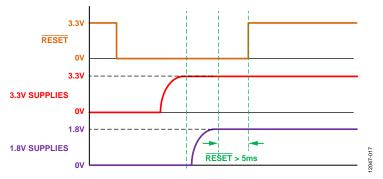

Adhere to the absolute maximum ratings at all times during power-up (see Table 6). The power-up sequence for the ADV7482 is as follows:

- 1. Assert RESET (pull the pin low).

- 2. Power up the 3.3 V supplies (D<sub>VDDIO</sub> and T<sub>VDD</sub>). These supplies must be powered up simultaneously.

- 3. Power up the 1.8 V supplies (D<sub>VDD</sub>, C<sub>VDD</sub>, P<sub>VDD</sub>, M<sub>VDD</sub>, and A<sub>VDD</sub>). These supplies must be powered up simultaneously.

- 4. RESET can be deasserted (pulled high) 5 ms after all supplies are fully powered up.

- After all power supplies and the RESET pin are powered up and stable, wait an additional 5 ms before initiating I<sup>2</sup>C communication with the ADV7482.

### **POWER-DOWN SEQUENCE**

The ADV7482 power supplies can be deasserted simultaneously as long as a higher rated supply (for example,  $D_{VDDIO}$ ) does not fall to a voltage level less than a lower rated supply (for example,  $D_{VDD}$ ), and the absolute maximum ratings specifications are followed.

Figure 10. Supply Power-Up Sequence

### THOERY OF OPERATION HDMI RECEIVER

The HDMI receiver supports video formats ranging from 480i to 1080p, and display resolutions from VGA ( $640 \times 480$  at 60 Hz) to UXGA ( $1600 \times 1200$  at 60 Hz).

The HDMI receiver allows programmable equalization of the HDMI data signals. This equalization compensates for the high frequency losses inherent in HDMI and DVI cabling, especially at longer lengths and higher frequencies. The receiver is capable of equalizing for cable lengths up to 30 meters to achieve robust receiver performance.

The HDMI interface of the ADV7482 allows for authentication of a video receiver, decryption of encoded data at the receiver, and renewability of that authentication during transmission, as specified by the HDCP 1.4 protocol.

Dual extended display identification data (EDID) support is provided via an on-chip 512-byte EDID RAM. The EDID RAM must be programmed at power-up. It can be configured as two 256-byte EDIDs, or as a single 512-byte EDID.

The ADV7482 has a synchronization regeneration block used to regenerate the data enable (DE) signal based on the measurement of the video format being displayed and to filter the horizontal and vertical synchronization signals to prevent glitches.

The HDMI receiver also supports TMDS error reduction coding, 4-bit (TERC4) error detection, used for the detection of corrupted HDMI packets.

The main HDMI receiver features include

- 162.0 MHz (UXGA at 24 BPP) maximum TMDS clock frequency.

- Integrated fully adaptive equalizer for cable lengths up to 30 meters.

- HDCP 1.4 support.

- Internal HDCP keys.

- HDCP repeater support, up to 25 key selection vectors (KSVs) supported.

- PCM audio packet support.

- Support for 8-channel TDM output data up to 48 kHz.

- Repeater support.

- Internal EDID RAM (512-byte for single mode, and 256-byte for dual mode operation).

- Hot Plug assert output pin (HPD).

- CEC controller.

### COMPONENT PROCESSOR

The ADV7482 has one any-to-any  $3 \times 3$  CSC matrix. The CSC block is located in the processing path before the CP section. CSC enables YCbCr-to-RGB and RGB-to-YCbCr conversions. Many other standards of color space can be implemented using the color space converter.

CP features include

- Support for all video modes supported by the HDMI receiver. These include 525i, 625i, 525p, 625p, 1080i, 1080p, and display resolutions from VGA (640 × 480 at 60 Hz) to UXGA (1600 × 1200 at 60 Hz).

- Manual adjustments including gain (contrast), offset (brightness), hue, and saturation.

- Free run output mode that provides stable timing when no video input is present.

- Timing adjustments controls for HS/VS/DE timing.

### **ANALOG FRONT END**

The ADV7482 AFE comprises a single high speed, 10-bit ADC that digitizes the analog video signal before applying it to the SDP. The AFE uses differential channels to the ADC to ensure high performance in mixed-signal applications and to enable differential CVBS to be connected directly to the ADV7482.