# Dual 12-Bit (8-Bit Byte) Double-Buffered CMOS D/A Converter

**DAC8248**

#### **FEATURES**

Two Matched 12-Bit DACs on One Chip

12-Bit Resolution with an 8-Bit Data Bus

Direct Interface with 8-Bit Microprocessors

Double-Buffered Digital Inputs

RESET to Zero Pin

12-Bit Endpoint Linearity (±1/2 LSB) Over Temperature

+5 V to +15 V Single Supply Operation

Latch-Up Resistant

Improved ESD Resistance

Packaged in a Narrow 0.3" 24-Pin DIP and 0.3" 24-Pin

SOL Package

Available in Die Form

#### **APPLICATIONS**

Multichannel Microprocessor-Controlled Systems Robotics/Process Control/Automation Automatic Test Equipment Programmable Attenuator, Power Supplies, Window Comparators Instrumentation Equipment Battery Operated Equipment

#### **GENERAL DESCRIPTION**

The DAC8248 is a dual 12-bit, double-buffered, CMOS digital-to-analog converter. It has an 8-bit wide input data port that interfaces directly with 8-bit microprocessors. It loads a 12-bit word in two bytes using a single control; it can accept either a least significant byte or most significant byte first. For designs with a 12-bit or 16-bit wide data path, choose the DAC8222 or DAC8221.

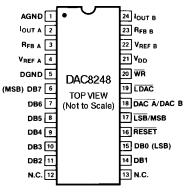

#### PIN CONNECTIONS

24-Pin 0.3" Cerdip (W Suffix), 24-Pin Epoxy DIP (P Suffix), 24-Pin SOL (S Suffix)

NC = NO CONNECT

The DAC8248's double-buffered digital inputs allow both DAC's analog output to be updated simultaneously. This is particularly useful in multiple DAC systems where a common LDAC signal updates all DACs at the same time. A single RESET pin resets both outputs to zero.

The DAC8248's monolithic construction offers excellent DAC-to-DAC matching and tracking over the full operating temperature range. The DAC consists of two thin-film R-2R resistor ladder networks, two 12-bit, two 8-bit, and two 4-bit data registers, and control logic circuitry. Separate reference input and feedback resistors are provided for each DAC. The DAC8248

(continued on page 4)

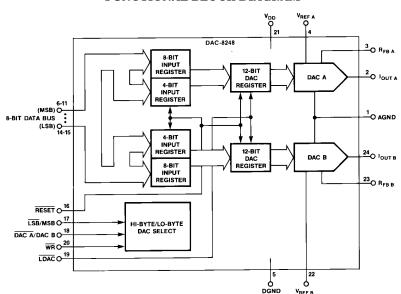

#### FUNCTIONAL BLOCK DIAGRAM

REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

## DAC8248\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

### COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

#### **DOCUMENTATION**

#### **Data Sheet**

DAC8248: Dual 12-Bit (8-Bit Byte) Double-Buffered CMOS D/A Converter Data Sheet

### REFERENCE MATERIALS 🖳

#### **Solutions Bulletins & Brochures**

• Digital to Analog Converters ICs Solutions Bulletin

#### DESIGN RESOURCES 🖳

- DAC8248 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

#### **DISCUSSIONS**

View all DAC8248 EngineerZone Discussions.

### SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

### **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# DAC8248-SPECIFICATIONS

**ELECTRICAL CHARACTERISTICS** (@  $V_{DD} = +5 \text{ V}$  or +15 V;  $V_{REFA} = V_{REFB} = +10 \text{ V}$ ;  $V_{OUTA} = V_{OUTB} = 0 \text{ V}$ ; AGND = DGND = 0 V;  $V_{AB} = V_{AB} =$

|                                                           |                                  |                                                                                            |      | DAC8248   |       |                          |

|-----------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------|------|-----------|-------|--------------------------|

| Parameter                                                 | Symbol                           | Conditions                                                                                 | Min  | Тур       | Max   | Units                    |

| STATIC ACCURACY                                           |                                  |                                                                                            |      |           |       |                          |

| Resolution                                                | N                                |                                                                                            | 12   |           |       | Bits                     |

| Relative Accuracy                                         | INL                              | DAC8248A/E/G                                                                               |      |           | ±1/2  | LSB                      |

| v                                                         |                                  | DAC8248F/H                                                                                 |      |           | ±1    | LSB                      |

| Differential Nonlinearity                                 | DNL                              | All Grades are Guaranteed Monotonic                                                        |      |           | ±1    | LSB                      |

| Full-Scale Gain Error <sup>1</sup>                        | $G_{ m FSE}$                     | DAC8248A/E                                                                                 |      |           | ±1    | LSB                      |

|                                                           | 152                              | DAC8248G                                                                                   |      |           | ±2    | LSB                      |

|                                                           |                                  | DAC8248F/H                                                                                 |      |           | ±4    | LSB                      |

| Gain Temperature Coefficient                              |                                  |                                                                                            |      |           |       |                          |

| $(\Delta Gain/\Delta Temperature)$                        | $TCG_{FS}$                       | (Notes 2, 3)                                                                               |      | $\pm 2$   | ±5    | ppm/°C                   |

|                                                           |                                  | All Digital Inputs = 0s                                                                    |      |           |       |                          |

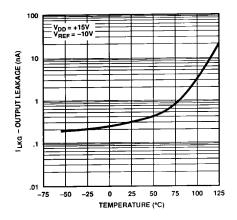

| Output Leakage Current                                    | $I_{LKG}$                        | $T_A = +25^{\circ}C$                                                                       |      | $\pm 5$   | ±10   |                          |

| $I_{OUT A}$ (Pin 2), $I_{OUT B}$ (Pin 24)                 |                                  | T <sub>A</sub> = Full Temperature Range                                                    |      |           | ±50   | nA                       |

| Input Resistance (V <sub>REF A</sub> , <sub>REF B</sub> ) | $R_{REF}$                        | (Note 4)                                                                                   | 8    | 11        | 15    | $\mathbf{k}\Omega$       |

|                                                           | $\Delta R_{REF}$                 |                                                                                            |      |           |       |                          |

| Input Resistance Match                                    | $\frac{\Delta R_{REF}}{R_{REF}}$ |                                                                                            |      | $\pm 0.2$ | ±1    | %                        |

| DIGITAL INPUTS                                            | 7027                             |                                                                                            |      |           |       |                          |

|                                                           | W                                | V = +5 V                                                                                   | 2.4  |           |       | V                        |

| Digital Input High                                        | $V_{INH}$                        | $V_{DD} = +5 \text{ V}$ $V_{DD} = +15 \text{ V}$                                           | 13.5 |           |       | V<br>V                   |

| Digital Input Low                                         | W                                | $V_{DD} = +13 \text{ V}$ $V_{DD} = +5 \text{ V}$                                           | 13.3 |           | 0.8   | V<br>V                   |

| Digital Iliput Low                                        | $V_{INL}$                        | $V_{DD} = +3 \text{ V}$ $V_{DD} = +15 \text{ V}$                                           |      |           | 1.5   | V<br>V                   |

| Input Current ( $V_{IN} = 0 \text{ V}$                    |                                  | $T_A = +25$ °C                                                                             |      | ±0.001    |       |                          |

| or $V_{DD}$ and $V_{INL}$ or $V_{INH}$ )                  | Т                                | $T_A = +23$ C<br>$T_A = Full$ Temperature Range                                            |      | ±0.001    | ±10   | μ <b>Α</b><br>μ <b>Α</b> |

| Input Capacitance                                         | I <sub>IN</sub>                  | DB0-DB11                                                                                   |      |           | 10    | μΑ<br>pF                 |

| (Note 2)                                                  | $C_{IN}$                         | $\overline{WR}$ , $\overline{LDAC}$ , $\overline{DAC}$ $\overline{A}/DAC$ $\overline{B}$ , |      |           | 10    | bī.                      |

| (Note 2)                                                  |                                  | LSB/MSB, RESET                                                                             |      |           | 15    | pF                       |

| POWER SUPPLY                                              |                                  | Espiriso, reser                                                                            |      |           | 10    | P                        |

| Supply Current                                            | $I_{DD}$                         | Digital Inputs = $V_{INL}$ or $V_{INH}$                                                    |      |           | 2     | mA                       |

| Supply Current                                            | 1DD                              | Digital Inputs = VINL of VINH Digital Inputs = 0 V or V <sub>DD</sub>                      |      | 10        | 100   | μA                       |

| DC Power Supply Rejection Ratio                           | PSRR                             | $\Delta V_{DD} = \pm 5\%$                                                                  |      | 10        | 100   | μΑ                       |

| $(\Delta Gain/\Delta V_{DD})$                             | 1 Diviv                          | 2 V DD - 20 %                                                                              |      |           | 0.002 | %/%                      |

| AC PERFORMANCE CHARACTE                                   | RISTICS <sup>2</sup>             |                                                                                            |      |           |       |                          |

| Propagation Delay <sup>5, 6</sup>                         | $t_{PD}$                         | $T_A = +25^{\circ}C$                                                                       |      |           | 350   | ns                       |

| Output Current Setting Time <sup>6, 7</sup>               | t <sub>S</sub>                   | $T_A = +25^{\circ}C$                                                                       |      |           | 1     | μs                       |

| Output Capacitance                                        | Co                               | Digital Inputs = All 0s                                                                    |      |           |       | ·                        |

|                                                           |                                  | C <sub>OUT A</sub> , C <sub>OUT B</sub>                                                    |      |           | 90    | pF                       |

|                                                           |                                  | Digital Inputs = All 1s                                                                    |      |           |       | •                        |

|                                                           |                                  | C <sub>OUT A</sub> , C <sub>OUT B</sub>                                                    |      |           | 120   | pF                       |

| AC Feedthrough at                                         | $FT_A$                           | $V_{REF A}$ to $I_{OUT A}$ ; $V_{REF A} = 20 \text{ V p-p}$                                |      |           |       | _                        |

| I <sub>OUT A</sub> or I <sub>OUT B</sub>                  |                                  | $f = 100 \text{ kHz}; T_A = +25^{\circ}\text{C}$                                           |      |           | -70   | dB                       |

|                                                           | $FT_B$                           | $V_{REF B}$ to $I_{OUT B}$ ; $V_{REF B} = 20 \text{ V p-p}$                                |      |           |       |                          |

|                                                           |                                  | $f = 100 \text{ kHz}; T_A = +25^{\circ}\text{C}$                                           |      |           | -70   | dB                       |

–2– REV. B

| Parameter                              | Symbol           | Conditions |       |                            | DAC8248         |                          | Units  |

|----------------------------------------|------------------|------------|-------|----------------------------|-----------------|--------------------------|--------|

|                                        | "                |            |       | $V_{DD} = +5 V$            |                 | $V_{DD} = +15 \text{ V}$ |        |

| Switching Characteristics (Notes 2, 8) |                  |            | +25°C | -40°C to +85°C<br>(Note 9) | -55°C to +125°C | All Temps<br>(Note 10)   |        |

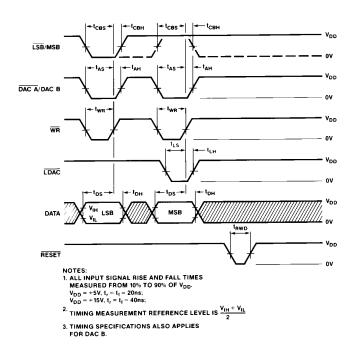

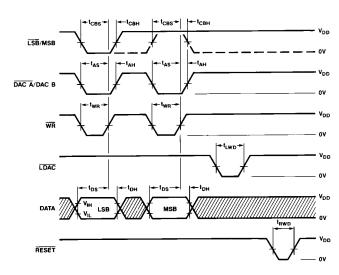

| LSB/MSB Select to                      |                  |            |       |                            |                 |                          |        |

| Write Set-Up Time LSB/MSB Select to    | t <sub>CBS</sub> |            | 130   | 170                        | 180             | 80                       | ns min |

| Write Hold Time<br>DAC Select to       | t <sub>CBH</sub> |            | 0     | 0                          | 0               | 0                        | ns min |

| Write Set-Up Time DAC Select to        | t <sub>AS</sub>  |            | 180   | 210                        | 220             | 80                       | ns min |

| Write Hold Time                        | t <sub>AH</sub>  |            | 0     | 0                          | 0               | 0                        | ns min |

| LDAC to Write Set-Up Time LDAC to      | t <sub>LS</sub>  |            | 120   | 150                        | 160             | 80                       | ns min |

| Write Hold Time Data Valid to          | t <sub>LH</sub>  |            | 0     | 0                          | 0               | 0                        | ns min |

| Write Set-Up Time Data Valid to        | t <sub>DS</sub>  |            | 160   | 210                        | 220             | 70                       | ns min |

| Write Hold Time                        | t <sub>DH</sub>  |            | 0     | 0                          | 0               | 10                       | ns min |

| Write Pulse Width                      | t <sub>WR</sub>  |            | 130   | 150                        | 170             | 90                       | ns min |

| LDAC Pulse Width                       | $t_{LWD}$        |            | 100   | 110                        | 130             | 60                       | ns min |

| Reset Pulse Width                      | $t_{ m RWD}$     |            | 80    | 90                         | 90              | 60                       | ns min |

Specifications subject to change without notice.

Burn-In Circuit

REV. B -3-

NOTES  $^{1}$ Measured using internal  $R_{FB\,A}$  and  $R_{FB\,B}$ . Both DAC digital inputs = 1111 1111 1111.  $^{2}$ Cuaranteed and not tested.  $^{3}$ Cain TC is measured from +25°C to  $T_{MIN}$  or from +25°C to  $T_{MAX}$ .  $^{4}$ Absolute Temperature Coefficient is approximately +50 ppm/°C.  $^{5}$ From 50% of digital input to 90% of final analog output current.  $V_{REF\,A} = V_{REF\,B} = +10$  V; OUT A, OUT B load = 100  $\Omega$ ,  $C_{EXT} = 13$  pF.  $^{6}$ WR,  $\overline{LDAC} = 0$  V; DB0-DB7 = 0 V to  $V_{DD}$  or  $V_{DD}$  to 0 V.  $^{7}$ Settling time is measured from 50% of the digital input change to where the output settles within 1/2 LSB of full scale.  $^{8}$ See Timing Diagram.  $^{9}$ These limits apply for the comparcial and industrial grade products.

These limits apply for the commercial and industrial grade products.  $^{10}$ These limits also apply as typical values for  $V_{DD} = +12$  V with +5 V CMOS logic levels and  $T_A = +25$ °C.

(continued from page 1)

operates on a single supply from +5 V to +15 V, and it dissipates less than 0.5 mW at +5 V (using zero or  $V_{\rm DD}$  logic levels). The device is packaged in a space-saving 0.3", 24-pin DIP.

The DAC8248 is manufactured with PMI's highly stable thinfilm resistors on an advanced oxide-isolated, silicon-gate, CMOS technology. PMI's improved latch-up resistant design eliminates the need for external protective Schottky diodes.

#### **ABSOLUTE MAXIMUM RATINGS**

| $(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$                             |

|-------------------------------------------------------------------------------------|

| $V_{DD}$ to AGND                                                                    |

| $V_{DD}$ to DGND                                                                    |

| AGND to DGND0.3 V, $V_{DD}$ +0.3 V                                                  |

| Digital Input Voltage to DGND $\dots -0.3 \text{ V}, \text{ V}_{DD} +0.3 \text{ V}$ |

| $I_{OUTA},I_{OUTB}$ to AGND0.3 V, $V_{DD}$ +0.3 V                                   |

| $V_{REFA},V_{REFB}$ to AGND±25 V                                                    |

| $V_{RFB\ A},V_{RFB\ B}$ to AGND±25 V                                                |

| Operating Temperature Range                                                         |

| AW Version                                                                          |

| EW, FW, FP Versions $-40^{\circ}$ C to $+85^{\circ}$ C                              |

| GP, HP, HS Versions $0^{\circ}$ C to $+70^{\circ}$ C                                |

| Junction Temperature +150°C                                                         |

| Storage Temperature65°C to +150°C                                                   |

| Lead Temperature (Soldering, 60 sec) +300°C                                         |

| Package Type            | $\theta_{JA}^{1}$ | $\theta_{JC}$ | Units |

|-------------------------|-------------------|---------------|-------|

| 24-Pin Hermetic DIP (W) | 69                | 10            | °C/W  |

| 24-Pin Plastic DIP (P)  | 62                | 32            | °C/W  |

| 24-Pin SOL (S)          | 72                | 24            | °C/W  |

#### NOTE

#### **CAUTION**

- Do not apply voltages higher than V<sub>DD</sub> or less than GND potential on any terminal except V<sub>REF</sub> and R<sub>FB</sub>.

- The digital control inputs are Zener-protected; however, permanent damage may occur on unprotected units from high energy electrostatic fields. Keep units in conductive foam at all times until ready to use.

- 3. Do not insert this device into powered sockets; remove power before insertion or removal.

- 4. Use proper antistatic handling procedures.

- 5. Devices can suffer permanent damage and/or reliability degradation if stressed above the limits listed under Absolute Maximum Ratings for extended periods. This is a stress rating only and functional operation at or above this specification is not implied.

#### ORDERING GUIDE1

| Model                                                                    | Relative<br>Accuracy<br>(+5 V or +15 V)                        | Gain Error<br>(+5 V or +15 V)                            | Temperature<br>Range                                                                                  | Package<br>Description                                                                                            |

|--------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| DAC8248AW <sup>2</sup> DAC8248EW DAC8248GP DAC8248FW DAC8248HP DAC8248FP | ±1/2 LSB<br>±1/2 LSB<br>±1/2 LSB<br>±1 LSB<br>±1 LSB<br>±1 LSB | ±1 LSB<br>±1 LSB<br>±2 LSB<br>±4 LSB<br>±4 LSB<br>±4 LSB | -55°C to +125°C<br>-40°C to +85°C<br>0°C to +70°C<br>-40°C to +85°C<br>0°C to +70°C<br>-40°C to +85°C | 24-Pin Cerdip<br>24-Pin Cerdip<br>24-Pin Plastic DIP<br>24-Pin Cerdip<br>24-Pin Plastic DIP<br>24-Pin Plastic DIP |

| DAC8248HS <sup>3</sup>                                                   | ±1 LSB                                                         | ±4 LSB                                                   | 0°C to +70°C                                                                                          | 24-Pin SOL                                                                                                        |

#### NOTES

#### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the DAC8248 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

\_ REV. B

$<sup>^{1}\</sup>theta_{JA}$  specified for worst case mounting conditions, i.e.,  $\theta_{JA}$  is specified for device in socket for cerdip and P-DIP packages;  $\theta_{JA}$  is specified for device soldered to printed circuit board for SOL package.

<sup>&</sup>lt;sup>1</sup>Burn-in is available on commercial and industrial temperature range parts in cerdip, plastic DIP, and TO-can packages.

<sup>&</sup>lt;sup>2</sup>For devices processed in total compliance to MIL-STD-883, add/883 after part number. Consult factory for 883 data sheet.

<sup>&</sup>lt;sup>3</sup>For availability and burn-in information on SO and PLCC packages, contact your local sales office.

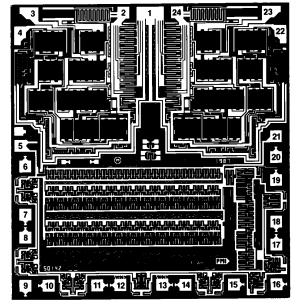

#### **DICE CHARACTERISTICS**

Die Size 0.124 × 0.132 inch, 16,368 sq. mils (3.15 × 3.55 mm, 10.56 sq. mm)

| 1. AGND               | 13. NC                 |

|-----------------------|------------------------|

| 2. I <sub>OUTA</sub>  | 14. DB1                |

| 3. R <sub>FB A</sub>  | 15. DB0(LSB)           |

| 4. V <sub>REF A</sub> | 16. RESET              |

| 5. DGND               | 17. <b>LSB</b> /MSB    |

| 6. DB7(MSB)           | 18. DAC A/DAC B        |

| 7. DB6                | 19. <b>LDAC</b>        |

| 8. DB5                | 20. WR                 |

| 9. DB4                | 21. V <sub>DD</sub>    |

| 10. DB3               | 22. V <sub>REF B</sub> |

| 11. DB2               | 23. R <sub>FB B</sub>  |

| 12. NC                | 24. I <sub>OUT B</sub> |

SUBSTRATE (DIE BACKSIDE) IS INTERNALLY CONNECTED TO  $\ensuremath{V_{\text{DD}}}.$

###

| Parameter                                     | Symbol                     | Conditions                                                 | DAC8248G<br>Limit | Units                        |

|-----------------------------------------------|----------------------------|------------------------------------------------------------|-------------------|------------------------------|

| Relative Accuracy                             | INL                        | Endpoint Linearity Error                                   | ±1                | LSB max                      |

| Differential Nonlinearity                     | DNL                        | All Grades are Guaranteed Monotonic                        | $\pm 1$           | LSB max                      |

| Full-Scale Gain Error <sup>1</sup>            | $G_{ m FSE}$               | Digital Inputs = 1111 1111 1111                            | $\pm 4$           | LSB max                      |

| Output Leakage                                |                            | Digital Inputs = 0000 0000 0000                            |                   |                              |

| (I <sub>OUT A</sub> , I <sub>OUT B</sub> )    | $I_{LKG}$                  | Pads 2 and 24                                              | $\pm 50$          | nA max                       |

| Input Resistance                              |                            |                                                            |                   |                              |

| $(V_{REF A}, V_{REF B})$                      | $R_{ m REF}$               | Pads 4 and 22                                              | 8/15              | $k\Omega$ min/ $k\Omega$ max |

| V <sub>REF A</sub> , V <sub>REF B</sub> Input | $\Delta R_{ m REF}$        |                                                            |                   |                              |

| Resistance Match                              | $\overline{ m R}_{ m REF}$ |                                                            | ±1                | % max                        |

| Digital Input High                            | $V_{INH}$                  | $V_{\rm DD} = +5 \text{ V}$                                | 2.4               | V min                        |

|                                               |                            | $V_{\rm DD} = +15 \text{ V}$                               | 13.5              | V min                        |

| Digital Input Low                             | $V_{INL}$                  | $V_{\rm DD} = +5 \text{ V}$                                | 0.8               | V max                        |

|                                               |                            | $V_{\mathrm{DD}} = +15 \mathrm{V}$                         | 1.5               | V max                        |

| Digital Input Current                         | $I_{IN}$                   | $V_{IN} = 0 \text{ V or } V_{DD}$ ; $V_{INL}$ or $V_{INH}$ | ±1                | μA max                       |

| Supply Current                                | $I_{\mathrm{DD}}$          | All Digital Inputs V <sub>INL</sub> or V <sub>INH</sub>    | 2                 | mA max                       |

|                                               |                            | All Digital Inputs 0 V or V <sub>DD</sub>                  | 0.1               | mA max                       |

| DC Supply Rejection                           |                            |                                                            |                   |                              |

| $(\Delta Gain/\Delta V_{DD})$                 | PSR                        | $\Delta V_{\mathrm{DD}} = \pm 5\%$                         | 0.002             | %/% max                      |

NOTES

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

REV. B \_5\_

$<sup>^{1}</sup>Measured$  using internal  $R_{FB\;A}$  and  $R_{FB\;B}.$

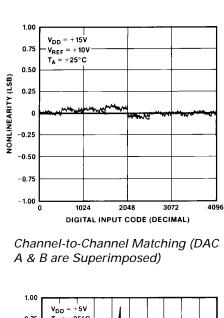

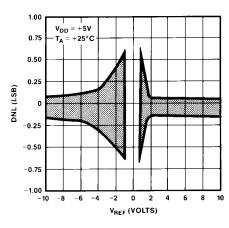

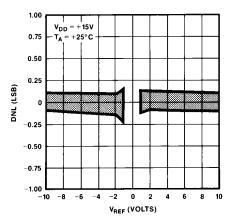

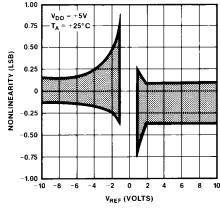

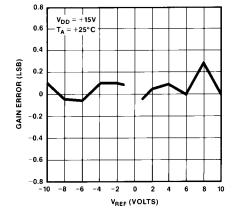

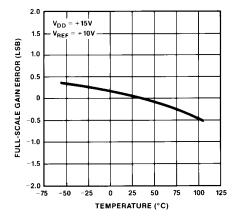

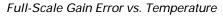

### **DAC8248**–Typical Performance Characteristics

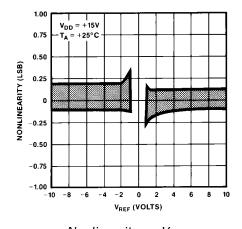

Differential Nonlinearity vs.  $V_{REF}$

Differential Nonlinearity vs.  $V_{REF}$

Nonlinearity vs.  $V_{REF}$

Nonlinearity vs.  $V_{REF}$

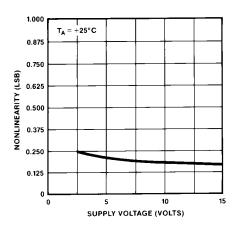

Nonlinearity vs. V<sub>DD</sub>

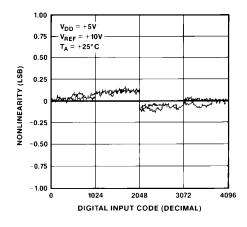

Nonlinearity vs. Code (DAC A & B are Superimposed)

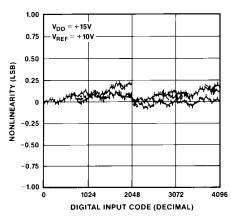

Nonlinearity vs. Code at  $T_A = -55^{\circ}C$ ,  $+25^{\circ}C$ ,  $+125^{\circ}C$  for DAC A & B (All Superimposed)

Absolute Gain Error Change vs. V<sub>REF</sub>

-6- REV. B

Logic Input Threshold Voltage vs. Supply Voltage ( $V_{DD}$ )

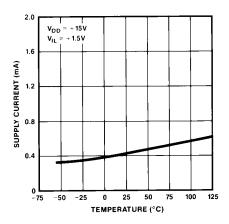

Supply Current vs. Temperature

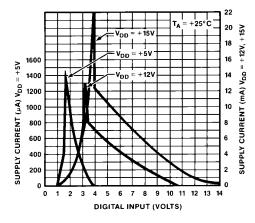

Supply Current vs. Logic Input Voltage

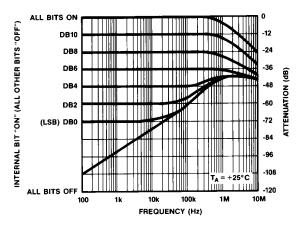

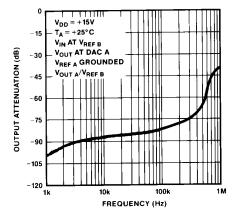

Multiplying Mode Frequency Response vs. Digital Code

Output Leakage Current vs. Temperature

Analog Crosstalk vs. Frequency

REV. B \_\_7\_

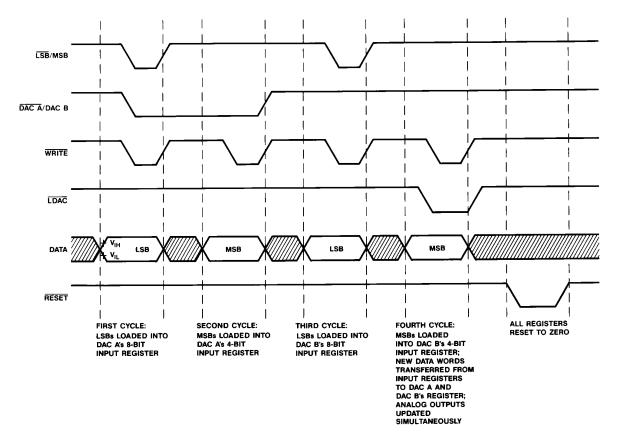

Four Cycle Update

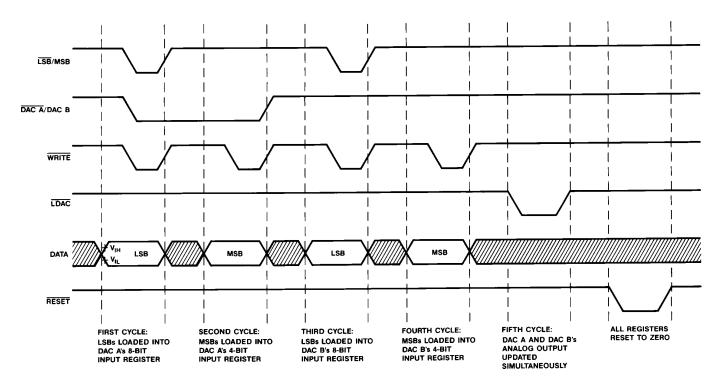

Five Cycle Update

Write Timing Cycle Diagram

-8-

#### PARAMETER DEFINITIONS

#### RESOLUTION (N)

The resolution of a DAC is the number of states (2<sup>n</sup>) that the full-scale range (FSR) is divided (or resolved) into; where n is equal to the number of bits.

#### **RELATIVE ACCURACY (INL)**

Relative accuracy, or integral nonlinearity, is the maximum deviation of the analog output (from the ideal) from a straight line drawn between the end points. It is expressed in terms of least significant bit (LSB), or as a percent of full scale.

#### DIFFERENTIAL NONLINEARITY (DNL)

Differential nonlinearity is the worst case deviation of any adjacent analog output from the ideal 1 LSB step size. The deviation of the actual "step size" from the ideal step size of 1 LSB is called the differential nonlinearity error or DNL. DACs with DNL greater than  $\pm 1$  LSB may be nonmonotonic.  $\pm 1/2$  LSB INL guarantees monotonicity and  $\pm 1$  LSB maximum DNL.

#### GAIN ERROR (G<sub>FSE</sub>)

Gain error is the difference between the actual and the ideal analog output range, expressed as a percent of full-scale or in terms of LSB value. It is the deviation in slope of the DAC transfer characteristic from ideal.

Refer to PMI 1990/91 Data Book, Section 11, for additional digital-to-analog converter definitions.

#### GENERAL CIRCUIT DESCRIPTION

#### **CONVERTER SECTION**

The DAC8248 incorporates two multiplying 12-bit current output CMOS digital-to-analog converters on one monolithic chip. It contains two highly stable thin-film R-2R resistor ladder networks, two 12-bit DAC registers, two 8-bit input registers, and two 4-bit input registers. It also contains the DAC control logic circuitry and 24 single-pole, double-throw NMOS transistor current switches.

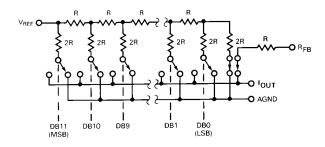

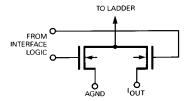

Figure 1 shows a simplified circuit for the R-2R ladder and transistor switches for a single DAC. R is typically 11 k $\Omega$ . The transistor switches are binarily scaled in size to maintain a constant voltage drop across each switch. Figure 2 shows a single NMOS transistor switch.

Figure 1. Simplified Single DAC Circuit Configuration. (Switches Are Shown For All Digital Inputs at Zero)

Figure 2. N-Channel Current Steering Switch

The binary-weighted currents are switched between  $I_{OUT}$  and AGND by the transistor switches. Selection between  $I_{OUT}$  and AGND is determined by the digital input code. It is important to keep the voltage difference between  $I_{OUT}$  and AGND terminals as close to zero as practical to preserve data sheet limits. It is easily accomplished by connecting the DAC's AGND to the noninverting input of an operational amplifier and  $I_{OUT}$  to the inverting input. The amplifier's feedback resistor can be eliminated by connecting the op amp's output directly to the DAC's  $R_{FB}$  terminal (by using the DAC's internal feedback resistor,  $R_{FB}$ ). The amplifier also provides the current-to-voltage conversion for the DAC's output current.

The output voltage is dependent on the DAC's digital input code and  $V_{REF}$ , and is given by:

$$V_{OUT} = V_{REF} \times D/4096$$

where D is the digital input code integer number that is between 0 and 4095.

The DAC's input resistance,  $R_{REF}$ , is always equal to a constant value, R. This means that  $V_{REF}$  can be driven by a reference voltage or current, ac or dc (positive or negative). It is recommended that a low temperature-coefficient external  $R_{FB}$  resistor be used if a current source is employed.

The DAC's output capacitance ( $C_{\rm OUT}$ ) is code dependent and varies from 90 pF (all digital inputs low) to 120 pF (all digital inputs high).

To ensure accuracy over the full operating temperature range, permanently turned "ON" MOS transistor switches were included in series with the feedback resistor ( $R_{FB}$ ) and the R-2R ladder's terminating resistor (see Figure 1). The gates of these NMOS transistors are internally connected to  $V_{\rm DD}$  and will be turned "OFF" (open) if  $V_{\rm DD}$  is not applied. If an op amp is using the DAC's  $R_{FB}$  resistor to close its feedback loop, then  $V_{\rm DD}$  must be applied before or at the same time as the op amp's supply; this will prevent the op amp's output from becoming "open circuited" and swinging to either rail. In addition, some applications require the DAC's ladder resistance to fall within a certain range and are measured at incoming inspection;  $V_{\rm DD}$  must be applied before these measurements can be made.

#### **DIGITAL SECTION**

The DAC8248's digital inputs are TTL compatible at  $V_{DD} = +5~V$  and CMOS compatible at  $V_{DD} = +15~V$ . They were designed to convert TTL and CMOS input logic levels into voltage levels that will drive the internal circuitry. The DAC8248 can use +5~V CMOS logic levels with  $V_{DD} = +12~V$ ; however, supply current will increase to approximately 5~mA-6~mA.

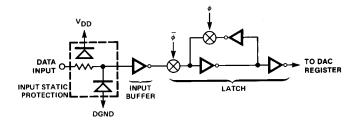

Figure 3 shows the DAC's digital input structure for one bit. This circuitry drives the DAC registers. Digital controls,  $\phi$  and  $\bar{\phi}$ , shown are generated from the DAC's input control logic circuitry.

Figure 3. Digital Input Structure For One Bit

The digital inputs are electrostatic-discharge (ESD) protected with two internal distributed diodes as shown in Figure 3; they are connected between  $V_{\rm DD}$  and DGND. Each input has a typical input current of less than 1 nA.

The digital inputs are CMOS inverters and draw supply current when operating in their linear region. Using a +5 V supply, the linear region is between +1.2 V to +2.8 V with current peaking at +1.8 V. Using a +15 V supply, the linear region is from +1.2 V to +12 V (current peaking at +3.9 V). It is recommended that the digital inputs be operated as close to the power supply voltage and DGND as is practically possible; this will keep supply currents to a minimum. The DAC8248 may be operated with any supply voltage between the range of +5 V to +15 V and still perform to data sheet limits.

The DAC8248's 8-bit wide data port loads a 12-bit word in two bytes: 8-bits then 4-bits (or 4-bits first then 8-bits, at users discretion) in a right justified data format. This data is loaded into the input registers with the  $\overline{LSB}/MSB$  and  $\overline{WR}$  control pins.

Data transfer from the input registers to the DAC registers can be automatic. It can occur upon loading of the second data byte into the input register, or can occur at a later time through a strobed transfer using the  $\overline{\text{LDAC}}$  control pin.

REV. B \_\_9\_

Figure 4. Four Cycle Update Timing Diagram

Figure 5. Five Cycle Update Timing Diagram

-10- REV. B

#### **AUTOMATIC DATA TRANSFER MODE**

Data may be transferred automatically from the input register to the DAC register. The first cycle loads the first data byte into the input register; the second cycle loads the second data byte and simultaneously transfers the full 12-bit data word to the DAC register. It takes four cycles to load and transfer two complete digital words for both DAC's, see Figure 4 (Four Cycle Update Timing Diagram) and the Mode Selection Table.

#### STROBED DATA TRANSFER MODE

Strobed data transfer allows the full 12-bit digital word to be loaded into the input registers and transferred to the DAC registers at a later time. This transfer mode requires five cycles: four to load two new data words into both DACs, and the fifth to transfer all data into the DAC registers. See Figure 5 (Five Cycle Update Timing Diagram) and the Mode Selection Table.

Strobed data transfer separating data loading and transfer operations serves two functions: the DAC output updating may be more precisely controlled, and multiple DACs in a multiple DAC system can be updated simultaneously.

#### RESET

The DAC8248 comes with a  $\overline{RESET}$  pin that is useful in system calibration cycles and/or during system power-up. All registers are reset to zero when  $\overline{RESET}$  is low, and latched at zero on the rising edge of the  $\overline{RESET}$  signal when  $\overline{WRITE}$  is high.

#### INTERFACE CONTROL LOGIC

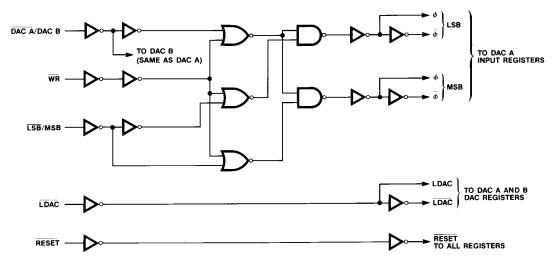

The DAC8248's control logic is shown in Figure 6. This circuitry interfaces with the system bus and controls the DAC functions.

Figure 6. Input Control Logic

#### MODE SELECTION TABLE

| DIGITAL INPUTS |                                   |         |         |             | <b>REGIS</b> | TER STATUS | S           |         |         |          |

|----------------|-----------------------------------|---------|---------|-------------|--------------|------------|-------------|---------|---------|----------|

|                |                                   |         |         |             |              | DAC A      |             |         | DAC B   |          |

|                |                                   |         |         |             | Input R      | egister    | DAC         | Input R | egister | DAC      |

| DAC A/B        | $\overline{\mathbf{W}}\mathbf{R}$ | LSB/MSB | RESET   | <b>LDAC</b> | LSB          | MSB        | Register    | LSB     | MSB     | Register |

| Ĺ              | L                                 | L       | Н       | Н           | WR           | LAT        | LAT         | LAT     | LAT     | LAT      |

| Ĺ              | L                                 | L       | H       | L           | WR           | LAT        | WR          | LAT     | LAT     | WR       |

| Ĺ              | L                                 | Н       | Н       | Н           | LAT          | WR         | LAT         | LAT     | LAT     | LAT      |

| Ĺ              | L                                 | Н       | Н       | L           | LAT          | WR         | WR          | LAT     | LAT     | WR       |

| Н              | L                                 | L       | Н       | Н           | LAT          | LAT        | LAT         | WR      | LAT     | LAT      |

| Н              | L                                 | L       | Н       | L           | LAT          | LAT        | WR          | WR      | LAT     | WR       |

| H              | L                                 | Н       | Н       | Н           | LAT          | LAT        | LAT         | LAT     | WR      | LAT      |

| H              | L                                 | Н       | Н       | L           | LAT          | LAT        | WR          | LAT     | WR      | WR       |

| X              | Н                                 | X       | Н       | Н           | LAT          | LAT        | LAT         | LAT     | LAT     | LAT      |

| K              | Н                                 | X       | Н       | L           | LAT          | LAT        | WR          | LAT     | LAT     | WR       |

| ζ              | X                                 | X       | L       | X           | ALL RE       | GISTERS A  | ARE RESET T | O ZEROS |         |          |

| X              | Н                                 | X       | <b></b> | X           | ZEROS        | ARE LATC   | HED IN ALL  | REGISTE | ERS     |          |

L = Low, H = High, X = Don't Care, WR = Registers Being Loaded, LAT = Registers Latched.

REV. B -11-

#### INTERFACE CONTROL LOGIC PIN FUNCTIONS

LSB/MSB - (PIN 17) LEAST SIGNIFICANT BIT (Active Low)/ MOST SIGNIFICANT BIT (Active High). Selects lower 8-bits (LSBs) or upper 4-bits (MSBs); either can be loaded first. It is used with the WR signal to load data into the input registers. Data is loaded in a right justified format.

**DAC A/DAC B - (PIN 18) DAC SELECTION.** Active low for DAC A and Active High for DAC B.

$\overline{WR}$  – (PIN 20)  $\overline{WRITE}$  – Active Low. Used with the  $\overline{LSB}/$  MSB signal to load data into the input registers, or Active High to latch data into the input registers.

$\overline{\text{LDAC}}$  – **(PIN 19) LOAD DAC.** Used to transfer data simultaneously from DAC A and DAC B input registers to both DAC output registers. The DAC register becomes transparent (activity on the digital inputs appear at the analog output) when both  $\overline{\text{WR}}$  and  $\overline{\text{LDAC}}$  are low. Data is latched into the output registers on the rising edge of  $\overline{\text{LDAC}}$ .

**RESET** – **(PIN 16)** – **Active Low.** Functions as a zero override; all registers are forced to zero when the **RESET** signal is low. All registers are latched to zeros when the write signal is high and **RESET** goes high.

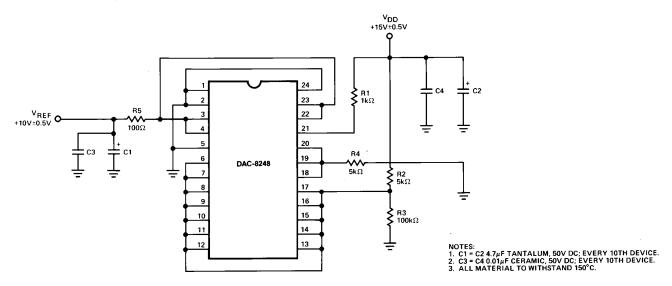

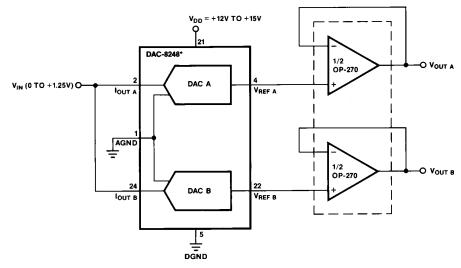

## APPLICATIONS INFORMATION UNIPOLAR OPERATION

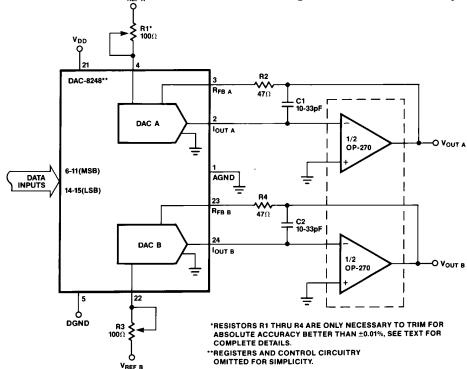

Figure 7 shows a simple unipolar (2-quadrant multiplication) circuit using the DAC8248 and OP270 dual op amp (use two OP42s for applications requiring higher speeds), and Table I shows the corresponding code table. Resistors R1, R2, and R3, R4 are used only if full-scale gain adjustments are required.

Table I. Unipolar Binary Code Table (Refer to Figure 7)

| Binary Number<br>DAC Register<br>MSB LS | Analog Output, V <sub>OUT</sub>                                 |

|-----------------------------------------|-----------------------------------------------------------------|

| 1111 1111 1111                          | $-V_{REF}\left(\frac{4095}{4096}\right)$                        |

| 1000 0000 0000                          | $-V_{REF} \left(\frac{2048}{4096}\right) = -\frac{1}{2}V_{REF}$ |

| 0000 0000 0001                          | $-V_{REF}\left(\frac{1}{4096}\right)$                           |

| 0000 0000 0000                          | 0 V                                                             |

NOTE

1 LSB =

$$(2^{-12})$$

$(V_{REF}) = \frac{1}{4096}$   $(V_{REF})$

Low temperature-coefficient (approximately 50 ppm/ $^{\circ}$ C) resistors or trimmers should be used. Maximum full-scale error without these resistors for the top grade device and  $V_{REF} = \pm 10$  V is 0.024%, and 0.049% for the low grade. Capacitors C1 and C2 provide phase compensation to reduce overshoot and ringing when high-speed op amps are used.

Full-scale adjustment is achieved by loading the appropriate DAC's digital inputs with 1111 1111 1111 and adjusting R1 (or R3 for DAC B) so that:

$$V_{OUT} = V_{REF} \times \left(\frac{4095}{4096}\right)$$

Full-scale can also be adjusted by varying  $V_{REF}$  voltage and eliminating R1, R2, R3, and R4. Zero adjustment is performed by

Figure 7. Unipolar Configuration (2-Ouadrant Multiplication)

–12– REV. B

loading the appropriate DAC's digital inputs with 0000 0000 0000 and adjusting the op amp's offset voltage to 0 V. It is recommended that the op amp offset voltage be adjusted to less than 10% of 1 LSB (244  $\mu V$ ), and over the operating temperature range of interest. This will ensure the DAC's monotonicity and minimize gain and linearity errors.

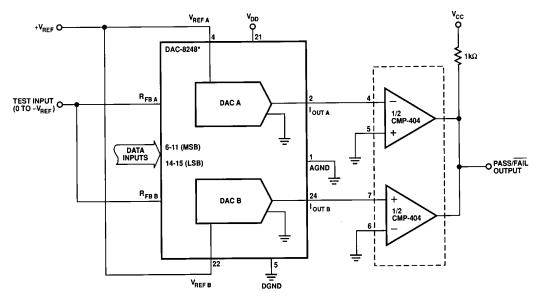

#### BIPOLAR OPERATION

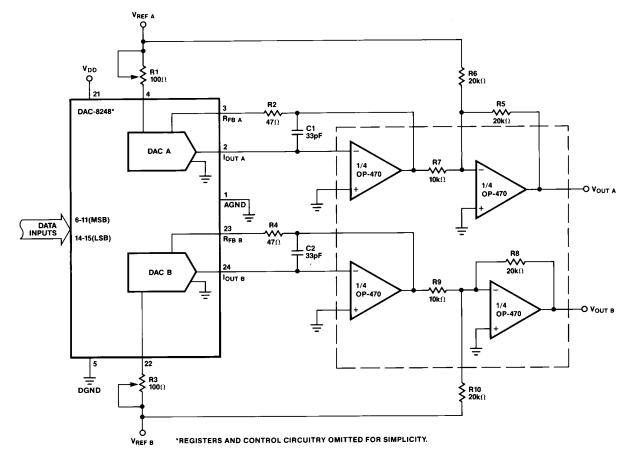

The bipolar (offset binary) 4-quadrant configuration using the DAC8248 is shown in Figure 8, and the corresponding code is shown in Table II. The circuit makes use of the OP470, a quad op amp (use four OP42s for applications requiring higher speeds).

The full-scale output voltage may be adjusted by varying  $V_{REF}$  or the value of R5 and R8, and thus eliminating resistors R1, R2, R3, and R4. If resistors R1 through R4 are omitted, then R5, R6, R7 (R8, R9, and R10 for DAC B) should be ratio-matched to 0.01% to keep gain error within data sheet specifications. The resistors should have identical temperature-coefficients if operating over the full temperature range.

Zero and full-scale are adjusted in one of two ways and are at the users discretion. Zero-output is adjusted by loading the appropriate DAC's digital inputs with 1000 0000 0000 and varying R1 (R3 for DAC B) so that  $V_{\rm OUT\,A}$  (or  $V_{\rm OUT\,B}$ ) equals 0 V. If R1, R2 (R3, R4 for DAC B) are omitted, then zero output can be adjusted by varying R6, R7 ratios (R9, R10 for DAC B). Full-scale is adjusted by loading the appropriate DAC's digital inputs with 1111 1111 1111 and varying R5 (R8 for DAC B).

Table II. Bipolar (Offset Binary) Code Table (Refer to Figure 8)

| Binary Number in<br>DAC Register<br>MSB LSB | Analog Output, V <sub>OUT</sub><br>(DAC A or DAC B) |

|---------------------------------------------|-----------------------------------------------------|

| 1111 1111 1111                              | $+V_{REF}\left(\frac{2047}{2048}\right)$            |

| 1000 0000 0001                              | $+V_{REF}\left(\frac{1}{2048}\right)$               |

| 1000 0000 0000                              | 0 V                                                 |

| 0111 1111 1111                              | $-V_{REF}\left(\frac{1}{2048}\right)$               |

| 0000 0000 0000                              | $-V_{REF}\left(\frac{2048}{2048}\right)$            |

NOTE:

1 LSB=

$$(2^{-11})(V_{REF}) = \frac{1}{2048}(V_{REF})$$

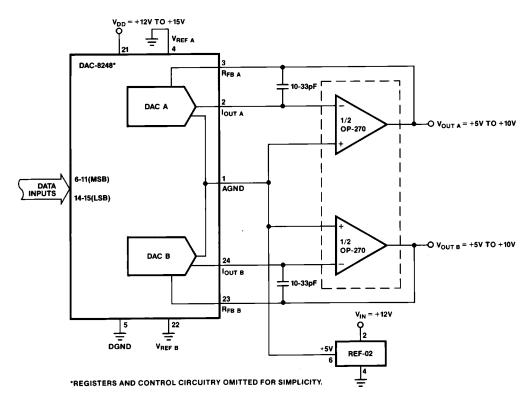

#### SINGLE SUPPLY OPERATION

#### **CURRENT STEERING MODE**

Because the DAC8248's R-2R resistor ladder terminating resistor is internally connected to AGND, it lends itself well for single supply operation in the current steering mode configuration. This means that AGND can be raised above system

Figure 8. Bipolar Configuration (4-Quadrant Multiplication)

ground as shown in Figure 9. The output voltage will be between +5 V and +10 V depending on the digital input code. The output expression is given by:

$$V_{OUT} = V_{OS} \times (D/4096) \, (V_{OS})$$

where  $V_{OS}$  = Offset Reference Voltage (+5 V in Figure 9)

D = Decimal Equivalent of the Digital Input Word

#### **VOLTAGE SWITCHING MODE**

Figure 10 shows the DAC8248 in another single supply configuration. The R-2R ladder is used in the voltage switching mode and functions as a voltage divider. The output voltage (at the  $V_{REF}$  pin) exhibits a constant impedance R (typically 11  $k\Omega$ ) and must be buffered by an op amp. The  $R_{FB}$  pins are not used and are left open. The reference input voltage must be maintained within +1.25 V of AGND, and  $V_{DD}$  between +12 V and +15 V; this ensures that device accuracy is preserved.

The output voltage expression is given by:

$$V_{OUT} = V_{REF} (D/4096)$$

where D = Decimal Equivalent of the Digital Input Word

#### APPLICATIONS TIPS

#### GENERAL GROUND MANAGEMENT

Grounding techniques should be tailored to each individual system. Ground loops should be avoided, and ground current paths should be as short as possible and have a low impedance.

The DAC8248's AGND and DGND pins should be tied together at the device socket to prevent digital transients from appearing at the analog output. This common point then becomes the single ground point connection. AGND and DGND is then brought out separately and tied to their respective power supply grounds. Ground loops can be created if both grounds are tied together at more than one location, i.e., tied together at the device and at the digital and analog power supplies.

PC board ground plane can be used for the single point ground connection should the connections not be practical at the device socket. If neither of these connections are practical or allowed, then the device should be placed as close as possible to the systems single point ground connection. Back-to-back Schottky diodes should then be connected between AGND and DGND.

#### POWER SUPPLY DECOUPLING

Power supplies used with the DAC8248 should be well filtered and regulated. Local supply decoupling consisting of a 1  $\mu F$  to 10  $\mu F$  tantalum capacitor in parallel with a 0.1  $\mu F$  ceramic is highly recommended. The capacitors should be connected between the  $V_{DD}$  and DGND pins and at the device socket.

Figure 9. Single Supply Operation (Current Switching Mode)

–14– REV. B

\*REGISTERS AND DIGITAL CIRCUITRY OMITTED FOR SIMPLICITY.

Figure 10. Single Supply Operation (Voltage Switching Mode)

'REGISTERS AND CONTROL CIRCUITRY OMITTED FOR SIMPLICITY.

Figure 11. Digitally-Programmable Window Detector (Upper/Lower Limit Detector)

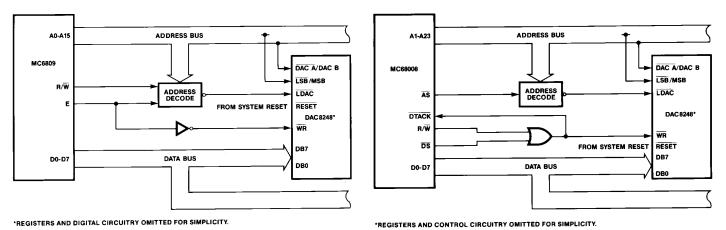

#### MICROPROCESSOR INTERFACE CIRCUITS

The DAC8248s versatile loading structure allows direct interface to an 8-bit microprocessor. Its simplicity reduces the number of required glue logic components. Figures 12 and 13 show the DAC8248 interface configurations with the MC6809 and MC68008 microprocessors.

REV. B -15-

Figure 12. DAC8248 to MC6809 Interface

Figure 13. DAC8248 to MC68008 Interface

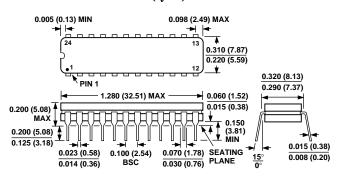

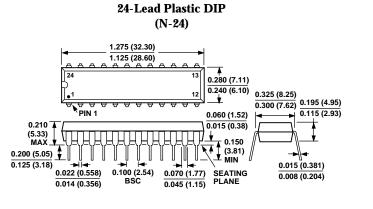

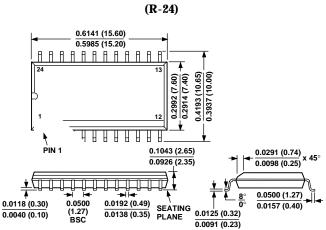

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 24-Lead Cerdip (Q-24)

24 Lead SOL