### **Typical Applications**

The HMC750LP4(E) is ideal for:

- OC-192 Receivers

- 10 Gbps Ethernet Receivers

- 10 Gbps Fiber Channel Receivers

- Broadband Test & Measurement

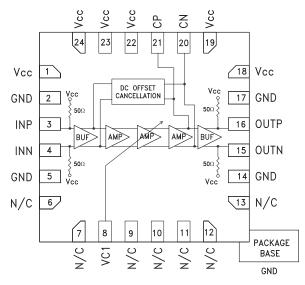

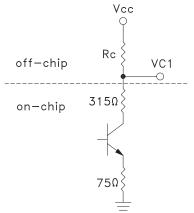

#### **Functional Diagram**

## HMC750LP4 / 750LP4E

### 12.5 Gbps LIMITING AMPLIFIER

#### Features

Supports Data Rates up to 12.5 Gbps Differential Gain: 44 dB 2mV p-p input Sensitivity 3 dB Bandwidth: 11 GHz Integrated DC Offset Correction Adjustable Differential Saturated O/P Voltage Swing up to 880 mVp-p Single +5V Power Supply Very Low RMS Jitter Degradation 24 Lead Plastic 4x4mm SMT Package: 16mm<sup>2</sup>

### **General Description**

HMC750LP4E is a limiting amplifier designed to support data transmission rates up to 12.5 Gbps. The amplifier can operate over a wide range of input voltage levels and provides constant-level differential output swing. HMC750LP4E also features an output level control pin, VC1, which allows for loss compensation or for signal level optimization. Differential output signal swing can be adjustable up to 880 mVp-p. Input signals higher than 3mV p-p can be amplified to saturated 880mV p-p differential signal.

All single-ended input signals to the HMC750LP4E are terminated with 50 ohms to +5V on-chip, and may be either AC or DC coupled. The outputs of the HMC750LP4E may be operated either differentially or single-ended. Outputs can be connected directly to a 50 ohm terminated system referenced to +5V, while DC blocking capacitors may be used if the terminating system is 50 ohms to a non +5V voltage. The HMC750LP4E operates from a single + 5V DC supply and is available in a plastic RoHS compliant 4x4 mm SMT package.

### Electrical Specifications, $T_A = +25^{\circ} C$ , Vcc = +5V, VC1 = +2.5V

| Parameter                             | Conditions                | Min. | Тур. | Max. | Units  |

|---------------------------------------|---------------------------|------|------|------|--------|

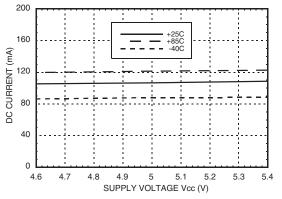

| Power Supply Voltage                  |                           | 4.6  | 5    | 5.4  | V      |

| Power Supply Current                  | VC1 = 2.5V                |      | 106  | 122  | mA     |

| Maximum Data Rate                     |                           |      | 12.5 |      | Gbps   |

| Differential Small Signal Gain        | VC1 = 2.5V                |      | 44   |      | dB     |

| Small Signal Bandwidth                | 3-dB Cutoff               |      | 11   |      | GHz    |

| Deterministic Jitter <sup>[1]</sup>   | Vin = 20 mV peak to peak  |      | 5    |      | ps p-p |

| Additive Random Jitter <sup>[2]</sup> | Vin = 200 mV peak to peak |      |      | 0.2  | ps rms |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# HMC750\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### EVALUATION KITS

HMC750LP4 Evaluation Board

### **DOCUMENTATION**

#### Data Sheet

• HMC750 Data Sheet

### REFERENCE MATERIALS

#### **Quality Documentation**

- Package/Assembly Qualification Test Report: LP4, LP4B, LP4C, LP4K (QTR: 2013-00487 REV: 04)

- Semiconductor Qualification Test Report: BiCMOS-A (QTR: 2013-00235)

### DESIGN RESOURCES

- HMC750 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all HMC750 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

v03.0111

### 12.5 Gbps LIMITING AMPLIFIER

#### Electrical Specifications (Conditions)

| Parameter             | Conditions                                                       | Min. | Тур. | Max. | Units |

|-----------------------|------------------------------------------------------------------|------|------|------|-------|

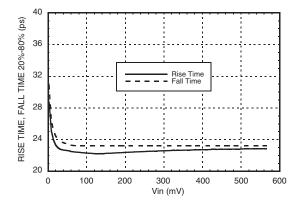

| Rise Time             | 20% - 80%                                                        |      | 23   | 27   | ps    |

| Fall Time             | 20% - 80%                                                        |      | 21   | 23   | ps    |

| Data Output Swing     | Differential Output Swing.<br>VC1 = 3V for maximum output swing. | 850  | 880  |      | mVp-p |

| Input Return Loss     | up to 10 GHz                                                     | 15   |      |      | dB    |

| Output Return Loss    | up to 10 GHz                                                     | 8    |      |      | dB    |

| Input Sensitivity     |                                                                  | 2    |      |      | mVp-p |

| Maximum Input Swing   |                                                                  |      | 1200 |      | mVp-p |

| Output Offset Voltage | VC1 = 3V for maximum output swing                                |      | 3    |      | mV    |

| VC1                   |                                                                  | 2    |      | 3    | V     |

| Vout DC               |                                                                  | 4.5  |      | 4.8  | V     |

[1] Deterministic jitter measured at 10 Gbps with PRBS 2<sup>23</sup>-1 pattern. It is the peak to peak deviation from the ideal time crossing [2] Random jitter is measured with 10 Gbps 10101... pattern

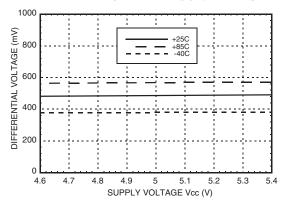

#### Differential Output vs. Supply Voltage [1]

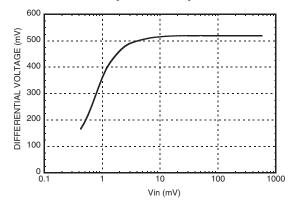

#### Differential Output vs. Vinput [1][2]

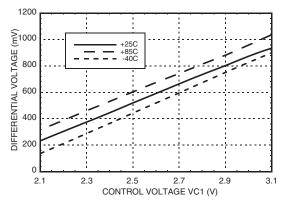

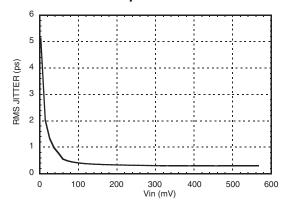

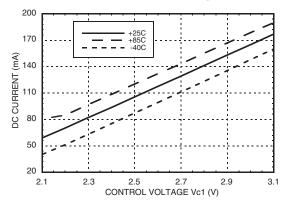

#### [1] VC1 = 2.5V [2] Vcc = 5V [3] Input Data Rate = 10 Gbps

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

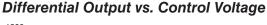

#### Differential Output vs. Control Voltage [2]

#### RMS Jitter vs. Vinput [1][2][3]

LIMITING AMPLIFIERS - SMT

6

#### Rise & Fall Time vs. Vinput [1] [2] [3]

DC Current vs. Control Voltage [2] [3]

DC Current vs. Supply Voltage <sup>[1] [3]</sup>

HMC750LP4 / 750LP4E

**12.5 Gbps LIMITING AMPLIFIER**

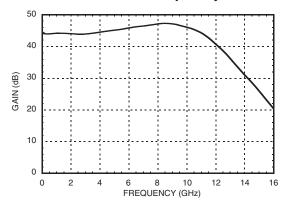

Differential Gain vs. Frequency <sup>[1] [2]</sup>

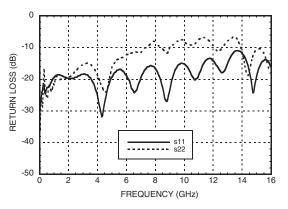

Return Loss [1] [2]

#### [1] VC1 = 2.5V [2] Vcc = 5V [3] Input Data Rate = 10 Gbps

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### HMC750LP4 / 750LP4E

### 12.5 Gbps LIMITING AMPLIFIER

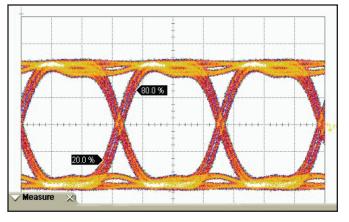

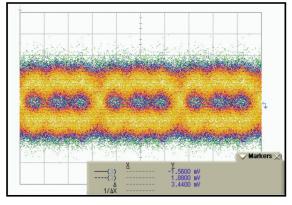

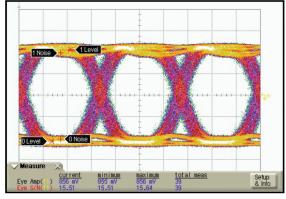

#### **Output Eye Diagram**

|                                    | Cur      | rent | Minimum       | Maximum  | Total Meas |

|------------------------------------|----------|------|---------------|----------|------------|

| Rise Time (f1)                     | 23.33 ps |      | 23.33 ps      | 23.33 ps | 32         |

| Fall Time (f1)                     | 24.67 ps |      | 24.00 ps      | 25.33 ps | 32         |

| Differential Eye<br>Amplitude (f1) | 860 mV   |      | 858 mV        | 860 mV   | 32         |

| Eye S/N (f1)                       | 15.35    |      | 15.28         | 15.50    | 32         |

| Vertical                           | Scale    |      | 100 mV / div  |          |            |

| Horizontal                         | Scale    | ;    | 30.0 ps / div |          |            |

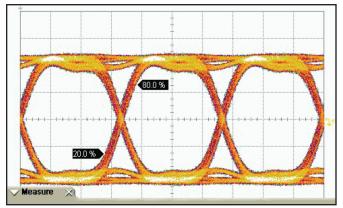

### Output Eye Diagram

|                                    | Current  |              | Minimum       | Maximum  | Total Meas |

|------------------------------------|----------|--------------|---------------|----------|------------|

| Rise Time (f1)                     | 23.33 ps |              | 22.67 ps      | 23.33 ps | 30         |

| Fall Time (f1)                     | 24.67 ps |              | 24.67 ps      | 26.00 ps | 30         |

| Differential Eye<br>Amplitude (f1) | 862 mV   |              | 861 mV        | 862 mV   | 30         |

| Eye S/N (f1)                       | 15.27    |              | 15.19         | 15.35    | 30         |

| Vertical Scale 1                   |          | 100 mV / div |               |          |            |

| Horizontal                         | Scale    |              | 30.0 ps / div |          |            |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

For price, delivery, and to place orders: Analog Devices, Inc., One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 Phone: 781-329-4700 • Order online at www.analog.com Application Support: Phone: 1-800-ANALOG-D

6 - 4

#### Test Conditions Eye diagram data presented on an Infinium DCA 86100A

Rate = 10 Gb/s

**Test Conditions**

DCA 86100A Rate = 10 Gb/s

Eye diagram data presented on an Infinium

Pseudo Random Code = 2<sup>23</sup> -1 Vin = 500 mVpp differential, VC1 = 3V

Pseudo Random Code = 2<sup>23</sup> -1

Vin = 100 mVpp differential, VC1 = 3V

### 12.5 Gbps LIMITING AMPLIFIER

#### Input Signal

Input and output signal for 10 Gbps, PRBS 2<sup>23</sup> -1, 3.5mV p-p differential, VC1 = 3V.

### Absolute Maximum Ratings

| Supply Voltage                                                       | 5.6V          |

|----------------------------------------------------------------------|---------------|

| Input Signals                                                        | 4V to 5.5V    |

| RF Input Power                                                       | 10 dBm        |

| Junction Temperature                                                 | 125 °C        |

| Continuous Pdiss (T = 85°C)<br>(Derate 24 mW/°C above 85°C)          | 0.95 Watts    |

| Thermal Resistance (R <sub>th</sub> )<br>(junction to ground paddle) | 42 °C/W       |

| Storage Temperature                                                  | -65 to 150 °C |

| Operating Temperature                                                | -40 to +85 °C |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

6

LIMITING AMPLIFIERS - SMT

Output Signal

v03.0111

### 12.5 Gbps LIMITING AMPLIFIER

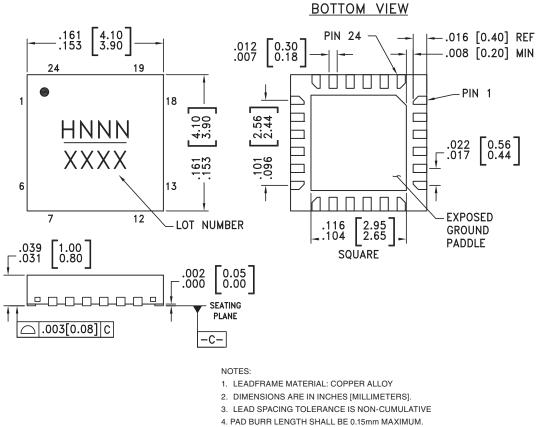

### **Outline Drawing**

v03.0111

- PAD BURB HEIGHT SHALL BE 0.05mm MAXIMUM.

- 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm.

- 6. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

- 7. REFER TO HMC APPLICATION NOTE FOR SUGGESTED PCB LAND PATTERN.

#### Package Information

| Part Number | Package Body Material                              | Lead Finish   | MSL Rating          | Package Marking <sup>[3]</sup> |

|-------------|----------------------------------------------------|---------------|---------------------|--------------------------------|

| HMC750LP4   | Low Stress Injection Molded Plastic                | Sn/Pb Solder  | MSL1 <sup>[1]</sup> | H750<br>XXXX                   |

| HMC750LP4E  | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1 <sup>[2]</sup> | <u>H750</u><br>XXXX            |

[1] Max peak reflow temperature of 235 °C

[2] Max peak reflow temperature of 260 °C

[3] 4-Digit lot number XXXX

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0111

### 12.5 Gbps LIMITING AMPLIFIER

### **Pin Descriptions**

| Pin Number                     | Function   | Description                                                                                              | Interface Schematic      |

|--------------------------------|------------|----------------------------------------------------------------------------------------------------------|--------------------------|

| 1, 18, 19,<br>22 - 24          | Vcc        | Positive supply.                                                                                         |                          |

| 2, 5, 14, 17,<br>Ground Paddle | GND        | Signal and supply ground. Package base must be connected to DC ground.                                   |                          |

| 3, 4                           | INP, INN   | Data inputs                                                                                              |                          |

| 6, 7,<br>9 - 13                | N/C        | No connection. These pins are not connected internally,<br>but should be connected to ground externally. |                          |

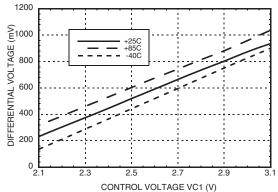

| 8                              | VC1        | Gain, output level control.                                                                              | VC1<br>3150<br>750       |

| 15, 16                         | OUTN, OUTP | Data outputs                                                                                             |                          |

| 20, 21                         | CN, CP     | Filter capacitor for offset correction.<br>Connect 100nF capacitor between CP and CN.                    | 12Ω<br>CPO<br>CNO<br>12Ω |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### HMC750LP4 / 750LP4E

### 12.5 Gbps LIMITING AMPLIFIER

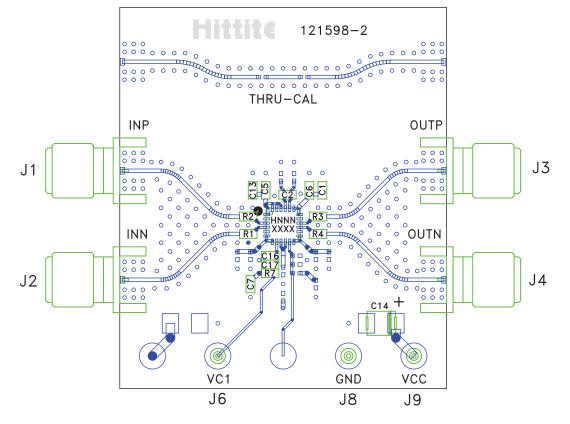

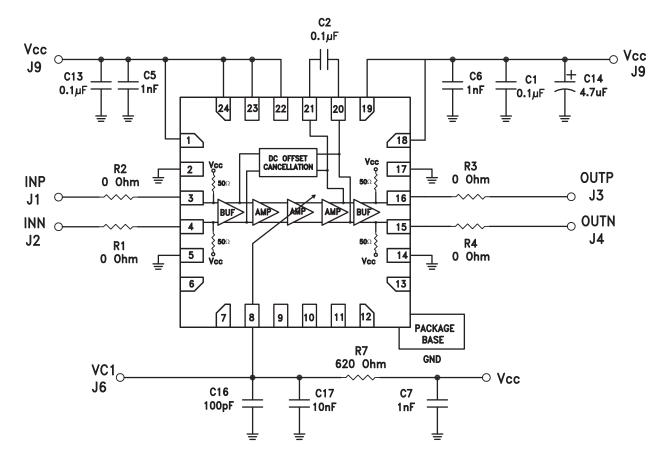

### **Evaluation PCB**

#### List of Materials for Evaluation PCB 121600 [1]

| Item                                                                    | Description                     |  |

|-------------------------------------------------------------------------|---------------------------------|--|

| J1 - J4                                                                 | PCB Mount SMA Connector         |  |

| J6, J8, J9                                                              | DC Pin                          |  |

| C1, C2, C13                                                             | 0.1 µF Capacitor, 0402 Pkg.     |  |

| C5 - C7                                                                 | 1 nF Capacitor, 0402 Pkg.       |  |

| C14                                                                     | 4.7 µF Capacitor, 0402 Pkg.     |  |

| C16                                                                     | 100 pF Capacitor, 0402 Pkg.     |  |

| C17                                                                     | 10 nF Capacitor, 0402 Pkg.      |  |

| R1 -R4                                                                  | 0 Ohm Resistor, 0402 Pkg.       |  |

| R7                                                                      | 620 Ohm Resistor, 0402 Pkg.     |  |

| U1                                                                      | HMC750LP4(E) Limiting Amplifier |  |

| PCB [2]                                                                 | 121598 Evaluation PCB           |  |

| (4) Defense as this work and a surfacing a second state surfluction DOD |                                 |  |

Reference this number when ordering complete evaluation PCB

Circuit Board Material: Arlon 25FR

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

v03.0111

### 12.5 Gbps LIMITING AMPLIFIER

### **Application Circuit**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### HMC750LP4 / 750LP4E

**12.5 Gbps LIMITING AMPLIFIER**

# ROHS V

### **Application Information**

#### Setting the output swing using external resistor Rc

The HMC750LP4E features output swing level adjustment by using VC1 pin. Output swing can be adjusted to the desired level by applying a DC voltage to VC1 pin. Differential output swing vs. control voltage relationship is given in the plot below.

In order to adjust the DC voltage on VC1 pin a resistor, Rc (R7 in application circuit), should be connected between VC1 pin and VCC as shown in the figure below.

The value of the resistor can be chosen using the following equation as a function of VC1. VC1 DC voltage value can be chosen by using the plot given above.

$$Rc = \frac{390(Vcc - VC1)}{Vc1 - 1.73}$$

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.