# 1 GSPS Quadrature Digital Upconverter with 14-Bit DAC

# EVAL-AD9957

### FEATURES

1 GSPS internal clock speed (up to 400 MHz analog output) Integrated 1 GSPS 14-bit DAC 250 MHz I/Q data throughput rate Phase noise ≤ -125 dBc/Hz (400 MHz carrier @ 1 kHz offset) Excellent dynamic performance >80 dB narrow-band SFDR 8 programmable profiles for shift keying Sin(x)/(x) correction (inverse sinc filter) **Reference clock multiplier** Internal oscillator for a single crystal operation Software and hardware controlled power-down Integrated RAM Phase modulation capability **Multichip synchronization Easy interface to Blackfin SPORT** Interpolation factors from 4× to 252× Interpolation DAC mode Gain control DAC Internal divider allows references up to 2 GHz 1.8 V and 3.3 V power supplies 100-lead TQFP\_EP package

# **GENERAL DESCRIPTION**

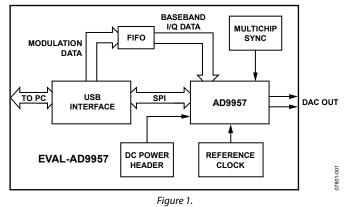

This data sheet serves as a guide to setup and use the AD9957 evaluation board. The AD9957 is a 1 GSPS quadrature digital upconverter with a 14-bit DAC.

The evaluation board software provides a graphical user interface for easy communication with the device along with many user-friendly features such as the mouse-over effect, which clarifies elements by hovering the mouse over the element.

Use this data sheet in conjunction with the AD9957 data sheet, available from Analog Devices, Inc., at www.analog.com.

### PACKAGE CONTENTS

AD9957 evaluation board AD9957/PCB installation software USB cable

# FUNCTIONAL BLOCK DIAGRAM

Rev. 0

Evaluation boards are only intended for device evaluation and not for production purposes. Evaluation boards are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. No license is granted by implication or otherwise under any patents or other intellectual property by application or use of evaluation boards. Information furnished by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Analog Devices reserves the right to change devices or specifications at any time without notice. Trademarks and registered trademarks are the property of their respective owners. Evaluation boards are not authorized to be used in life support devices or systems.

# **TABLE OF CONTENTS**

| Features 1                                     |

|------------------------------------------------|

| General Description                            |

| Package Contents 1                             |

| Functional Block Diagram 1                     |

| Revision History 2                             |

| Evaluation Board Hardware                      |

| Requirements                                   |

| Setting up the Evaluation Board                |

| Evaluation Board Software                      |

| Installing the Software 5                      |

| Installing the Driver                          |

| Launching the Program 5                        |

| Feature Windows7                               |

| Control7                                       |

| Profiles10                                     |

| Profiles Windows10                             |

| View Windows14                                 |

| QDUC RAM Control14                             |

| FIFO Control15                                 |

| MultiChip Sync Control15                       |

| GPIO                                           |

| Debug Window16                                 |

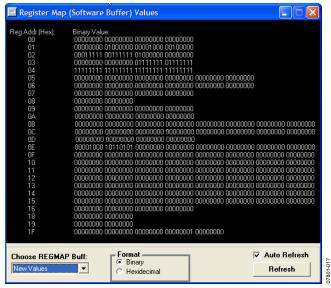

| Register Map (Software Buffer) Values Window17 |

| DUT I/O 17                                     |

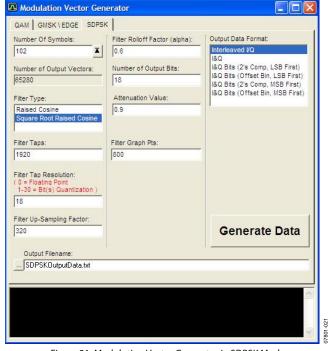

| Modulation Vector Generator18                  |

| QAM                                            |

| GMSK/EDGE19                                    |

| SDPSK                                               | 19 |

|-----------------------------------------------------|----|

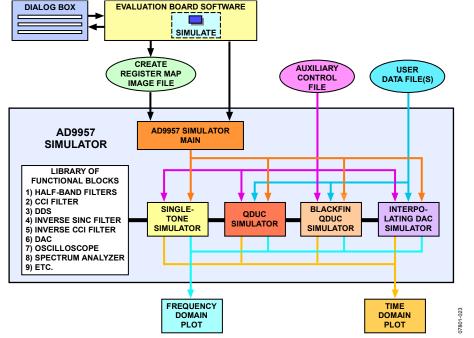

| Simulator                                           | 20 |

| Simulator Tool                                      | 21 |

| Overview                                            | 21 |

| Simulator Activation                                | 21 |

| Simulator Description                               | 21 |

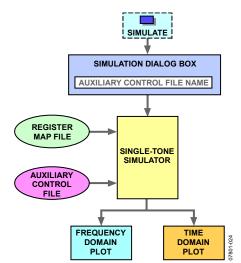

| Single-Tone Mode Simulation                         | 23 |

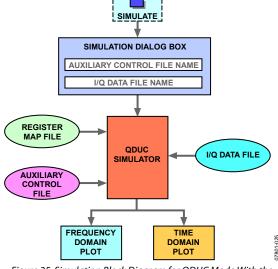

| QDUC Parallel Data Mode Simulation                  | 24 |

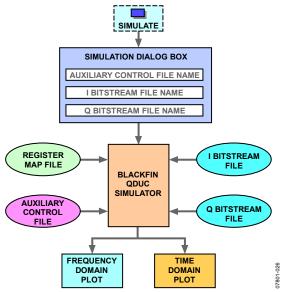

| QDUC BlackFin (Serial Data) Mode Simulation         | 24 |

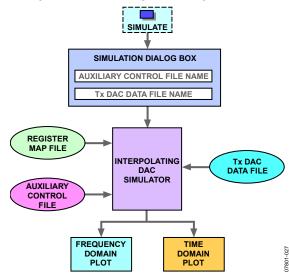

| Interpolating DAC Mode Simulation                   | 25 |

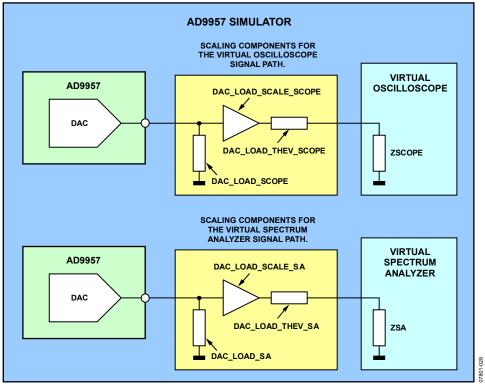

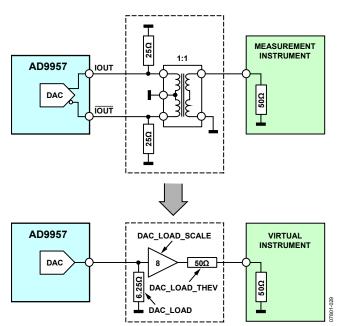

| Virtual Oscilloscope and Spectrum Analyzer          | 25 |

| User Data File(s)                                   | 25 |

| Auxiliary Control File                              | 26 |

| Keywords                                            | 27 |

| Debug                                               | 27 |

| Showclip                                            | 27 |

| Samples                                             | 27 |

| DDSCORE                                             | 27 |

| RSET                                                | 27 |

| DACXFR                                              | 27 |

| FFTWINDOWTYPE                                       | 27 |

| Virtual Oscillope and Spectrum Analyzer Instruments |    |

| Keywords                                            |    |

| DAC Output Signal Keywords                          |    |

| Ordering Information                                |    |

| Ordering Guide                                      |    |

| ESD Caution                                         | 32 |

# **REVISION HISTORY**

7/09—Revision 0: Initial Version

# **EVALUATION BOARD HARDWARE**

# REQUIREMENTS

To use the evaluation board and run the software, the requirements listed in Table 1 must be met.

| ltem             | Requirement                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| Operating System | Windows <sup>®</sup> 98/ME/2000/XP                                                                                           |

| Processor        | Pentium <sup>®</sup> I or better                                                                                             |

| Memory           | 128 MB or better                                                                                                             |

| Ports            | One USB port                                                                                                                 |

| Clocking         | Signal generator capable of generating<br>sinusoidal waves of at least 0 dBm power,<br>up to at least 10 MHz                 |

| Power Supplies   | Capability to generate at least two<br>independent dc voltages (1.8 V/3.3 V)                                                 |

| Measurement      | Appropriate measurement device, such as a<br>spectrum analyzer or a high bandwidth<br>oscilloscope                           |

| Cables           | USB 1.1/2.0 cable, and SMA-to-x cables (x = SMA or BNC, depending on the connector of the device interfacing with the board) |

# SETTING UP THE EVALUATION BOARD

#### **DC** Power Supply

The AD9957 evaluation board has two power supply connectors (four pins each): TB1 and TB2. TB1 powers the USB interface circuitry, the digital I/O interface, and the digital core. TB2 powers the DAC and the clock input circuitry.

Table 2 shows the necessary connections and the appropriate biasing voltage for TB1 and TB2.

| 8 8       |         |         |             |  |

|-----------|---------|---------|-------------|--|

| Connector | Pin No. | Label   | Voltage (V) |  |

| TB1       | 1       | VCC     | 3.3         |  |

| TB1       | 2       | GND     | 0           |  |

| TB1       | 3       | DVDD_IO | 3.3         |  |

| TB1       | 4       | DVDD    | 1.8         |  |

| TB2       | 1, 3    | GND     | 0           |  |

| TB2       | 2       | DAC_VDD | 3.3         |  |

| TB2       | 4       | CLK_VDD | 1.8         |  |

#### Table 2. Connections and Biasing Voltage

# **Device Clock Oscillator Options**

The AD9957 architecture provides the user with three options when providing an input signal to the part. The first option allows the user to provide a high frequency input signal, connected to J1. The second option allows the user to connect the part using a lower input reference frequency, enabling the clock multiplier, connected through J1. The third option allows the user to connect a crystal resonator on the backside of the board.

Note that the AD9957 does not populate the PLL loop filter components. Therefore, to use the internal PLL of the AD9957, the user must solder down these components, or else the PLL is not stable. The AD9957 data sheet has helpful formulas to calculate the appropriate values.

To enable the crystal mode, switch the jumper, W7, to the XTAL mode. Remove C51 and C52. Place 0  $\Omega$  resistors at R4 and R11 on the backside of the board. The crystal oscillates at 25 MHz.

Refer to the AD9957 data sheet for details on the maximum input speeds and input sensitivities of these two inputs.

#### **Device Communication Requirements**

Two interface standards are available on the evaluation board:

- USB 1.1/2.0

- A header row (U5 and U9), which places the part under the control of an external controller (such as a microprocessor, FPGA, or DSP).

Analog Devices provides a GUI for the PC but does not provide control software for external controllers.

Use the jumper settings listed in Table 3 to enable different modes of communication.

**Table 3. Jumper Settings for Communication Modes**

| Mode                 | Settings                                                                                                    |

|----------------------|-------------------------------------------------------------------------------------------------------------|

| PC Control, USB Port | Set Jumper W1 and Jumper W2 to<br>enable.<br>Set Jumper W4 to EN.<br>Place a jumper on W5, W6, and W3.      |

| External Control     | Set Jumper W1 and Jumper W2 to<br>disable.<br>Set Jumper W4 to DIS.<br>Remove the jumper on W5, W6, and W3. |

Jumper W1, Jumper W2, and Jumper W4 enable the USB circuitry to control the AD9957. Jumper W3 controls the EEPROM and is used in starting up the USB circuitry. Jumper W5 and Jumper W6 control the signals SDO and SDIO to and from the AD9957.

Figure 2. Evaluation Board Layout

#### Manual I/O Control Headers

Header connectors (U5, U6, and U9) provide the communication interface for the AD9957 when the part is under the command of an external controller (see Table 3 for the correct jumper settings).

#### **Multidevice Synchronous Control**

J2, J5, J6, and J7 connections are used to set up the AD9957 for multidevice synchronous operation.

#### DAC Output

The J4 connection is the filtered output of the DAC and J3 represents the unfiltered (default) DAC output. To enable the filtered path, R19 on the PCB must be installed.

#### **Clock Mode Select**

Clock mode select controls whether the reference clock source is a 20 MHz to 30 MHz crystal or an external signal generator. A 25 MHz crystal is provided on underside of the AD9957 evaluation board.

#### **Reference Clock Input**

The reference clock input is the input for the external reference clock signal.

#### **Power Supply Connections**

These two connectors, TB1 and TB2, provide all the necessary supply voltages needed by the AD9957 and the evaluation board (see Table 2).

### USB Port

When the part is under PC control (default mode), the evaluation board communicates with the AD9957 via the USB port.

# **EVALUATION BOARD SOFTWARE**

# **INSTALLING THE SOFTWARE**

Use the following steps to install the AD9957 evaluation software:

- 1. Log into your PC system with administrative privileges.

- 2. Uninstall any previous versions of the AD9957 evaluation software from your PC system.

- Insert the AD9957 evaluation software CD. Do not connect the AD9957 evaluation board to the computer until the AD9957 evaluation software has been installed.

- 4. Open the **Readme.txt** file located in the **Software** folder before proceeding with the installation of the AD9957 evaluation software.

- 5. Run the **setup.exe** file located in the **Software** folder and follow the on-screen installation instructions.

# **INSTALLING THE DRIVER**

Once the software has been installed onto your PC, interface the AD9957 evaluation software to the AD9957 evaluation board via the USB port (see Figure 2).

In order for the evaluation board and software to communicate properly, drivers must be loaded onto your PC system. Use the instructions in the following sections to install these drivers on your PC system.

#### Windows 98/ME/2000 Users

- 1. Power up the AD9957 evaluation board (see Table 2).

- 2. Connect the evaluation board to the computer using a USB cable via the USB port; the VBUS LED (CR1 on the AD9957 evaluation board) illuminates.

- 3. When the USB cable is connected, the **Found New Hardware** window appears.

- 4. Click **Finish** in the **Found New Hardware Wizard** when the install is complete.

After the window has disappeared, the USB status LED (CR2 on the AD9957 evaluation board) flashes, which indicates that the evaluation board is connected properly.

#### Windows XP Users

- 1. Power up the AD9957 evaluation board (see Table 2).

- 2. Connect the evaluation board to the computer using a USB cable via the USB port. Then, the VBUS LED (CR1 on the AD9957 evaluation board) illuminates.

- When the USB cable is connected, the Found New Hardware Wizard appears. Click Next to continue. The AD9957 Firmware Loader appears.

- 4. Click **Continue Anyway** when the **Hardware Installation** warning window appears.

- 5. Click **Finish** in the **Found New Hardware Wizard** when the install is complete.

- 6. Click **Next** when the next **Found New Hardware Wizard** appears.

- 7. Click **Continue Anyway** when the **Hardware Installation** warning window appears.

- 8. Click **Finish** in the **Found New Hardware Wizard** when the install is complete.

Once this screen has disappeared, the USB status LED (CR2 on AD9957 evaluation board) should be flashing, indicating that the evaluation board is properly connected. If the LED does not flash, verify that all power and USB connections are properly connected.

#### Installing the Simulator

- 1. Run **Setup.exe** in the software MLRT73 installer directory on the CD.

- 2. Follow the on screen instructions for installing the simulator.

- 3. The simulator can be accessed from the AD9957 evaluation board software. See the Simulator Activation section for further information.

# LAUNCHING THE PROGRAM

Follow these steps to load the AD9957 evaluation software:

- 1. Before starting the software, make sure that the AD9957 evaluation board is powered up, connected to the computer, and that the USB status LED is flashing.

- 2. Click the **Start** button.

- Select Programs > AD9957 Eval Software folder, > AD9957 Eval Software to load the software.

A status message appears. See the Status Messages upon Loading Software section for more information.

### Status Messages upon Loading Software

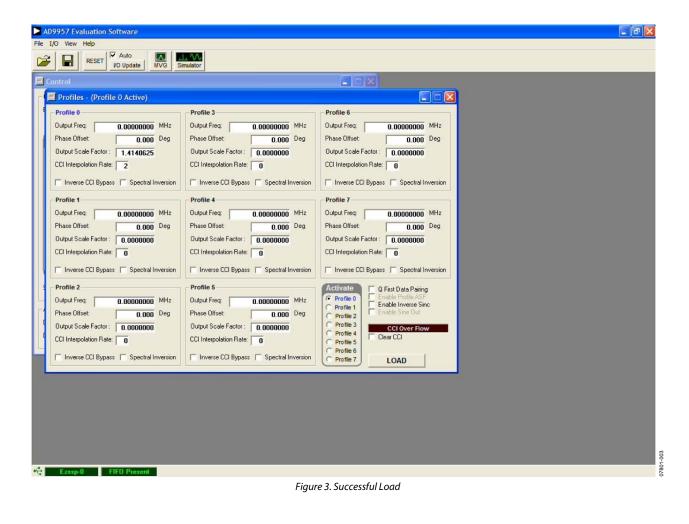

Once the AD9957 evaluation software has been loaded, a green splash screen appears. The status box within the splash screen gives the status of the AD9957 evaluation software. Green writing in the status box indicates that the software has loaded (see Figure 3). The status box disappears following a successful load.

A splash screen with red writing in the status box indicates that the software did not load and that an error occurred. Click within this box to create a cursor. Scrolling up through the status box with the cursor indicates why the software did not load correctly. Most status message errors are resolved by checking jumper settings, making sure that the evaluation board is powered up correctly, and inspecting the USB port and cable connections. In addition, check that the clock input source is connected and properly configured.

# **FEATURE WINDOWS**

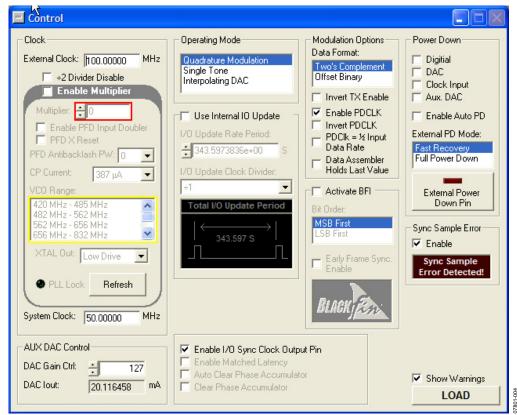

*Figure 4. Chip Level Control Window*

# CONTROL

The **Control** window provides control of the clock input, clock multiplier, DAC gain settings, internal I/O update, and power down functions of the AD9957. The following sections describe the chip level control window portions as they appear in Figure 4.

#### Load

The **LOAD** button is used to send data to the AD9957 device. All **LOAD** buttons found in the evaluation software have the same functionality.

When new data is detected, **LOAD** flashes orange, indicating that you need to click **LOAD** to send the updates to the serial I/O buffer where they are stored until an I/O update is issued. The I/O update sends the contents of the serial I/O buffer to active registers.

I/O updates can be sent manually (Manual I/O Update) or automatically (Auto I/O Update) (see Figure 3). By default, the AD9957 evaluation software is set to Auto I/O Update. When LOAD is clicked, an I/O update signal is automatically sent to the device. If synchronization across channels is desired, use the Manual I/O Update button. To send an I/O update, uncheck the Auto I/O Update box at the top of the screen and press the I/O Update button.

The **Show Warnings** check box in Figure 4 can be selected to show when you have entered data that exceeds the specifications of the AD9957.

# Clock

The **Clock** section allows you to configure the reference clock path in the AD9957.

**External Clock** inputs the operating frequency of the external reference clock or crystal. The maximum reference clock frequency of the AD9957 is 1 GHz. A red outline indicates that the value entered is out of range.

The **÷2 Divider Disable** checkbox disables the input divider for the clock path. The maximum frequency of this divider is 2 GHz.

The **Enable Multiplier** section selects the PLL multiplication factor (12× to 127×) which is used to scale the input frequency. The default setting of this box is disabled, indicating that the reference clock multiplier circuitry is bypassed and the reference clock/crystal input is piped directly to the DDS core.

**CP Current** selects the charge pump current output of the PLL in the reference clock multiplier circuitry. Selecting a higher current output results in the loop locking faster, but there is a trade-off. Increasing this current output also increases phase noise.

The **VCO Range** menu allows you to select the range of operation for the VCO on the AD9957. The AD9957 evaluation software automatically determines which range the AD9957 should operate in. However, if you to run a given frequency in a band other than the one selected by the software, a warning box prompts you to confirm this. Note that using a VCO frequency outside of its specified range may result in undesired operation, including nonfunctionality. See the AD9957 data sheet for more information regarding the different VCO bands.

The **XTAL Out** drop-down menu selects the output drive strength of the XTAL reference output. There are three drive strengths: low, middle, and high.

**PLL Lock** indicates when the PLL is in a valid lock state. If the PLL loses lock, the indicator light display lights up or turns green.

**System Clock** displays the operating frequency the DDS core (system). The value shown here is derived from the values entered in the **External Clock** and **Multiplier** boxes.

Refer to the AD9957 data sheet for more information regarding clock modes and operation.

# AUX DAC Control

The **DAC Gain Ctrl** drop-down menu controls the auxiliary DAC setting to select the full-scale output current of the DAC. See the AD9957 data sheet for more information about DAC gain setting.

The **DAC Iout** box displays the full-scale output current of the DAC. This number is based on a DAC\_RSET resistor value of 10 k $\Omega$ .

### **Operating Mode**

The **Operating Mode** selector allows you to select between the three operating modes of the AD9957. **Quadrature Modulation** is the default setting. This puts the AD9957 into quadrature digital up-converter (QDUC) mode. QDUC mode takes digital baseband data and upconverts it to a specified IF output. Single tone allows you to get a single tone output from the AD9957. Single tone mode allows you to select a single output frequency. **Interpolating DAC** keeps baseband data at baseband but can change the sample rate of the data. See the AD9957 data sheet for more information about the different modes of operation.

#### Internal I/O Update

The **Use Internal IO Update** check box sets the I/O update pin to an output. This output generates an active high pulse when the internal I/O update occurs. The rate of the internal I/O update can be programmed through the serial port. See the AD9957 data sheet for more information.

#### **Modulation Options**

The **Data Format** selection allows you to select the formatting method of the input data either from **Two's Complement** or **Offset Binary**.

The **Invert TX Enable** check box allows you to invert the polarity of the TxENABLE signal.

The **Enable PDCLK** check box allows you to control the PDCLK functionality.

The **Invert PDCLK** box allows you to invert the polarity of the PDCLK signal.

The **PDClk = \frac{1}{2} Input Data Rate** box allows you to set the PDCLK signal to  $\frac{1}{2}$  of the input data rate.

The **Data Assembler Holds Last Value** box allows you to choose between the data assembler, which outputs all zeros or the last value received when TxENABLE is low.

#### Activate BFI

Using the Active BFI control allows you to make the AD9957 data compatible with an Analog Devices, Inc., Blackfin<sup>®</sup> DSP.

The **Bit Order** section allows you to specify the input format of LSB or MSB first.

The **Early Frame Sync Enable** box changes the BFI compatibility to late frame or early frame.

#### Power Down

The **Digital**, **DAC**, **Clock Input**, and **Aux**. **DAC** power-down controls allow you to power down each of the specific circuit blocks individually.

Setting the **Enable Auto PD** box enables the condition when the TxENABLE pin is Logic 0, the baseband signal processing chain is flushed of residual data, and the clocks are automatically stopped. Clocks restart when the TxENABLE pin is a Logic 1. The enable auto PD bit does nothing when it is cleared.

The **External PD Mode** section allows you to control which power-down mode is used in conjunction with the external power-down pin. The **Fast Recovery** mode sets the AD9957 into a power-down state that keeps clocks running and bias circuits active but does not allow the part to output data. This mode uses significantly more power than **Full Power Down** mode. **Full Power Down** mode stops clocks and powers down bias circuits. It takes significantly longer to power back up from power-down state.

The **External Power Down Pin** button allows you to control the external power-down pin without having to alter the evaluation board. See the AD9957 data sheet for more information about full power-down conditions.

#### Sync Sample Error

The **Sync Sample Error** section allows you to enable/disable the sync sample error detection using the bit provided. If a sync error is detected, the external flag is set.

#### **Other Controls**

The Enable I/O Sync Clock Output Pin box allows you to enable/disable the output driver for the I/O sync clock output.

The **Enable Matched Latency** box allows you to align the application of the frequency tuning word, phase offset word, and amplitude scale factor at the same time. If this bit is cleared, then those words are applied at different times.

The **Auto Clear Phase Accumulator** box sets the DDS phase accumulator to a reset state when the I/O\_UPDATE pin is set high or when a profile changes.

The **Clear Phase Accumulator** box holds the DDS phase accumulator in a reset state as long as the clear phase accumulator bit is set.

# PROFILES

| 🗏 Profiles - (Profile 0 Active)                                                                                                          |                                           |                                                          |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------|--|--|--|

| Profile 0                                                                                                                                | Profile 3                                 | Profile 6                                                |  |  |  |

| Output Freq: 0.00000000 MHz                                                                                                              | Output Freq: 0.00000000 MHz               | Output Freq: 0.00000000 MHz                              |  |  |  |

| Phase Offset: 0.000 Deg                                                                                                                  | Phase Offset: 0.000 Deg                   | Phase Offset: 0.000 Deg                                  |  |  |  |

| Output Scale Factor : 1.4140625                                                                                                          | Output Scale Factor : 0.0000000           | Output Scale Factor : 0.0000000                          |  |  |  |

| CCI Interpolation Rate: 2                                                                                                                | CCI Interpolation Rate:                   | CCI Interpolation Rate: 0                                |  |  |  |

| Inverse CCI Bypass      Spectral Inversion     Inverse CCI Bypass      Spectral Inversion     Inverse CCI Bypass      Spectral Inversion |                                           |                                                          |  |  |  |

| Profile 1                                                                                                                                | Profile 4                                 | Profile 7                                                |  |  |  |

| Output Freq: 0.00000000 MHz                                                                                                              | Output Freq: 0.00000000 MHz               | Output Freq: 0.00000000 MHz                              |  |  |  |

| Phase Offset: 0.000 Deg                                                                                                                  | Phase Offset: 0.000 Deg                   | Phase Offset: 0.000 Deg                                  |  |  |  |

| Output Scale Factor : 0.0000000                                                                                                          | Output Scale Factor : 0.0000000           | Output Scale Factor : 0.0000000                          |  |  |  |

| CCI Interpolation Rate: 0                                                                                                                | CCI Interpolation Rate: 0                 | CCI Interpolation Rate:                                  |  |  |  |

| 🗂 Inverse CCI Bypass 📄 Spectral Inversion                                                                                                | 🗖 Inverse CCI Bypass 🔲 Spectral Inversion | 🗖 Inverse CCI Bypass 🔲 Spectral Inversion                |  |  |  |

| Profile 2                                                                                                                                | Profile 5                                 | Activate 🔲 🛛 Q First Data Pairing                        |  |  |  |

| Output Freq: 0.00000000 MHz                                                                                                              | Output Freq: 0.00000000 MHz               | Profile 0     Enable Profile ASF     Enable Inverse Sinc |  |  |  |

| Phase Offset: 0.000 Deg                                                                                                                  | Phase Offset: 0.000 Deg                   | C Profile 1 Enable Sine Out                              |  |  |  |

| Output Scale Factor: 0.0000000                                                                                                           | Output Scale Factor : 0.0000000           | C Profile 3 CCI Over Flow                                |  |  |  |

| CCI Interpolation Rate: 0                                                                                                                | CCI Interpolation Rate: 0                 | C Profile 4 Clear CCI                                    |  |  |  |

| 🖵 Inverse CCI Bypass 🖵 Spectral Inversion                                                                                                | 🔲 Inverse CCI Bypass 🔲 Spectral Inversion | C Profile 6<br>C Profile 7 LOAD                          |  |  |  |

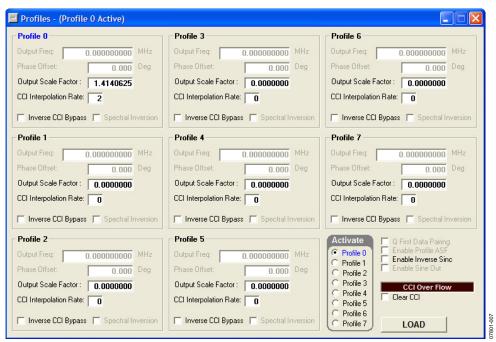

Figure 5. Profiles Control Window for QDUC Modulation Mode

# **PROFILES WINDOWS**

The **Profiles** window allows you to change the different profile settings easily. Figure 5 to Figure 7 show the profile control windows for the three operating modes of the AD9957: QDUC modulation mode, single-tone mode, and interpolating DAC mode.

#### **QDUC Modulation Mode**

**Output Freq** is used to set the frequency generated by the DDS. This is the IF carrier to which the unconverted modulation data is applied.

**Phase Offset** controls the phase of the DDS output. This can be changed from  $0^{\circ}$  to  $360^{\circ}$  with 16-bit resolution.

**Output Scale Factor** digitally controls the amplitude of the carrier from the DDS. This scalar has 8-bits of resolution.

Note that this can be used in conjunction with **DAC Gain Ctrl** (see Figure 4) to increase the flexibility of the output amplitude.

**CCI Interpolation Rate** is the upconversion rate through the cascaded comb integrator (CCI) filters on the AD9957. This can vary from 1 to 63 using a 6-bit control word. Note that this is not the only source of interpolation. See the AD9957 data sheet for more information on interpolation.

**Inverse CCI Bypass** allows you to enable or disable the inverse CCI filter. This filter predistorts the data coming into the CCI section to compensate for a slight attenuation gradient caused by the CCI filter.

**Spectral Inversion** allows you to change the orientation of the modulated signal with respect to the carrier.

| Profile 0               | Profile 3                     | Profile 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Freq: 0.00000000 | MHz Output Freq: 0.00000000 M | Hz Output Freq: 0.000000000 MHz<br>eg Phase Offset: 1 ÷ 0.000 Deg<br>Amplitude SF: 1 • 0.00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8.000000000             | 0.00000000                    | Profile 7           Hz         Output Freq:         0.000000000         MHz           Phase Offset:         1 * 0.000         Deg           Amplitude SF:         1 * 0.000000         Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                         |                               | Hz<br>eg C Profile 0<br>C Profile 1<br>C Profile 1<br>C Profile 2<br>C Profile 2<br>C Profile 3<br>C Profile 3<br>C Profile 4<br>C Profile 5<br>C Profile 5 |

Figure 6. Profile Control Window for Single-Tone Mode

#### Single-Tone Mode

**Output Freq** is used to set the frequency generated by the DDS. In the case of a single tone output, the AD9957 generates a sine/cosine wave at this output frequency.

**Phase Offset** controls the phase of the DDS output. This can be changed from  $0^{\circ}$  to  $360^{\circ}$  with 16-bit resolution.

**Amplitude SF** digitally controls the amplitude of the carrier from the DDS. This scalar has 14-bits of resolution. Note that this can be used in conjunction with **DAC Gain Ctrl** to increase the flexibility of the output amplitude. The **Enable Profile ASF** must be checked to use this control.

*Figure 7. Profile Control Window for Interpolating DAC Mode*

#### Interpolating DAC Mode

**Output Freq** and **Phase Offset** are not available in interpolating DAC mode. There is no DDS output frequency when using this mode. This mode can resample the baseband data to a different data rate, but does not perform any upconversion.

**Output Scale Factor** digitally controls the amplitude of the carrier from the DDS. This scalar has eight bits of resolution. Note that this can be used in conjunction with **DAC Gain Ctrl** to increase the flexibility of the output amplitude.

**CCI Interpolation Rate** is the upconversion rate through the cascaded comb integrator (CCI) filters on the AD9957. This can vary from 1 to 63 using a 6-bit control word.

**Inverse CCI Bypass** allows you to enable or disable the inverse CCI filter. This filter predistorts the data coming into the CCI section to compensate for a slight attenuation gradient caused by the CCI filter.

#### **Data Entry Windows**

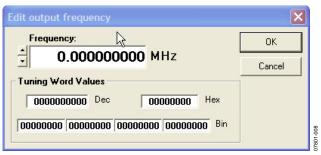

The **Edit output frequency** window (see Figure 8) appears by double-clicking the **Output Freq** data entry form. The **Edit output frequency** window allows you to set individual bits in the frequency tuning word. These can be entered by using dec, hex, or binary format. This window also allows you to enter in a tuning word and see the correct dec, hex, or binary representations for this word. You can scroll through the **Frequency** form to view the different tuning words one bit at a time.

Figure 8. Edit Output Frequency Pop-Up Window

The Edit Phase Offset window (see Figure 9) appears by double-clicking the Phase Offset data entry form. The Edit Phase Offset window allows you to set individual bits in the phase offset tuning word. These can be entered in using dec, hex, or binary format. This window also allows you to enter in a tuning word and see the correct dec, hex, or binary representations for this word. You can scroll through the Phase Offset form to view the different tuning words one bit at a time.

Figure 9. Edit Phase Offset Pop-Up Window

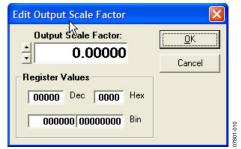

Edit Output Scale Factor window (see Figure 10) appears by double-clicking the Output Scale Factor data entry form. The Edit Output Scale Factor window allows you to set individual bits in the output scale factor tuning word. These can be entered in using dec, hex, or binary. This window also allows you to enter in a tuning word and see the correct dec, hex, or binary representations for this word. You can scroll the Output Scale Factor to view the different tuning words one bit at a time.

Figure 10. Edit Output Scale Factor Pop-Up Window

# Activate

The **Activate** section in the **Profiles** window allows you to select which profile register is active. The active profile register is the one that supplies the frequency tuning and phase offset words along with the amplitude control and modulation control (for QDUC mode) to the DDS core. This section functions the same way for all modes of the AD9957. This window controls three external pins, which may also be driven by an external source.

### Other Controls and CCI Overflow/Clear

The **Q First Data Pairing** check box selects between applying I-data followed by Q-data or Q-data followed by I-data.

The **Enable Profile ASF** check box selects different amplitude scale factors by using the different profiles.

The **Enable Inverse Sinc** check box turns on or off the inverse sinc filter. This filter compensates for the frequency related amplitude roll-off caused by the sinc function nature of the sampling DAC.

The **Enable Sine Out** check box selects the output as cosine or sine.

The **Clear CCI** check box clears the CCI filter from an overflow condition. An overflow condition causes wide band noise at the output of the device. This condition is usually caused by a CCI rate change while Tx\_ENABLE is high. In addition, the overflow can be the result of excessive jitter on the external clock, or the internal PLL is unlocked.

### **VIEW WINDOWS**

To access the **View Windows**, click the **View** tab at the top of the screen in Figure 3 and select from the pull-down menu.

#### **OSK Control**

To use the OSK function of the AD9957, click the Enable Output Shift Keying box (see Figure 11). Set the Amplitude Scale Factor to control the final amplitude of the signal. Check Use External OSK Pin for manual control of the OSK. You can use the OSK Pin button to manually control the on/off of the OSK manually. The OSK Pin button controls a pin that can be driven externally. Check Enable Auto OSK to use the automatic OSK function. Set the Amplitude Ramp Rate and the Amplitude Step Adjust using the boxes provided. The Load ARR @ I/O Update box allows you to reload the ramp rate timer when an I/O update is issued or when there is a profile change.

Figure 11. OSK Control Window

### **QDUC RAM CONTROL**

Click the **Enable RAM** check box to use the RAM (see Figure 12). The RAM has two available internal destinations. See the AD9957 data sheet for a complete description of the RAM and its entire functionality. The **QDUC RAM Destination** box selects which of the two destinations the RAM data is loaded into.

Set the beginning address, final address, and address step rate in the forms provided. Use the **Mode Control** pull-down window to select the playback mode for the RAM. Use **Load RAM** and **Save RAM** to load or save files to and from the PC for use in the RAM. The **Set ISFC Pin High** and **Set ISFC Pin Low** buttons are used to control that external pin. When this pin is high, the RAM sweeps from the beginning RAM address to the end address. When it is low, the RAM sweeps from the end address to the beginning address.

| 📃 QDUC RAM Control                                                                                                                              |                                                                                                            |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Enable RAM C QDUC RAM Destination                                                                                                               |                                                                                                            |  |  |  |  |  |  |

| FRAM Segment 0       Beginning Address:       0       Final Address:       0       Address Step Rate:       0.0000       us       Mode Control: | RAM Segment 1<br>Beginning Address: 0<br>Final Address: 0<br>Address Step Rate: 0.0000 µs<br>Mode Control: |  |  |  |  |  |  |

| File Format: RAW Binary                                                                                                                         | Set ISFC Pin High Load File                                                                                |  |  |  |  |  |  |

| Save RAM<br>File Name:                                                                                                                          |                                                                                                            |  |  |  |  |  |  |

| File Format: RAW Binary                                                                                                                         | Save LOAD                                                                                                  |  |  |  |  |  |  |

Figure 12. QDUC RAM Control Window

# **FIFO CONTROL**

The AD9957 evaluation board comes equipped with a FIFO that allows you to apply baseband modulation data to the AD9957 for evaluation purposes. This should be only raw I/Q data. Note that the FIFO has a speed limit of 100 MHz; consider this when designing modulation data. The FIFO has a refresh time when the memory wraps around that last 2048 PDCLK cycles. The FIFO holds Tx\_ENABLE during the refresh time. This affects use with the FIFO in looping the transmission.

In the LOAD FIFO section (see Figure 13), use the three select buttons, Fill FIFO with Random Data, Load FIFO with (0-262143), and Load Data from a file:, to select the source of the data to be loaded into the FIFO. Use the browse button or the form to enter the location of the file to be used. If using BFI mode, select the Format Data for BFI Mode check box and be aware of the LSB First Mode check box under the BFI Mode Data Format section. Use the LOAD FIFO button to transfer the data from the PC to the FIFO. A pop-up box alerts you whether the transfer was successful. Use the Loop Transmission check box to tell the AD9957 evaluation software to run the modulation data into the AD9957 continuously. Leaving this box unchecked only transmits the data for one burst. Use the Transmit FIFO Data button to initiate the transfer of data to the AD9957.

| FIFO Control                                  |  |

|-----------------------------------------------|--|

|                                               |  |

| ◯ Fill FIFO with Random Data                  |  |

| C Load FIFO with (0-262143)                   |  |

| Contract Load Data from a file:               |  |

|                                               |  |

| Format Data for BFI Mode BFI Mode Data Format |  |

| LOAD FIFO                                     |  |

|                                               |  |

| 🗖 Loop Transmission                           |  |

| Transmit FIFO Data                            |  |

|                                               |  |

Figure 13. FIFO Control Window

### **MULTICHIP SYNC CONTROL**

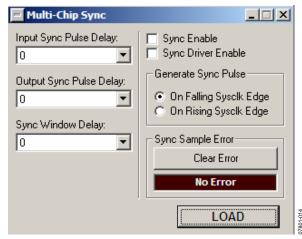

The Multi-Chip Sync window allows you to set up the sync function (see Figure 14). This allows you to sync multiple chips to one master AD9957. Refer to the AD9957 data sheet for a full discussion on multichip sync functions. The Input Sync Pulse Delay pull-down menu sets the input delay of the synchronization receiver in 150 ps steps. The Output Sync Pulse Delay pull-down menu sets the output delay of the synchronization generator in 150 ps steps. The Sync Window Delay pull-down menu sets the state that the internal clock generator assumes when it receives a sync pulse. The Sync Enable check box sets the synchronization clock receiver to active. The Sync Driver Enable check box sets the synchronization clock generator to active. The Generate Sync Pulse control area allows you to select the sync pulse generation corresponding to the rising or falling SYSCLK edge. The Sync Sample Error section displays a flag when there is a sync sample error. Use the Clear Error button to clear a sample error. Refer to the AD9910 data sheet section for synchronizing multiple parts.

Figure 14. Multi-Chip Sync Window

# GPIO

### **Configure GPIO Lines**

The **Input** and **Output** buttons allow you to select whether an individual pin is configured as an input or an output (see Figure 15). The **Data Pins** column lists all 18 of the GPIO pins. The **LOAD** and **READ** buttons allow you to program each pin or read the value of each pin.

### **Read/Write Data Lines**

The **Data Line** column shows the 18 pins available. The **Data** column allows you to set each pin to logic high or logic low.

| Image: Endpoint       D0       0         Internat       Endpoint       D1       0         Internat       Endpoint       D2       0         Internat       Endpoint       D2       0         Internat       Endpoint       D3       0         Internat       Endpoint       D3       0         Internat       Endpoint       D5       0         Internat       Endpoint       D5       0         Internat       Endpoint       D7       0         Internat       Endpoint       D10       0         Internat       Endpoint       D11       0         Internat       Endpoint       D12       0         Internat       Endpoint       D13       0         Internat       Endpoint       D16       0         Internat       Endpoint       D16       0      <                                                                                                                                                                                                                                                                         | Configure GI | -10 Lines |               | - Read\Writ | e Data |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|---------------|-------------|--------|

| Impul       Impul <td< th=""><th>ata Pins</th><th>Input</th><th>Output</th><th>Data Line</th><th>Data</th></td<> | ata Pins     | Input     | Output        | Data Line   | Data   |

| 2         trapul         Output           13         Irapul         Output           15         Irapul         Output           16         Irapul         Output           17         Irapul         Output           16         Irapul         Output           17         Irapul         Output           18         Irapul         Output           19         Irapul         Output           10         Irapul         Output           10         Irapul         Output           11         Irapul         Output           11         Irapul         Output           12         Irapul         Output           13         Irapul         Output           14         Irapul         Output           15         Irapul         Output           16         Irapul         Output           15         Irapul         Output           16         Irapul         Output           17         Irapul         Output           16         Irapul         Output           17         Irapul         Output                                                                                                                                                                                                                                                                        | 0            | Input     | Gutput        | DO          | 0      |

| 3       Imput       Øulput       D3       0         5       Imput       Øulput       D6       0         7       Imput       Øulput       D7       0         6       Imput       Øulput       D7       0         6       Imput       Øulput       D8       0         9       Øulput       D9       0       0         10       Imput       Øulput       D10       0         11       Imput       Øulput       D11       0         12       Imput       Øulput       D13       0         13       Imput       Øulput       D13       0         14       Imput       Øulput       D13       0         13       Imput       Øulput       D13       0         14       Imput       Øulput       D14       0         15       Imput       Øulput       D15       0         16       Imput       Øulput       D16       0         17       Imput       Øulput       D177       0                                                                                                                                                                                                                                                                                                                                                                                                                 | 1            | Input     | Guppor        | D1          | 0      |

| 6         Unput         Quiput         D6         0           7         Unput         Quiput         D7         0           6         Unput         Quiput         D7         0           6         Unput         Quiput         D8         0           5         Unput         Quiput         D8         0           10         Imput         Quiput         D10         0           11         Imput         Quiput         D10         0           12         Imput         Quiput         D11         0           13         Imput         Quiput         D13         0           14         Unput         Quiput         D14         0           15         Unput         Quiput         D15         0           16         Imput         Quiput         D16         0           17         Imput         Quiput         D17         0                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20           | Input     | Gulput        | D2          | 0      |

| 7         Grand         Output           Grand         Grand         Glatput           Grand         Grand         Glatput           Grand         Grand         Glatput           Grand         Graph         Glatput           Grand         Graph         Glatput           Grand         Graph         Glatput           Graph         Graph         Glatput           Graph         Glatput         D10           Graph         Glatput         D11           Graph         Glatput         D12           Graph         Glatput         D13           Graph         Glatput         D14           Graph         Glatput         D14           Graph         Glatput         D15           Graph         Glatput         D15           Graph         Glatput         D16           Glatput         Glatput         D16                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3            | Imput     | Output        | D3          | 0      |

| 6     Immut     Output       8     Immut     Output       9     0       10     Immut       11     Immut       11     Immut       11     Immut       12     Immut       13     Immut       14     Immut       15     Immut       16     Immut       17     Immut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6            | Input     | Gulput        | D6          | 0      |

| B         Imput         Output           10         Imput         Output           11         Imput         Output           11         Imput         Output           12         Imput         Output           13         Imput         Output           14         Imput         Output           15         Imput         Output           16         Imput         Output           17         Imput         Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7            | lingitul  | <b>Culput</b> | D7          | 0      |

| 10         Imput         Output           11         Imput         Output           12         Imput         Output           13         Imput         Output           14         Imput         Output           15         Imput         Output           16         Imput         Output           17         Imput         Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8            | Impiral   | Output:       | D8          | 0      |

| Hypol         Output         D11         0           12         Imput         Output         D12         0           13         Imput         Output         D13         0           14         Imput         Output         D14         0           15         Imput         Output         D13         0           16         Imput         Output         D14         0           17         Imput         Output         D15         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8            | Input     | Output        | D9          | 0      |

| 12         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17         17 <th18< th="">         17         17         17<!--</td--><td>10</td><td>Input</td><td>Gulput,</td><td>D10</td><td>0</td></th18<>                                           | 10           | Input     | Gulput,       | D10         | 0      |

| 13         Import         Official         D13         0           14         Import         Output         D14         0           15         Import         Output         D15         0           16         Import         Output         D16         0           17         Import         Output         D16         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11           | Input     | Gupper        | D11         | 0      |

| 14         Input         Output           15         Input         Output           16         Input         Output           17         Input         Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12           | Input     | Gutput        | D12         | 0      |

| 15         Input         Output         D15         0           16         Iteanut         Output         D16         0           17         Reput         Output         D17         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12           | Input.    | Gulput        | D13         | 0      |

| Ifensit         Otenue         D16         0           17         Input         Output         D17         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14           | Tepput    | Gulput        | D14         | 0      |

| 17 Dinour Din 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15           | ligut.    | <b>Dulpul</b> | D15         | 0      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16           | Incid     | Output        | D16         | 0      |

| 1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17.          | Treat     | Output        | D17         | 0      |