### EV-ADF4159EB1Z/EV-ADF4159EB3Z User Guide UG-383

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### Evaluating the ADF4159 Frequency Synthesizer for Phase-Locked Loops

#### **FEATURES**

Self-contained board, including synthesizer, 100 MHz reference, USB interface, and voltage regulators Accompanying software allows control of synthesizer

Accompanying software allows control of synthesiz functions from a PC (via USB interface) Externally powered by 5.5 V and 15 V supplies

#### **EVALUATION KIT CONTENTS**

EV-ADF4159EB1Z or EV-ADF4159EB3Z evaluation board CD with evaluation software USB cable

#### **REQUIRED ADDITIONAL EQUIPMENT**

VCO (for EV-ADF4159EB3Z) Loop filter components (for EV-ADF4159EB3Z) Soldering equipment Spectrum analyzer Power supplies (5.5 V and 15 V) Windows®-based PC with USB port for evaluation software

#### **REQUIRED DOCUMENTS**

ADF4159 data sheet UG-383 user guide

#### **REQUIRED SOFTWARE**

Analog Devices ADF4158-9 evaluation software, Version 4.x or higher (included on the CD in the evaluation board kit or available for download at www.analog.com)

#### **GENERAL DESCRIPTION**

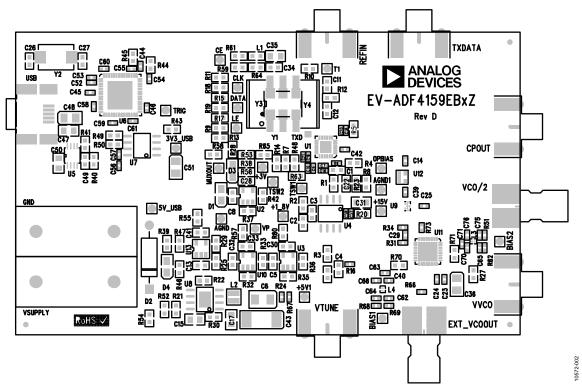

The EV-ADF4159EB1Z/ EV-ADF4159EB3Z evaluates the performance of the ADF4159 frequency synthesizer for phaselocked loops (PLL). A photograph of the evaluation board is shown in Figure 1. The evaluation board involves the ADF4159 synthesizer, a USB connector, SMA connectors, a reference oscillator, and power supply connectors. There are also footprints for active filter components and a voltage controlled oscillator (VCO); if used, these components must be soldered to the board to complete the loop. An on-board temperature compensated crystal oscillator (TCXO) provides the 100 MHz reference frequency, and a USB cable is included to connect the board to a PC USB port.

In addition, the evaluation kit contains Windows-based software to allow easy programming of the synthesizer.

#### **EVALUATION BOARD PHOTOGRAPH**

Figure 1.

### TABLE OF CONTENTS

| Features 1                      | L |

|---------------------------------|---|

| Evaluation Kit Contents 1       | L |

| Required Additional Equipment 1 | L |

| Required Documents 1            | L |

| Required Software 1             | L |

| General Description 1           | L |

| Evaluation Board Photograph1    | L |

| Revision History 2              | 2 |

| Evaluation Board Hardware       | 3 |

| Overview                        | 3 |

| Power Supplies                  | 3 |

| Local Oscillator                | 3 |

| VCO                             | 3 |

### **REVISION HISTORY**

| 7/14—Rev. A to Rev. B                 |

|---------------------------------------|

| Changes to Sample Loop Filter Section |

| 11/13—Rev. 0 to Rev. A                |

| Deleted EV-ADF4159EB2ZUniversal       |

| Changes to Figure 7                   |

| Changes to Figure 89                  |

| Changes to Figure 910                 |

| 8/13—Revision 0: Initial Version      |

| Output Signals                                 | 3 |

|------------------------------------------------|---|

| Loop Filter                                    | 4 |

| VCO Configuration                              | 5 |

| EV-ADF4159EB1Z                                 | 5 |

| EV-ADF4159EB3Z                                 | 5 |

| Evaluation Setup                               | 6 |

| Getting Started                                | 7 |

| Installing the Software                        | 7 |

| Configuring and Setting up the Board           | 7 |

| Using the Software—Main Controls               |   |

| Using the Software—Ramp and Shift-Key Controls |   |

| Evaluation Board Schematics                    |   |

# EVALUATION BOARD HARDWARE

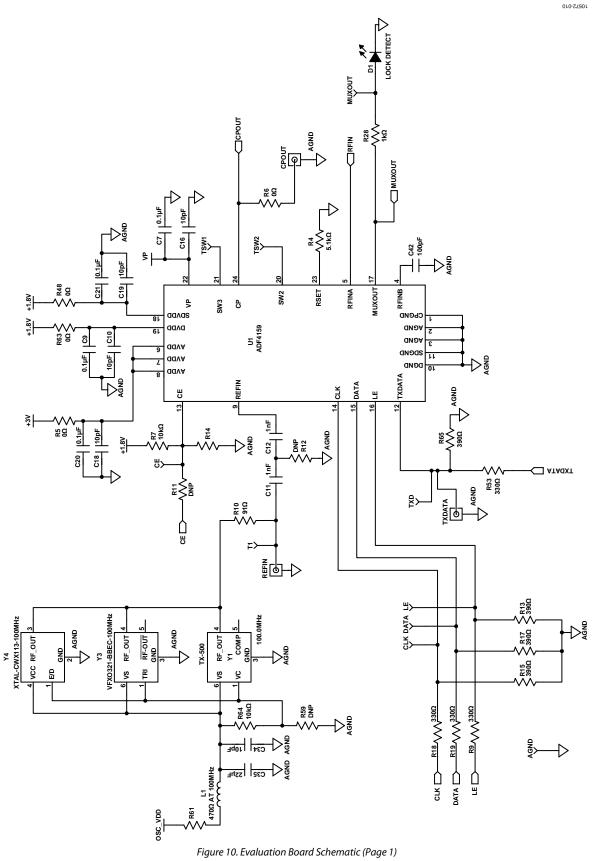

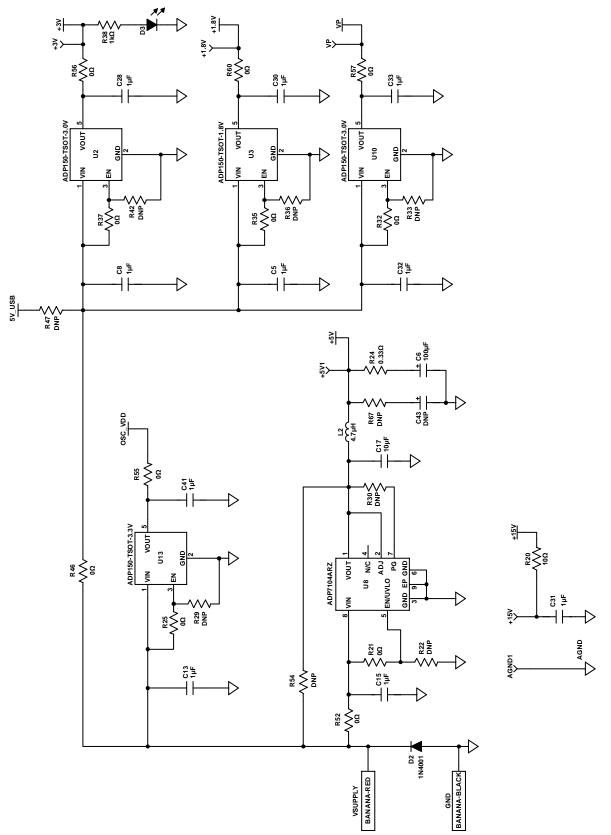

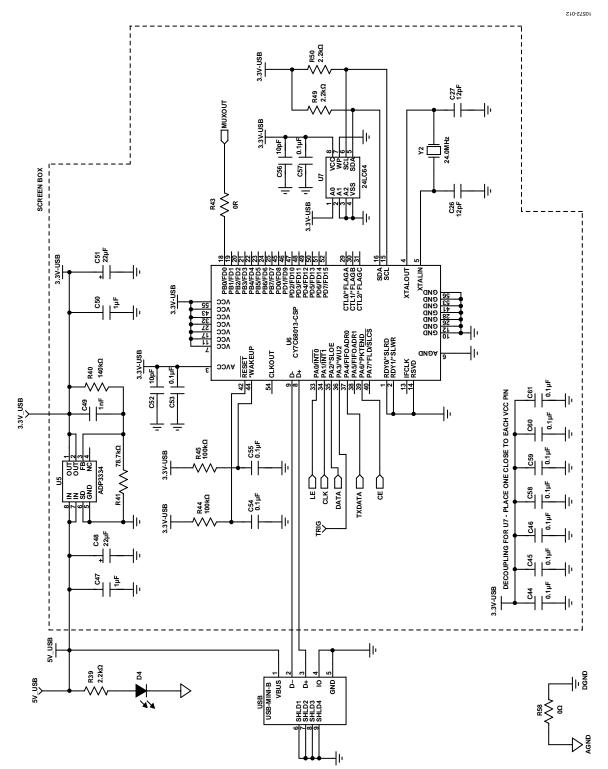

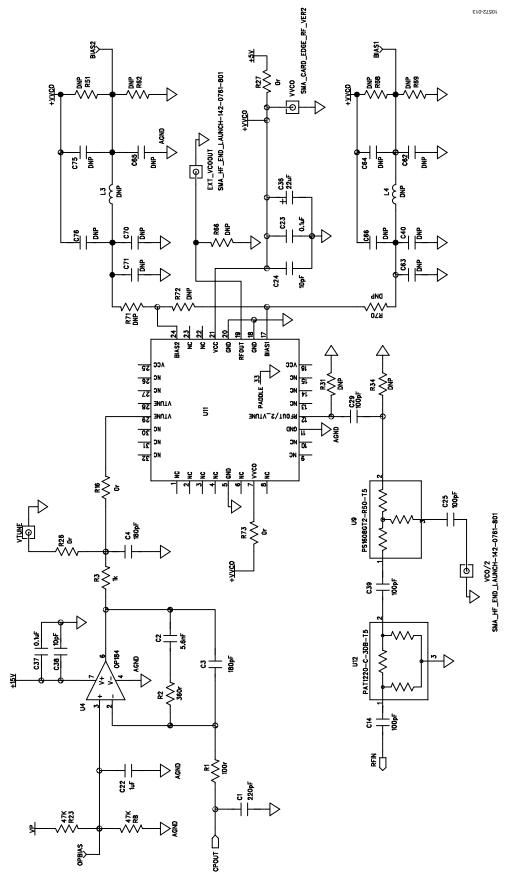

The evaluation board kit includes a cable for connecting the evaluation board to the USB port of a PC. The silkscreen for the evaluation board is show in Figure 2, and the schematics for the evaluation board are shown in Figure 10 to Figure 13.

#### **POWER SUPPLIES**

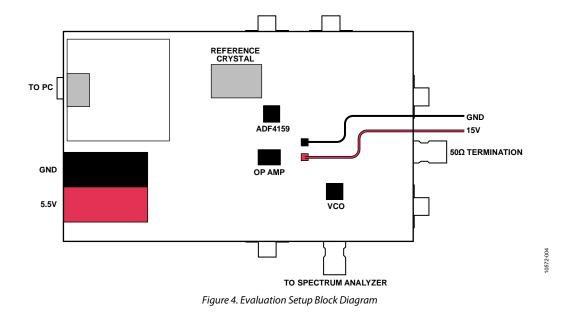

The evaluation board is powered by a 5.5 V power supply connected to the red and black banana connectors. Connect the red connector to a 5.5 V power supply and the black connector to ground.

The op amp is powered by a 15 V power supply.

Optionally, the VCO can be powered independently by connecting a 5 V supply to the VVCO SMA and removing R27. When this option is used, reduce the voltage on the banana connectors to 5 V.

The USB section of the evaluation board (see the area bounded by the gold box in Figure 1) is powered by the USB host.

#### LOCAL OSCILLATOR

The 100 MHz TXCO provides the reference frequency. To ensure that the PFD frequency is also 100 MHz, set the on-chip R-divider to 1.

Alternatively, an external reference can be used by connecting the reference to the REFIN SMA and removing R10 and L1.

#### VCO

The VCO configuration is different for each evaluation board model: EV-ADF4159EB1Z and EV-ADF4159EB3Z. See the VCO Configuration section for more information.

#### **OUTPUT SIGNALS**

With a VCO connected, the evaluation board outputs the VCO output on the EXT\_VCOOUT SMA and the VCO output is divided by 2 on the VCO/2 SMA.

Figure 2. Evaluation Board Silkscreen

### LOOP FILTER

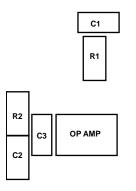

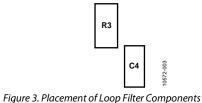

The loop filter schematic is included in Figure 13. The general placement of loop filter components is shown in Figure 3. When using a loop filter, calculate the values of the necessary components and solder them to the board. The ADIsimPLL software, which is available on the CD included in the evaluation board kit or from www.analog.com/adisimpll, provides tools for designing loop filters and calculating component values.

After soldering the loop filter components to the evaluation board, connect a 15 V supply to the op amp power supplies, a 15 V supply to the red 15 V test point, and the ground to the black AGND test point (see Figure 1). See the Sample Loop Filter section for an example configuration.

#### Sample Loop Filter

Use the parameters of the sample loop filter described in this section as a guide for adding a loop filter onto the evaluation board.

Refer to Figure 3 for proper placement of components and to Table 1 for recommended component values.

The sample loop filter is designed for

- VCO kV = 150 MHz/V

- PFD frequency = 100 MHz

- Charge pump current = 2.5 mA

- Loop bandwidth = 282 kHz

- Phase margin = 48.1°

#### Table 1. Sample Loop Filter Components Values

| Value            |  |  |  |  |  |  |

|------------------|--|--|--|--|--|--|

| 100 Ω            |  |  |  |  |  |  |

| 220 pF           |  |  |  |  |  |  |

| 360 Ω            |  |  |  |  |  |  |

| 5.6 nF           |  |  |  |  |  |  |

| 1 kΩ             |  |  |  |  |  |  |

| 180 pF           |  |  |  |  |  |  |

| 180 pF<br>180 pF |  |  |  |  |  |  |

|                  |  |  |  |  |  |  |

### **VCO CONFIGURATION**

### EV-ADF4159EB1Z

The EV-ADF4159EB1Z evaluation board has a MACOM VCO (MAOC-009269) with a range of 11.4 GHz to 12.8 GHz installed. The RFOUT signal is connected to the EXT\_VCOOUT SMA. The RFOUT/2 signal of the VCO is fed back to the ADF4159 PLL; therefore, when the VCO outputs 12 GHz, the ADF4159 is locked at 6 GHz.

For optimum performance, ensure that the components values are as described in Table 2.

#### Table 2. Component Values for EV-ADF4159EB1Z

| Value <sup>1</sup> |

|--------------------|

| 0 Ω                |

| 100 pF             |

| DNP                |

| DNP                |

| DNP                |

|                    |

<sup>1</sup> DNP is do not populate.

Terminate the VCO/2 SMA with 50  $\Omega_{..}$

### EV-ADF4159EB3Z

The EV-ADF4159EB3Z evaluation board does not have a VCO installed. The board is configured for use with an external VCO board. Connect an external VCO to the evaluation board using SMA cables. There are two configuration options:

- The VCO control voltage can be connected to the VTUNE SMA, and the VCO RFOUT signal can be connected to the VCO/2 SMA. This configuration uses the on-board loop filter.

- The CPOUT SMA can be used to connect the ADF4159 charge pump output to an external loop filter. Connect the VCO RFOUT signal to the VCO/2 SMA to feed the signal back into the ADF4159.

For optimum performance, ensure that the component values are as shown in Table 3.

| Component | Value <sup>1</sup> |

|-----------|--------------------|

| R34       | 50 Ω               |

| R31       | DNP                |

| C29       | DNP                |

<sup>1</sup> DNP is do not populate.

# **EVALUATION SETUP**

Figure 5. Evaluation Setup

### **GETTING STARTED**

#### INSTALLING THE SOFTWARE

For the software installation procedure, see the UG-476 user guide. The control software for the EV-ADF4159EB1Z and EV-ADF4159EB3Z is provided on the CD included in the evaluation board kit.

#### **CONFIGURING AND SETTING UP THE BOARD**

- 1. Set up the circuit as shown in Figure 4.

- 2. Run the ADF4158-9 software.

- 3. Select **ADF4159** and **USB board (green)**, and then click **Connect** (see Figure 6).

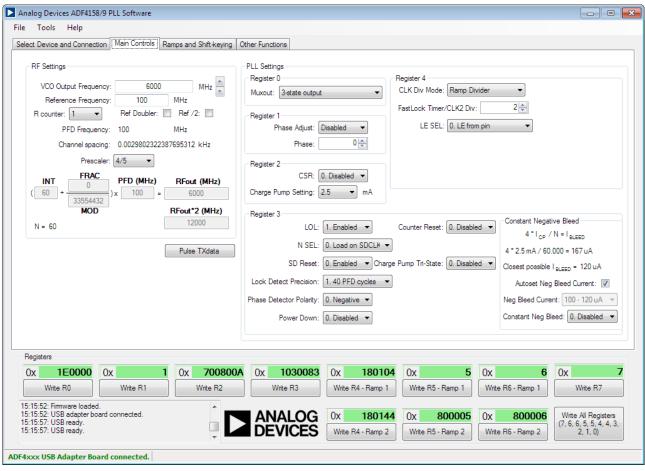

- 4. Click the **Main Controls** tab to view the main controls (see Figure 7). The default values are set to lock a VCO at 12 GHz.

- Click Write All Registers (7, 6, 6, 5, 5, 4, 4, 3, 2, 1, 0) or manually write to each register (Write R7, Write R6 - Ramp 1, Write R6 - Ramp 2, Write R5 - Ramp 1, Write R5 - Ramp 2, Write R4 - Ramp 1, Write R4 - Ramp 2, Write R3, Write R2, Write R1, and Write R0).

- 6. On the spectrum analyzer, confirm that the output signal is locked at 12 GHz.

| е     | Tools      | Help                |                     |       |                            |         |                |        |                   |    |            |      |                 |                           | _                                             |

|-------|------------|---------------------|---------------------|-------|----------------------------|---------|----------------|--------|-------------------|----|------------|------|-----------------|---------------------------|-----------------------------------------------|

| elec  | ct Device  | and Conr            | ection Main Contro  | ls Ra | amps and Shift-keying Othe | r Funct | ons            |        |                   |    |            |      |                 |                           |                                               |

|       |            |                     | e a device to evalu | ate — | ADF4158<br>ADF4159         |         |                | Choose | connection method |    | Connect    | C SD | P board (black) |                           |                                               |

| jiste |            | 0000                | 0x                  | 9     | 0x 7008002                 | 0x      | 20003          | 0x     | 180004            | 0x | 5          | 0x   |                 | <b>6</b> 0x               |                                               |

|       | Write RC   |                     | ,<br>Write R1       |       | Write R2                   |         | Write R3       | -      | ite R4 - Ramp 1   |    | 5 · Ramp 1 | Writ | e R6 - Ramp 1   | Í                         | Write R7                                      |

| 1:12  | 7: USB rea | lapter boai<br>ady. | d connected.        |       |                            | AN      | IALOG<br>VICES | 0x     |                   | 0x | 800005     | -    | 80000           | <ul> <li>Write</li> </ul> | e All Registers (7,<br>i, 5, 4, 4, 3, 2, 1, 0 |

|       | : USB rea  |                     |                     |       |                            |         |                |        | ite R4 - Ramp 2   |    | 5-Ramp 2   |      | e R6 - Ramp 2   |                           |                                               |

Figure 6. Software—Device Selection

#### USING THE SOFTWARE—MAIN CONTROLS

Use the **Main Controls** tab to select the RL and PLL settings. Because the evaluation board is set up to feedback the VCO/2 output to the ADF4159, in the **RF Settings** area, set the **RF VCO Output Frequency** to half the VCO output. Set the **Reference Frequency** to be the same as the applied reference signal. The PFD frequency is calculated from the reference frequency, the R-counter, the reference doubler, and the reference-divide-by-2. Ensure that the value in the **PFD Frequency** box matches the value specified in the loop filter design.

In the **PLL Settings** area, program the **Charge Pump Setting** to the value for which the loop filter was designed. Program the

**Phase Detector Polarity** to negative when using an inverting active loop filter configuration (as is on this evaluation board).

The **Muxout** drop-down box allows you to choose the signal that is connected to the output of the MUXOUT pin.

Clicking **Pulse TXdata** triggers a pulse on the TXDATA pin. This pulse starts low and then stays high for approximately  $4 \mu s$ .

The register values are shown at the bottom of the window. When the background of a register value is green, this indicates that the value has been changed and needs to be written to the part. Clicking the button below each register value writes that value to the part.

Figure 7. Software—Main Controls

0572-006

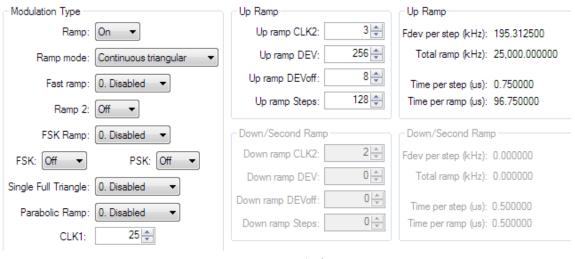

# USING THE SOFTWARE—RAMP AND SHIFT-KEY CONTROLS

In the **Ramps and Shift-keying** tab, you can configure the ramping and shift-keying functionality of the ADF4159.

The ramp type can be selected in the **Ramp mode** drop-down box, and the various ramp parameters can be set in **CLK1** and **Up Ramp** boxes.

#### Example

Figure 8 shows the ramping and shift-keying settings for an example of a continuous triangular ramp of 128 up ramp steps

over 50 MHz with an up ramp time of 96  $\mu$ s. (Up ramp refers to the ramp from the initial frequency to the end frequency, whereas down ramp refers to the ramp/jump from the end frequency back to the initial frequency.) For 50 MHz, the PLL is programmed for a 25 MHz ramp because the evaluation board uses the RFOUT/2 signal. After each parameter is set in the software, it needs to be written to the part.

The other options in this tab allow configuring the various ramps and shift-keying controls of the ADF4159.

Figure 8. Example of Ramp

# EV-ADF4159EB1Z/EV-ADF4159EB3Z User Guide

| nalog Devices ADF4158/9 PLL Software<br>e Tools Help               |                                     |                                           |                                         |

|--------------------------------------------------------------------|-------------------------------------|-------------------------------------------|-----------------------------------------|

| elect Device and Connection   Main Controls   Ramp                 | os and Shift-keying Other Functions |                                           |                                         |

| \                                                                  |                                     |                                           |                                         |

| Ramping and Shift-Keying                                           | Us David                            | U. Barra                                  | Delara                                  |

| Modulation Type<br>Ramp: Off                                       | Up Ramp<br>Up ramp CLK2: 2          | Up Ramp                                   | Delay word:                             |

| Ramp: Off                                                          |                                     | Fdev per step (kHz): 0.000000             | Delay CLK: 0. PFD CLK                   |

| Ramp mode: Continuous sawtooth 💌                                   | Up ramp DEV: 0                      | Total ramp (kHz): 0.000000                |                                         |

| Fast ramp: 0. Disabled 👻                                           | Up ramp DEVoff: 0                   | Time per step (us): 0.020000              | Delay (us): 0.000                       |

| Ramp 2: Off -                                                      | Up ramp Steps: 0 🚔                  | Time per ramp (us): 0.020000              | Delay start: 0. Disabled 👻              |

| FSK Ramp: 0. Disabled 🔻                                            | Down/Second Ramp                    | ⊂ Down/Second Ramp                        | Delay between ramps: 0. Disabled 🔻      |

|                                                                    | Down ramp CLK2: 2                   | Fdev per step (kHz): 0.000000             | Ramp delay fastlock: 0. Disabled 💌      |

| FSK: Off   PSK: Off                                                | Down ramp DEV:                      | Total ramp (kHz): 0.000000                | TX RB DEL: 0. No delay with TX_RB moc 🔻 |

| Single Full Triangle: 0. Disabled 🔹                                | Down ramp DEVoff: 0                 |                                           | Triangle Delay: 0. Disabled 🔻           |

| Parabolic Ramp: 0. Disabled 👻                                      |                                     | Time per step (us): 0.020000              |                                         |

| CLK1:                                                              | Down ramp Steps: 0                  | Time per ramp (us): 0.020000              |                                         |

|                                                                    | TXdata                              | Readback to Muxout                        |                                         |

| Other                                                              | TX Ramp CLK: 0. CLK Div 🔻           | Readback to muxout: 0. Disabled  Muxout ( | le PLL Testmodes,<br>(R0) must be set   |

| Charge Pump Setting: 2.5                                           | Pulse TXdata                        | INT: FRAC:                                | estmodes.                               |

| Interrupt: Interrupt off                                           | TXdata trigger: 0. Disabled ▼       |                                           | ach Readback,<br>t write to R4.         |

| Toggle Ramp On/Off                                                 | TXdata invert: 0. Not inverted 🔻    |                                           |                                         |

|                                                                    |                                     |                                           |                                         |

|                                                                    |                                     |                                           |                                         |

| Registers                                                          |                                     |                                           |                                         |

|                                                                    | 0x 700800A 0x 103                   | 0083 0x 180104 0x                         | 5 0x 6 0x 7                             |

| Write R0 Write R1                                                  | Write R2 Write R3                   |                                           |                                         |

|                                                                    |                                     |                                           |                                         |

| 5:15:52: Firmware loaded.<br>5:15:52: USB adapter board connected. |                                     | OG 0x 180144 0x 80000                     |                                         |

| 5:15:57: USB ready.<br>5:15:57: USB ready.                         |                                     |                                           | (7, 6, 6, 5, 5, 4, 4, 3,                |

| Ixxx USB Adapter Board connected.                                  |                                     |                                           |                                         |

Figure 9. Software—Ramp Controls

### **EVALUATION BOARD SCHEMATICS**

Rev. B | Page 11 of 16

### EV-ADF4159EB1Z/EV-ADF4159EB3Z User Guide

10-27201

Figure 11. Evaluation Board Schematic (Page 2)

### EV-ADF4159EB1Z/EV-ADF4159EB3Z User Guide

Figure 12. Evaluation Board Schematic (Page 3)

Figure 13. Evaluation Board Schematic (Page 4)

Rev. B | Page 14 of 16

### NOTES

### NOTES

#### ESD Caution

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices. Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2013–2014 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG10572-0-7/14(B)

www.analog.com

Rev. B | Page 16 of 16