# AVR459: SB200 Hardware User's Guide

# Features

- Full evaluation of Atmel smart battery reference design.

- Socket for SB20x smart battery reference designs.

- Development platform for AVR based smart batteries.

- Communication gateway between PC and smart battery.

- Single Wire UART for single and dual cell batteries.

- TWI/ SMBus<sup>™</sup> interface for larger batteries.

- Battery Charger.

- Charge with up to 19V and 2A.

- Auto-limitation of charging voltage and current.

- Auto-termination of charging when charging period expires.

- Adjustable Constant Current Load for battery discharging.

- Sink up to 4A continuous current.

- Auto-shut down if too hot.

# **1** Introduction

The SB200 is a development platform for SB20x smart battery reference designs, which offers an easy way to start evaluation and hence development of smart battery applications using Atmel<sup>®</sup> AVR<sup>®</sup> microcontrollers. The SB200 is not in itself a reference design, but is intended to be used with e.g. SB201-1, which is a reference design that demonstrates implementation of a single cell smart battery (Li-Ion).

16340/CR123A battery cells can be inserted in the SB200 battery sockets, and a SB20x is inserted in the dedicated daughter board socket. This forms a "battery pack" with a given number of cells, safety protection and full battery capacity monitoring capabilities. Alternately other cell types can be soldered into the SB200.

To simulate the use of the "battery pack" the SB200 features a Charger that can charge the battery pack, and a Constant Current Load that can simulate an application that draws power from the battery pack.

Figure 1-1. SB200 with two batteries and SB201-2 inserted.

8-bit **AVR**<sup>®</sup> Microcontrollers

# **Application Note**

Rev. 8132A-AVR-10/08

# 2 Safety precautions when using Li-Ion batteries

The batteries provided with the SB200 have built in protection which might cause strange effects to occur if the battery is exposed to overstress situations, such as over-charging. The built in protection does affect the battery characteristics, especially in terms of resistance, but will ensure that even incorrect use and bugs in a smart battery application under development does not pose a safety hazard.

Nevertheless, if battery cells heat up, are physically damaged or shows other signs that can cause or be a consequence of malfunction, the battery cell should be discarded into a safe deposit.

If other batteries without protection are used, please observe the safety guidelines following the batteries. Li-lon and Polymer batteries & packs may explode and cause fire if misused or defective.

# 2.1 Warning – HOT!

Be aware that the heat sinks of the Constant Current Load can get **very hot**. The shunt resistors  $(0.5\Omega)$  at the load and from the charger will also get very hot. Do not touch them!

The SB200 will limit the temperature to approximately 125°C by turning off the load if the temperature rises above this point.

Figure 2-1. Constant Current Load – hot heat sink.

# **3 Functional overview**

The SB200 is developed to ease development of Smart Battery applications: It offers a communication gateway between the SB20x reference designs which uses half duplex UART or SMBus to USB. It can charge the batteries connected or inserted in the board, and act as a load to investigate behavior during discharging of the battery.

The SB200 comes with a PC-software that controls the various features of the kit. An introduction to this software is found in application note "AVR491 – quick start guide for SB200". Both the executable and the source code for the PC software are available from the Atmel web-site, and can be installed into AVR Studio.

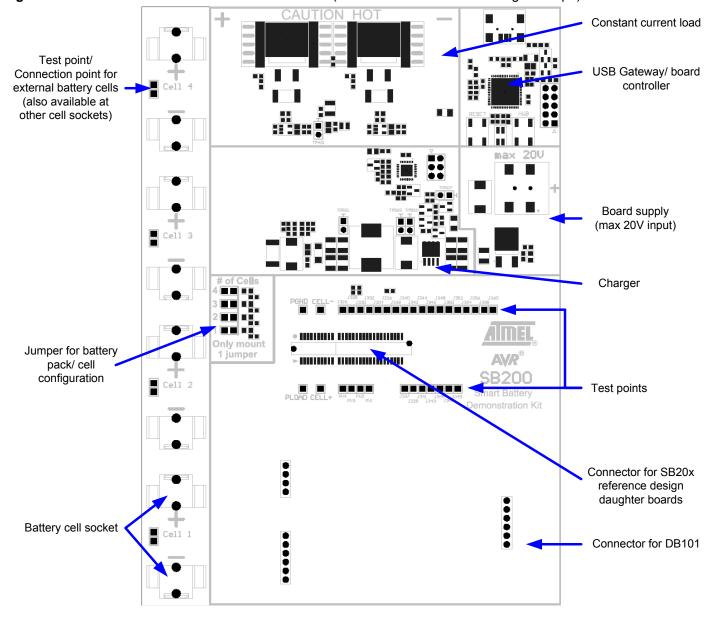

An overview of the hardware is seen in Figure 3-1

2

# AVR459

Figure 3-1. Placement of hardware modules on SB200 (areas within silkscreen rectangles/shape).

# 4 Details of the SB200 blocks

The following sections describe the SB200 blocks on a functional level. Electrical schematics, a Bill of Materials and CAD (gerber) files are available as separate files, which can be downloaded from the Atmel web site <u>http://www.atmel.com/sb200</u>.

The source code for the SB200 firmware is available from the Atmel web site as well, but is provided as is. No support is provided on this part of the code, as it is made as a development tool for smart battery application only. SB200 firmware is based on demo application for AT90USBKEY. The supported code is therefore only the source code for the SB20x smart battery reference designs.

# 5 Insertion of battery cells and placement of the corresponding jumper

Insert only the number of battery cells that are intended to be used with the SB20x in the SB20x daughter board socket. Further, make sure to place the jumper that selects the number of cells correct – otherwise one of the battery cells will be shorted.

| Step | Action                         | Remark                                          |

|------|--------------------------------|-------------------------------------------------|

| 1    | Power Off SB200                | Remove Batteries !                              |

| 2    | Insert SB201-?                 |                                                 |

| 3    | Start PC SW                    |                                                 |

| 4    | Power On SB200                 | Check that correct SB201 is shown in status bar |

| 5    | # of Cells LED should light up |                                                 |

| 6    | Place Red Jumper correct       | Only one jumper                                 |

| 7    | Insert battery / batteries     |                                                 |

| 8    | Press HWB button               | One minute charge is started                    |

# 6 Supply voltage

SB200 can be supplied with up to 20V through the DC jack. The DC jack has positive center. Minimum supply voltage is 7V.

The supply voltage need not be 20V, but needs to be a few volts higher than the maximum voltage of the battery stack on the board. The Charger and the opamp's in the Constant Current Load need that to function properly.

If a two cell smart battery application is being developed it is therefore sufficient to connect e.g. 10V. A higher voltage will only generate unnecessary heat in the board supply regulator, which is used to generate 5V for the USB1287, tiny861 and the DAC.

# 7 Charger

The Charger on the SB200 can deliver 0-20 volts and 0-2 ampere, using a constant current, constant voltage charging scheme. It is configured by setting maximum voltage, maximum current and timeout. The Charger will make sure that no limit is exceeded and will try to make sure one of them is reached.

## 7.1 How it works

A fast PWM output on the Charger is connected via a buck converter to the battery. By changing the duty cycle on the PWM, the voltage to the battery can be adjusted. To be able to measure voltage and current, two ADC pins is connected on both sides of a shunt resistor just before the battery.

The Charger continuously measures the voltage and current and adjusts the PWM output accordingly. The PWM is adjusted one step at a time and this will make it take approximately seven tenths of a second to go from minimum to maximum output. If either maximum current, maximum voltage or timeout is set to zero, charging will stop immediately.

# AVR459

When setting maximum current and voltage, the charging time in minutes is also set. This can be up to 255 minutes and the Charger will stop when the time is reached.

The HWB button on SB200 starts a charge cycle with a duration of 1 minute (or until you press it again). The charge voltage is set depending on which SB20x that is connected. This will also power up the SB20x, if it was off. The voltage, current and timeout will be sent to the PC.

# 7.2 Resolution

The ADC on tiny861 has an external reference of 2.5V, and with 10-bit ADC, this give a resolution of 2.44mV. The voltage input to the ADC is scaled down 8x, so max voltage possible to measure is 19.98V, and resolution is 19.5mV. The current input uses the differential input with 20x gain over a shunt resistor of 0.5 $\Omega$ . This is also scaled down 8x, thus giving a resolution of 1,95mA, so max current possible to measure is 2A. The PWM output to the buck converter has 512 values, which means a resolution of "Input Voltage" divided by 512, e.g. at 10V input the resolution will be approximately 19.5mV.

Note that the battery cell voltage reported in the SB200 PC application may vary during charging. This is because the Charger is continually adjusting the voltage to match the voltage and current limits set.

### 7.3 Communication

The Charger has a simple communication interface on the SPI bus. It understands two commands: One command is "SetCharging" and it configures maximum current, maximum voltage and timeout. The other command is "ChargerRead". This command to the Charger reads the voltage and current seen from the ATtiny861. (Please refer to section 14.4 for more information about the communication).

If it receives any other command, doesn't get all parameters or notices a checksum error it will just discard the message.

The implementation is based on the BC100 reference design and application note AVR458. Please refer to this application note for more information about charging Lilon batteries.

# 8 Constant Current Load

The constant current is implemented with a 14-bit DAC, differential amplifiers and two MOSFET transistors operated in their linear mode. The reference is 5V, step size is approximately  $305\mu$ V. Shunt resistor is two of  $0.5\Omega$  in parallel. Resolution is 1.22mA and max current is 20A.

The load can draw high currents for a short time and is mainly limited by thermal overstress. The current drawn by the load is controlled from the PC software. If the current is kept below 2A for single cell and 1A dual cells applications the load should not overheat (the higher the voltage of the battery stack the lower should the current be).

The USB1287 monitors the temperature of the load, and will shut it down if it reaches 125°C to avoid damage to the MOSFET's.

The load has fairly good accuracy at higher currents, while it may be somewhat inaccurate at lower currents. The constant current stability is very good and it can

therefore be used to test and characterize battery cells and application. The load can be calibrated to get better accuracy and linearity by rewriting the firmware for SB200.

### 8.1 Short circuit load condition

The load is implemented as an integrating circuit. This means that it can be used to simulate high out-rush currents: if the load is enabled, but no current source is available, it will saturate and open fully (max load). When a voltage/current source is enabled the load will for a short moment draw maximum current, and can be seen as a short circuit load. As soon as the current starts flowing the load will start to adjust the current to reach the target level.

This can cause problems if one is not aware of this, since the smart battery AVR MCU will be detect this as a high current/over current/short circuit situation. However, this characteristic of the load can be used to test an implementation of a smart battery, as it can be used intentionally to trigger a high out-rush current situation and validate correct behavior.

# 9 Test and connection points

The SB200 offer a variety of test and connection points, some for easy access to relevant signals with scope probes, and others to make it possible to connect external units.

### 9.1 External connection

On each side of the heat sink at the Constant Current Load, connection points are available. These can be used to measure the battery stack voltage, or an external charger can be connected here. The connection points are designed to match a 4mm power connector such as <u>Farnell</u> no: 1101128 / 1101127. This makes it also easy to connect an external load if the on-board load is not sufficient. It also allows for the on-board load to be used towards an external target, for testing purposes.

## 9.2 External battery cells

If it is desired to connect battery cells to the SB200 that does not fit in the sockets, these can be placed on an external board and connected to the SB200 test/connection points at each of the battery cell sockets (see Figure 3-1).

These connections points can also be used to connect an external power supply instead of batteries. This can be used to more easily and safely test how the smart battery implementation reacts to extreme voltage/current conditions.

If working with cells that fit in the sockets these test/connection points can be used to measure the voltage over the battery cells.

### 9.3 Signal line test points

**AVR459**

All signals available on the SB20x edge connector are available as test points. These are located next to the SB20x daughter board connector (see Figure 3-1). 2.54mm pin headers can be mounted to make it easier to hook a scope probe to these test points.

| J323PV2Positive voltage cell 2J325PV1Positive voltage cell 1J326 <sup>(1)</sup> V4Positive voltage cell 4J327PV4Positive voltage cell 4J328SCLTW/SMBus clockJ329PV3Positive voltage cell 3J330SDATW/SMBus dataJ332 <sup>(1)</sup> AIJ334 <sup>(1)</sup> AIJ336 <sup>(1)</sup> AIJ337PA3AVR Port A pin 3J338 <sup>(1)</sup> AIJ339PA2AVR Port A pin 1J340 <sup>(1)</sup> IIJ341PA1AVR Port A pin 1J342 <sup>(1)</sup> IIJ341PA1AVR Port A pin 1J342 <sup>(1)</sup> IIJ343PA0AVR Port A pin 0J344 <sup>(1)</sup> IIJ345VrefVoltage referenceJ346CELLIBAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WIJ351MISOSPI master input slave outputJ352SKSPI clockJ358SSSPI slave selectJ360RESETReset to smart battery AVR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Test point designator | Signal      | Description                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|--------------------------------|

| J326 <sup>(1)</sup> J           J327         PV4         Positive voltage cell 4           J328         SCL         TWI/SMBus clock           J329         PV3         Positive voltage cell 3           J330         SDA         TWI/SMBus data           J332 <sup>(1)</sup> -         -           J336 <sup>(1)</sup> -         -           J336 <sup>(1)</sup> -         -           J338 <sup>(1)</sup> -         -           J339         PA3         AVR Port A pin 3           J338 <sup>(1)</sup> -         -           J340 <sup>(1)</sup> -         -           J341         PA1         AVR Port A pin 2           J343         PA0         AVR Port A pin 1           J342 <sup>(1)</sup> -         -           J343         PA0         AVR Port A pin 1           J342 <sup>(1)</sup> -         -           J343         PA0         AVR Port A pin 0           J344 <sup>(1)</sup> -         -           J345         Vref         Voltage reference           J346         CELL2BAL_ON         Cell 1 cell balancing enable           J347         GND_ID         GND for ID circuitry           J348                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J323                  | PV2         | Positive voltage cell 2        |

| J327         PV4         Positive voltage cell 4           J328         SCL         TWI/SMBus clock           J329         PV3         Positive voltage cell 3           J330         SDA         TWI/SMBus data           J332 <sup>(1)</sup> -         -           J334 <sup>(1)</sup> -         -           J336 <sup>(1)</sup> -         -           J336 <sup>(1)</sup> -         -           J338 <sup>(1)</sup> PA3         AVR Port A pin 3           J338 <sup>(1)</sup> -         -           J339         PA2         AVR Port A pin 2           J340 <sup>(1)</sup> -         -           J341         PA1         AVR Port A pin 1           J342 <sup>(1)</sup> -         -           J343         PA0         AVR Port A pin 0           J343         PA0         AVR Port A pin 0           J344 <sup>(1)</sup> -         -           J345         Vref         Voltage reference           J346         CELL1BAL_ON         Cell 1 cell balancing enable           J347         GND_ID         GND for ID circuitry           J348         CELL2BAL_ON         Cell 2 cell balancing enable           J349         Vreg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | J325                  | PV1         | Positive voltage cell 1        |

| J328         SCL         TWI/SMBus clock           J329         PV3         Positive voltage cell 3           J330         SDA         TWI/SMBus data           J332 <sup>(1)</sup> -         -           J334 <sup>(1)</sup> -         -           J336 <sup>(1)</sup> -         -           J337         PA3         AVR Port A pin 3           J338 <sup>(1)</sup> -         -           J339         PA2         AVR Port A pin 2           J340 <sup>(1)</sup> -         -           J341         PA1         AVR Port A pin 1           J342 <sup>(1)</sup> -         -           J343         PA0         AVR Port A pin 0           J343         PA0         AVR Port A pin 0           J344 <sup>(1)</sup> -         -           J345         Vref         Voltage reference           J346         CELL1BAL_ON         Cell 1 cell balancing enable           J347         GND_ID         GND for ID circuitry           J348         CELL2BAL_ON         Cell 2 cell balancing enable           J349         Vreg         Regulated supply voltage           J350         UART1W         -           J354         MOSI         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | J326 <sup>(1)</sup>   |             |                                |

| J329         PV3         Positive voltage cell 3           J330         SDA         TWI/SMBus data           J332 <sup>(1)</sup> -         -           J334 <sup>(1)</sup> -         -           J336 <sup>(1)</sup> -         -           J337         PA3         AVR Port A pin 3           J338 <sup>(1)</sup> -         -           J339         PA2         AVR Port A pin 2           J340 <sup>(1)</sup> -         -           J341         PA1         AVR Port A pin 1           J342 <sup>(1)</sup> -         -           J343         PA0         AVR Port A pin 0           J343         PA0         AVR Port A pin 0           J344 <sup>(1)</sup> -         -           J345         Vref         Voltage reference           J346         CELL1BAL_ON         Cell 1 cell balancing enable           J347         GND_ID         GND for ID circuitry           J348         CELL2BAL_ON         Cell 2 cell balancing enable           J349         Vreg         Regulated supply voltage           J350         UART1W         -           J354         MOSI         SPI master output, slave input           J356         SCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | J327                  | PV4         | Positive voltage cell 4        |

| J330         SDA         TWI/SMBus data           J332 <sup>(1)</sup> -         -           J334 <sup>(1)</sup> -         -           J336 <sup>(1)</sup> -         -           J336 <sup>(1)</sup> -         -           J337         PA3         AVR Port A pin 3           J338 <sup>(1)</sup> -         -           J339         PA2         AVR Port A pin 2           J340 <sup>(1)</sup> -         -           J341         PA1         AVR Port A pin 1           J342 <sup>(1)</sup> -         -           J343         PA0         AVR Port A pin 0           J344 <sup>(1)</sup> -         -           J345         Vref         Voltage reference           J346         CELL1BAL_ON         Cell 1 cell balancing enable           J347         GND_ID         GND for ID circuitry           J348         CELL2BAL_ON         Cell 2 cell balancing enable           J349         Vreg         Regulated supply voltage           J350         UART1W         -           J354         MOSI         SPI master output, slave input           J356         SCK         SPI clock           J358         SS         SPI slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | J328                  | SCL         | TWI/SMBus clock                |

| J332 <sup>(1)</sup> J334 <sup>(1)</sup> J334 <sup>(1)</sup> J336 <sup>(1)</sup> J337         PA3           J338 <sup>(1)</sup> J337           J338 <sup>(1)</sup> J338           J339         PA2           J340 <sup>(1)</sup> J339           J340 <sup>(1)</sup> J340           J341         PA1           AVR Port A pin 1           J342 <sup>(1)</sup> J343           J343         PA0           J344 <sup>(1)</sup> J344 <sup>(1)</sup> J345         Vref           J346         CELL1BAL_ON           CELL2BAL_ON         Cell 1 cell balancing enable           J349         Vreg           J348         CELL2BAL_ON           J350         UART1W           J352         MISO           J356         SCK           SPI master output, slave input           J358         SS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | J329                  | PV3         | Positive voltage cell 3        |

| J334 <sup>(1)</sup> Image: selectJ336 <sup>(1)</sup> PA3AVR Port A pin 3J337PA3AVR Port A pin 3J338 <sup>(1)</sup> Image: selectAVR Port A pin 2J340 <sup>(1)</sup> PA2AVR Port A pin 1J341PA1AVR Port A pin 1J342 <sup>(1)</sup> Image: selectImage: selectJ343PA0AVR Port A pin 0J344 <sup>(1)</sup> Image: selectJ345VrefVoltage referenceJ346CELL1BAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WImage: selectJ358SSSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | J330                  | SDA         | TWI/SMBus data                 |

| J336 <sup>(1)</sup> PA3AVR Port A pin 3J337PA3AVR Port A pin 3J338 <sup>(1)</sup> IJ339PA2AVR Port A pin 2J340 <sup>(1)</sup> IJ341PA1AVR Port A pin 1J342 <sup>(1)</sup> IJ343PA0AVR Port A pin 0J344 <sup>(1)</sup> IJ345VrefVoltage referenceJ346CELL1BAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ350UART1WIJ352MISOSPI master input slave outputJ356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | J332 <sup>(1)</sup>   |             |                                |

| J337PA3AVR Port A pin 3J338 <sup>(1)</sup> -J339PA2AVR Port A pin 2J340 <sup>(1)</sup> -J341PA1AVR Port A pin 1J342 <sup>(1)</sup> -J343PA0AVR Port A pin 0J344 <sup>(1)</sup> -J345VrefVoltage referenceJ346CELL1BAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ350UART1W-J352MISOSPI master input slave outputJ354SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | J334 <sup>(1)</sup>   |             |                                |

| J338PA2AVR Port A pin 2J340J340PA1AVR Port A pin 1J341PA1AVR Port A pin 1J342J343PA0AVR Port A pin 0J344J345VrefVoltage referenceJ346CELL1BAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WJ352J356SCKSPI master input slave outputJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | J336 <sup>(1)</sup>   |             |                                |

| J339PA2AVR Port A pin 2J340 <sup>(1)</sup> IJ341PA1AVR Port A pin 1J342 <sup>(1)</sup> IJ343PA0AVR Port A pin 0J344 <sup>(1)</sup> IJ345VrefVoltage referenceJ346CELL1BAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WIJ352MISOSPI master input slave outputJ354MOSISPI master output, slave inputJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | J337                  | PA3         | AVR Port A pin 3               |

| J340 <sup>(1)</sup> PA1AVR Port A pin 1J341PA1AVR Port A pin 1J342 <sup>(1)</sup> PA0AVR Port A pin 0J343PA0AVR Port A pin 0J344 <sup>(1)</sup> VefVoltage referenceJ345VrefVoltage referenceJ346CELL1BAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WJ352J354MOSISPI master input slave outputJ356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | J338 <sup>(1)</sup>   |             |                                |

| J341PA1AVR Port A pin 1J342(1)IJ343PA0AVR Port A pin 0J344(1)IJ345VrefVoltage referenceJ346CELL1BAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WIJ354MOSISPI master input slave outputJ356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | J339                  | PA2         | AVR Port A pin 2               |

| J342(1)AVR Port A pin 0J343PA0AVR Port A pin 0J344(1)-J345VrefVoltage referenceJ346CELL1BAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WJ352MISOSPI master input slave outputJ354SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | J340 <sup>(1)</sup>   |             |                                |

| J343PA0AVR Port A pin 0J344Image: state of the s                                     | J341                  | PA1         | AVR Port A pin 1               |

| J344Image: Second s | J342 <sup>(1)</sup>   |             |                                |

| J345VrefVoltage referenceJ346CELL1BAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WJ352J354MOSISPI master input slave outputJ356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J343                  | PA0         | AVR Port A pin 0               |

| J346CELL1BAL_ONCell 1 cell balancing enableJ347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WJ352MISOSPI master input slave outputJ354MOSISPI master output, slave inputJ356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | J344 <sup>(1)</sup>   |             |                                |

| J347GND_IDGND for ID circuitryJ348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WJ352J354MISOSPI master input slave outputJ356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | J345                  | Vref        | Voltage reference              |

| J348CELL2BAL_ONCell 2 cell balancing enableJ349VregRegulated supply voltageJ350UART1WJ352MISOSPI master input slave outputJ354MOSISPI master output, slave inputJ356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J346                  | CELL1BAL_ON | Cell 1 cell balancing enable   |

| J349VregRegulated supply voltageJ350UART1WJ352MISOJ354MOSIJ356SCKJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | J347                  | GND_ID      | GND for ID circuitry           |

| J350UART1WJ352MISOSPI master input slave outputJ354MOSISPI master output, slave inputJ356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | J348                  | CELL2BAL_ON | Cell 2 cell balancing enable   |

| J352MISOSPI master input slave outputJ354MOSISPI master output, slave inputJ356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | J349                  | Vreg        | Regulated supply voltage       |

| J354MOSISPI master output, slave inputJ356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | J350                  | UART1W      |                                |

| J356SCKSPI clockJ358SSSPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J352                  | MISO        | SPI master input slave output  |

| J358 SS SPI slave select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | J354                  | MOSI        | SPI master output, slave input |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | J356                  | SCK         | SPI clock                      |

| J360 RESET Reset to smart battery AVR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | J358                  | SS          | SPI slave select               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | J360                  | RESET       | Reset to smart battery AVR     |

Notes: 1. Test point reserved for future use

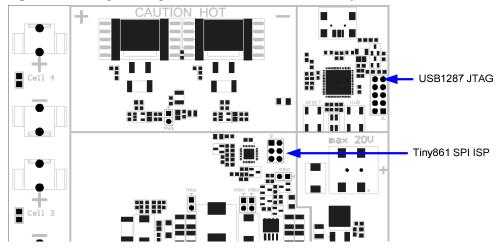

# 10 Programming the USB1287 or the tiny861

Reprogramming of the AT90USB1287 (USB gateway and board controller) and the ATtiny861 that controls the Charger is possible, and may be required to use the latest version of the firmware. It is recommended to always upgrade to the latest version of the firmware, found on www.atmel.com, to ensure that the firmware match this documentation and operates accordingly. The firmware source code running in these devices are available, but only as an extra service: These devices are part of the

development platform, not part of a reference design. Therefore the source code for these devices are provided as is, and with limited support. The product supported fully is the source code for the reference designs such as the SB201.

One case where update of the USB1287 firmware can be relevant is if a different communication protocol is desired to be used between the smart battery and the host. During the development it can be desired to use the USB1287 as a gateway to communicate with the smart battery via this interface/protocol. Changes and extensions to the communication interface/protocol are left to the users to implement.

To program the tiny861, the USB cable must be disconnected, and the USB1287 will release the SPI-lines which are used for inter-communication.

Figure 10-1. Programming interfaces for USB1287 and tiny861.

# **11 Buttons**

Next to the USB1287 two buttons are present:

"Reset" will reset the USB1287 device and the Constant Current Load.

"HWB" will either enable the Charger for a short time to start the smart battery device, or it will stop the Charger next time the button is pressed.

| SB20x   | Max Voltage | Max Current | Timeout |

|---------|-------------|-------------|---------|

| SB201-1 | 4200mV      | 100mA       | 1min    |

| SB201-2 | 8400mV      | 100mA       | 1min    |

# **12 Status LED**

8

An RGB LED is located between the buttons. This indicates the status of the USB1287. When the LED is red the USB1287 is transmitting, and when it is green the USB1287 is receiving. As transmission is so fast that the human eye cannot distinguish the individual colors, the LED would appear yellow during transfers.

# 13 DB101 support for portable demonstration

A DB101 can be placed on the female pin header. This is an alternative to using a PC as host. The DB101 would typically only be used for demonstration, where standalone battery powered operation is desired. Atmel does not provide firmware for this.

## 13.1 Battery cells provided with SB200

Though the capacity of the cells is specified to 880mAh they are actually closer to 700mAh.

The cells have built in protection, which affects the characteristic of the battery. It can be an advantage to use unprotected cells if a more correct behavior is desired. However, it is recommended to use protected cells until the implementation is verified to not allow overstress of the connected cells.

# **14 Communication Gateway**

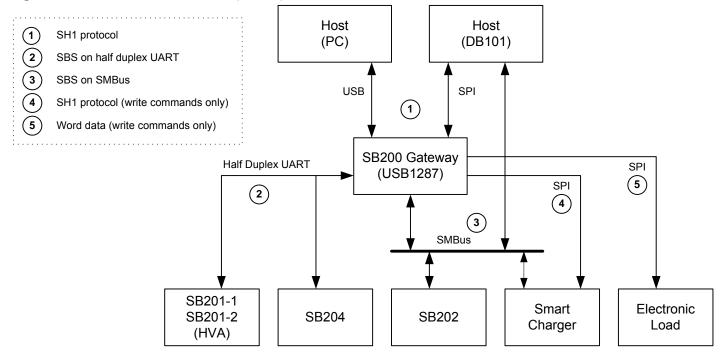

An AT90USB1287 AVR microcontroller acts as both communication gateway and board controller. It passes messages from its USB interface to other units on the SB200. The communication links on the SB200 is shown on Figure 14-1. The figure also shows reference designs SB204 and SB202 which are not available upon release of the SB200

Figure 14-1. Communication links on (and off) the SB200.

# 14.1 Communication protocol between the Host (PC) and the USB1287 gateway.

The SH1 protocol is built to be tested/invoked from a terminal, that's the reason for all the ASCII characters. The package uses a:

- Fixed character as preamble to indicate start of package

- Destination address byte

- Source address byte

- Command byte

- Size byte

- Data payload

- Simple checksum byte, the sum of previous bytes

- Carriage return character

The package is minimum 7 bytes and maximum 262 bytes in size. DATA is transmitted only if NBYTES is nonzero.

### Example: Send 2 bytes from PC to Electronic Load.

| SYNC | ADDRESS | SENDER | COMMAND | NBYTES | DATA   | CS   | CR   |

|------|---------|--------|---------|--------|--------|------|------|

| U    | E       | Р      | С       | 2      | int mA | Calc | 7    |

| 0x55 | 0x45    | 0x50   | 0x43    | 0x02   | 0x04B0 | 0xE3 | 0x0D |

# 14.1.1 Source and destination ADDRESS.

| Address (ASCII) | Address (hex) | HW Module       |

|-----------------|---------------|-----------------|

| С               | 0x43          | Charger         |

| D               | 0x44          | DB101 Display   |

| E               | 0x45          | Electronic Load |

| М               | 0x4D          | Main Controller |

| Р               | 0x50          | PC              |

| S               | 0x53          | SB20x           |

## 14.2 Global COMMAND