# 16-Kbit (2K × 8) Serial (I<sup>2</sup>C) F-RAM

### Features

- 16-Kbit ferroelectric random access memory (F-RAM) logically organized as 2K x 8

- □ High-endurance 100 trillion (10<sup>14</sup>) read/writes

- □ 151-year data retention (See the Data Retention and Endurance table)

- □ NoDelay<sup>™</sup> writes

- Advanced high-reliability ferroelectric process

- Fast 2-wire Serial interface (I<sup>2</sup>C)

- Up to 1-MHz frequency

- □ Direct hardware replacement for serial (I<sup>2</sup>C) EEPROM

- □ Supports legacy timings for 100 kHz and 400 kHz

- Low power consumption

100 μA active current at 100 kHz

4 μA (typ) standby current

- Voltage operation: V<sub>DD</sub> = 4.5 V to 5.5 V

- Industrial temperature: -40 °C to +85 °C

- 8-pin small outline integrated circuit (SOIC) package

- Restriction of hazardous substances (RoHS) compliant

### **Functional Description**

The FM24C16B is a 16-Kbit nonvolatile memory employing an advanced ferroelectric process. A ferroelectric random access memory or F-RAM is nonvolatile and performs reads and writes similar to a RAM. It provides reliable data retention for 151 years while eliminating the complexities, overhead, and system-level reliability problems caused by EEPROM and other nonvolatile memories.

Unlike EEPROM, the FM24C16B performs write operations at bus speed. No write delays are incurred. Data is written to the memory array immediately after each byte is successfully transferred to the device. The next bus cycle can commence without the need for data polling. In addition, the product offers substantial write endurance compared with other nonvolatile memories. Also, F-RAM exhibits much lower power during writes than EEPROM since write operations do not require an internally elevated power supply voltage for write circuits. The FM24C16B is capable of supporting 10<sup>14</sup> read/write cycles, or 100 million times more write cycles than EEPROM.

These capabilities make the FM24C16B ideal for nonvolatile memory applications, requiring frequent or rapid writes. Examples range from data logging, where the number of write cycles may be critical, to demanding industrial controls where the long write time of EEPROM can cause data loss. The combination of features allows more frequent data writing with less overhead for the system.

The FM24C16B provides substantial benefits to users of serial (I<sup>2</sup>C) EEPROM as a hardware drop-in replacement. The device specifications are guaranteed over an industrial temperature range of -40 °C to +85 °C.

For a complete list of related documentation, click here.

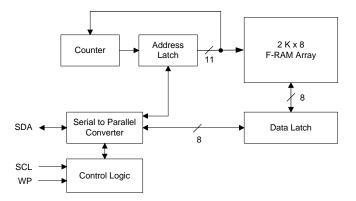

### Logic Block Diagram

Cypress Semiconductor Corporation Document Number: 001-84450 Rev. \*K 198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised April 19, 2017

# Contents

| Pinout                             | 3  |

|------------------------------------|----|

| Pin Definitions                    | 3  |

| Functional Overview                | 4  |

| Memory Architecture                | 4  |

| I2C Interface                      | 4  |

| STOP Condition (P)                 | 4  |

| START Condition (S)                | 4  |

| Data/Address Transfer              | 5  |

| Acknowledge/No-acknowledge         |    |

| Slave Device Address               |    |

| Addressing Overview (Word Address) | 6  |

| Data Transfer                      |    |

| Memory Operation                   | 6  |

| Write Operation                    |    |

| Read Operation                     |    |

| Endurance                          |    |

| Maximum Ratings                    | 9  |

| Operating Range                    |    |

| DC Electrical Characteristics      |    |

| Data Retention and Endurance       | 10 |

|                                    |    |

| Capacitance                             | 10 |

|-----------------------------------------|----|

| Thermal Resistance                      | 10 |

| AC Test Loads and Waveforms             | 10 |

| AC Test Conditions                      | 10 |

| AC Switching Characteristics            | 11 |

| Power Cycle Timing                      | 12 |

| Ordering Information                    | 13 |

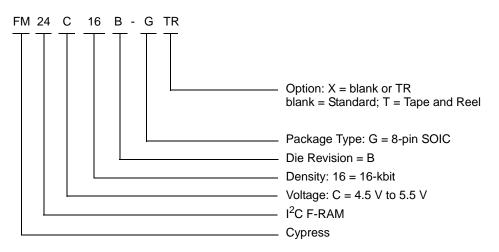

| Ordering Code Definitions               | 13 |

| Package Diagram                         | 14 |

| Acronyms                                | 15 |

| Document Conventions                    | 15 |

| Units of Measure                        | 15 |

| Document History Page                   | 16 |

| Sales, Solutions, and Legal Information | 17 |

| Worldwide Sales and Design Support      | 17 |

| Products                                |    |

| PSoC® Solutions                         | 17 |

| Cypress Developer Community             |    |

| Technical Support                       |    |

|                                         |    |

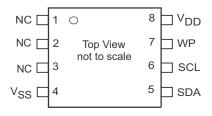

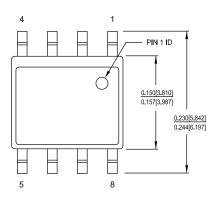

# Pinout

### Figure 1. 8-pin SOIC pinout

# **Pin Definitions**

| Pin Name        | I/O Type     | Description                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA             | Input/Output | Serial Data/Address. This is a bi-directional pin for the I <sup>2</sup> C interface. It is open-drain and is intended to be wire-AND'd with other devices on the I <sup>2</sup> C bus. The input buffer incorporates a Schmitt trigger for noise immunity and the output driver includes slope control for falling edges. An external pull-up resistor is required. |

| SCL             | Input        | <b>Serial Clock</b> . The serial clock pin for the $l^2C$ interface. Data is clocked out of the device on the falling edge, and into the device on the rising edge.                                                                                                                                                                                                  |

| WP              | Input        | Write Protect. When tied to V <sub>DD</sub> , addresses in the entire memory map will be write-protected. When WP is connected to ground, all addresses are write enabled. This pin is pulled down internally.                                                                                                                                                       |

| V <sub>SS</sub> | Power supply | Ground for the device. Must be connected to the ground of the system.                                                                                                                                                                                                                                                                                                |

| V <sub>DD</sub> | Power supply | Power supply input to the device.                                                                                                                                                                                                                                                                                                                                    |

## **Functional Overview**

The FM24C16B is a serial F-RAM memory. The memory array is logically organized as 2,048 × 8 bits and is accessed using an industry-standard I<sup>2</sup>C interface. The functional operation of the F-RAM is similar to serial (I<sup>2</sup>C) EEPROM. The major difference between the FM24C16B and a serial (I<sup>2</sup>C) EEPROM with the same pinout is the F-RAM's superior write performance, high endurance, and low power consumption.

## **Memory Architecture**

When accessing the FM24C16B, the user addresses 2K locations of eight data bits each. These eight data bits are shifted in or out serially. The addresses are accessed using the I<sup>2</sup>C protocol, which includes a slave address (to distinguish other non-memory devices), a row address, and a segment address. The row address consists of 8-bits that specify one of the 256 rows. The 3-bit segment address specifies one of the 8 segments within each row. The complete address of 11-bits specifies each byte address uniquely.

The access time for the memory operation is essentially zero, beyond the time needed for the serial protocol. That is, the memory is read or written at the speed of the  $l^2C$  bus. Unlike a serial ( $l^2C$ ) EEPROM, it is not necessary to poll the device for a ready condition because writes occur at bus speed. By the time a new bus transaction can be shifted into the device, a write

operation is complete. This is explained in more detail in the interface section.

Note that the FM24C16B contains no power management circuits other than a simple internal power-on reset. It is the user's responsibility to ensure that  $V_{DD}$  is within data sheet tolerances to prevent incorrect operation.

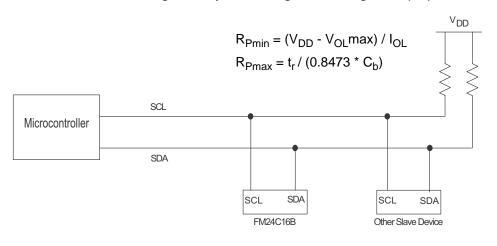

# I<sup>2</sup>C Interface

The FM24C16B employs a bi-directional  $I^2C$  bus protocol using few pins or board space. Figure 2 illustrates a typical system configuration using the FM24C16B in a microcontroller-based system. The industry standard  $I^2C$  bus is familiar to many users but is described in this section.

By convention, any device that is sending data onto the bus is the transmitter while the target device for this data is the receiver. The device that is controlling the bus is the master. The master is responsible for generating the clock signal for all operations. Any device on the bus that is being controlled is a slave. The FM24C16B is always a slave device.

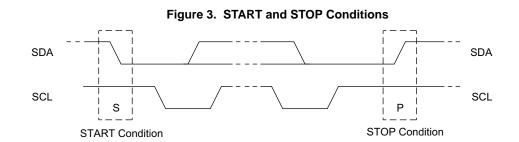

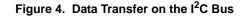

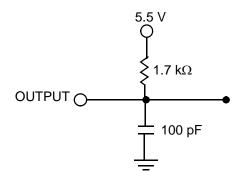

The bus protocol is controlled by transition states in the SDA and SCL signals. There are four conditions including START, STOP, data bit, or acknowledge. Figure 3 on page 5 and Figure 4 on page 5 illustrates the signal conditions that specify the four states. Detailed timing diagrams are shown in the electrical specifications section.

### Figure 2. System Configuration using Serial (I<sup>2</sup>C) nvSRAM

### **STOP Condition (P)**

A STOP condition is indicated when the bus master drives SDA from LOW to HIGH while the SCL signal is HIGH. All operations using the FM24C16B should end with a STOP condition. If an operation is in progress when a STOP is asserted, the operation will be aborted. The master must have control of SDA in order to assert a STOP condition.

### **START Condition (S)**

A START condition is indicated when the bus master drives SDA from HIGH to LOW while the SCL signal is HIGH. All commands should be preceded by a START condition. An operation in progress can be aborted by asserting a START condition at any time. Aborting an operation using the START condition will ready the FM24C16B for a new operation.

If during operation the power supply drops below the specified  $V_{DD}$  minimum, the system should issue a START condition prior to performing another operation.

#### Data/Address Transfer

All data transfers (including addresses) take place while the SCL signal is HIGH. Except under the two conditions described above, the SDA signal should not change while SCL is HIGH.

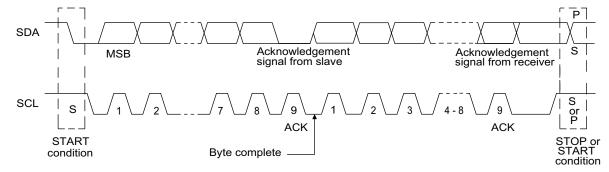

#### Acknowledge/No-acknowledge

The acknowledge takes place after the 8th data bit has been transferred in any transaction. During this state the transmitter should release the SDA bus to allow the receiver to drive it. The receiver drives the SDA signal LOW to acknowledge receipt of the byte. If the receiver does not drive SDA LOW, the condition is a no-acknowledge and the operation is aborted.

The receiver would fail to acknowledge for two distinct reasons. First is that a byte transfer fails. In this case, the no-acknowledge ceases the current operation so that the device can be addressed again. This allows the last byte to be recovered in the event of a communication error.

Second and most common, the receiver does not acknowledge to deliberately end an operation. For example, during a read operation, the FM24C16B will continue to place data onto the bus as long as the receiver sends acknowledges (and clocks). When a read operation is complete and no more data is needed, the receiver must not acknowledge the last byte. If the receiver acknowledges the last byte, this will cause the FM24C16B to attempt to drive the bus on the next clock while the master is sending a new command such as STOP.

#### Slave Device Address

The first byte that the FM24C16B expects after a START condition is the slave address. As shown in Figure 6, the slave address contains the device type, the page of memory to be accessed, and a bit that specifies if the transaction is a read or a write.

Bits 7–4 are the device type and should be set to 1010b for the FM24C16B. These bits allow other function types to reside on the  $I^2C$  bus within an identical address range. Bits 3–1 are the page select. It specifies the 256-byte block of memory that is targeted for the current operation. Bit 0 is the read/write bit (R/W). R/W = '1' indicates a read operation and R/W = '0' indicates a write operation.

#### Figure 6. Memory Slave Device Address

#### Addressing Overview (Word Address)

After the FM24C16B (as receiver) acknowledges the slave address, the master can place the word address on the bus for a write operation. The word address is the lower 8-bits of the address to be combined with the 3-bits page select to specify exactly the byte to be written. The complete 11-bit address is latched internally. No word address occurs for a read operation, though the 3-bit page select is latched internally. Reads always use the lower 8-bits that are held internally in the address latch. That is, reads always begin at the address following the previous access. A random read address can be loaded by doing a write operation as explained below.

After transmission of each data byte, just prior to the acknowledge, the FM24C16B increments the internal address latch. This allows the next sequential byte to be accessed with no additional addressing. After the last address (7FFh) is reached, the address latch will roll over to 000h. There is no limit to the number of bytes that can be accessed with a single read or write operation.

#### Data Transfer

After the address bytes have been transmitted, data transfer between the bus master and the FM24C16B can begin. For a read operation the FM24C16B will place 8 data bits on the bus then wait for an acknowledge from the master. If the acknowledge occurs, the FM24C16B will transfer the next

sequential byte. If the acknowledge is not sent, the FM24C16B will end the read operation. For a write operation, the FM24C16B will accept 8 data bits from the master then send an acknowledge. All data transfer occurs MSB (most significant bit) first.

### **Memory Operation**

The FM24C16B is designed to operate in a manner very similar to other  $I^2C$  interface memory products. The major differences result from the higher performance write capability of F-RAM technology. These improvements result in some differences between the FM24C16B and a similar configuration EEPROM during writes. The complete operation for both writes and reads is explained below.

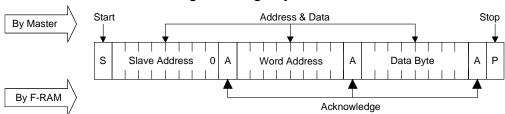

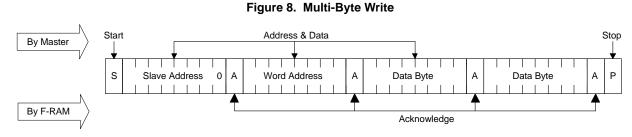

#### Write Operation

All writes begin with a slave address, then a word address. The bus master indicates a write operation by setting the LSB of the slave address (R/W bit) to a '0'. After addressing, the bus master sends each byte of data to the memory and the memory generates an acknowledge condition. Any number of sequential bytes may be written. If the end of the address range is reached internally, the address counter will wrap from 7FFh to 000h.

Unlike other nonvolatile memory technologies, there is no effective write delay with F-RAM. Since the read and write access times of the underlying memory are the same, the user experiences no delay through the bus. The entire memory cycle occurs in less time than a single bus clock. Therefore, any operation including read or write can occur immediately following a write. Acknowledge polling, a technique used with EEPROMs to determine if a write is complete is unnecessary and will always return a ready condition.

Internally, an actual memory write occurs after the 8th data bit is transferred. It will be complete before the acknowledge is sent. Therefore, if the user desires to abort a write without altering the memory contents, this should be done using START or STOP condition prior to the 8th data bit. The FM24C16B uses no page buffering.

The memory array can be write-protected using the WP pin. Setting the WP pin to a HIGH condition ( $V_{DD}$ ) will write-protect all addresses. The FM24C16B will not acknowledge data bytes that are written to protected addresses. In addition, the address counter will not increment if writes are attempted to these addresses. Setting WP to a LOW state ( $V_{SS}$ ) will disable the write protect. WP is pulled down internally.

Figure 7 and Figure 8 on page 7 below illustrate a single-byte and multiple-byte write cycles.

### Figure 7. Single-Byte Write

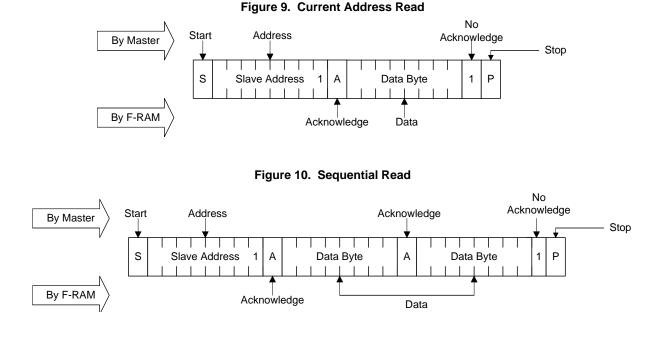

### **Read Operation**

There are two basic types of read operations. They are current address read and selective address read. In a current address read, the FM24C16B uses the internal address latch to supply the lower 8 address bits. In a selective read, the user performs a procedure to set these lower address bits to a specific value.

#### Current Address & Sequential Read

As mentioned above the FM24C16B uses an internal latch to supply the lower 8 address bits for a read operation. A current address read uses the existing value in the address latch as a starting place for the read operation. The system reads from the address immediately following that of the last operation.

To perform a current address read, the bus master supplies a slave address with the LSB set to a '1'. This indicates that a read operation is requested. The three page select bits in the slave address specifies the block of memory that is used for the read operation. After receiving the complete slave address, the FM24C16B will begin shifting out data from the current address on the next clock. The current address is the 3-bits from the slave address combined with the 8-bits that were in the internal address latch.

Beginning with the current address, the bus master can read any number of bytes. Thus, a sequential read is simply a current address read with multiple byte transfers. After each byte the internal address counter will be incremented.

**Note** Each time the bus master acknowledges a byte, this indicates that the FM24C16B should read out the next sequential byte.

There are four ways to properly terminate a read operation. Failing to properly terminate the read will most likely create a bus contention as the FM24C16B attempts to read out additional data onto the bus. The four valid methods are:

- 1. The bus master issues a no-acknowledge in the 9th clock cycle and a STOP in the 10th clock cycle. This is illustrated in the diagrams below. This is preferred.

- 2. The bus master issues a no-acknowledge in the 9th clock cycle and a START in the 10th.

- 3. The bus master issues a STOP in the 9th clock cycle.

- 4. The bus master issues a START in the 9th clock cycle.

If the internal address reaches 7FFh, it will wrap around to 000h on the next read cycle. Figure 9 and Figure 10 below show the proper operation for current address reads.

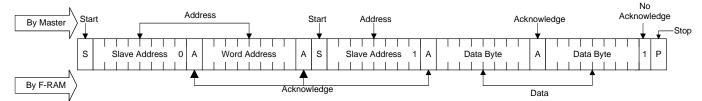

#### Selective (Random) Read

There is a simple technique that allows a user to select a random address location as the starting point for a read operation. This involves using the first two bytes of a write operation to set the internal address followed by subsequent read operations.

To perform a selective read, the bus master sends out the slave address with the LSB (R/W) set to 0. This specifies a write

operation. According to the write protocol, the bus master then sends the word address byte that is loaded into the internal address latch. After the FM24C16B acknowledges the word address, the bus master issues a START condition. This simultaneously aborts the write operation and allows the read command to be issued with the slave address LSB set to a '1'. The operation is now a current address read.

#### Figure 11. Selective (Random) Read

### Endurance

The FM24C16B internally operates with a read and restore mechanism. Therefore, endurance cycles are applied for each read or write cycle. The memory architecture is based on an array of rows and columns. Each read or write access causes an endurance cycle for an entire row. In the FM24C16B, a row is 64 bits wide. Every 8-byte boundary marks the beginning of a new

row. Endurance can be optimized by ensuring frequently accessed data is located in different rows. Regardless, FRAM read and write endurance is effectively unlimited at the 1MHz I<sup>2</sup>C speed. Even at 3000 accesses per second to the same row, 10 years time will elapse before 1 trillion endurance cycles occur.

# **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. These user guidelines are not tested.

| Storage temperature55 °C to +125 °C                                                                      |

|----------------------------------------------------------------------------------------------------------|

| Maximum accumulated storage time<br>At 125 °C ambient temperature 1000 h<br>At 85 °C ambient temperature |

| Ambient temperature<br>with power applied55 °C to +125 °C                                                |

| Supply voltage on $V_{DD}$ relative to $V_{SS}$ 1.0 V to +7.0 V                                          |

| Input voltage                                                                                            |

| DC voltage applied to outputs in High-Z state0.5 V to $V_{\text{DD}}$ + 0.5 V                            |

| Transient voltage (< 20 ns) on any pin to ground potential2.0 V to $V_{DD}$ + 2.0 V                      |

| Package power dissipation capability ( $T_A = 25 \text{ °C}$ ) 1.0 W                                           |

|----------------------------------------------------------------------------------------------------------------|

| Surface mount lead<br>soldering temperature (10 seconds)+260 °C                                                |

| Electrostatic Discharge Voltage <sup>[1]</sup><br>Human Body Model (AEC-Q100-002 Rev. E) 2 kV                  |

| Charged Device Model (AEC-Q100-011 Rev. B)                                                                     |

| Latch-up current> 140 mA                                                                                       |

| * Exception: The "V $_{\rm IN}$ < V $_{\rm DD}$ + 1.0 V" restriction does not apply to the SCL and SDA inputs. |

# **Operating Range**

| Range      | Ambient Temperature (T <sub>A</sub> ) | V <sub>DD</sub> |

|------------|---------------------------------------|-----------------|

| Industrial | –40 °C to +85 °C                      | 4.5 V to 5.5 V  |

# **DC Electrical Characteristics**

Over the Operating Range

| Parameter                       | Description                          | Test Cond                                                                           | itions                     | Min                  | <b>Typ</b> <sup>[2]</sup> | Max                   | Unit |

|---------------------------------|--------------------------------------|-------------------------------------------------------------------------------------|----------------------------|----------------------|---------------------------|-----------------------|------|

| V <sub>DD</sub>                 | Power supply                         |                                                                                     |                            | 4.5                  | 5.0                       | 5.5                   | V    |

| I <sub>DD</sub>                 | Average V <sub>DD</sub> current      | SCL toggling                                                                        | f <sub>SCL</sub> = 100 kHz | -                    | _                         | 100                   | μΑ   |

|                                 |                                      | between $V_{DD} - 0.3 V$ and $V_{SS}$ ,                                             | f <sub>SCL</sub> = 400 kHz | -                    | _                         | 200                   | μΑ   |

|                                 |                                      | other inputs $V_{SS}$ or $V_{DD} - 0.3$ V.                                          | f <sub>SCL</sub> = 1 MHz   | -                    | -                         | 400                   | μΑ   |

| I <sub>SB</sub>                 | Standby current                      | SCL = SDA = $V_{DD}$ . All other inputs $V_{SS}$ or $V_{DD}$ . Stop command issued. |                            | -                    | 4                         | 10                    | μΑ   |

| ILI                             | Input leakage current<br>(Except WP) | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                    |                            | -1                   | -                         | +1                    | μΑ   |

|                                 | Input leakage current (for WP)       | $V_{SS} \le V_{IN} \le V_{DD}$                                                      |                            | -1                   | -                         | +100                  | μΑ   |

| I <sub>LO</sub>                 | Output leakage current               | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                    |                            | -1                   | -                         | +1                    | μΑ   |

| V <sub>IH</sub>                 | Input HIGH voltage                   |                                                                                     |                            | $0.7 \times V_{DD}$  | -                         | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IL</sub>                 | Input LOW voltage                    |                                                                                     |                            | - 0.3                | -                         | 0.3 × V <sub>DD</sub> | V    |

| V <sub>OL</sub>                 | Output LOW voltage                   | I <sub>OL</sub> = 3 mA                                                              |                            | -                    | _                         | 0.4                   | V    |

| R <sub>in</sub> <sup>[3]</sup>  | Input resistance (WP)                | For $V_{IN} = V_{IL (Max)}$                                                         |                            | 40                   | _                         | -                     | kΩ   |

|                                 |                                      | For $V_{IN} = V_{IH (Min)}$                                                         |                            | 1                    | _                         | -                     | MΩ   |

| V <sub>HYS</sub> <sup>[4]</sup> | Input Hysteresis                     |                                                                                     |                            | $0.05 \times V_{DD}$ | _                         | _                     | V    |

Notes

4. These parameters are guaranteed by design and are not tested.

<sup>1.</sup> Electrostatic Discharge voltages specified in the datasheet are the JEDEC standard limits used for qualifying the device. To know the maximum value device passes for, please refer to the device qualification report available on the website. 2. Typical values are at 25 °C,  $V_{DD} = V_{DD}$  (typ). Not 100% tested. 3. The input pull-down circuit is strong (40 kΩ) when the input voltage is below  $V_{IL}$  and weak (1 MΩ) when the input voltage is above  $V_{IH}$ .

# **Data Retention and Endurance**

| Parameter       | Description    | Test condition             | Min              | Max | Unit   |

|-----------------|----------------|----------------------------|------------------|-----|--------|

| T <sub>DR</sub> | Data retention | T <sub>A</sub> = 85 °C     | 10               | -   | Years  |

|                 |                | T <sub>A</sub> = 75 °C     | 38               | -   |        |

|                 |                | T <sub>A</sub> = 65 °C     | 151              | -   |        |

| NV <sub>C</sub> | Endurance      | Over operating temperature | 10 <sup>14</sup> | -   | Cycles |

# Capacitance

| Parameter <sup>[5]</sup> | Description                  | Test Conditions                                                | Max | Unit |

|--------------------------|------------------------------|----------------------------------------------------------------|-----|------|

| C <sub>O</sub>           | Output pin capacitance (SDA) | $T_A = 25 \text{ °C}, f = 1 \text{ MHz}, V_{DD} = V_{DD}(typ)$ | 8   | pF   |

| Cl                       | Input pin capacitance        |                                                                | 6   | pF   |

### Thermal Resistance

| Parameter <sup>[5]</sup> | Description                              | Test Conditions                                                                                  | 8-pin SOIC | Unit |

|--------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------|------------|------|

| $\Theta_{JA}$            |                                          | Test conditions follow standard test methods and procedures for measuring thermal impedance, per |            | °C/W |

| $\Theta_{JC}$            | Thermal resistance<br>(junction to case) | EIA/JESD51.                                                                                      | 47         | °C/W |

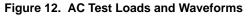

### **AC Test Loads and Waveforms**

# **AC Test Conditions**

| Input pulse levels                       | 10% and 90% of V <sub>DD</sub> |

|------------------------------------------|--------------------------------|

| Input rise and fall times                | 10 ns                          |

| Input and output timing reference levels | s0.5 × V <sub>DD</sub>         |

| Output load capacitance                  | 100 pF                         |

Note 5. These parameters are guaranteed by design and are not tested.

# **AC Switching Characteristics**

### Over the Operating Range

| Parameter [6]                   |                      |                                                |     |      |     |     |      |      |      |

|---------------------------------|----------------------|------------------------------------------------|-----|------|-----|-----|------|------|------|

| Cypress<br>Parameter            | Alt.<br>Parameter    | Description                                    |     | Max  | Min | Max | Min  | Мах  | Unit |

| f <sub>SCL</sub> <sup>[7]</sup> |                      | SCL clock frequency                            | -   | 0.1  | -   | 0.4 | -    | 1.0  | MHz  |

| t <sub>SU; STA</sub>            |                      | Start condition setup for repeated Start       | 4.7 | 1    | 0.6 | -   | 0.25 | -    | μs   |

| t <sub>HD;STA</sub>             |                      | Start condition hold time                      | 4.0 | 1    | 0.6 | -   | 0.25 | -    | μs   |

| t <sub>LOW</sub>                |                      | Clock LOW period                               | 4.7 | 1    | 1.3 | -   | 0.6  | -    | μs   |

| t <sub>HIGH</sub>               |                      | Clock HIGH period                              | 4.0 | 1    | 0.6 | -   | 0.4  | -    | μs   |

| t <sub>SU;DAT</sub>             | t <sub>SU;DATA</sub> | Data in setup                                  | 250 | 1    | 100 | -   | 100  | -    | ns   |

| t <sub>HD;DAT</sub>             | t <sub>HD;DATA</sub> | Data in hold                                   | 0   | 1    | 0   | -   | 0    | -    | ns   |

| t <sub>DH</sub>                 |                      | Data output hold (from SCL @ V <sub>IL</sub> ) | 0   | _    | 0   | -   | 0    | -    | ns   |

| t <sub>R</sub> <sup>[8]</sup>   | t <sub>r</sub>       | Input rise time                                | -   | 1000 | -   | 300 | -    | 300  | ns   |

| t <sub>F</sub> <sup>[8]</sup>   | t <sub>f</sub>       | Input fall time                                | -   | 300  | -   | 300 | -    | 100  | ns   |

| t <sub>SU;STO</sub>             |                      | STOP condition setup                           | 4.0 | _    | 0.6 | _   | 0.25 | _    | μs   |

| t <sub>AA</sub>                 | t <sub>VD;DATA</sub> | SCL LOW to SDA Data Out Valid                  | -   | 3    | I   | 0.9 | -    | 0.55 | μs   |

| t <sub>BUF</sub>                |                      | Bus free before new transmission               | 4.7 | -    | 1.3 | _   | 0.5  | -    | μs   |

| t <sub>SP</sub>                 |                      | Noise suppression time constant on SCL, SDA    | _   | 50   |     | 50  | -    | 50   | ns   |

Figure 13. Read Bus Timing Diagram

#### Notes

- Test conditions assume signal transition time of 10 ns or less, timing reference levels of  $V_{DD}/2$ , input pulse levels of 0 to  $V_{DD}(typ)$ , and output loading of the specified  $I_{OL}$  and load capacitance shown in Figure 12. The speed-related specifications are guaranteed characteristic points along a continuous curve of operation from DC to  $f_{SCL}$  (max). 6.

- 7.

- 8. These parameters are guaranteed by design and are not tested.

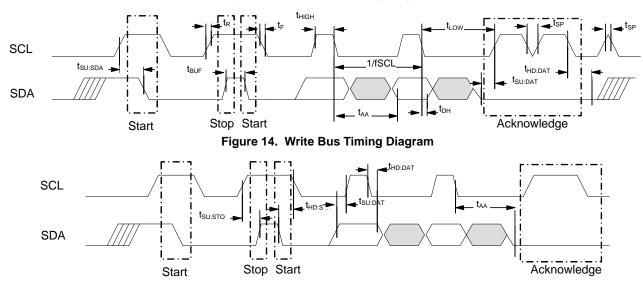

# **Power Cycle Timing**

## Over the Operating Range

| Parameter                          | Description                                                        | Min | Max | Unit |

|------------------------------------|--------------------------------------------------------------------|-----|-----|------|

| t <sub>PU</sub>                    | Power-up V <sub>DD</sub> (min) to first access (START condition)   | 1   | -   | ms   |

| t <sub>PD</sub>                    | Last access (STOP condition) to power-down (V <sub>DD</sub> (min)) | 0   | -   | μs   |

| t <sub>VR</sub> <sup>[9, 10]</sup> | V <sub>DD</sub> power-up ramp rate                                 | 30  | _   | µs/V |

| t <sub>VF</sub> <sup>[9, 10]</sup> | V <sub>DD</sub> power-down ramp rate                               | 30  | _   | µs/V |

## Figure 15. Power Cycle Timing

Notes

9. Slope measured at any point on the  $\rm V_{\rm DD}$  waveform. 10. Guaranteed by design.

# **Ordering Information**

| Ordering Code | Package<br>Diagram | Package Type | Operating<br>Range |

|---------------|--------------------|--------------|--------------------|

| FM24C16B-G    | 51-85066           | 8-pin SOIC   | Industrial         |

| FM24C16B-GTR  |                    |              |                    |

All these parts are Pb-free. Contact your local Cypress sales representative for availability of these parts.

### **Ordering Code Definitions**

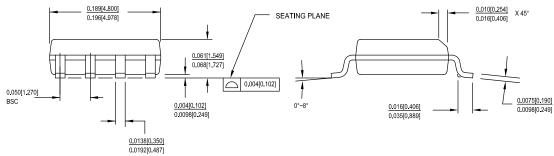

# Package Diagram

Figure 16. 8-pin SOIC (150 Mils) Package Outline, 51-85066

- 1. DIMENSIONS IN INCHES[MM] MIN. MAX.

- 2. PIN 1 ID IS OPTIONAL, ROUND ON SINGLE LEADFRAME RECTANGULAR ON MATRIX LEADFRAME

- 3. REFERENCE JEDEC MS-012

- 4. PACKAGE WEIGHT 0.07gms

| PART #  |               |  |  |  |

|---------|---------------|--|--|--|

| S08.15  | STANDARD PKG  |  |  |  |

| SZ08.15 | LEAD FREE PKG |  |  |  |

| SW8.15  | LEAD FREE PKG |  |  |  |

51-85066 \*H

# Acronyms

| Acronym          | Description                                |

|------------------|--------------------------------------------|

| ACK              | Acknowledge                                |

| CMOS             | Complementary Metal Oxide Semiconductor    |

| EIA              | Electronic Industries Alliance             |

| I <sup>2</sup> C | Inter-Integrated Circuit                   |

| I/O              | Input/Output                               |

| JEDEC            | Joint Electron Devices Engineering Council |

| LSB              | Least Significant Bit                      |

| MSB              | Most Significant Bit                       |

| NACK             | No Acknowledge                             |

| RoHS             | Restriction of Hazardous Substances        |

| R/W              | Read/Write                                 |

| SCL              | Serial Clock Line                          |

| SDA              | Serial Data Access                         |

| SOIC             | Small Outline Integrated Circuit           |

| WP               | Write Protect                              |

# **Document Conventions**

### **Units of Measure**

| Symbol | Unit of Measure |

|--------|-----------------|

| °C     | degree Celsius  |

| Hz     | hertz           |

| Kb     | kilobit         |

| kHz    | kilohertz       |

| kΩ     | kilohm          |

| MHz    | megahertz       |

| MΩ     | megaohm         |

| μΑ     | microampere     |

| μS     | microsecond     |

| mA     | milliampere     |

| ms     | millisecond     |

| ns     | nanosecond      |

| Ω      | ohm             |

| %      | percent         |

| pF     | picofarad       |

| V      | volt            |

| W      | watt            |

# **Document History Page**

| C | Document | Title: | FM24C16B | 16-Kbit | (2K × 8) | Serial (I <sup>2</sup> | C) F-RAM |

|---|----------|--------|----------|---------|----------|------------------------|----------|

|   |          |        |          |         |          |                        |          |

| Rev. | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 3902082 | GVCH               | 02/25/2013         | New spec.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *A   | 3924523 | GVCH               | 03/07/2013         | Changed t <sub>PU</sub> spec value from 10 ms to 1 ms.                                                                                                                                                                                                                                                                                                                                                                                                         |

| *B   | 3996669 | GVCH               | 05/13/2013         | Added Appendix A - Errata for FM24C16B.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *C   | 4045469 | GVCH               | 06/30/2013         | All errata items are fixed and the errata is removed.                                                                                                                                                                                                                                                                                                                                                                                                          |

| *D   | 4283418 | GVCH               | 02/19/2014         | Converted to Cypress standard format.<br>Changed endurance value from 10 <sup>12</sup> to 10 <sup>14</sup> cycles.<br>Updated Maximum Ratings:<br>- Removed Moisture Sensitivity Level (MSL).<br>- Added junction temperature and latch up current.<br>Added Input leakage current (I <sub>LI</sub> ) for WP.<br>Updated Data Retention and Endurance.<br>Added Thermal Resistance.<br>Removed Package Marking Scheme (top mark).<br>Completing Sunset Review. |

| *E   | 4272607 | GVCH               | 03/11/2014         | Typo fixed (AC Switching Characteristics): Parameter spec unit changed from ns to µs<br>— t <sub>SU:STA</sub> , t <sub>HD:STA</sub> , t <sub>LOW</sub> , t <sub>HIGH</sub> , t <sub>SU:STO</sub> , t <sub>AA</sub> and t <sub>BUF</sub>                                                                                                                                                                                                                        |

| *F   | 4343617 | GVCH               | 04/21/2014         | Typo fixed (DC Electrical Characteristics): $V_{OL}$ parameter spec unit changed from C to V.                                                                                                                                                                                                                                                                                                                                                                  |

| *G   | 4566147 | GVCH               | 11/10/2014         | Updated Functional Description:<br>Added "For a complete list of related documentation, click here." at the end.                                                                                                                                                                                                                                                                                                                                               |

| *H   | 4782742 | GVCH               | 06/01/2015         | Updated Ordering Information:<br>Fixed Typo (Replaced "001-85066" with "51-85066" in "Package Diagram'<br>column).<br>Updated Package Diagram:<br>spec 51-85066 – Changed revision from *F to *G.<br>Updated to new template.                                                                                                                                                                                                                                  |

| *    | 4874535 | ZSK / PSR          | 08/06/2015         | Updated Maximum Ratings:<br>Removed "Maximum junction temperature".<br>Added "Maximum accumulated storage time".<br>Added "Ambient temperature with power applied".                                                                                                                                                                                                                                                                                            |

| *J   | 5606370 | GVCH               | 01/27/2017         | Updated Maximum Ratings:<br>Updated Electrostatic Discharge Voltage (in compliance with AEC-Q100<br>standard):<br>Changed value of "Human Body Model" from 4 kV to 2 kV.<br>Changed value of "Charged Device Model" from 1.25 kV to 500 V.<br>Removed "Machine Model" related information.<br>Updated Package Diagram:<br>spec 51-85066 – Changed revision from *G to *H.<br>Updated to new template.<br>Completing Sunset Review.                             |

| *K   | 5700082 | GVCH               | 04/19/2017         | Updated Maximum Ratings:<br>Added Note 1 and referred the same note in "Electrostatic Discharge Voltage"<br>Updated to new template.                                                                                                                                                                                                                                                                                                                           |

# Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

### **PSoC<sup>®</sup> Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 001-84450 Rev. \*K

<sup>©</sup> Cypress Semiconductor Corporation, 2013–2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and other sont, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress parents you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to any Unintended Uses of Cypress products.