# **Integrated Device Technology**

# 89HT0816P Signal Retimers

16 Channel Signal Retimers for 8.0Gbps, 5.0Gbps and 2.5Gbps PCle®

POWER MANAGEMENT | ANALOG & RF | INTERFACE & CONNECTIVITY | CLOCKS & TIMING | MEMORY & LOGIC | TOUCH & USER INTERFACE | VIDEO & DISPLAY | AUDIO

#### **FEATURES**

### • High Performance Retimer

- Eliminates random input jitter

- Eliminates deterministic ISI jitter

- Compensates for PCB trace and cable attenuations

- Performance and power tunable for each data rate

- Wide swing, transmit driver offers up to 8dB of transmit deemphasis to meet the needs of the most challenging of backplanes

- Multi-stage equalizer: CTLE and 5 tap DFE

- Fast acquisition PLL for LOs exit

- SERDES Rx eye generation (on-chip)

## • PCIe Standards and Compatibility

- PCI Express Base Specification 3.0 compliant

- PCI Express Base Specification 2.1 compliant

## • Power Management

- Low power

- Supports the following optional PCI Express features

- LOs ASPM

- L1 ASPM

## • Hot Plug Support

#### • SerDes Power Savings

- Supports low swing (half-swing) SerDes operation

- SerDes associated with unused lanes are placed in a low power state automatically

# • Link Configurability

- Links can be configured with 1x8, 1x4, 1x1, 2x4, 2x1

- Automatic per port link width negotiation (e.g., a x8 port can link train to x8, x4, or x1)

- Per-lane SerDes configuration

- De-emphasis, receive equalization, drive strength

#### • Clocking

- Uses standard 100 MHz PCle reference clock

- SSCLK (Spread Spectrum Clocking) supported with common clock configuration

- Non-SSCLK supported with common and non-common clock configuration

## • I<sup>2</sup>C Interface

- Dedicated master interface

- External EEPROM configuration loading

- Dedicated slave interface

- Configuration loading

- Writing new or initial image into external EEPROM

- Expose internal global CSR space to system controller

# Reliability, Availability and Serviceability (RAS)

- Physical layer error checking and accounting

- End-to-end data path parity protection

- Checksum Serial EEPROM content protected

## • Test and Debug

- Per link/lane error diagnostic registers

- All registers accessible from I<sup>2</sup>C, or JTAG port

- SerDes test modes

- Supports IEEE 1149.6 AC JTAG and IEEE 1149.1 JTAG

- Several loopback modes

- Packaged in a 15x15mm, 196-pin CABGA, 1mm ball spacing

# **General Description**

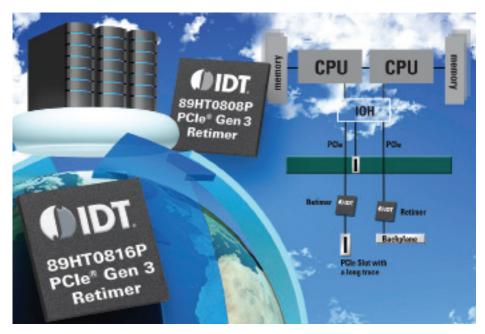

The 89HT0816P is a Signal Retimer/Conditioners used to improve signal integrity for enhancing system performance and reliability across long PCB traces or cables. It removes both random and deterministic jitter from the input signal eliminating inter-symbol interference, and resets the output jitter budget. It provides sixteen differential, 8Gbps PCIe Express® 3.0 channels, supporting up to 8 full lanes. It also fully support PCIe Express 5Gbps and 2.5Gbps features. The T0816P is targeted to meet the high-performance needs of PCIe® Gen 3/2/1 applications.

## **Applications**

IDT's Retimer products fit into server, storage, and blade products, as well as Consumer Electronics and Communications applications.

# **Improving Signal Integrity with IDT Retimers**

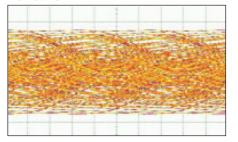

## No Retimer

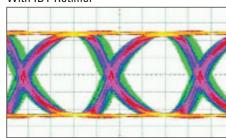

With IDT Retimer

Example Eye diagram FR4 and PRBS patterns

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDTs sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not quarameted to perform the same way when installation in such representations and the operating parameters of the described products are determined in the independent state and are not quarameted to perform the same way when installation in such representations when the products are indicated by the indication in the indication of the products are indicated by the indication in the indication of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties. IDTs products are not intended for use in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such aramened does not an express, written are apresses, written are apresses, written are apresses, to the reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such aramened does not convey any license under intellectual property rights of IDT or any third parties. IDTs

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

PB\_89HT0816P\_REVA1110