# ISL28113/14SOT23EVAL1Z Evaluation Board User's Guide

#### Introduction

The ISL28113/14SOT23EVAL1Z evaluation board is a design platform containing all the circuitry needed to characterize critical performance parameters of the ISL28113 and ISL28114 operational amplifiers, using a variety of user defined test circuits.

The ISL28113 and ISL28114 CMOS operational amplifiers feature low power consumption, low input bias current, and rail-to-rail input and output drive capability. They are designed to operate with a single lithium cell or two Ni Cd batteries.

#### **Reference Documents**

- ISL28113 Data Sheet, FN6728

- ISL28114 Data Sheet, <u>FN6800</u>

#### **Evaluation Board Key Features**

The ISL28113/14SOT23EVAL1Z is designed to enable the IC to operate from a single supply,  $\pm 2.4$ VDC to  $\pm 5.5$ VDC or from split supplies,  $\pm 1.2$ VDC to  $\pm 2.75$ V. The board is configured for a single op amp connected for differential input with a closed loop gain of 10. A single external reference voltage (VREF) pin and provisions for a user-selectable voltage divider - filter are included.

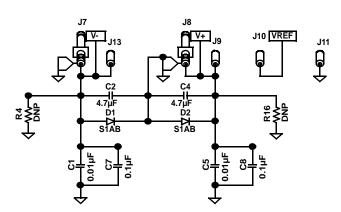

### **Power Supplies (Figure 1)**

External power connections are made through the +V, -V and Ground connections on the evaluation board. For single supply operation, the -V and Ground pins are tied together to the power supply negative terminal. For split supplies, +V and -V terminals connect to their respective power supply terminals. De-coupling capacitors C2 and

FIGURE 1. POWER SUPPLY CIRCUIT

C4 can connect to ground through R4 and R16 resistors. These resistors are not populated, but can be used to provide additional power supply filtering. Four additional capacitors, C1 and C5 (0.01 $\mu$ F) and C7 and C8 (0.1 $\mu$ F) are connected close to the part to filter out high frequency noise. Anti-reverse diodes D1 and D2 protect the circuit in the case of accidental polarity reversal.

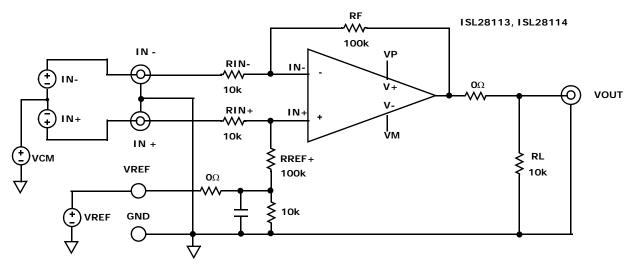

## Amplifier Configuration (Figure 2)

The schematic of the op-amp with the components supplied is shown in Figure 2. The circuit implements a differential input amp with a closed loop gain of 10. The circuit can operate from a single supply or from dual supplies. The VREF pin can be connected to ground to establish a ground referenced input for split supply operation, or can be externally set to any reference level for single supply operation. **Note:** VREF should not be left floating.

FIGURE 2. BASIC AMPLIFIER CONFIGURATION

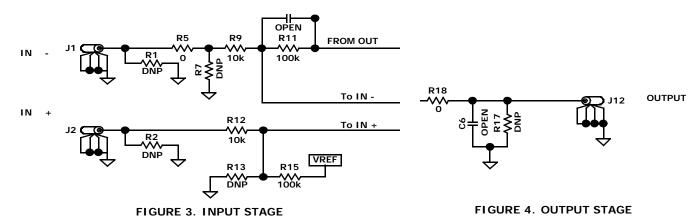

## User-selectable Options (Figures 3 and 4)

Component pads are included to enable a variety of user-selectable circuits to be added to the amplifier inputs, the VREF input, the output and the amplifier feedback loop.

A voltage divider and filter option (Figure 3) can be added to establish a power supply-tracking common mode reference at the VREF input. The inverting and

non-inverting inputs have additional resistor placements for adding input attenuation, or to establish input DC offsets through the VREF pin.

The output (Figure 4) has additional resistor and capacitor placements for loading.

NOTE: Operational amplifiers are sensitive to output capacitance and may oscillate. In the event of oscillation, reduce output capacitance by using shorter cables, or add a resistor in series with the output.

### ISL28113/14SOT23EVAL1Z Components Parts List

| DEVICE #                                          | DESCRIPTION                                          | COMMENTS                                    |

|---------------------------------------------------|------------------------------------------------------|---------------------------------------------|

| C2, C4                                            | CAP-TANTALUM, SMD, 4.7µF, 50V, 10%, LOW ESR, ROHS    | Power Supply Decoupling                     |

| C1, C5                                            | CAP, SMD, 0603, 0.01µF, 25V, 10%, X7R, ROHS          | Power Supply Decoupling                     |

| C7, C8                                            | CAP, SMD, 0603, 0.1µF, 25V, 10%, X7R, ROHS           | Power Supply Decoupling                     |

| C3, C6                                            | CAP, SMD, 0603, DNP-PLACE HOLDER, ROHS               | User Selectable Capacitors - not populated  |

| D1, D2                                            | DIODE-RECTIFIER, SMD, SOD-123, 2P, 40V, 0.5A, ROHS   | Reverse Power Protection                    |

| U1 (ISL28113EVAL1Z)                               | ISL28113FHZ-T7, IC-RAIL-TO-RAIL OP AMP, SOT-23, ROHS |                                             |

| U1 (ISL28114EVAL1Z)                               | ISL28114FHZ-T7, IC-RAIL-TO-RAIL OP AMP, SOT-23, ROHS |                                             |

| R1-R4, R6-R8, R10, R13,<br>R14, R16, R17, R19-R21 | RESISTOR, SMD, 0603, 0.1%, MF, DNP-PLACE HOLDER      | User Selectable Resistors - not populated   |

| R5, R18                                           | RES, SMD, 0603, 0Ω, 1/10W, TF, ROHS                  | 0Ω User Selectable Resistors                |

| R9, R12                                           | RES, SMD, 0603, 10k, 1/10W, 1%, TF, ROHS             | Gain and Other User Selectable<br>Resistors |

| R11, R15                                          | RES, SMD, 0603, 100k, 1/10W, 1%, TF, ROHS            | Gain Resistors                              |

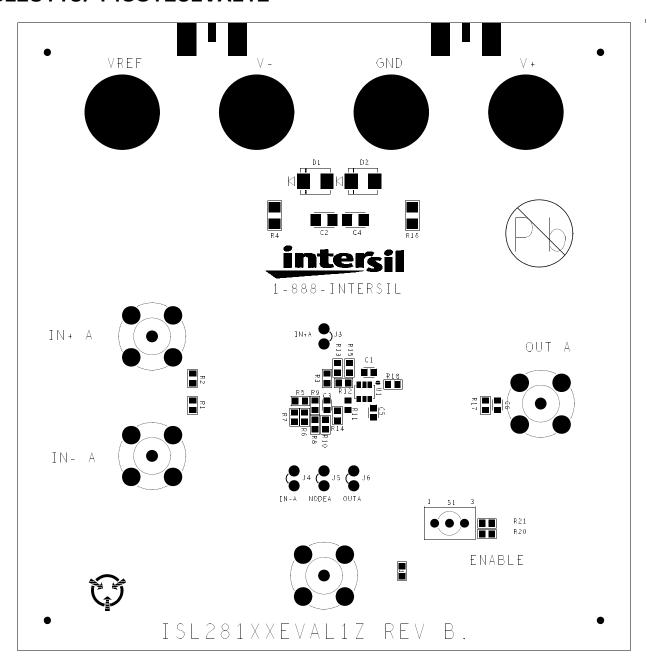

### ISL28113/14SOT23EVAL1Z

FIGURE 5. TOP VIEW

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

4

## ISL28113/14SOT23EVAL1Z Schematic Diagram 4.7µF D1 D1 S1AB 4.7µF D2 DI S1AB IN+ NODE OUT R10 СЗ OPEN R11 OUTPUT -**VVV**-100k IN U1 GENERIC 5 IN + R12 **VVV** 10k 0.01µF SOT23\_6 0.01µF R15 VREF R13 DNP **ENABLE** R20 NP R19 WV DNP

FIGURE 6.

\_\_1 DNP

R21 DNP