# RENESAS

#### NOT RECOMMENDED FOR NEW DESIGNS RECOMMENDED REPLACEMENT PART EL5171

# EL2141

# 150MHz Differential Twisted Pair Driver

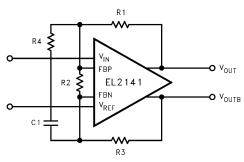

The EL2141 is a very high bandwidth amplifier whose output is in differential form, and is thus primarily targeted for applications such as driving twisted pair lines, or any application where common mode injection is likely to occur. The input signal can be in either single-ended or differential form, but the output is always in differential form.

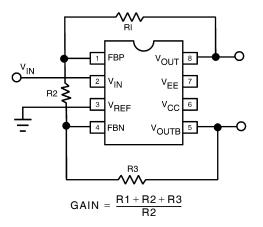

On the EL2141, two feedback inputs provide the user with the ability to set the device gain, (stable at minimum gain of two).

The output common mode level is set by the reference pin (V<sub>REF</sub>), which has a -3dB bandwidth of over 100MHz. Generally, this pin is grounded, but it can be tied to any voltage reference.

The transmission of ADSL/HDSL signals requires very low distortion amplification, so this amplifier was designed with this as a primary goal. The actual signal distortion levels depend upon input and output signal amplitude, as well as the output load impedance. (See distortion data inside.)

Both outputs ( $V_{OUT}$ ,  $V_{OUTB}$ ) are short circuit protected to withstand temporary overload condition.

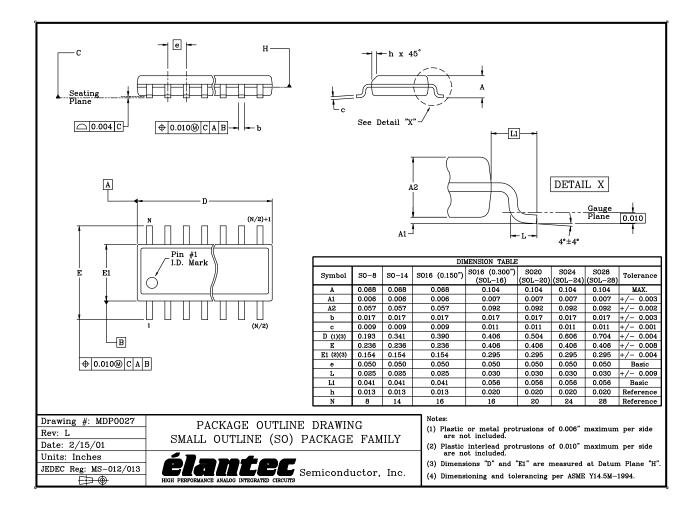

| PART<br>NUMBER               | PACKAGE                 | TAPE &<br>REEL | PKG. DWG. # |

|------------------------------|-------------------------|----------------|-------------|

| EL2141CS                     | 8-pin SOIC              | -              | MDP0027     |

| EL2141CS-T7                  | 8-pin SOIC              | 7"             | MDP0027     |

| EL2141CS-T13                 | 8-pin SOIC              | 13"            | MDP0027     |

| EL2141CSZ<br>(See Note)      | 8-pin SOIC<br>(Pb-free) | -              | MDP0027     |

| EL2141CSZ-T7<br>(See Note)   | 8-pin SOIC<br>(Pb-free) | 7"             | MDP0027     |

| EL2141CSZ-<br>T13 (See Note) | 8-pin SOIC<br>(Pb-free) | 13"            | MDP0027     |

## **Ordering Information**

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Features

- · Fully differential inputs, outputs, and feedback

- Differential input range ±2.3V

- 150MHz 3dB bandwidth

- 800V/µs slew rate

- -55dB distortion at 3MHz

- -75dB distortion at 100kHz

- ±5V supplies or +6V single supply

- 50mA minimum output current

- Output swing (200 $\Omega$  load) to within 1.5V of supplies (14V\_{PKPK} differential)

- Low power-11mA typical supply current

- Pb-free available (RoHS compliant)

### Applications

- Twisted pair driver

- Differential line driver

- VGA over twisted pair

- ADSL/HDSL driver

- Single ended to differential amplification

- Transmission of analog signals in a noisy environment

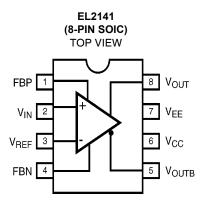

#### Pinout

DATASHEET

FN7048 Rev 1.00 February 11, 2005

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| Supply Voltage V <sub>S</sub> + and GND |  |

|-----------------------------------------|--|

| Maximum Output Current ±60mA            |  |

| Storage Temperature Range65°C to +150°C |  |

| Operating Junction Temperature          |  |

$\label{eq:second} \begin{array}{l} \mbox{Recommended Operating Temperature} & \dots & -40^\circ \mbox{C to } 85^\circ \mbox{C} \\ \mbox{V}_{IN}, \mbox{V}_{INB}, \mbox{V}_{REF} & \dots & \dots & \mbox{V}_{EE} + 0.8 \mbox{V} \mbox{(MIN) to } \mbox{V}_{CC} - 0.8 \mbox{V} \mbox{(MAX)} \\ \mbox{V}_{IN} - \mbox{V}_{INB} & \dots & \dots & \mbox{\pm} 5 \mbox{V} \end{array}$

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

#### **DC Electrical Specifications** $V_{CC} = +5V$ , $V_{EE} = -5V$ , $T_A = 25^{\circ}C$ , $V_{IN} = 0V$ , $R_L = 200$ , unless otherwise specified.

| PARAMETER              | DESCRIPTION                                                                      | MIN  | TYP  | MAX  | UNITS  |

|------------------------|----------------------------------------------------------------------------------|------|------|------|--------|

| V <sub>SUPPLY</sub>    | Supply Operating Range (V <sub>CC</sub> -V <sub>EE</sub> )                       | ±3.0 | ±5.0 | ±6.3 | V      |

| IS                     | Power Supply Current (No Load)                                                   |      | 11   | 14   | mA     |

| V <sub>OS</sub>        | Input Referred Offset Voltage                                                    | -25  | 10   | 40   | mV     |

| I <sub>IN</sub>        | Input Bias Current (VIN, VINB, VREF)                                             | -20  | 6    | 20   | μA     |

| Z <sub>IN</sub>        | Differential Input Impedance                                                     |      | 400  |      | kΩ     |

| V <sub>DIFF</sub>      | Differential Input Range                                                         | ±2.0 | ±2.3 |      | V      |

| A <sub>VOL</sub>       | Open Loop Voltage Gain                                                           |      | 75   |      | dB     |

| V <sub>OUT</sub> (200) | Output Voltage Swing (200 $\Omega$ load, V_OUT to V_OUTB)                        | ±3.4 | ±3.6 |      | V      |

| V <sub>OUT</sub> (100) | Output Voltage Swing (100 $\Omega$ Load, V <sub>OUT</sub> to V <sub>OUTB</sub> ) | ±2.9 | ±3.1 |      | V      |

| V <sub>N</sub>         | Input Referred Voltage Noise                                                     |      | 36   |      | nV/√Hz |

| V <sub>REFOS</sub>     | Output Offset Relative to V <sub>REF</sub>                                       | -60  | -25  | +60  | mV     |

| PSRR                   | Power Supply Rejection Ratio                                                     | 60   | 70   |      | dB     |

| I <sub>OUT</sub> (min) | Minimum Output Current                                                           | 50   | 60   |      | mA     |

| R <sub>OUT</sub>       | (V <sub>OUT</sub> = V <sub>OUTB</sub> = 0V) Output Impedance                     |      | 0.1  |      | Ω      |

#### AC Electrical Specifications $V_{CC} = +5V$ , $V_{EE} = -5V$ , $T_A = 25^{\circ}C$ , $V_{IN} = 0V$ , $R_{LOAD} = 200$ , unless otherwise specified

| PARAMETER                 | DESCRIPTION                     | MIN | ТҮР  | MAX | UNITS |

|---------------------------|---------------------------------|-----|------|-----|-------|

| BW(-3dB)                  | -3dB Bandwidth (@ gain of 2)    |     | 150  |     | MHz   |

| SR                        | Differential Slewrate           |     | 800  |     | V/µs  |

| Tstl                      | Settling Time to 1%             |     | 15   |     | ns    |

| GBW                       | Gain Bandwidth Product          |     | 400  |     | MHz   |

| V <sub>REFBW</sub> (-3dB) | V <sub>REF</sub> -3dB Bandwidth |     | 130  |     | MHz   |

| V <sub>REFSR</sub>        | V <sub>REF</sub> Slewrate       |     | 100  |     | V/µs  |

| THDf1                     | Distortion at 100kHz (Note 1)   |     | -75  |     | dB    |

| dP                        | Differential Phase @ 3.58MHz    |     | 0.16 |     | 0     |

| dG                        | Differential Gain @ 3.58MHz     |     | 0.24 |     | %     |

NOTE:

1. Distortion measurement quoted for V<sub>OUT</sub>–V<sub>OUTB</sub> = 12V pk-pk, R<sub>LOAD</sub> = 200 $\Omega$ , V<sub>GAIN</sub> = 8

# **Pin Descriptions**

|        | -                 |                                                                                                                                                                                   |

|--------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EL2141 | PIN NAME          | FUNCTION                                                                                                                                                                          |

| 2      | V <sub>IN</sub>   | Non-inverting Input                                                                                                                                                               |

| 1      | FBP               | Non-inverting Feedback Input. Resistor R1 must be Connected from this Pin to V <sub>OUT</sub> .                                                                                   |

| 4      | FBN               | Inverting Feedback Input. Resistor R3 must be Connected from this pin to VOUTB.                                                                                                   |

| 3      | V <sub>REF</sub>  | Output Common-mode Control. The Common-mode Voltage of $V_{OUT}$ and $V_{OUTB}$ will Follow the Voltage on this Pin. Note that on the EL2141, this pin is also the $V_{INB}$ pin. |

| 5      | V <sub>OUTB</sub> | Inverting Output                                                                                                                                                                  |

| 6      | V <sub>CC</sub>   | Positive Supply                                                                                                                                                                   |

| 7      | V <sub>EE</sub>   | Negative Supply                                                                                                                                                                   |

| 8      | V <sub>OUT</sub>  | Non-inverting Output                                                                                                                                                              |

|        |                   |                                                                                                                                                                                   |

# **Typical Performance Curves**

+6

+5

+4

+3

+2

+1

0

GAIN (dB)

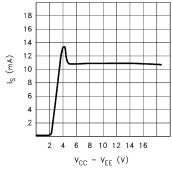

FIGURE 1. IS vs SUPPLY VOLTAGE

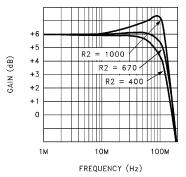

FIGURE 2. FREQUENCY RESPONSE vs RESISTOR R2 (GAIN = 2)

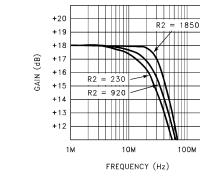

FIGURE 4. FREQUENCY RESPONSE vs RESISTOR R2 (GAIN = 8)

1M 10M 100M FREQUENCY (Hz)

-40

25

90 -

150

FIGURE 3. FREQUENCY RESPONSE vs TEMPERATURE

## Typical Performance Curves (Continued)

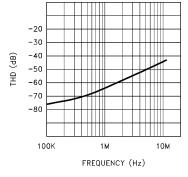

FIGURE 5. DISTORTION vs FREQUENCY (GAIN = 6, R<sub>LOAD</sub> = 200 $\Omega$ ) V<sub>IN</sub> = 2V<sub>PK-PK</sub>

## Applications Information

#### Choice of Feedback Resistor

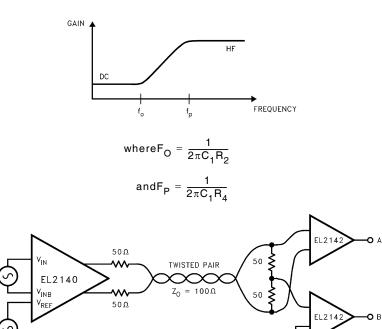

There is little to be gained from choosing resistor R2 values below  $400\Omega$  and, in fact, it would only result in increased power dissipation and signal distortion. Above  $400\Omega$ , the bandwidth response will develop some peaking (for a gain of two), but substantially higher resistor R2 values may be used for higher voltage gains, such as up to  $2k\Omega$  at a gain of eight before peaking will develop. R1 and R3 are selected as needed to set the voltage gain, and while R1 = R3 is suggested, the gain equation above holds for any values (see distortion for further suggestions).

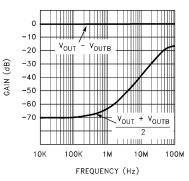

#### Capacitance Considerations

As with many high bandwidth amplifiers, the EL2141 prefers not to drive highly capacitive loads. It is best if the capacitance on  $V_{OUT}$  and  $V_{OUTB}$  is kept below 10pF if the user does not want gain peaking to develop.

In addition, on the EL2141, the two feedback nodes FBP and FBN should be laid out so as to minimize stray capacitance, else an additional pole will potentially develop in the response with possible gain peaking.

FIGURE 6. OUTPUT SIGNAL AND COMMON MODE SIGNAL vs FREQUENCY

The amount of capacitance tolerated on any of these nodes in an actual application will also be dependent on the gain setting and the resistor values in the feedback network.

#### **Distortion Considerations**

The harmonics that these amplifiers will potentially produce are the 2nd, 3rd, 5th, and 6th. Their amplitude is application dependent. All other harmonics should be negligible by comparison. Each should be considered separately:

**H2** The second harmonic arises from the input stage, and the lower the applied differential signal amplitude, the lower the magnitude of the second harmonic. For practical considerations of required output signal and input noise levels, the user will end up choosing a circuit gain. Referring to Figure 1, it is best if the voltage at the negative feedback node tracks the V<sub>REF</sub> node, and the voltage at the positive feedback node tracks the V<sub>IN</sub> node respectively. This would theoretically require that R1 + R2 = R3, although the lowest distortion is found at about R3 = R1 + (0.7\*R2). With this arrangement, the second harmonic should be suppressed well below the value of the third harmonic.

H3 The third harmonic should be the dominant harmonic and is primarily affected by output load current which, of course, is unavoidable. However, this should encourage the user not to waste current in the gain setting resistors, and to use values that consume only a small proportion of the load current, so long as peaking does not occur. The more load current, the worse the distortion, but depending on the frequency, it may be possible to reduce the amplifier gain so that there is more internal gain left to cancel out any distortion.

**H5** The fifth harmonic should always be below the third, and will not become significant until heavy load currents are drawn. Generally, it should respond to the same efforts applied to reducing the third harmonic.

**H6** The sixth harmonic should not be a problem and is the result of poor power supply decoupling. While 100nF chip capacitors may be sufficient for some applications, it would be insufficient for driving full signal swings into a twisted pair line at 100kHz. Under these conditions, the addition of  $4.7\mu$ F tantalum capacitors would cure the problem.

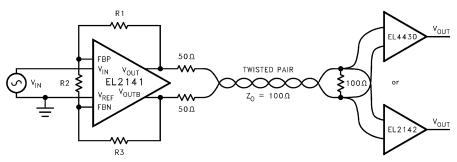

# Typical Applications Circuits

FIGURE 7. TYPICAL TWISTED PAIR APPLICATION

FIGURE 8. DIFFERENTIAL LINE DRIVER WITH EQUALIZATION

$DCGain = \frac{R1 + R2 + R3}{R2}(SeeFigure9)$

$(HF)Gain = \frac{R1 + (R2/R4) + R3}{(R2/R4)}(SeeFigure9)$

FIGURE 9. DUAL SIGNAL TRANSMISSION CIRCUIT

## SOIC Package Outline Drawing

NOTE: The package drawing shown here may not be the latest version. To check the latest revision, please refer to the Intersil website at <<u>http://www.intersil.com/design/packages/index.asp></u>

© Copyright Intersil Americas LLC 1995-2005. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com