### NOT RECOMMENDED FOR NEW DESIGNS RECOMMENDED REPLACEMENT PART ISL29125

DATASHEET

ISL29120

Digital Output, Low Power, Red, Green, and Blue Color Light Sensor

FN8314 Rev 0.00 May 29, 2012

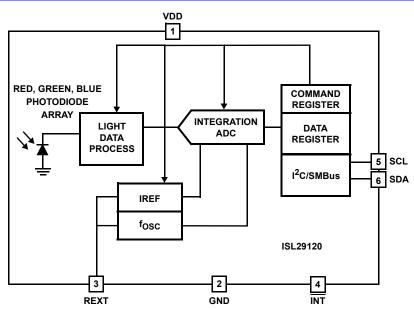

The ISL29120 is a low power, high sensitivity, integrated red, green, and blue light sensor with an  $\rm I^2C$  (SMBus Compatible) interface. Its state-of-the-art photodiode array provides an accurate red, green and blue spectral response. The ADC is capable of rejecting 50Hz and 60Hz flicker caused by artificial light sources. A selectable range allows the user to optimize sensitivity suitable for the specific application.

ISL29120 is optimized for sensing red, green and blue light components in an non-infrared environment (fluorescent and LED lighting). When operating in infrared rich environments, an external IR blocking filter should be used for accurate measurements.

In normal continuous operation, the ISL29120 power consumption is  $70\mu A$ , which reduces to  $0.3\mu A$  in power down mode. In polling mode, the auto-power-down function shuts down most of the device after each ADC conversion.

The ISL29120 supports both hardware and software interrupts. The interrupt thresholds are user programmable. The Interrupt persistency feature reduces false trigger notification.

Designed to operate on supplies from 2.25V to 3.3V and  $I^2C$  supply from 1.7V to 3.6V, the ISL29120 is specified for operation over the -40°C to +85°C ambient temperature range.

### **Features**

- 70µA Operating Current, 0.3µA Shutdown Current

- I<sup>2</sup>C (SMBus Compatible) Output

- Programmable 4, 8, 12 or 16-bits ADC Resolution

- · Programmable Interrupt Windows

- . Two Optical Sensitivity Ranges

- 2.25 to 3.63V Operating Power Supply

- 1.7V to 3.6V Supply for I<sup>2</sup>C Interface

- 2.0mmx2.1mmx0.7mm 6 Ld ODFN Package

# **Applications**

- Smart Phone, PDA, GPS, Tablet PCs, LCD-TVs, Digital Picture Frames, Digital Cameras

- . Dynamic Display Color Balancing

- · Printer Color Enhancement

- Industrial/Commercial LED Lighting Color Management

- · Ambient Light Color Detection/Correction

- . OLED Display Aging Compensation

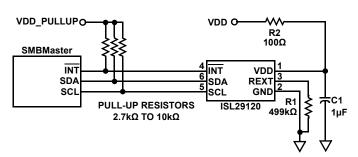

FIGURE 1. TYPICAL APPLICATION

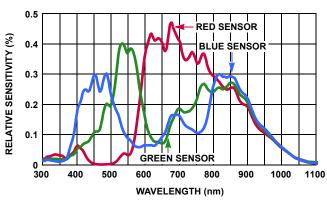

FIGURE 2. RELATIVE SPECTRAL SENSITIVITY FOR RED, GREEN AND BLUE SENSE MODES

FIGURE 3. BLOCK DIAGRAM

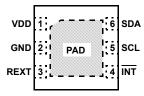

# **Pin Configuration**

ISL29120 (6 LD ODFN) TOP VIEW

\*EXPOSED PAD (0) CAN BE CONNECTED TO GND OR ELECTRICALLY ISOLATED

# **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | TEMP.<br>RANGE<br>(°C) | PACKAGE<br>Tape and Reel<br>(Pb-Free) | PKG.<br>DWG.# |

|--------------------------------|------------------------|---------------------------------------|---------------|

| ISL29120IR0Z-T7                | -40 to +85             | 6 Ld ODFN                             | L6.2x2.1      |

| ISL29120IROZ-EVALZ             | Evaluation Bo          | ard                                   |               |

#### NOTES:

- 1. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL29120</u>. For more information on MSL please see tech brief <u>TB477</u>.

# **Pin Descriptions**

| PIN NUMBER | PIN NAME | DESCRIPTION                                                                                                 |                                         |  |  |  |

|------------|----------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|

| 0          | PAD      | Exposed thermal pad, connected to gro                                                                       | posed thermal pad, connected to ground. |  |  |  |

| 1          | VDD      | Positive power supply, 2.25V to 3.63V.                                                                      |                                         |  |  |  |

| 2          | GND      | Ground pin.                                                                                                 | round pin.                              |  |  |  |

| 3          | REXT     | onnect to ground through a 499kΩ resistor.                                                                  |                                         |  |  |  |

| 4          | ĪNT      | nterrupt Output, Open Drain                                                                                 |                                         |  |  |  |

| 5          | SCL      | <sup>2</sup> C serial clock Input SCL and SDA are Open Drain. Pull-up to 1.7V min to 3.63V max power supply |                                         |  |  |  |

| 6          | SDA      | <sup>2</sup> C serial data Input/Output                                                                     |                                         |  |  |  |

### **Absolute Maximum Ratings** (T<sub>A</sub> = +25°C)

| V <sub>DD</sub> , Supply Voltage between V <sub>DD</sub> and GND | 4.0V         |

|------------------------------------------------------------------|--------------|

| I <sup>2</sup> C Bus (SCL, SDA) Pin Voltage                      | 0.2V to 4.0V |

| I <sup>2</sup> C Bus (SCL, SDA) Pin Current                      | <10mA        |

| REXT Pin Voltage                                                 |              |

| ESD Rating                                                       |              |

| Human Body Model                                                 | 2kV          |

#### **Thermal Information**

| Thermal Resistance (Typical)                 | $\theta_{JA}(^{\circ}C/W)$ |

|----------------------------------------------|----------------------------|

| 6 Ld ODFN Package (Note 4)                   | 62                         |

| Maximum Die Temperature                      | +90°C                      |

| Storage Temperature                          | 0°C to +100°C              |

| Operating Temperature                        | 40°C to +85°C              |

| Pb-Free Reflow Profile                       | . see link below           |

| hatter / / / / / / / / / / / / / / / / / / / |                            |

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

### $\textbf{Electrical Specifications} \quad \text{$V_{DD}$ = $3V$, $T_{A}$ = $+25\,^{\circ}$C, $R_{EXT}$ = $499$$$k$\Omega \ 1\% \ tolerance, $16$-bit ADC operation, unless otherwise specified. }$

| PARAMETER        | DESCRIPTION                                            | CONDITION                                                            | MIN<br>(Note 5) | TYP   | MAX<br>(Note 5) | UNIT   |

|------------------|--------------------------------------------------------|----------------------------------------------------------------------|-----------------|-------|-----------------|--------|

| V <sub>DD</sub>  | Power Supply Range                                     |                                                                      | 2.25            |       | 3.63            | ٧      |

| I <sub>DD</sub>  | Supply Current                                         |                                                                      |                 | 70    | 85              | μA     |

| I <sub>DD1</sub> | Supply Current when<br>Powered Down                    | Software disabled or auto power-down                                 |                 | 0.01  | 0.3             | μA     |

| V <sub>I2C</sub> | Supply Voltage Range for I <sup>2</sup> C<br>Interface |                                                                      | 1.7             |       | 3.63            | V      |

| t <sub>int</sub> | ADC Conversion Time                                    | 16-bit ADC data                                                      |                 | 90    |                 | ms     |

| F <sub>I2C</sub> | I <sup>2</sup> C Clock Rate Range                      |                                                                      |                 |       | 400             | kHz    |

| DATA_0           | Dark Count                                             | Range Setting = 0; ADC Resolution 16 Bits                            |                 | 1     | 5               | Counts |

| DATA_FS          | Full Scale ADC Code                                    | ADC Resolution 16 Bits                                               |                 |       | 65535           | Counts |

| DATA_Red         | Red Count                                              | Range = 0; $\lambda$ = 640nm; Irradiance 155 $\mu$ W/cm <sup>2</sup> | 15000           | 20000 | 25000           | Counts |

|                  |                                                        | Range = 1; $\lambda$ = 640nm; Irradiance 155 $\mu$ W/cm <sup>2</sup> |                 | 4350  |                 | Counts |

| DATA_Green       | Green Count                                            | Range = 0; $\lambda$ = 530nm; Irradiance 212 $\mu$ W/cm <sup>2</sup> | 15000           | 20000 | 25000           | Counts |

|                  |                                                        | Range = 1; $\lambda$ = 530nm; Irradiance 212 $\mu$ W/cm <sup>2</sup> |                 | 4350  |                 | Counts |

| DATA_Blue        | Blue Count                                             | Range = 0; $\lambda$ = 470nm; Irradiance 215 $\mu$ W/cm <sup>2</sup> | 15000           | 20000 | 25000           | Counts |

|                  |                                                        | Range = 1; $\lambda$ = 470nm; Irradiance 215 $\mu$ W/cm <sup>2</sup> |                 | 4350  |                 | Counts |

| V <sub>REF</sub> | Voltage at R <sub>EXT</sub> Pin                        |                                                                      |                 | 0.52  |                 | ٧      |

| V <sub>IL</sub>  | SCL and SDA Input Low<br>Voltage                       |                                                                      |                 |       | 0.55            | V      |

| V <sub>IH</sub>  | SCL and SDA Input High<br>Voltage                      |                                                                      | 1.25            |       |                 | V      |

| I <sub>SDA</sub> | SDA Current Sinking<br>Capability                      |                                                                      | 4               | 5     |                 | mA     |

#### NOTES:

- 5. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 6. 640nm Red, 530nm Green and 470 nm Blue LEDs are used to generate a nominal count of 20000 for the Red, Green and Blue data output to characterize part to part variation in production test.

# **Principles of Operation**

#### **Photodiodes and ADC**

The ISL29120 contains three photodiode arrays, which convert light into current. The spectral response for red, green and blue color ambient intensity sensing is as shown in Figure 2. After light is converted to current during the light to signal process, the current output is converted to a digital count by an on-chip Analog-to-Digital Converter (ADC). The ADC converter resolution is selectable from 4, 8, 12 or 16 bits. The ADC conversion time is inversely proportional to the ADC resolution.

The ADC converter uses an integrating architecture. This conversion method is ideal for converting small signals in the presence of a periodic noise. A 100ms integration time (16-bit mode) for instance, rejects 50Hz and 60Hz power line as well as florescent flicker noise.

The ADC integration time is determined by an internal oscillator and the n-bit (n = 4, 8, 12, 16) counter inside the ADC. A good balancing act of integration time and resolution depends on the application for optimum system performance.

The ADC provides two programmable ranges to dynamically accommodate different lighting conditions. For dim conditions, the ADC can be configured at its high sensitivity (low optical) range. For bright conditions, the ADC can be configured at its low sensitivity (higher optical) range.

Note that the effective optical sensitivity of the ISL29120 in terms of counts/ $\mu$ W/cm² is directly proportional to the ADC integration time.

### **I<sup>2</sup>C Interface**

There are eight 8-bit registers inside the ISL29120 for configuration, control and status indication. The two command registers at address 0x00 and 0x01 define the operation of the device and provide status of the interrupt events. Two 8-bit read only registers at address 0x02 and 0x03 are for the ADC output. These registers contain the results of the latest A/D conversion.

Registers 0x04 and 0x05 contain the 'low threshold' value and registers 0x06 and 0x07 store the 'high threshold' value for interrupt generation.

The ISL29120's I $^2$ C interface slave address is internally hard-wired as 1000110x, where x is R (read) or  $\overline{W}$  (write) bit.

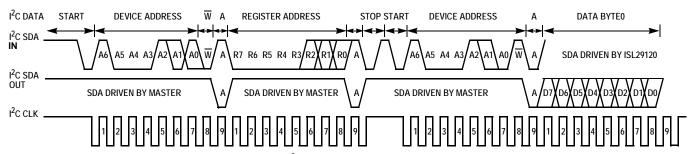

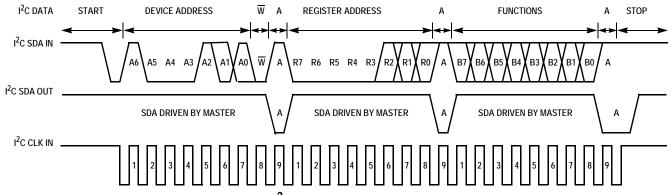

Figure 4 shows a sample one-byte read. Figure 5 shows a sample one-byte write. The  $I^2C$  bus master always drives the SCL (clock) line, while either the master or the slave can drive the SDA (data) line. Figure 5 shows a sample write. Every  $I^2C$  transaction begins with the master asserting a start condition (SDA falling while SCL remains high). The following byte is driven by the master, and includes the slave address and read/write bit. The receiving device is responsible for pulling SDA low during the acknowledgement period. Every  $I^2C$  transaction ends with the master asserting a stop condition (SDA rising while SCL remains high).

For more information about the I<sup>2</sup>C standard, consult the Philips<sup>M</sup> I<sup>2</sup>C specification documents.

FIGURE 4. I<sup>2</sup>C READ TIMING DIAGRAM SAMPLE

FIGURE 5. I<sup>2</sup>C WRITE TIMING DIAGRAM SAMPLE

#### **Register Set**

There are eight registers that are available in the ISL29120. Table 1 summarizes their functions.

**TABLE 1. REGISTER SET**

|      |                     | BIT  |      |      |      |      |      |       |       |         |

|------|---------------------|------|------|------|------|------|------|-------|-------|---------|

| ADDR | REG NAME            | 7    | 6    | 5    | 4    | 3    | 2    | 1     | 0     | DEFAULT |

| 00h  | COMMANDI            | 0P2  | 0P1  | OP0  | 0    | 0    | IFLG | PRST1 | PRST0 | 00h     |

| 01h  | COMMANDII           | 0    | 0    | 0    | 0    | RES1 | RES0 | 0     | RANGE | 00h     |

| 02h  | DATA <sub>LSB</sub> | D7   | D6   | D5   | D4   | D3   | D2   | D1    | D0    | 00h     |

| 03h  | DATA <sub>MSB</sub> | D15  | D14  | D13  | D12  | D11  | D10  | D9    | D8    | 00h     |

| 04h  | INT_LT_LSB          | TL7  | TL6  | TL5  | TL4  | TL3  | TL2  | TL1   | TL0   | 00h     |

| 05h  | INT_LT_MSB          | TL15 | TL14 | TL13 | TL12 | TL11 | TL10 | TL9   | TL8   | 00h     |

| 06h  | INT_HT_LSB          | TH7  | TH6  | TH5  | TH4  | TH3  | TH2  | TH1   | TH0   | FFh     |

| 07h  | INT_HT_MSB          | TH15 | TH14 | TH13 | TH12 | TH11 | TH10 | TH9   | TH8   | FFh     |

### **Command Register I 0x00**

The first command register has the following functions:

**Operation Mode:** Bits[7:5]. These three bits determine the operation mode of the device.

**TABLE 2. OPERATION MODE**

| 0x00[7:5] | OPERATION               |

|-----------|-------------------------|

| 000       | Power-down              |

| 001       | Red Sensor once         |

| 010       | Blue Sensor once        |

| 011       | Green Sensor once       |

| 100       | Reserved                |

| 101       | Red Sensor continuous   |

| 110       | Blue Sensor continuous  |

| 111       | Green Sensor continuous |

Interrupt flag: Bit[2]. This is the interrupt status bit. The bit is set high when the interrupt thresholds have been triggered. Once triggered, the  $\overline{\text{INT}}$  pin stays low and the status bit stays high. Both the interrupt pin and the status bit are cleared at the end of Command Register I read.

**TABLE 3. INTERRUPT FLAG**

| 0x00[2] | OPERATION                 |

|---------|---------------------------|

| 0       | No Interrupt event        |

| 1       | Interrupt event triggered |

Interrupt persist: Bits[1:0]. The interrupt pin and the interrupt flag are triggered/set when the data sensor reading is out of the interrupt threshold window after m consecutive data conversion cycles. The interrupt persist bits determine m.

**TABLE 4. INTERRUPT PERSISTENCE**

| 0x00[1:0] | NUMBER OF DATA CONVERSION CYCLES |

|-----------|----------------------------------|

| 00        | 1                                |

| 01        | 4                                |

| 10        | 8                                |

| 11        | 16                               |

### **Command Register II 0x01**

The second command register has the following functions:

**Resolution:** Bits[3:2] determine the ADC's resolution and the integration time. The integration time is the period the device's analog-to-digital (A/D) converter samples the photodiode current for a measurement.

**TABLE 5. ADC RESOLUTION DATA WIDTH**

| 0x01[3:2] | INTEGRATION TIME (ms) | RESOLUTION |

|-----------|-----------------------|------------|

| 00        | 90                    | 16 Bits    |

| 01        | 5.6                   | 12 Bits    |

| 10        | 0.35                  | 8 Bits     |

| 11        | 0.022                 | 4 Bits     |

1. Range 0x01[0]: The Full Scale Optical Range (FSOR). Optical sensitivity for the 'Low' range is 4.75 times the optical sensitivity in 'High' range.

TABLE 6. RANGE

| 0x01[0] | FSR  |

|---------|------|

| 0       | Low  |

| 1       | High |

#### Data Registers (0x02 and 0x03)

ISL29120 has two 8-bit read-only registers to hold the LSByte and MSByte data from the ADC. The most significant byte (MSB) is accessed at address 0x03, and the least significant byte (LSB) is accessed at address 0x02. For 16-bit resolution, the data is from D0 to D15; for 12-bit resolution, the data is from D0 to D11; for 8-bit resolution, the data is from D0 to D7. The registers are refreshed after every conversion cycle.

**TABLE 7. DATA REGISTERS**

| ADDRESS | CONTENTS                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------------------|

| 0x02    | D0 is LSB for 4, 8, 12 or 16-bit resolution; D3 is MSB for 4-bit resolution; D7 is MSB for 8-bit resolution |

| 0x03    | D15 is MSB for 16-bit resolution; D11 is MSB for 12-bit resolution                                          |

#### **Interrupt Threshold Registers**

Registers 0x04 and 0x05 set the low (LO) threshold for the interrupt pin and the interrupt flag. Register 0x04 is the LSByte and 0x05 is the MSByte. By default, the Interrupt threshold LO is 00 hex for both LSByte and MSByte.

Registers 0x06 and 0x07 set the high (HI) threshold for the interrupt pin and the interrupt flag. Register 0x06 is the LSByte and 0x07 is the MSByte. By default, the Interrupt threshold HI is 0xFF for both LSByte and MSByte.

Note that there is only one set of threshold registers as ISL29120 performs R, G and B conversions sequentially. If different thresholds are required for each color, then these threshold registers must be re-configured prior to issuing a convert start command. If a common threshold setting for the R, G and B is desired then the threshold register can be initialized at power-up.

Interrupt threshold registers should be programmed appropriately for the selected ADC conversion resolution. For example, for 12-bit mode, only the corresponding 12 bits of the threshold registers must be programmed and the remaining bits should be set to zero.

#### **Interrupt Function**

An interrupt event (IFLG) is indicated by 0x00[2]. The user must clear this bit during the device initialization. The ISL29120 will issue an interrupt indication by setting the IFLG bit if the count in Register 0x02 and 0x03 are outside the user's programmed window in interrupt threshold registers. Read Register 0x00 to clear the interrupt flag. Interrupt flags should also be cleared following a interrupt threshold configuration change.

An Interrupt persistency 0x01[1:0] option is available for interrupt event control for the RGB ambient light measurement. Persistency requires x-in-a-row interrupt flags before the  $\overline{\text{INT}}$  pin is driven low. The user must read Register 0x0 to clear the Interrupt.

#### **Noise/Flicker Rejection**

Integrating ADC's provide excellent flicker/noise-rejection for periodic sources whose frequency is an integer multiple of the conversion rate. For instance, a 60Hz AC unwanted signal's sum from 0ms to k\*16.66ms (k = 1,2...k<sub>i</sub>) is zero. Similarly, setting the device's integration time to be an integer multiple of the

periodic noise signal significantly improves the light sensor output signal in the presence of noise.

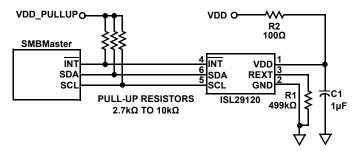

# **Typical Application Circuit**

A typical application for the ISL29120 is shown in Figure 6. The ISL29120's  $I^2C$  address is internally hardwired as 1000110x. The device can be connected to a system's  $I^2C$  bus with other  $I^2C$  compliant devices.

FIGURE 6. ISL29120 TYPICAL APPLICATION CIRCUIT

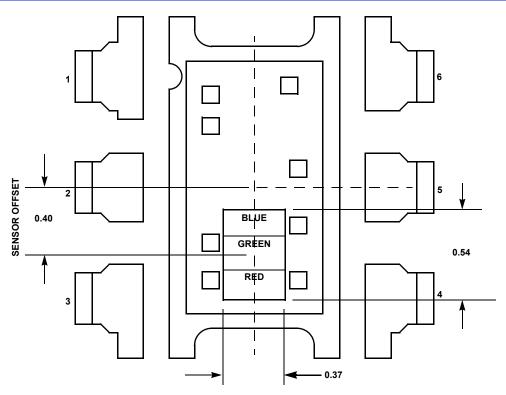

# **Suggested PCB Footprint**

It is important that users check the "Surface Mount Assembly Guidelines for Optical Dual FlatPack No Lead (ODFN) Package" before starting ODFN product board mounting. <a href="http://internal.intersil.com/content/dam/Intersil/documents/tb47/tb477.pdf">http://internal.intersil.com/content/dam/Intersil/documents/tb47/tb477.pdf</a>

### **PCB Layout Considerations**

The ISL29120 is relatively insensitive to PCB layout. There are only a few considerations that will ensure best performance.

Route the supply and I $^2$ C traces away from sources of digital switching noise. Use a 1 $\mu$ F power-supply decoupling capacitors close to the device. A series resistor in the power supply to isolate switching noise elsewhere in the system is recommended. The 499k $\Omega$  resistor should be placed close to the device and away from any noise sources.

#### **Soldering Considerations**

Convection heating is recommended for reflow soldering; direct-infrared heating is not recommended. The plastic ODFN package does not require a custom reflow soldering profile, and is qualified to +260°C. A standard reflow soldering profile with a +260°C maximum is recommended.

### **RGB Spectral Sensitivity**

Typical spectral response of the ISL29120's Red, Green and Blue channels is shown in Figure 2. It should be observed that there is a considerable cross-spectral sensitivity among three colors. In addition, all three channels have a strong sensitivity to light in infra-red spectrum.

It is therefore imperative that the a color sense system-based on ISL29120 be calibrated for the desired application using a mathematical model to compensate for the cross-spectral coupling between the Red, Green and Blue channels.

For operation in infra-red rich environments, such as sunlight or incandescent lighting, use of an external Infrared filter is required for meaningful spectral color sensing.

FIGURE 7. 6 LD ODFN SENSOR LOCATION OUTLINE

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE         | REVISION | CHANGE           |

|--------------|----------|------------------|

| May 29, 2012 | FN8314.0 | Initial release. |

### **About Intersil**

Intersil Corporation is a leader in the design and manufacture of high-performance analog, mixed-signal and power management semiconductors. The company's products address some of the largest markets within the industrial and infrastructure, personal computing and high-end consumer markets. For more information about Intersil, visit our website at <a href="https://www.intersil.com">www.intersil.com</a>.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com/en/support/ask-an-expert.html">www.intersil.com/en/support/ask-an-expert.html</a>. Reliability reports are also available from our website at <a href="https://www.intersil.com/en/support/qualandreliability.html#reliability">https://www.intersil.com/en/support/qualandreliability.html#reliability</a>

© Copyright Intersil Americas LLC 2012. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

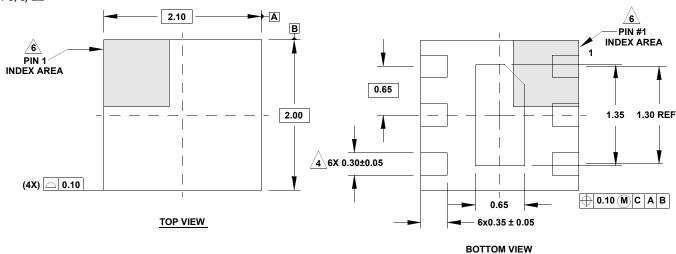

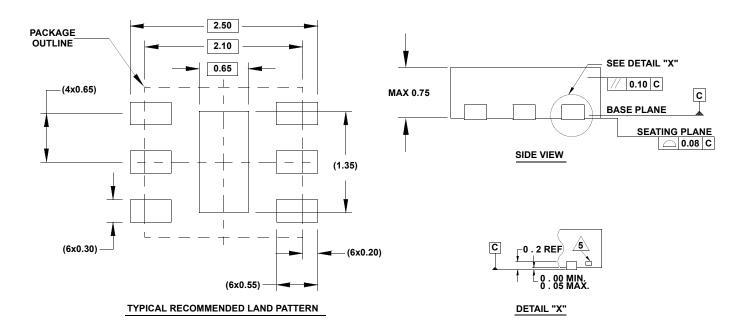

# **Package Outline Drawing**

#### L6.2x2.1

6 LEAD OPTICAL DUAL FLAT NO-LEAD PLASTIC PACKAGE (ODFN)

Rev 3, 5/11

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.