# ISL85403DEMO1Z Demonstration Board User Guide

## **Description**

The ISL85403DEM01Z board allows quick evaluation of the ISL85403 in the synchronous buck configuration. It also demonstrates the compact size solution for the wide input voltage range point-of-load DC/DC converter using ISL85403.

# **Specifications**

The design specifications of the ISL85403DEM01Z are shown in Table 1.

**TABLE 1. SPECIFICATIONS**

| PARAMETERS                         | VALUES                     |  |

|------------------------------------|----------------------------|--|

| Input Voltage (V <sub>IN</sub> )   | 7V to 40V                  |  |

| Output Voltage (V <sub>OUT</sub> ) | 5.0V                       |  |

| Max. Output Current (IOUT_MAX)     | 2.5A                       |  |

| Switching Frequency                | 500kHz                     |  |

| Output Ripple                      | 50mV at 2.5A Load          |  |

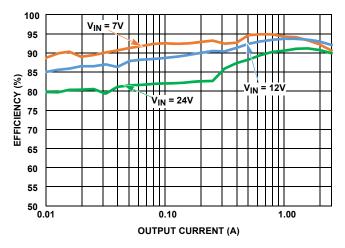

| Peak Efficiency                    | 93% at 50% Load, 12V Input |  |

## **Key Features**

- · Small, compact design

- V<sub>IN</sub> range of 7V to 40V

- V<sub>OUT</sub> adjustable from 0.8V to 5V

- · Convenient power connection

#### References

ISL85403 Datasheet

## **Ordering Information**

| PART NUMBER    | DESCRIPTION                                                       |  |

|----------------|-------------------------------------------------------------------|--|

| ISL85403DEM01Z | ISL85403 Evaluation kit, synchronous buck configuration 5V output |  |

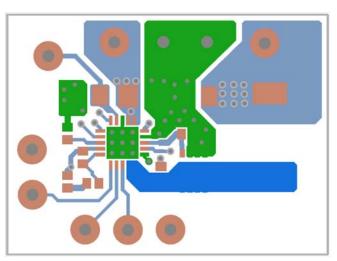

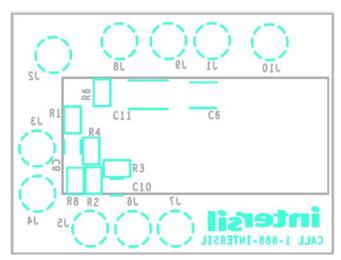

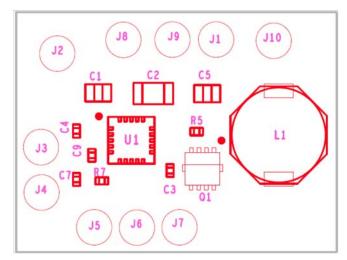

FIGURE 1. TOP VIEW

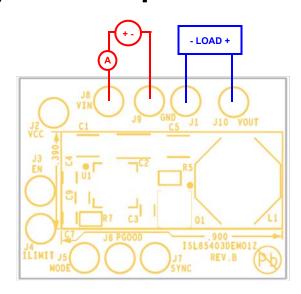

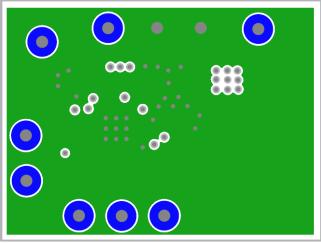

FIGURE 2. BOTTOM VIEW

# **Functional Description**

The ISL85403 is a flexible switching regulator with an integrated  $127m\Omega$  high-side MOSFET. It can be used as a synchronous buck converter, a 2-stage boost-buck converter, or a noninverting buckboost converter.

The ISL85403DEM01Z board demonstrates the compact size and operations of the ISL85403 in the synchronous buck configuration. The ISL85403DEM01Z board is shown in Figures 1 and 2.

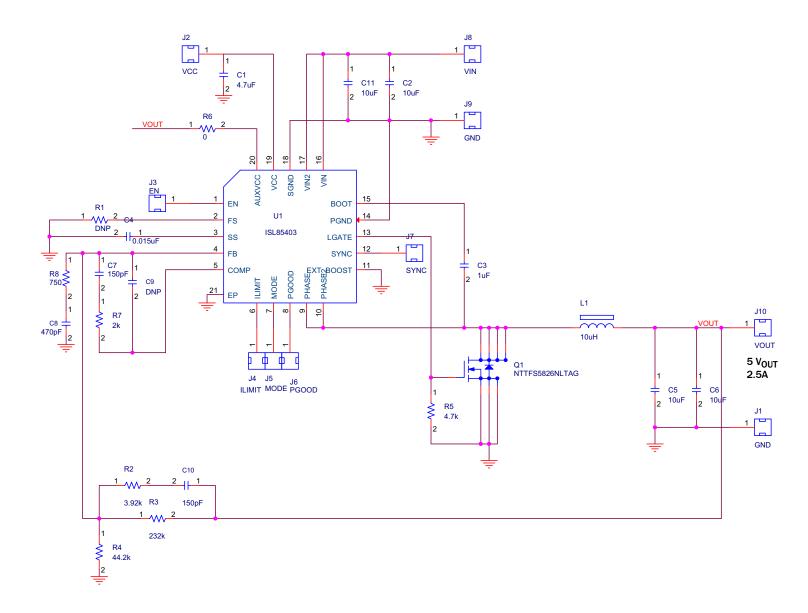

The schematic is shown on page 3, bill of materials on page 4, and PCB layers for reference start on page 7. Figures 4 through 12 show performance data taken from the demo board.

### Operating Range

The board input voltage range is 7V to 40V. The output voltage is set to 5V and can be changed by voltage feedback resistors R3 and  $R_4$ , as shown in Equation 1:

$$R_4 = R_3 \cdot \frac{V_{ref}}{V_{out} - v_{ref}}$$

(EQ. 1)

NOTE: In order to change to a higher output voltage, the output capacitors have to be changed for the higher voltage rating.

The board is set to a default frequency of 500kHz (FS pin/R<sub>1</sub> is open). The switching frequency can be programmed to other values by a resistor at R<sub>1</sub>. Refer to the ISL85403 datasheet for the resistor value and the switching frequency. The switching frequency can also be synchronized to external clock by connecting the external clock to the SYNC terminal (J7).

## **PCB Layout Guidelines**

- 1. Place the input ceramic capacitors as closely as possible to the IC VIN pin and power ground connecting to the power MOSFET or Diode. Keep this loop (input ceramic capacitor, IC VIN pin and MOSFET/Diode) as tiny as possible to minimize the voltage spikes induced by the trace parasitic inductance.

- 2. Keep the phase node copper area small but large enough to handle the load current.

- 3. Place the output ceramic and aluminum capacitors close to the power stage components as well.

- 4. Place vias (at least 9) in the bottom pad of the IC. The bottom pad should be placed in ground copper plane with an area as large as possible in multiple layers to effectively reduce the thermal impedance.

- 5. Place the 4.7µF ceramic decoupling capacitor at the VCC pin (the closest place to the IC). Put multiple vias close to the ground pad of this capacitor.

- 6. Keep the bootstrap capacitor close to the IC.

- 7. Keep the LGATE drive trace as short as possible and try to avoid using via in the LGATE drive path to achieve the lowest impedance.

- 8. Place the output voltage sense trace close to the place that is to be strictly regulated.

- 9. Place all the peripheral control components close to the IC.

#### **Quick Test Setup**

FIGURE 3. ISL85403DEM01Z BOARD SETUP

- 1. If PWM mode is desired, connect test point MODE (J5) to ground. Otherwise leave the J5 open for PFM mode.

- 2. Connect the power supply to the input terminals VIN (J8) and GND (J9). Connect the load terminals to the buck outputs VOUT (J10) and GND (J11). Make sure the setup is correct prior to applying any power or load to the board.

- 3. Adjust the power supply to 12V and turn it on.

- 4. Verify the output voltage is 5V and use oscilloscope to monitor the phase node waveforms.

## **ISL85403DEMO1Z Circuit Schematic**

# **Application Note 1960**

# **Bill of Materials**

| REF DES    | PART NUMBER        | QTY | DESCRIPTION                                                  | MANUFACTURER |

|------------|--------------------|-----|--------------------------------------------------------------|--------------|

| <b>C</b> 9 |                    | 0   | DNP                                                          |              |

| C7, C10    | VARIOUS            | 2   | CAP, SMD, 0402, 150pF, 50V, 10%, COG, ROHS                   | VARIOUS      |

| C3         | ECJ-OEBOJ105M      | 1   | CAP, SMD, 0402, 1µF, 6.3V, 20%, X5R, ROHS                    | PANASONIC    |

| C4         | VARIOUS            | 1   | CAP, SMD, 0402, 0.015µF, 16V, 10%, X7R, ROHS                 | VARIOUS      |

| C8         | VARIOUS            | 1   | CAP, SMD, 0402, 470pF, 50V, 10%, X7R, R0HS                   | VARIOUS      |

| C5, C6     | GRM21BR71A106KE51K | 2   | CAP, SMD, 0805, 10µF, 10V, 10%, X7R, R0HS                    | Murata       |

| C1         | GRM21BR71A475KA73L | 1   | CAP, SMD, 0805, 4.7µF, 10V, 10%, X7R, ROHS                   | Murata       |

| C2, C11    | C3216X5R1H106K     | 2   | CAP, SMD, 1206, 10µF, 50V, 10%, X5R, ROHS                    | TDK          |

| L1         | SD8350-100-R       | 1   | COIL-PWR INDUCTOR, SMD, 9.5x8.3, 10μH, 20%, 4A, 31.4mΩ, ROHS | COILTRONICS  |

| U1         | ISL85403IRZ        | 1   | IC-SWITCHING REGULATOR, 20P, QFN, 4X4, ROHS                  | INTERSIL     |

| Q1         | NTTFS5826NLTAG     | 1   | TRANSIST-MOS, N-CHANNEL, 8P, PG-TSDSON-8, 60V, 8A, ROHS      | ON SEMI      |

| R2         | VARIOUS            | 1   | RES, SMD, 0402, 3.92k, 1/16W, 1%, TF, ROHS                   | VARIOUS      |

| R3         | VARIOUS            | 1   | RES, SMD, 0402, 232k, 1/16W, 1%, TF, ROHS                    | VARIOUS      |

| R7         | VARIOUS            | 1   | RES, SMD, 0402, 2k, 1/16W, 1%, TF, ROHS                      | VARIOUS      |

| R4         | ERJ-2RKF4422X      | 1   | RES, SMD, 0402, 44.2k, 1/16W, 1%, TF, ROHS                   | VARIOUS      |

| R5         | VARIOUS            | 1   | RES, SMD, 0402, 4.7k, 1/16W, 1%, TF, ROHS                    | VARIOUS      |

| R6         | VARIOUS            | 1   | RES, SMD, 0402, 0Ω, 1/16W, 1%, TF, ROHS                      | VARIOUS      |

| R1         | N/A                | 0   | Do not populate                                              | N/A          |

# **Typical Performance Curves**

FIGURE 4. EFFICIENCY vs LOAD

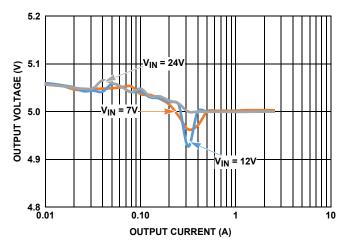

FIGURE 5. LINE REGULATION

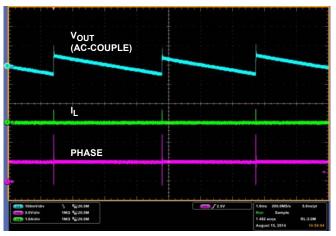

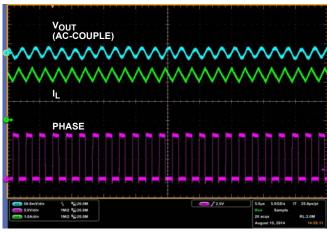

FIGURE 6. OUTPUT RIPPLE AT 0A LOAD

FIGURE 7. OUTPUT RIPPLE AT 2.5A LOAD

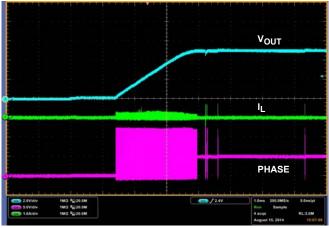

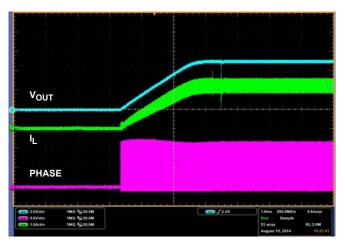

FIGURE 8. SOFT-START AT 0A LOAD

FIGURE 9. SOFT-START AT 2.5A LOAD

# Typical Performance Curves (Continued)

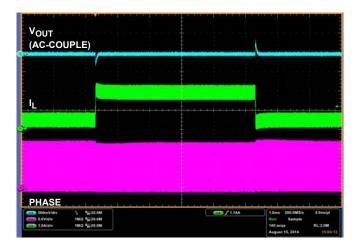

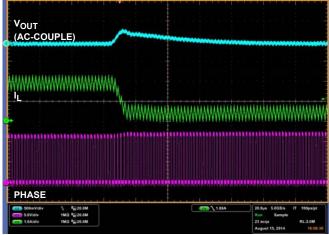

FIGURE 10. LOAD TRANSIENT RESPONSE

FIGURE 11. LOAD TRANSIENT RESPONSE

FIGURE 12. LOAD TRANSIENT RESPONSE

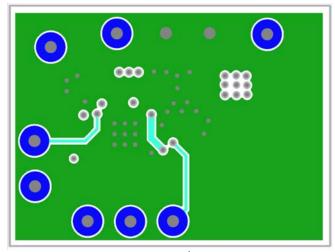

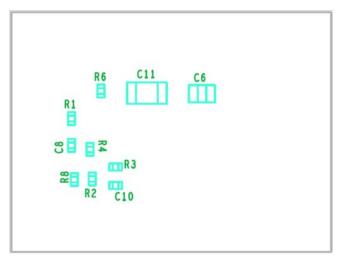

# **Board Layout**

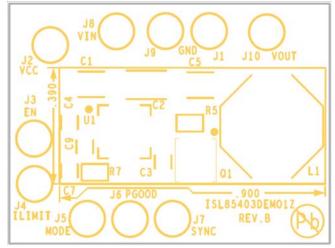

FIGURE 13. SILKSCREEN TOP COMPONENTS

FIGURE 14. TOP LAYER

FIGURE 15. 2<sup>nd</sup> LAYER

FIGURE 16. 3<sup>rd</sup> LAYER

FIGURE 17. BOTTOM LAYER

FIGURE 18. SILKSCREEN BOTTOM COMPONENTS

# **Application Note 1960**

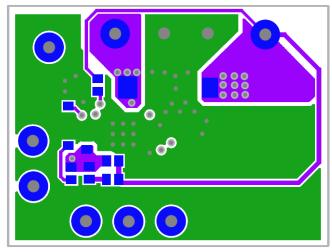

# **Board Layout** (Continued)

FIGURE 19. TOP COMPONENT ASSEMBLY

FIGURE 20. BOTTOM COMPONENT ASSEMBLY (MIRRORED)

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.