# LT6119-1/LT6119-2

Current Sense Amplifier, Reference and Comparators with POR

The LT®6119 is a complete high side current sense device

that incorporates a precision current sense amplifier, an

integrated voltage reference and two latching comparators.

Two versions of the LT6119 are available. The LT6119-1

has the comparators connected in opposing polarity and

the LT6119-2 has the comparators connected in the same

polarity. The comparator latch functionality can be enabled

or disabled and the comparators can be configured to reset

upon power-on. The input and the open-drain outputs of

the comparators are independent from the current sense

amplifier. The comparator trip points and amplifier gain

The overall propagation delay of the LT6119 is typically

only 1.4µs, allowing for quick reaction to overcurrent and undercurrent conditions. The 1MHz bandwidth allows the

LT6119 to be used for error detection in critical applications such as motor control. The high threshold accuracy

of the comparators, combined with the ability to latch

both comparators, ensures the LT6119 can capture high

The LT6119 is fully specified for operation from -40°C

to 125°C, making it suitable for industrial and automo-

tive applications. The LT6119 is available in a small

are configured with external resistors.

DESCRIPTION

speed events.

10-lead MSOP.

### FEATURES

- Current Sense Amplifier

- Fast Step Response: 500ns

- Low Offset Voltage: 200µV Maximum

- Low Gain Error: 0.2% Maximum

- Internal 400mV Precision Reference

- Internal Latching Comparators

- Power-On Reset Capability

- Fast Response Time: 500ns

- Total Threshold Error: ±1.25% Maximum

- Two Comparator Polarity Options

- Wide Supply Range: 2.7V to 60V

- Supply Current: 550µA

- Specified for –40°C to 125°C Temperature Range

- Available in 10-Lead MSOP Package

### **APPLICATIONS**

- Overcurrent, Undercurrent and Fault Detection

- Current Shunt Measurement

- Battery Monitoring

- Motor Control

- Automotive Monitoring and Control

- Industrial Control

**σ**, LT, LTC, LTM, TimerBlox, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

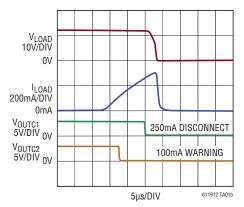

## TYPICAL APPLICATION

#### 0.10 IRF9640 τοι οδο 121/ 0.1μF **Ι ≥**100Ω 3.3V 2 9 SENSEHI SENSELO V+ OUTA · V<sub>OUT</sub> **≤**10k **≤**1.62k **≤**100k **\$**6.04k LT6119-2 LE 100nF INC2 1k 2 37k OUTC2 100mA WARNING 2N2700 OUTC1 INC1 250mA DISCONNECT 1.6k Ŧ CMH25234B

Fast Acting Fault Protection with Power-On Reset and Early Warning

#### **Response to Overcurrent Event**

### ABSOLUTE MAXIMUM RATINGS

| (Note 1)                                                                |

|-------------------------------------------------------------------------|

| Total Supply Voltage (V <sup>+</sup> to V <sup>-</sup> )60V             |

| Maximum Voltage                                                         |

| (SENSELO, SENSEHI, OUTA) V <sup>+</sup> + 1V                            |

| Maximum V <sup>+</sup> – (SENSELO or SENSEHI)                           |

| Maximum LE Voltage60V                                                   |

| Maximum Comparator Input Voltage60V                                     |

| Maximum Comparator Output Voltage60V                                    |

| Input Current (Note 2)–10mA                                             |

| SENSEHI, SENSELO Input Current±10mA                                     |

| Differential SENSEHI or SENSELO Input Current ±2.5mA                    |

| Amplifier Output Short-Circuit Duration (to V <sup>-</sup> ) Indefinite |

| Operating Temperature Range (Note 3)                                    |

| LT6119I–40°C to 85°C                                                    |

| LT6119H–40°C to 125°C                                                   |

| Specified Temperature Range (Note 3)                                    |

| LT6119I–40°C to 85°C                                                    |

| LT6119H–40°C to 125°C                                                   |

| Maximum Junction Temperature 150°C                                      |

| Storage Temperature Range65°C to 150°C                                  |

| Lead Temperature (Soldering, 10 sec)                                    |

|                                                                         |

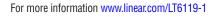

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION  | SPECIFIED TEMPERATURE RANGE |

|------------------|-------------------|---------------|----------------------|-----------------------------|

| LT6119IMS-1#PBF  | LT6119IMS-1#TRPBF | LTGNV         | 10-Lead Plastic MSOP | –40°C to 85°C               |

| LT6119HMS-1#PBF  | LT6119HMS-1#TRPBF | LTGNV         | 10-Lead Plastic MSOP | -40°C to 125°C              |

| LT6119IMS-2#PBF  | LT6119IMS-2#TRPBF | LTGNW         | 10-Lead Plastic MSOP | -40°C to 85°C               |

| LT6119HMS-2#PBF  | LT6119HMS-2#TRPBF | LTGNW         | 10-Lead Plastic MSOP | -40°C to 125°C              |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

611912f

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 12V, V<sub>PULLUP</sub> = V<sup>+</sup>, V<sub>LE</sub> = 2.7V, R<sub>IN</sub> = 100 $\Omega$ , R<sub>OUT</sub> = R1 + R2 + R3 = 10k, gain = 100, R<sub>C</sub> = 25.5k, C<sub>L</sub> = C<sub>LC</sub> = 2pF, unless otherwise noted. (See Figure 3)

| SYMBOL                         | PARAMETER                                                                              | CONDITIONS                                                                                                                                                    |   | MIN          | ТҮР        | MAX         | UNITS      |

|--------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|------------|-------------|------------|

| V <sup>+</sup>                 | Supply Voltage Range                                                                   |                                                                                                                                                               |   | 2.7          |            | 60          | V          |

| ls                             | Supply Current (Note 4)                                                                | V <sup>+</sup> = 2.7V, R <sub>IN</sub> = 1k, V <sub>SENSE</sub> = 5mV                                                                                         |   |              | 475        |             | μA         |

|                                |                                                                                        | $V^+ = 60V, R_{IN} = 1k, V_{SENSE} = 5mV$                                                                                                                     | • |              | 600        | 700<br>1000 | μA<br>μA   |

|                                | LE Pin Current                                                                         | $V_{LE} = 0V, V^+ = 60V$                                                                                                                                      |   |              | -100       |             | nA         |

| V <sub>IH</sub>                | LE Pin Input High                                                                      | V <sup>+</sup> = 2.7V to 60V                                                                                                                                  |   | 1.5          |            |             | V          |

| V <sub>IL</sub>                | LE Pin Input Low                                                                       | V <sup>+</sup> = 2.7V to 60V                                                                                                                                  |   |              |            | 0.5         | V          |

| Current Sen                    | se Amplifier                                                                           | •                                                                                                                                                             |   |              |            |             |            |

| V <sub>OS</sub>                | Input Offset Voltage                                                                   | V <sub>SENSE</sub> = 5mV<br>V <sub>SENSE</sub> = 5mV                                                                                                          | • | -200<br>-300 |            | 200<br>300  | μV<br>μV   |

| $\Delta V_{OS}/\Delta T$       | Input Offset Voltage Drift                                                             | V <sub>SENSE</sub> = 5mV                                                                                                                                      |   |              | ±0.8       |             | μV/°C      |

| IB                             | Input Bias Current<br>(SENSELO, SENSEHI)                                               | V <sup>+</sup> = 2.7V to 60V                                                                                                                                  | • |              | 60         | 300<br>350  | nA<br>nA   |

| I <sub>OS</sub>                | Input Offset Current                                                                   | V <sup>+</sup> = 2.7V to 60V                                                                                                                                  |   |              | ±5         |             | nA         |

| I <sub>OUTA</sub>              | Output Current (Note 5)                                                                |                                                                                                                                                               |   | 1            |            |             | mA         |

| PSRR                           | Power Supply Rejection Ratio<br>(Note 6)                                               | V <sup>+</sup> = 2.7V to 60V                                                                                                                                  | • | 120<br>114   | 127        |             | dB<br>dB   |

| CMRR                           | Common Mode Rejection Ratio                                                            | V <sup>+</sup> = 36V, V <sub>SENSE</sub> = 5mV, V <sub>ICM</sub> = 2.7V to 36V                                                                                |   |              | 125        |             | dB         |

|                                |                                                                                        | $V^+ = 60V, V_{SENSE} = 5mV, V_{ICM} = 27V \text{ to } 60V$                                                                                                   | • | 110<br>103   | 125        |             | dB<br>dB   |

| V <sub>SENSE(MAX)</sub>        | Full-Scale Input Sense Voltage<br>(Note 5)                                             | R <sub>IN</sub> = 500Ω                                                                                                                                        | • | 500          |            |             | mV         |

|                                | Gain Error (Note 7)                                                                    | V <sup>+</sup> = 2.7V to 12V<br>V <sup>+</sup> = 12V to 60V, V <sub>SENSE</sub> = 5mV to 100mV                                                                | • | -0.2         | -0.08      | 0           | %          |

|                                | SENSELO Voltage (Note 8)                                                               | $V^+$ = 2.7V, $V_{SENSE}$ = 100mV, $R_{OUT}$ = 2k<br>$V^+$ = 60V, $V_{SENSE}$ = 100mV                                                                         | • | 2.5<br>27    |            |             | V<br>V     |

|                                | Output Swing High (V <sup>+</sup> to V <sub>OUTA</sub> )                               | V <sup>+</sup> = 2.7V, V <sub>SENSE</sub> = 27mV                                                                                                              |   |              |            | 0.2         | V          |

|                                |                                                                                        | V <sup>+</sup> = 12V, V <sub>SENSE</sub> = 120mV                                                                                                              | • |              |            | 0.5         | V          |

| BW                             | Signal Bandwidth                                                                       | I <sub>OUT</sub> = 1mA<br>I <sub>OUT</sub> = 100μA                                                                                                            |   |              | 1<br>140   |             | MHz<br>kHz |

| t <sub>r</sub>                 | Input Step Response (to 50% of Final Output Voltage)                                   | V <sup>+</sup> = 2.7V, V <sub>SENSE</sub> = 24mV Step, Output Rising Edge<br>V <sup>+</sup> = 12V to 60V, V <sub>SENSE</sub> = 100mV Step, Output Rising Edge |   |              | 500<br>500 |             | ns<br>ns   |

| t <sub>SETTLE</sub>            | Settling Time to 1%                                                                    | $V_{SENSE} = 10mV$ to 100mV, $R_{OUT} = 2k$                                                                                                                   |   |              | 2          |             | μs         |

| Reference a                    | nd Comparator                                                                          |                                                                                                                                                               |   |              |            |             |            |

| V <sub>TH(R)</sub><br>(Note 9) | Rising Input Threshold Voltage<br>(LT6119-1 Comparator 1<br>LT6119-2 Both Comparators) | V <sup>+</sup> = 2.7V to 60V                                                                                                                                  | • | 395          | 400        | 405         | mV         |

| V <sub>TH(F)</sub><br>(Note 9) | Falling Input Threshold Voltage<br>(LT6119-1 Comparator 2)                             | V <sup>+</sup> = 2.7V to 60V                                                                                                                                  | • | 395          | 400        | 405         | mV         |

| V <sub>HYS</sub>               | $V_{HYS} = V_{TH(R)} - V_{TH(F)}$                                                      | V <sup>+</sup> = 2.7V to 60V                                                                                                                                  |   | 3            | 10         | 15          | mV         |

|                                | Comparator Input Bias Current                                                          | V <sub>INC1,2</sub> = 0V, V <sup>+</sup> = 60V                                                                                                                |   | -50          |            |             | nA         |

| V <sub>OL</sub>                | Output Low Voltage                                                                     | I <sub>OUTC1,C2</sub> = 500μA, V <sup>+</sup> = 2.7V                                                                                                          | • |              | 60         | 150<br>220  | mV<br>mV   |

|                                | High to Low Propagation Delay                                                          | 5mV Overdrive<br>100mV Overdrive                                                                                                                              |   |              | 3<br>0.5   |             | μs<br>µs   |

### **ELECTRICAL CHARACTERISTICS**

The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . V<sup>+</sup> = 12V,  $V_{PULLUP} = V^+$ ,  $V_{LE} = 2.7V$ ,  $R_{IN} = 100\Omega$ ,  $R_{OUT} = R1 + R2 + R3 = 10k$ , gain = 100,  $R_C = 25.5k$ ,  $C_L = C_{LC} = 2pF$ , unless otherwise noted. (See Figure 3)

| SYMBOL             | PARAMETER                    | CONDITIONS | MIN | ТҮР  | MAX | UNITS |

|--------------------|------------------------------|------------|-----|------|-----|-------|

|                    | Output Fall Time             |            |     | 0.08 |     | μs    |

| t <sub>RESET</sub> | Reset Time                   |            |     | 0.5  |     | μs    |

| t <sub>RPW</sub>   | Minimum LE Reset Pulse Width |            | 2   |      |     | μs    |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Input and output pins have ESD diodes connected to ground. The SENSEHI and SENSELO pins have additional current handling capability specified as SENSEHI, SENSELO input current.

Note 3: The LT6119I is guaranteed to meet specified performance from -40°C to 85°C. LT6119H is guaranteed to meet specified performance from -40°C to 125°C.

**Note 4:** Supply current is specified with the comparator outputs high. When the comparator outputs go low the supply current will increase by 75µA typically per comparator.

Note 5: The full-scale input sense voltage and the maximum output current must be considered to achieve the specified performance.

Note 6: Supply voltage and input common mode voltage are varied while amplifier input offset voltage is monitored.

Note 7: Specified gain error does not include the effects of external resistors R<sub>IN</sub> and R<sub>OUT</sub>. Although gain error is only guaranteed between 12V and 60V, similar performance is expected for  $V^+ < 12V$ , as well.

Note 8: Refer to SENSELO. SENSEHI Range in the Applications Information section for more information.

Note 9: The input threshold voltage which causes the output voltage of the comparator to transition from high to low is specified. The input voltage which causes the comparator output to transition from low to high is the magnitude of the difference between the specified threshold and the hysteresis.

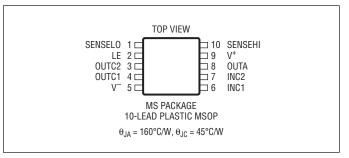

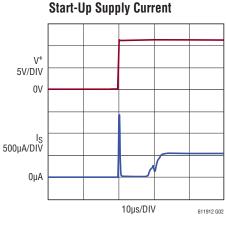

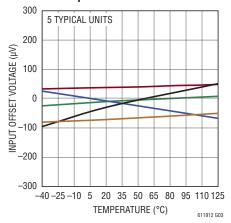

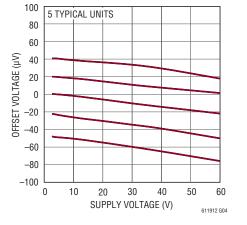

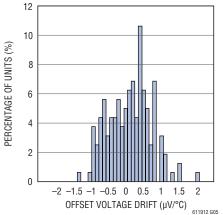

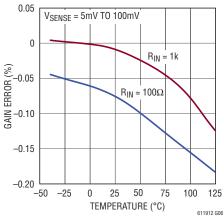

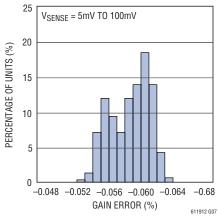

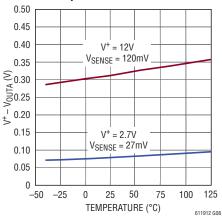

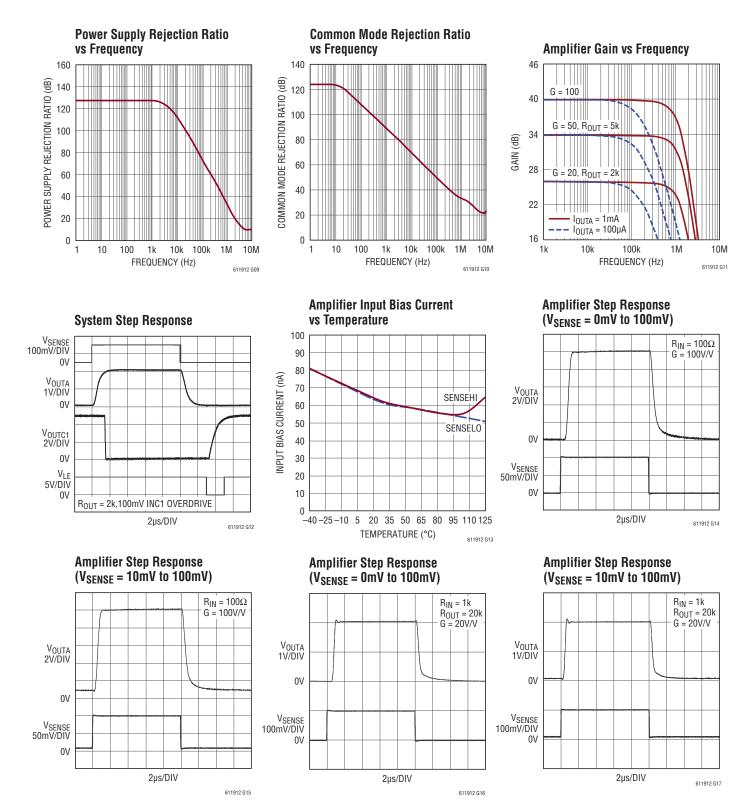

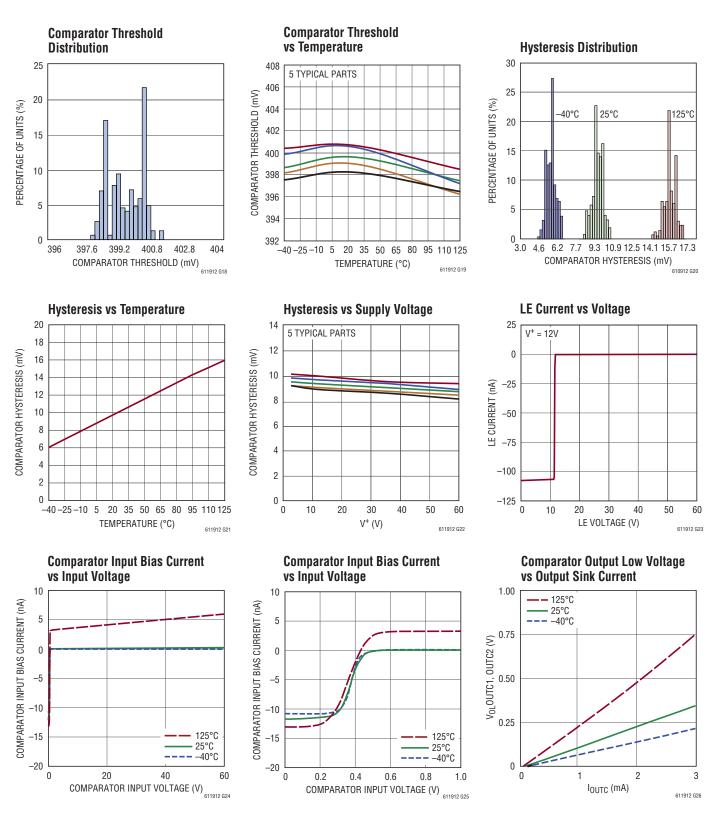

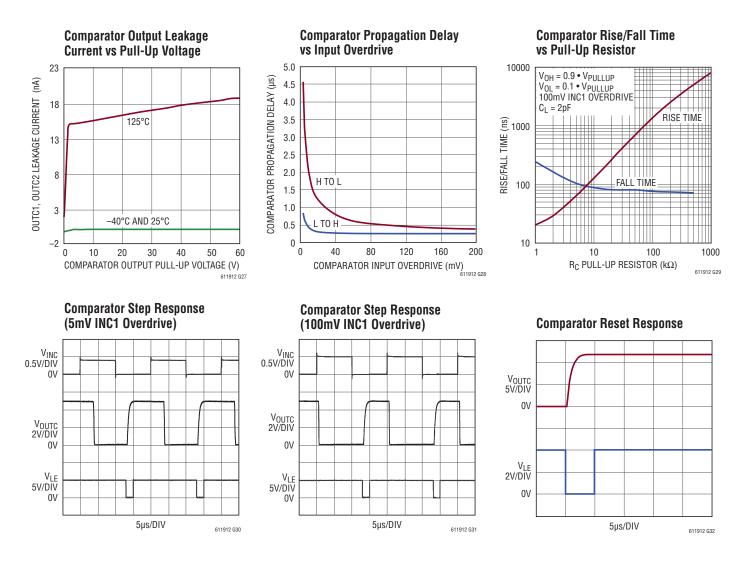

# **TYPICAL PERFORMANCE CHARACTERISTICS** Performance characteristics taken at $T_A = 25^{\circ}C$ , $V^+ = 12V$ , $V_{PULLUP} = V^+$ , $V_{LE} = 2.7V$ , $R_{IN} = 100\Omega$ , $R_{OUT} = R1 + R2 + R3 = 10k$ , gain = 100, $R_C = 25.5k$ , $C_L = C_{LC} = 2pF$ , unless otherwise

noted. (See Figure 3)

#### **Input Offset Voltage** vs Temperature

**Amplifier Offset Voltage** vs Supply Voltage

**Offset Voltage Drift Distribution**

#### **Amplifier Gain Error** vs Temperature

Amplifier Gain Error Distribution

Amplifier Output Swing vs Temperature

6119121

**TYPICAL PERFORMANCE CHARACTERISTICS** Performance characteristics taken at  $T_A = 25^{\circ}C$ ,  $V^+ = 12V$ ,  $V_{PULLUP} = V^+$ ,  $V_{LE} = 2.7V$ ,  $R_{IN} = 100\Omega$ ,  $R_{OUT} = R1 + R2 + R3 = 10k$ , gain = 100,  $R_C = 25.5k$ ,  $C_L = C_{LC} = 2pF$ , unless otherwise noted. (See Figure 3)

611912f

**TYPICAL PERFORMANCE CHARACTERISTICS** Performance characteristics taken at  $T_A = 25^{\circ}C$ ,  $V^+ = 12V$ ,  $V_{PULLUP} = V^+$ ,  $V_{LE} = 2.7V$ ,  $R_{IN} = 100\Omega$ ,  $R_{OUT} = R1 + R2 + R3 = 10k$ , gain = 100,  $R_C = 25.5k$ ,  $C_L = C_{LC} = 2pF$ , unless otherwise

$V^{+} = 12V$ ,  $V_{PULLUP} = V^{+}$ ,  $V_{LE} = 2.7V$ ,  $R_{IN} = 100\Omega$ ,  $R_{OUT} = R1 + R2 + R3 = 10k$ , gain = 100,  $R_{C} = 25.5k$ ,  $C_{L} = C_{LC} = 2pF$ , unless otherwise noted. (See Figure 3)

**TYPICAL PERFORMANCE CHARACTERISTICS** Performance characteristics taken at  $T_A = 25^{\circ}C$ ,  $V^+ = 12V$ ,  $V_{PULLUP} = V^+$ ,  $V_{LE} = 2.7V$ ,  $R_{IN} = 100\Omega$ ,  $R_{OUT} = R1 + R2 + R3 = 10k$ , gain = 100,  $R_C = 25.5k$ ,  $C_L = C_{LC} = 2pF$ , unless otherwise noted. (See Figure 3)

611912f

### PIN FUNCTIONS

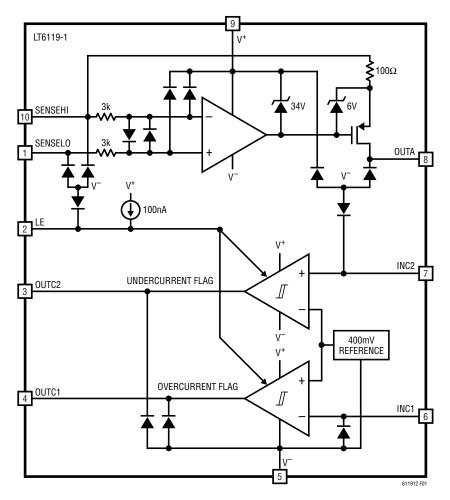

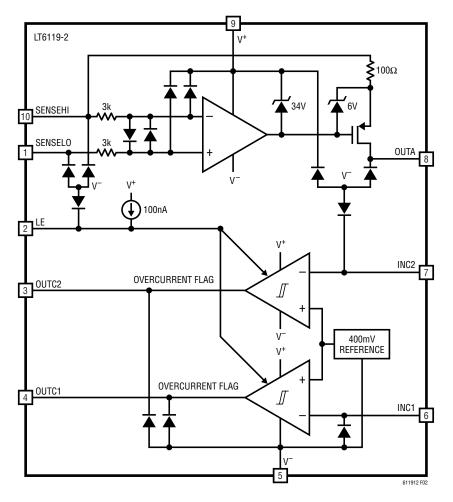

**SENSELO (Pin 1):** Sense Amplifier Input. This pin must be tied to the load end of the sense resistor.

**LE (Pin 2):** Latch Control Pin. When high, the comparator latch is enabled. With the comparator latch enabled, the comparator output will latch at a low level once tripped. When the LE input is low, the comparator latch is disabled and the comparator functions transparently.

**OUTC2 (Pin 3):** Open-Drain Comparator 2 Output. Offstate voltage may be as high as 60V above  $V^-$ , regardless of V<sup>+</sup> used.

**OUTC1 (Pin 4):** Open-Drain Comparator 1 Output. Offstate voltage may be as high as 60V above  $V^-$ , regardless of V<sup>+</sup> used.

**V<sup>-</sup> (Pin 5):** Negative Supply Pin. This pin is normally connected to ground.

**INC1 (Pin 6):** Inverting Input of Comparator 1. The second input of this comparator is internally connected to the 400mV reference.

**INC2 (Pin 7):** Input of Comparator 2. For the LT6119-1 this is the noninverting input of comparator 2. For the LT6119-2 this is the inverting input of comparator 2. The second input of each of these comparators is internally connected to the 400mV reference.

**OUTA (Pin 8):** Current Output of the Sense Amplifier. This pin will source a current that is equal to the sense voltage divided by the external gain setting resistor, R<sub>IN</sub>.

**V**<sup>+</sup> (**Pin 9**): Positive Supply Pin. The V<sup>+</sup> pin can be connected directly to either side of the sense resistor,  $R_{SENSE}$ . When V<sup>+</sup> is tied to the load end of the sense resistor, the SENSEHI pin can go up to 0.2V above V<sup>+</sup>. Supply current is drawn through this pin.

**SENSEHI (Pin 10):** Sense Amplifier Input. The internal sense amplifier will drive SENSEHI to the same potential as SENSELO. A resistor (typically  $R_{IN}$ ) tied from supply to SENSEHI sets the output current,  $I_{OUT} = V_{SENSE}/R_{IN}$ , where  $V_{SENSE}$  is the voltage developed across  $R_{SENSE}$ .

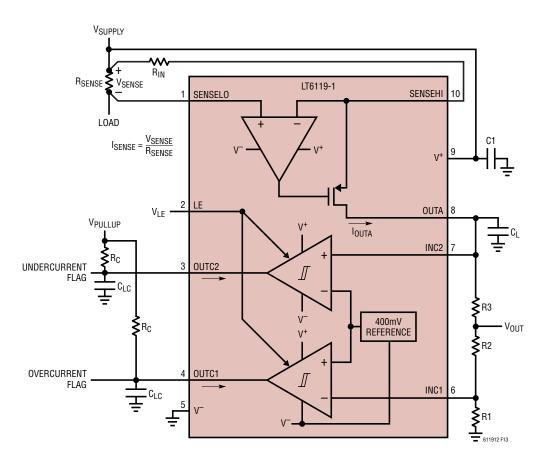

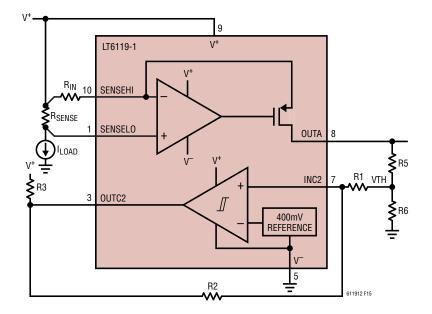

### **BLOCK DIAGRAMS**

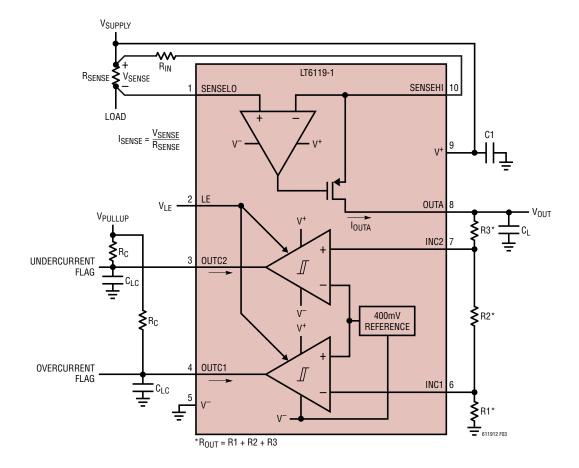

Figure 1. LT6119-1 Block Diagram (Comparators with Opposing Polarity)

611912f

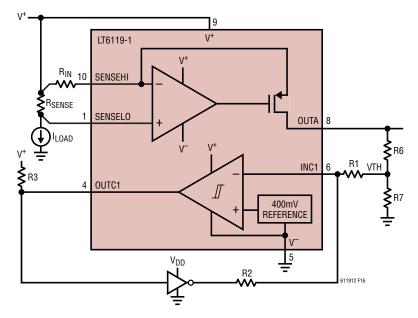

### **BLOCK DIAGRAMS**

Figure 2. LT6119-2 Block Diagram (Comparators with the Same Polarity)

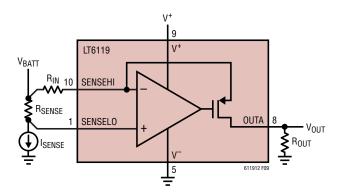

The LT6119 high side current sense amplifier provides accurate monitoring of currents through an external sense resistor. The input sense voltage is level-shifted from the sensed power supply to a ground referenced output and is amplified by a user-selected gain to the output. The output voltage is directly proportional to the current flowing through the sense resistor.

The LT6119 comparators have a threshold set with a built-in 400mV precision reference and have 10mV of hysteresis. The open-drain outputs can be easily used to level shift to digital supplies.

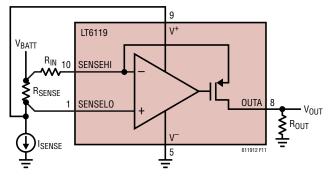

### Amplifier Theory of Operation

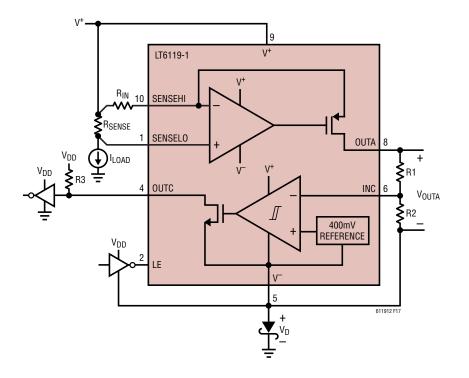

An internal sense amplifier loop forces SENSEHI to have the same potential as SENSELO, as shown in Figure 3. Connecting an external resistor,  $R_{IN}$ , between SENSEHI and  $V_{SUPPLY}$  forces a potential,  $V_{SENSE}$ , across  $R_{IN}$ . A corresponding current,  $I_{OUTA}$ , equal to  $V_{SENSE}/R_{IN}$ , will flow through  $R_{IN}$ . The high impedance inputs of the sense amplifier do not load this current, so it will flow through an internal MOSFET to the output pin, OUTA.

The output current can be transformed back into a voltage by adding a resistor from OUTA to  $V^-$ (typically ground). The output voltage is then:

$V_{OUT} = V^- + I_{OUTA} \bullet R_{OUT}$

where  $R_{OUT} = R1 + R2 + R3$ , as shown in Figure 3.

#### Table 1. Example Gain Configurations

|  | GAIN | N $R_{IN}$ $R_{OUT}$ $V_{SENSE}$ FOR $V_{OUT}$ = 5V |     | I <sub>OUTA</sub> AT V <sub>OUT</sub> = 5V |       |  |

|--|------|-----------------------------------------------------|-----|--------------------------------------------|-------|--|

|  | 20   | 499Ω                                                | 10k | 250mV                                      | 500µA |  |

|  | 50   | 200Ω                                                | 10k | 100mV                                      | 500µA |  |

|  | 100  | 100Ω                                                | 10k | 50mV                                       | 500µA |  |

### **Useful Equations**

Input Voltage:

$$V_{SENSE} = I_{SENSE} \bullet R_{SENSE}$$

Voltage Gain:  $\frac{V_{OUT}}{V_{SENSE}} = \frac{R_{OUT}}{R_{IN}}$

Current Gain:  $\frac{I_{OUTA}}{I_{SENSE}} = \frac{R_{SENSE}}{R_{IN}}$

Note that  $V_{SENSE(MAX)}$  can be exceeded without damaging the amplifier, however, output accuracy will degrade as  $V_{SENSE}$  exceeds  $V_{SENSE(MAX)}$ , resulting in increased output current,  $I_{OUTA}$ .

#### Selection of External Current Sense Resistor

The external sense resistor,  $\mathsf{R}_{\text{SENSE}}$ , has a significant effect on the function of a current sensing system and must be chosen with care.

First, the power dissipation in the resistor should be considered. The measured load current will cause power dissipation as well as a voltage drop in  $R_{SENSE}$ . As a result, the sense resistor should be as small as possible while still providing the input dynamic range required by the measurement. Note that the input dynamic range is the difference between the maximum input signal and the minimum accurately reproduced signal, and is limited primarily by input DC offset of the internal sense amplifier of the LT6119. To ensure the specified performance,  $R_{SENSE}$  should be small enough that  $V_{SENSE}$  does not exceed  $V_{SENSE(MAX)}$  under peak load conditions. As an example, an application may require the maximum sense voltage be 100mV. If this application is expected to draw 2A at peak load,  $R_{SENSE}$  should be set to 50m $\Omega$ .

Once the maximum  $R_{SENSE}$  value is determined, the minimum sense resistor value will be set by the resolution or dynamic range required. The minimum signal that can be accurately represented by this sense amplifier is limited by the input offset. As an example, the LT6119 has a maximum input offset of 200µV. If the minimum current is 20mA, a sense resistor of 10m $\Omega$  will set V<sub>SENSE</sub> to 200µV. This is the same value as the input offset. A larger sense resistor will reduce the error due to offset by increasing the sense voltage for a given load current. Choosing a 50m $\Omega$  R<sub>SENSE</sub> will maximize the dynamic range and provide a system that has 100mV across the sense resistor at peak load (2A), while input offset causes an error equivalent to only 4mA of load current.

In the previous example, the peak dissipation in  $R_{SENSE}$  is 200mW. If a 5m $\Omega$  sense resistor is employed, then the effective current error is 40mA, while the peak sense voltage is reduced to 10mV at 2A, dissipating only 20mW.

611912f

The low offset and corresponding large dynamic range of the LT6119 make it more flexible than other solutions in this respect. The  $200\mu$ V maximum offset gives 68dB of dynamic range for a sense voltage that is limited to 500mV max.

#### Sense Resistor Connection

Kelvin connection of the SENSEHI and SENSELO inputs to the sense resistor should be used in all but the lowest power applications. Solder connections and PC board interconnections that carry high currents can cause significant error in measurement due to their relatively large resistances. One 10mm × 10mm square trace of 1oz copper is approximately 0.5m $\Omega$ . A 1mV error can be caused by as little as 2A flowing through this small interconnect. This will cause a 1% error for a full-scale V<sub>SENSE</sub> of 100mV. A 10A load current in the same interconnect will cause a 5% error for the same 100mV signal. By isolating the sense traces from the high current paths, this error can be reduced by orders of magnitude. A sense resistor with integrated Kelvin sense terminals will give the best results. Figure 3 illustrates the recommended method for connecting the SENSEHI and SENSELO pins to the sense resistor.

Figure 3. LT6119-1 Typical Connection

#### Selection of External Input Gain Resistor, $R_{IN}$

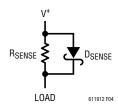

$R_{IN}$  should be chosen to allow the required speed and resolution while limiting the output current to 1mA. The maximum value for  $R_{IN}$  is 1k to maintain good loop stability. For a given  $V_{SENSE}$ , larger values of  $R_{IN}$  will lower power dissipation in the LT6119 due to the reduction in  $I_{OUT}$  while smaller values of  $R_{IN}$  will result in faster response time due to the increase in  $I_{OUT}$ . If low sense currents must be resolved accurately in a system that has a very wide dynamic range, a smaller  $R_{IN}$  may be used if the maximum  $I_{OUTA}$  current is limited in another way, such as with a Schottky diode across  $R_{SENSE}$  (Figure 4). This will reduce the high current measurement accuracy by limiting the result, while increasing the low current measurement resolution.

Figure 4. Shunt Diode Limits Maximum Input Voltage to Allow Better Low Input Resolution Without Overranging

This approach can be helpful in cases where occasional bursts of high currents can be ignored.

Care should be taken when designing the board layout for  $R_{IN}$ , especially for small  $R_{IN}$  values. All trace and interconnect resistances will increase the effective  $R_{IN}$  value, causing a gain error.

The power dissipated in the sense resistor can create a thermal gradient across a printed circuit board and consequently a gain error if  $R_{\rm IN}$  and  $R_{\rm OUT}$  are placed such that they operate at different temperatures. If significant power is being dissipated in the sense resistor then care should be taken to place  $R_{\rm IN}$  and  $R_{\rm OUT}$  such that the gain error due to the thermal gradient is minimized.

### Selection of External Output Gain Resistor, ROUT

The output resistor,  $R_{OUT}$ , determines how the output current is converted to voltage.  $V_{OUT}$  is simply  $I_{OUTA} \bullet R_{OUT}$ . Typically,  $R_{OUT}$  is a combination of resistors configured

as a resistor divider which has voltage taps going to the comparator inputs to set the comparator thresholds.

In choosing an output resistor, the maximum output voltage must first be considered. If the subsequent circuit is a buffer or ADC with limited input range, then  $R_{OUT}$  must be chosen so that  $I_{OUTA(MAX)} \bullet R_{OUT}$  is less than the allowed maximum input range of this circuit.

In addition, the output impedance is determined by  $R_{OUT}$ . If another circuit is being driven, then the input impedance of that circuit must be considered. If the subsequent circuit has high enough input impedance, then almost any useful output impedance will be acceptable. However, if the subsequent circuit has relatively low input impedance, or draws spikes of current such as an ADC load, then a lower output impedance may be required to preserve the accuracy of the output. More information can be found in the Output Filtering section. As an example, if the input impedance of the driven circuit,  $R_{IN(DRIVEN)}$ , is 100 times  $R_{OUT}$ , then the accuracy of  $V_{OUT}$  will be reduced by 1% since:

$$V_{OUT} = I_{OUTA} \bullet \frac{R_{OUT} \bullet R_{IN(DRIVEN)}}{R_{OUT} + R_{IN(DRIVEN)}}$$

$$= I_{OUTA} \bullet R_{OUT} \bullet \frac{100}{101} = 0.99 \bullet I_{OUTA} \bullet R_{OUT}$$

#### **Amplifier Error Sources**

The current sense system uses an amplifier and resistors to apply gain and level-shift the result. Consequently, the output is dependent on the characteristics of the amplifier, such as gain error and input offset, as well as the matching of the external resistors.

Ideally, the circuit output is:

$$V_{OUT} = V_{SENSE} \bullet \frac{R_{OUT}}{R_{IN}}; V_{SENSE} = R_{SENSE} \bullet I_{SENSE}$$

In this case, the only error is due to external resistor mismatch, which provides an error in gain only. However, offset voltage, input bias current and finite gain in the amplifier can cause additional errors:

Output Voltage Error,  $\Delta V_{OUT(VOS)},$  Due to the Amplifier DC Offset Voltage,  $V_{OS}$

$$\Delta V_{OUT(VOS)} = V_{OS} \bullet \frac{R_{OUT}}{R_{IN}}$$

The DC offset voltage of the amplifier adds directly to the value of the sense voltage,  $V_{\text{SENSE}}$ . As  $V_{\text{SENSE}}$  is increased, accuracy improves. This is the dominant error of the system and it limits the available dynamic range.

# Output Voltage Error, $\Delta V_{OUT(IBIAS)},$ Due to the Bias Currents $I_B^+$ and $I_B^-$

The amplifier bias current  $I_B^+$  flows into the SENSELO pin while  $I_B^-$  flows into the SENSEHI pin. The error due to  $I_B$  is the following:

$$\Delta V_{OUT(IBIAS)} = R_{OUT} \left( I_{B}^{+} \bullet \frac{R_{SENSE}}{R_{IN}} - I_{B}^{-} \right)$$

Since  $I_B^+ \approx I_B^- = I_{BIAS}$ , if  $R_{SENSE} << R_{IN}$  then,

$\Delta V_{OUT(IBIAS)} = -R_{OUT} (I_{BIAS})$

It is useful to refer the error to the input:

$\Delta V_{VIN(IBIAS)} = -R_{IN} (I_{BIAS})$

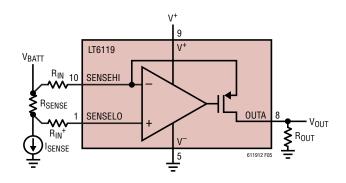

Figure 5.  $R_{IN}^{+}$  Reduces Error Due to  $I_{B}$

For instance, if  $I_{BIAS}$  is 100nA and  $R_{IN}$  is 1k, the input referred error is 100µV. This error becomes less significant as the value of  $R_{IN}$  decreases. The bias current error can be reduced if an external resistor,  $R_{IN}^+$ , is connected as shown in Figure 5, the error is then reduced to:

$$V_{OUT(IBIAS)} = \pm R_{OUT} \bullet I_{OS}; I_{OS} = I_B^+ - I_B^-$$

Minimizing low current errors will maximize the dynamic range of the circuit.

# Output Voltage Error, $\Delta V_{OUT(GAIN\;ERROR)},$ Due to External Resistors

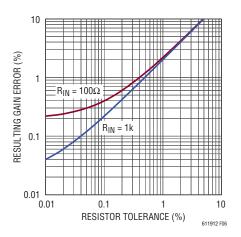

The LT6119 exhibits a very low gain error. As a result, the gain error is only significant when low tolerance resistors are used to set the gain. Note the gain error is systematically negative. For instance, if 0.1% resistors are used for R<sub>IN</sub> and R<sub>OUT</sub> then the resulting worst-case gain error is –0.4% with R<sub>IN</sub> = 100 $\Omega$ . Figure 6 is a graph of the maximum gain error which can be expected versus the external resistor tolerance.

Figure 6. Gain Error vs Resistor Tolerance

#### **Output Current Limitations Due to Power Dissipation**

The LT6119 can deliver a continuous current of 1mA to the OUTA pin. This current flows through  $R_{IN}$  and enters the current sense amplifier via the SENSEHI pin. The power dissipated in the LT6119 due to the output signal is:

$P_{OUT} = (V_{SENSEHI} - V_{OUTA}) \bullet I_{OUTA}$

Since  $V_{SENSEHI} \approx V^+$ ,  $P_{OUTA} \approx (V^+ - V_{OUTA}) \bullet I_{OUTA}$

There is also power dissipated due to the quiescent power supply current:

$P_S = I_S \bullet V^+$

The comparator output current flows into the comparator output pin and out of the  $V^-$  pin. The power dissipated in the LT6119 due to each comparator is often insignificant and can be calculated as follows:

$\mathsf{P}_{\mathsf{OUTC1,C2}} = (\mathsf{V}_{\mathsf{OUTC1,C2}} - \mathsf{V}^{-}) \bullet \mathsf{I}_{\mathsf{OUTC1,C2}}$

The total power dissipated is the sum of these dissipations:

$P_{TOTAL} = P_{OUTA} + P_{OUTC1} + P_{OUTC2} + P_{S}$

At maximum supply and maximum output currents, the total power dissipation can exceed 100mW. This will cause significant heating of the LT6119 die. In order to prevent damage to the LT6119, the maximum expected dissipation in each application should be calculated. This

number can be multiplied by the  $\theta_{JA}$  value, 160°C/W, to find the maximum expected die temperature. Proper heat sinking and thermal relief should be used to ensure that the die temperature does not exceed the maximum rating.

### LE Pin

The LE pin is used to enable the comparator's output latch. When the LE pin is high, the output latch is enabled and the comparator outputs will stay low once tripped. When LE is low, the comparator output latches are disabled and the comparators operate transparently. To continuously operate the comparators transparently, the LE pin should be grounded. Do not leave the LE pin floating.

#### **Power-On Reset**

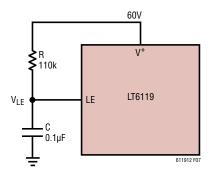

During start-up, the state of the comparator outputs cannot be guaranteed. To guarantee the correct state of the comparators outputs on start-up, a power-on reset (POR) is required. A POR can be implemented by holding the LE pin low until the LT6119 is in such a state that the comparator outputs are stable. This can be achieved by using an RC network between the LE, V<sup>+</sup> and GND, as shown in Figure 7. When power is applied to the LT6119, the RC network causes the voltage on the LE pin to remain below the V<sub>IL</sub> (0.5V) threshold long enough for the comparator outputs to settle into the correct state. The LE pin should remain below 0.5V for at least 100µs after power-up in order to

Figure 7. RC Network Achieves Power-On Reset

guarantee a valid comparator outputs. The RC value can be determined with the following equation:

$$RC = \frac{t}{\ln\left(\frac{V^+}{V^+ - 0.5V}\right)}; \quad t \ge 100 \mu S$$

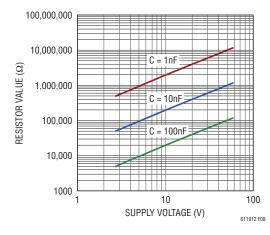

The RC will need to be chosen based on the supply voltage of the circuit. Figure 8 can be used to easily determine an appropriate RC combination for an applications supply voltage range.

Figure 8. Minimum Resistance for Three Typical Capacitor Values

#### **Output Filtering**

The AC output voltage, V<sub>OUT</sub>, is simply I<sub>OUTA</sub> • Z<sub>OUT</sub>. This makes filtering straightforward. Any circuit may be used which generates the required Z<sub>OUT</sub> to get the desired filter response. For example, a capacitor in parallel with R<sub>OUT</sub> will give a lowpass response. This will reduce noise at the output, and may also be useful as a charge reservoir to keep the output steady while driving a switching circuit such as a MUX or ADC. This output capacitor in parallel with R<sub>OUT</sub> will create an output pole at:

$$f_{-3dB} = \frac{1}{2 \bullet \pi \bullet R_{OUT} \bullet C_L}$$

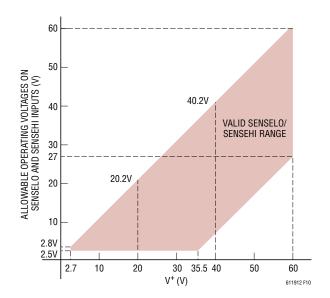

#### SENSELO, SENSEHI Range

The difference between  $V_{BATT}$  (see Figure 9) and V<sup>+</sup>, as well as the maximum value of  $V_{SENSE}$ , must be considered to ensure that the SENSELO pin does not exceed the range listed in the Electrical Characteristics table. The SENSELO and SENSEHI pins of the LT6119 can function from 0.2V above the positive supply to 33V below it. These operating voltages are limited by internal diode clamps shown in Figures 1 and 2. On supplies less than 35.5V, the lower range is limited by V<sup>-</sup> + 2.5V. This allows the monitored supply, V<sub>BATT</sub>, to be separate from the LT6119 positive supply, as shown in Figure 9. Figure 10 shows the range of operating voltages for the SENSELO and SENSEHI inputs, for different supply voltage inputs (V<sup>+</sup>).

Figure 9. V<sup>+</sup> Powered Separately from Load Supply ( $V_{BATT}$ )

#### Figure 10. Allowable SENSELO, SENSEHI Voltage Range

611912f

The SENSELO and SENSEHI range has been designed to allow the LT6119 to monitor its own supply current (in addition to the load), as long as  $V_{\text{SENSE}}$  is less than 200mV. This is shown in Figure 11.

#### Minimum Output Voltage

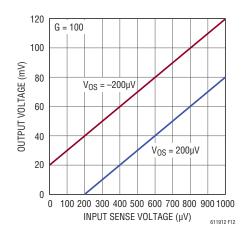

The output of the LT6119 current sense amplifier can produce a non-zero output voltage when the sense voltage is zero. This is a result of the sense amplifier  $V_{OS}$  being forced across  $R_{IN}$  as discussed in the Output Voltage Error,  $\Delta V_{OUT(VOS)}$  section. Figure 12 shows the effect of the input offset voltage on the transfer function for parts at the  $V_{OS}$  limits. With a negative offset voltage, zero input sense voltage produces an output voltage. With a positive offset voltage, the output voltage is zero until the input sense voltage exceeds the input offset voltage. Neglecting  $V_{OS}$ , the output circuit is not limited by saturation of pull-down circuitry and can reach OV.

#### **Response Time**

The LT6119 amplifier is designed to exhibit fast response to inputs for the purpose of circuit protection or current monitoring. This response time will be affected by the external components in two ways, delay and speed.

If the output current is very low and an input transient occurs, there may be an increased delay before the output voltage begins to change. The Typical Performance Characteristics show that this delay is short and it can be improved by increasing the minimum output current, either by increasing  $R_{SENSE}$  or decreasing  $R_{IN}$ . Note that the Typical Performance Characteristics are labeled with respect to the initial sense voltage.

The speed is also affected by the external components. Using a larger  $R_{OUT}$  will decrease the response time, since  $V_{OUT} = I_{OUTA} \bullet Z_{OUT}$  where  $Z_{OUT}$  is the parallel combination

Figure 11. LT6119 Supply Current Monitored with Load

Figure 12. Amplifier Output Voltage vs Input Sense Voltage

of  $R_{OUT}$  and any parasitic and/or load capacitance. Note that reducing  $R_{IN}$  or increasing  $R_{OUT}$  will both have the effect of increasing the voltage gain of the circuit. If the output capacitance is limiting the speed of the system,  $R_{IN}$  and  $R_{OUT}$  can be decreased together in order to maintain the desired gain and provide more current to charge the output capacitance.

The response time of the comparators is the sum of the propagation delay and the fall time. The propagation delay is a function of the overdrive voltage on the input of the comparators. A larger overdrive will result in a lower propagation delay. This helps achieve a fast system response time to fault events. The fall time is affected by the load on the output of the comparator as well as the pull-up voltage.

The LT6119 amplifier has a typical response time of 500ns and the comparators have a typical response time of 500ns. When configured as a system, the amplifier output drives the comparator input causing a total system response time which is typically greater than that implied by the individually specified response times. This is due to the overdrive on the comparator input being determined by the speed of the amplifier output.

### **Internal Reference and Comparators**

The integrated precision reference and comparators combined with the high precision current sense allow for rapid and easy detection of abnormal load currents. This is often critical in systems that require high levels of safety and reliability. The LT6119 comparators are optimized for fault detection and are designed with latching outputs. Latching outputs prevent faults from clearing themselves and require a separate system or user to reset the outputs. In applications where the comparator output can intervene and disconnect loads from the supply, latched outputs are required to avoid oscillation. Latching outputs are also useful for detecting problems that are intermittent. The comparator outputs on the LT6119 are always latching and there is no way to disable this feature. Each of the comparators has one input available externally, with the two versions of the part differing by the polarity of those available inputs. The other comparator inputs are connected internally to the 400mV precision reference. The input threshold (the voltage which causes the output to transition from high to low) is designed to be equal to that of the reference. The reference voltage is established with respect to the device V<sup>-</sup> connection.

### **Comparator Inputs**

The comparator inputs can swing from V<sup>-</sup> to 60V regardless of the supply voltage used. The input current for inputs well above the threshold is just a few pAs. With decreasing input voltage, a small bias current begins to be drawn out of the input near the threshold, reaching 50nA max when at ground potential. Note that this change in input bias current can cause a small nonlinearity in the OUTA transfer function if the comparator inputs are coupled to the amplifier output with a voltage divider. For example, if the maximum comparator input current is 50nA, and the resistance seen looking out of the comparator input is 1k, then a change in output voltage of 50µV will be seen on the analog output when the comparator input voltage passes through its threshold. If both comparator inputs are connected to the output then they must both be considered.

### **Setting Comparator Thresholds**

The comparators have an internal precision 400mV reference. In order to set the trip points of the LT6119-1 comparators, the output currents,  $I_{OVER}$  and  $I_{UNDER}$ , as well as the maximum output current,  $I_{MAX}$ , must be calculated:

$$I_{OVER} = \frac{V_{SENSE(OVER)}}{R_{IN}}, I_{UNDER} = \frac{V_{SENSE(UNDER)}}{R_{IN}},$$

$$I_{MAX} = \frac{V_{SENSE(MAX)}}{R_{IN}}$$

where  $I_{OVER}$  and  $I_{UNDER}$  are the over and under currents through the sense resistor which cause the comparators to trip.  $I_{MAX}$  is the maximum current through the sense resistor.

Depending on the desired maximum amplifier output voltage ( $V_{MAX}$ ) the three output resistors, R1, R2 and R3, can be configured in two ways. If:

$$V_{MAX} > \left[\frac{400mV}{I_{OVER}} + \frac{400mV - I_{UNDER}(R1)}{I_{UNDER}}\right]I_{MAX}$$

then use the configuration shown in Figure 3. The desired trip points and full-scale analog output voltage for the circuit in Figure 3 can then be achieved using the following equations:

$$R1 = \frac{400 \text{mV}}{I_{\text{OVER}}}$$

$$R2 = \frac{400 \text{mV} - I_{\text{UNDER}} (\text{R1})}{I_{\text{UNDER}}}$$

$$R3 = \frac{V_{\text{MAX}} - I_{\text{MAX}} (\text{R1} + \text{R2})}{I_{\text{MAX}}}$$

If:

$$V_{\text{MAX}} < \left[\frac{400 \text{mV}}{I_{\text{OVER}}} + \frac{400 \text{mV} - I_{\text{UNDER}} (\text{R1})}{I_{\text{UNDER}}}\right] I_{\text{MAX}}$$

then use the configuration shown in Figure 13.

Figure 13. Typical Configuration with Alternative  $\mathbf{R}_{\text{OUT}}$  Configuration

The desired trip points and full-scale analog output voltage for the circuit in Figure 15 can be achieved as follows:

$$R1 = \frac{400 \text{mV}}{I_{\text{OVER}}}$$

$$R2 = \frac{V_{\text{MAX}} - I_{\text{MAX}} (\text{R1})}{I_{\text{MAX}}}$$

$$R3 = \frac{400 \text{mV} - I_{\text{UNDER}} (\text{R1} + \text{R2})}{I_{\text{UNDER}}}$$

Trip points for the LT6119-2 can be set by replacing  $I_{UNDER}$  with a second overcurrent,  $I_{OVER2}.$

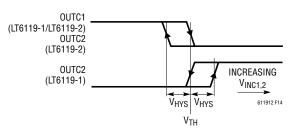

#### Hysteresis

Each comparator has a typical built-in hysteresis of 10mV to simplify design, ensure stable operation in the presence of noise at the inputs, and to reject supply noise that might be induced by state change load transients. The hysteresis is designed such that the threshold voltage is altered when the output is transitioning from low to high as is shown in Figure 14.

Figure 14. Comparator Output Transfer Characteristics

External positive feedback circuitry can be employed to increase the effective hysteresis if desired, but such circuitry will have an effect on both the rising and falling input thresholds,  $V_{TH}$  (the actual internal threshold remains unaffected).

Figure 15 shows how to add additional hysteresis to a noninverting comparator.

R6 can be calculated from the extra hysteresis being added,  $V_{HYS(EXTRA)}$  and the amplifier output current which you want to cause the comparator output to trip,  $I_{UNDER}$ . Note that the hysteresis being added,  $V_{HYS(EXTRA)}$ , is in addition to the typical 10mV of built-in hysteresis.

$$R6 = \frac{400mV - V_{HYS(EXTRA)}}{I_{UNDEB}}$$

Figure 15. Noninverting Comparator with Added Hysteresis

R1 should be chosen such that R1 >> R6 so that  $V_{\text{OUTA}}$  does not change significantly when the comparator trips.

R3 should be chosen to allow sufficient  $V_{\mbox{\scriptsize OL}}$  and comparator output rise time due to capacitive loading.

R2 can be calculated:

$$R2 = \frac{R1 \cdot (V^{+} - 400mV) - (V_{HYS(EXTRA)} \cdot R3)}{V_{HYS(EXTRA)}}$$

For very large values of R2 PCB related leakage may become an issue. A tee network can be implemented to reduce the required resistor values.

The approximate total hysteresis will be:

$$V_{HYS} = 10mV + R1 \cdot \left(\frac{V^+ - 400mV}{R2 + R3}\right)$$

For example, to achieve  $I_{UNDER} = 100\mu A$  with 50mV of total hysteresis, R6 = 3.57k. Choosing R1 = 35.7k, R3 = 10k and V<sup>+</sup> = 5V results in R2 = 4.12M.

The analog output voltage will also be affected when the comparator trips due to the current injected into R6 by the positive feedback. Because of this, it is desirable to

have (R1 + R2 + R3) >> R6. The maximum V<sub>OUTA</sub> error caused by this can be calculated as:

$$\Delta V_{\text{OUTA}} = V^+ \bullet \left(\frac{\text{R6}}{\text{R1} + \text{R2} + \text{R3} + \text{R6}}\right)$$

In the previous example, this is an error of 4.3mV at the output of the amplifier or  $43\mu$ V at the input of the amplifier assuming a gain of 100.

When using the comparators with their inputs decoupled from the output of the amplifier, they may be driven directly by a voltage source. It is useful to know the threshold voltage equations with the additional hysteresis. The input falling edge threshold which causes the output to transition from high to low is:

$$V_{TH(F)} = 400 \text{mV} \bullet \text{R1} \bullet \left(\frac{1}{\text{R1}} + \frac{1}{\text{R2} + \text{R3}}\right) - \left(\frac{\text{V}^+ \bullet \text{R1}}{\text{R2} + \text{R3}}\right)$$

The input rising edge threshold which causes the output to transition from low to high is:

$$V_{TH(R)} = 410 \text{mV} \bullet \text{R1} \bullet \left(\frac{1}{\text{R1}} + \frac{1}{\text{R2}}\right)$$

Figure 16 shows how to add additional hysteresis to an inverting comparator.

Figure 16. Inverting Comparator with Added Hysteresis

R7 can be calculated from the amplifier output current which is required to cause the comparator output to trip,  $I_{OVER}$ .

$$R7 = \frac{400mV}{I_{OVER}}$$

, Assuming (R1+R2) >> R7

To ensure (R1 + R2) >> R7, R1 should be chosen such that R1 >> R7 so that  $V_{OUTA}$  does not change significantly when the comparator trips.

R3 should be chosen to allow sufficient  $V_{OL}$  and comparator output rise time due to capacitive loading.

R2 can be calculated:

$$R2 = R1 \bullet \left(\frac{V_{DD} - 390mV}{V_{HYS(EXTRA)}}\right)$$

Note that the hysteresis being added,  $V_{HYS(EXTRA)}$ , is in addition to the typical 10mV of built-in hysteresis. For very large values of R2 PCB related leakage may become an issue. A tee network can be implemented to reduce the required resistor values.

The approximate total hysteresis is:

$$V_{HYS} = 10mV + R1 \bullet \left(\frac{V_{DD} - 390mV}{R2}\right)$$

For example, to achieve  $I_{OVER} = 900\mu$ A with 50mV of total hysteresis, R7 = 442 $\Omega$ . Choosing R1 = 4.42k, R3 = 10k and V<sub>DD</sub> = 5V results in R2 = 513k.

The analog output voltage will also be affected when the comparator trips due to the current injected into R7 by the positive feedback. Because of this, it is desirable to have (R1 + R2) >> R7. The maximum  $V_{OUTA}$  error caused by this can be calculated as:

$$\Delta V_{\text{OUTA}} = V_{\text{DD}} \bullet \left(\frac{\text{R7}}{\text{R1} + \text{R2} + \text{R7}}\right)$$

In the previous example, this is an error of 4.3mV at the output of the amplifier or  $43\mu$ V at the input of the amplifier assuming a gain of 100.

Since the comparators can be used independently of the current sense amplifier, it is useful to know the threshold voltage equations with additional hysteresis. The input rising edge threshold which causes the output to transition from high to low is:

$$V_{\rm TH(R)} = 400 \,{\rm mV} \cdot \left(1 + \frac{{\rm R1}}{{\rm R2}}\right)$$

The input falling edge threshold which causes the output to transition from low to high is:

$$V_{TH(F)} = 390 \text{mV} \cdot \left(1 + \frac{\text{R1}}{\text{R2}}\right) - V_{DD}\left(\frac{\text{R1}}{\text{R2}}\right)$$

#### **Comparator Outputs**

The comparator outputs can maintain a logic low level of 150mV while sinking 500 $\mu$ A. The outputs can sink higher currents at elevated V<sub>OL</sub> levels, as shown in the Typical Performance Characteristics. Load currents are conducted to the V<sup>-</sup> pin. The output off-state voltage may range between 0V and 60V with respect to V<sup>-</sup>, regardless of the supply voltage used. As with any open-drain device, the outputs may be tied together to implement wire-OR logic functions. The LT6119-1 can be used as a single-output window comparator in this way.

#### **Reverse-Supply Protection**

The LT6119 is not protected internally from external reversal of supply polarity. To prevent damage that may occur during this condition, a Schottky diode should be added in series with V<sup>-</sup> (Figure 17). This will limit the reverse current through the LT6119. Note that this diode will limit the low voltage operation of the LT6119 by effectively reducing the supply voltage to the part by V<sub>D</sub>.

Also note that the comparator reference, comparator output and LE input are referenced to the  $V^-$  pin. In

order to preserve the precision of the reference and to avoid driving the comparator inputs below V<sup>-</sup>, R2 must connect to the V<sup>-</sup> pin. This will shift the amplifier output voltage up by V<sub>D</sub>. V<sub>OUTA</sub> can be accurately measured differentially across R1 and R2. The comparator output low voltage will also be shifted up by V<sub>D</sub>. The LE pin threshold is referenced to the V<sup>-</sup> pin. In order to provide valid input levels to the LT6119 and avoid driving LE below V<sup>-</sup> the negative supply of the driving circuit should be tied to V<sup>-</sup>.

Figure 17. Schottky Prevents Damage During Supply Reversal

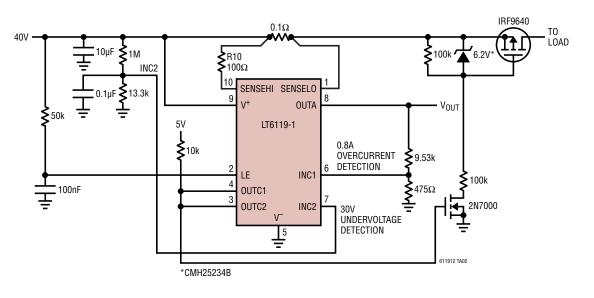

### TYPICAL APPLICATIONS

Electronic Fuse and Undervoltage Detector with Power-On Reset

The electronic fuse can be reset either by pulling the LE line low or by cycling the power to the system. The circuit is designed to have a  $100\mu$ S power-on period. After power, while LE is still below the threshold, the comparator is kept transparent to allow for initial inrush current.

The comparators monitor for overcurrent and undervoltage conditions. If either fault condition is detected the battery will immediately be disconnected from the load. The latching comparator outputs ensure the battery stays disconnected from the load until an outside source resets the LT6119 comparator outputs.

### TYPICAL APPLICATIONS

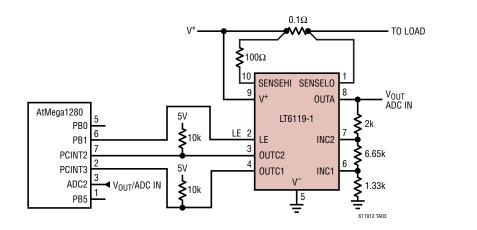

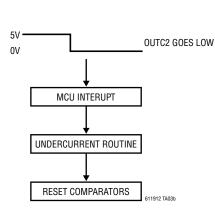

#### MCU Interfacing with Hardware Interrupts

The comparators are set to have a 50mA undercurrent threshold and a 300mA overcurrent threshold. The MCU

will receive the comparator outputs as hardware interrupts and immediately run an appropriate fault routine.

Example:

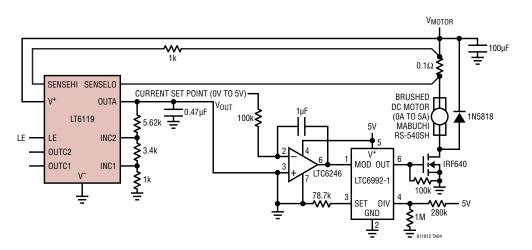

Simplified DC Motor Torque Control

The figure shows a simplified DC motor control circuit. The circuit controls motor current, which is proportional to motor torque; the LT6119 is used to provide current feedback to a difference amplifier that controls the current in the motor. The LTC<sup>®</sup>6992 is used to convert the output of the difference amp to the motors PWM control signal.

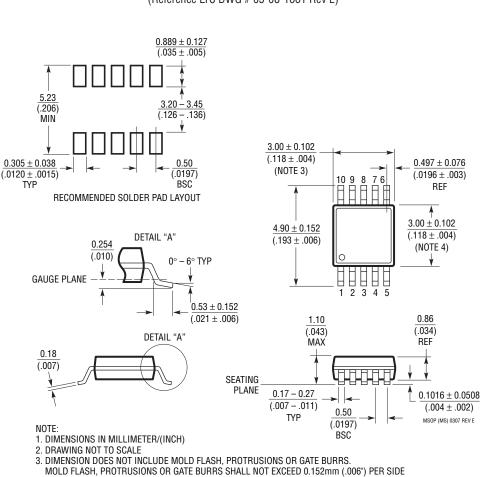

### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

**MS Package 10-Lead Plastic MSOP** (Reference LTC DWG # 05-08-1661 Rev E)

4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

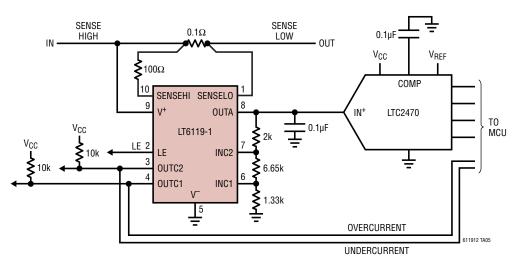

### TYPICAL APPLICATION

**ADC Driving Application**

The low sampling current of the LTC2470 16-bit delta sigma ADC is ideal for the LT6119.

### **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                                    | COMMENTS                                                                   |

|-------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| LT1787      | Bidirectional High Side Current Sense Amplifier                                | 2.7V to 60V, 75µV Offset, 60µA Quiescent, 8V/V Gain                        |

| LTC4150     | Coulomb Counter/Battery Gas Gauge                                              | Indicates Charge Quantity and Polarity                                     |

| LT6100      | Gain-Selectable High Side Current Sense Amplifier                              | 4.1V to 48V, Gain Settings: 10, 12.5, 20, 25, 40, 50V/V                    |

| LTC6101     | High Voltage High Side Current Sense Amplifier                                 | Up to 100V, Resistor Set Gain, 300µV Offset, SOT-23                        |

| LTC6102     | Zero-Drift High Side Current Sense Amplifier                                   | Up to 100V, Resistor Set Gain, 10µV Offset, MSOP8/DFN                      |

| LTC6103     | Dual High Side Current Sense Amplifier                                         | 4V to 60V, Resistor Set Gain, 2 Independent Amps, MSOP8                    |

| LTC6104     | Bidirectional High Side Current Sense Amplifier                                | 4V to 60V, Separate Gain Control for Each Direction, MSOP8                 |

| LT6105      | Precision Rail-to-Rail Input Current Sense Amplifier                           | –0.3V to 44V Input Range, 300µV Offset, 1% Gain Error                      |

| LT6106      | Low Cost High Side Current Sense Amplifier                                     | 2.7V to 36V, 250µV Offset, Resistor Set Gain, SOT-23                       |

| LT6107      | High Temperature High Side Current Sense Amplifier                             | 2.7V to 36V, -55°C to 150°C, Fully Tested: -55°C, 25°C, 150°C              |

| LT6108      | High Side Current Sense Amplifier with Reference and Comparator with Shutdown  | 2.7V to 60V, 125 $\mu V$ Offset, Resistor Set Gain, ±1.25% Threshold Error |

| LT6700      | Dual Comparator with 400mV Reference                                           | 1.4V to 18V, 6.5µA Supply Current                                          |

| LT6109      | High Side Current Sense Amplifier with Reference and Comparators with Shutdown | 2.7V to 60V, 125 $\mu$ V Offset, Resistor Set Gain, ±1.25% Threshold Error |

| LT6118      | LT6108 without Shutdown and POR Capability                                     | 2.7V to 60V, 200µV, Resistor Set Gain, ±1.25% Threshold Error              |