## 105V, 2.3A Low EMI Synchronous Step-Down Regulator

### **FEATURES**

- Wide V<sub>IN</sub> Range: 4.4V to 105V (110V Abs Max)

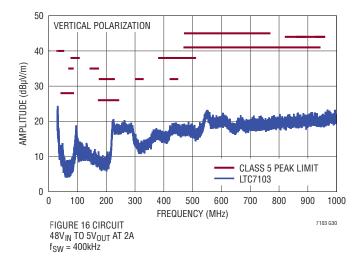

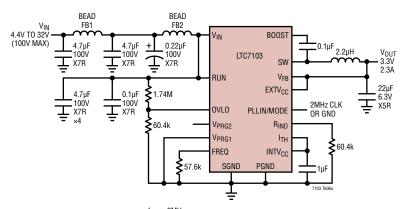

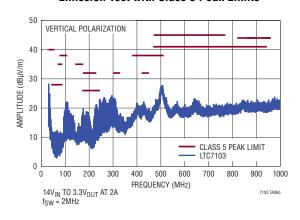

- Ultralow EMI/EMC Emissions: CISPR 25 Compliant

- 2μA I<sub>O</sub> When Regulating 48V<sub>IN</sub> to 3.3V<sub>OUT</sub>

- Fast and Accurate Output Current Programming and Monitoring with No External R<sub>SENSE</sub>

- Brick Wall Current Limit

- Low Minimum On-Time: 40ns

- Wide V<sub>OUT</sub> Range: 1V to V<sub>IN</sub>

- 100% Maximum Duty Cycle Operation

- Programmable Fixed Frequency: 200kHz to 2MHz

- Eight, Pin-Selectable Fixed (1.2V to 15V) or Adjustable Output Voltages

- Selectable Pulse-Skipping or Low Ripple Burst Mode® Operation at Light Loads

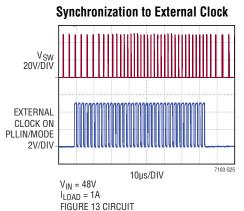

- PLL Synchronization to External Clock

- **EXTV**<sub>CC</sub> LDO Powers Chip from  $V_{OUT} = 3.3V$  to 40V

- OPTI-LOOP® or Fixed Internal Compensation

- Input and Output Overvoltage Protection

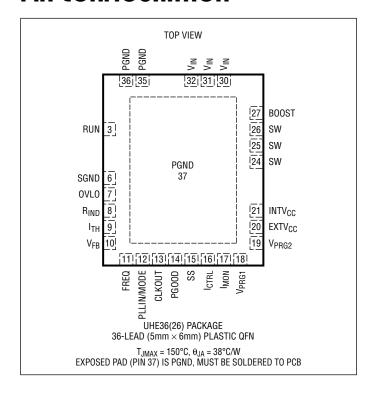

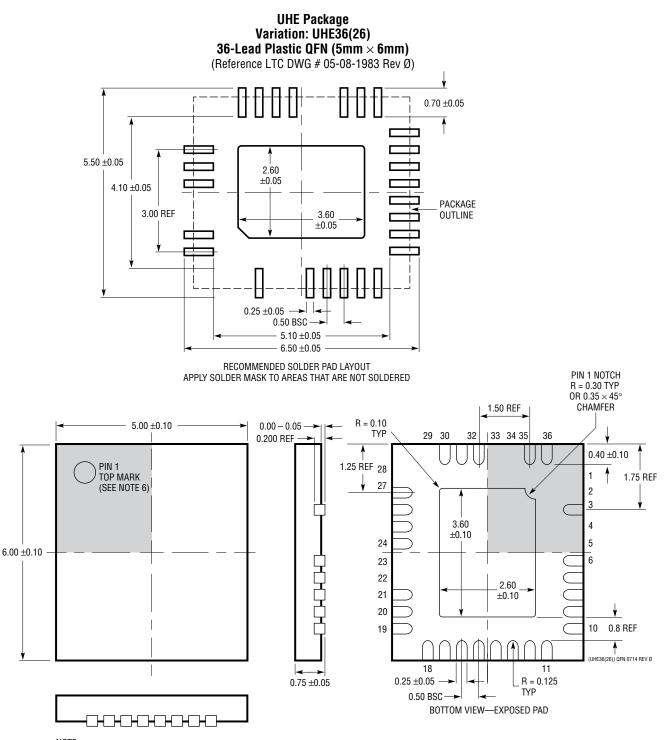

- Thermally Enhanced (5mm × 6mm) QFN Package

#### **APPLICATIONS**

- Battery Chargers and CC/CV Supplies

- Automotive and Military Systems

- Industrial, Avionics and Heavy Equipment

- Medical Instruments and Telecommunication Systems

### DESCRIPTION

The LTC®7103 is a high efficiency, monolithic synchronous step-down DC/DC converter utilizing a constant frequency, average current mode control architecture. It operates from an input voltage range of 4.4V to 105V and provides an adjustable regulated output voltage from 1V to  $V_{IN}$  while delivering up to 2.3A of output current.

The LTC7103 features high frequency operation and a low minimum on-time that reduce inductor size and enable constant-frequency operation even at very high step-down ratios. In addition, the LTC7103 achieves the lowest possible dropout voltage with 100% maximum duty cycle operation. During light load operation, converter efficiency and output ripple can be optimized by selecting Burst Mode or pulse-skipping operation.

The LTC7103 includes accurate, high speed average current programming and monitoring without the need for an external sense resistor. Additional features include a bypass LDO to maximize efficiency, fixed or adjustable output voltage and loop compensation, and a wide array of protection features to enhance reliability.

T, LT, LTC, LTM, Linear Technology, Burst Mode, OPTI-LOOP and the Linear logo are registered trademarks of Analog Devices, Inc. All other trademarks are the property of their respective owners.

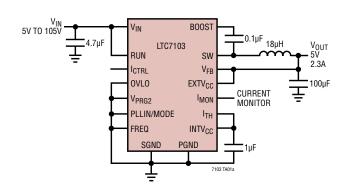

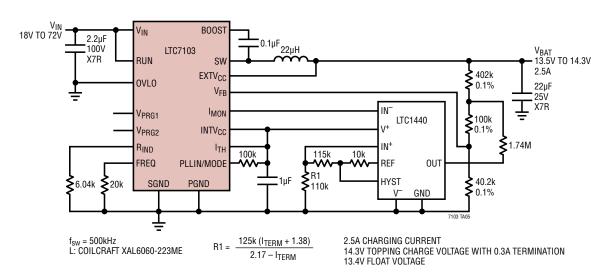

## TYPICAL APPLICATION

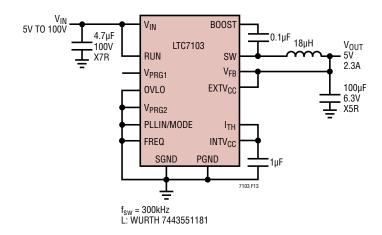

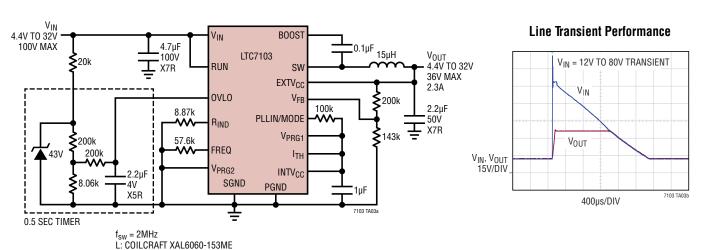

5V to 105V Input to 5V/2.3A Output Step-Down Regulator

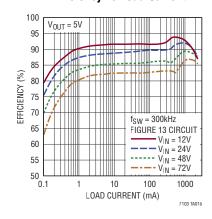

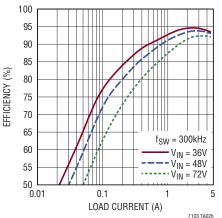

#### **Efficiency vs Load Current**

## **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| V <sub>IN</sub> Supply Voltage                                    | 0.3V to 110V               |

|-------------------------------------------------------------------|----------------------------|

| INTV <sub>CC</sub> , (BOOST-SW) Voltages                          | 0.3V to 6V                 |

| BOOST Voltage                                                     | 0.3V to 110V               |

| RUN Voltage                                                       | 0.3V to 110V               |

| V <sub>FB</sub> , PGOOD Voltages                                  | 0.3V to 16V                |

| EXTV <sub>CC</sub> Voltage                                        | 0.3V to 41V                |

| R <sub>IND</sub> , V <sub>PRG1</sub> , V <sub>PRG2</sub> Voltages | 0.3V to INTV <sub>CC</sub> |

| I <sub>CTRL</sub> , SS Voltages                | 0.3V to INTV <sub>CC</sub> |

|------------------------------------------------|----------------------------|

| FREQ, I <sub>TH</sub> , PLLIN/MODE, OVLO Volta | ages0.3V to 6V             |

| Operating Junction Temperature Ran             | ge (Notes 2, 3, 4)         |

| LTC7103E, LTC7103I                             | –40°C to 125°C             |

| LTC7103H                                       | –40°C to 150°C             |

| LTC7103MP                                      | –55°C to 150°C             |

| Storage Temperature Range                      | –65°C to 150°C             |

## PIN CONFIGURATION

## ORDER INFORMATION

(http://www.linear.com/product/LTC7103#orderinfo)

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|-------------------|

| LTC7103EUHE#PBF  | LTC7103EUHE#TRPBF  | 7103          | 36-Lead (5mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC7103IUHE#PBF  | LTC7103IUHE#TRPBF  | 7103          | 36-Lead (5mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC7103HUHE#PBF  | LTC7103HUHE#TRPBF  | 7103          | 36-Lead (5mm × 6mm) Plastic QFN | -40°C to 150°C    |

| LTC7103MPUHE#PBF | LTC7103MPUHE#TRPBF | 7103          | 36-Lead (5mm × 6mm) Plastic QFN | -55°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . (Note 2) $V_{IN} = 12 \,^{\circ}\text{V}$ unless otherwise noted.

| SYMBOL                      | PARAMETER                                   | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | MIN                                                                           | TYP                                                                           | MAX                                                                           | UNITS                      |

|-----------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------|

| Main Regul                  | ator and Voltage Loop                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | ,                                                                             |                                                                               |                                                                               |                            |

| $\overline{V_{\text{IN}}}$  | Operating Input Voltage Range               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 4.4                                                                           |                                                                               | 105                                                                           | V                          |

| V <sub>IN(UVLO)</sub>       | V <sub>IN</sub> Undervoltage Lockout        | V <sub>IN</sub> Rising<br>V <sub>IN</sub> Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | 4.36<br>4.11                                                                  | 4.50<br>4.25                                                                  | 4.64<br>4.39                                                                  | V                          |

| $\overline{V_{\text{OUT}}}$ | Operating Output Voltage Range              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 1.0                                                                           |                                                                               | 105                                                                           | ٧                          |

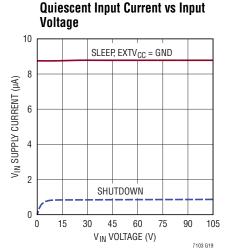

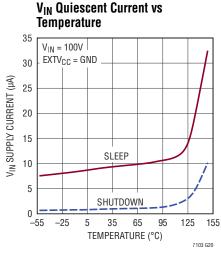

| Iq                          | V <sub>IN</sub> Input DC Supply Current     | (Note 8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                                                                               |                                                                               |                                                                               |                            |

|                             | Pulse-Skipping Mode                         | $V_{FB} = 1.04V$ , EXTV <sub>CC</sub> = 3.3V<br>$V_{FB} = 1.04V$ , EXTV <sub>CC</sub> = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                                               | 200<br>4.4                                                                    |                                                                               | μA<br>mA                   |

|                             | Sleep Mode                                  | $V_{FB} = 1.04V$ , EXTV <sub>CC</sub> = 3.3V<br>$V_{FB} = 1.04V$ , EXTV <sub>CC</sub> = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                                               | 1.0<br>9.0                                                                    |                                                                               | μ <i>Α</i><br>μ <i>Α</i>   |

|                             | Shutdown                                    | RUN = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                                                                               | 0.7                                                                           | 8.0                                                                           | μА                         |

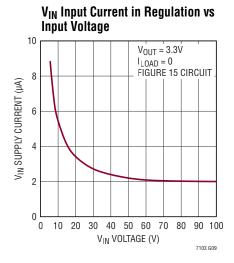

|                             | V <sub>IN</sub> Input Current In Regulation | Figure 13 Circuit, $V_{IN}$ = 48V, $I_{OUT}$ = 500 $\mu$ A<br>Figure 15 Circuit, $V_{IN}$ = 48V, $I_{OUT}$ = 0 $\mu$ A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                                               | 64<br>2                                                                       | 75                                                                            | μA<br>μA                   |

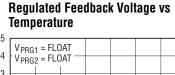

| V <sub>FB</sub>             | Regulated Feedback Voltage                  | $ \begin{array}{l} (\text{Note 5}) \\ I_{TH}  \text{Voltage} = 0.5 \text{V to } 1.2 \text{V, } V_{IN} = 4.5 \text{V to } 105 \text{V} \\ V_{PRG1} = V_{PRG2} = \text{FLOAT} \\ V_{PRG1} = V_{PRG2} = \text{INTV}_{CC} \\ V_{PRG1} = \text{FLOAT, } V_{PRG2} = \text{INTV}_{CC} \\ V_{PRG1} = V_{PRG2} = \text{SGND} \\ V_{PRG1} = \text{SGND, } V_{PRG2} = \text{FLOAT} \\ V_{PRG1} = \text{SGND, } V_{PRG2} = \text{INTV}_{CC} \\ V_{PRG1} = \text{FLOAT, } V_{PRG2} = \text{SGND} \\ V_{PRG1} = \text{INTV}_{CC, } V_{PRG2} = \text{FLOAT} \\ V_{PRG1} = \text{INTV}_{CC, } V_{PRG2} = \text{SGND} \\ V_{PRG1} = \text{INTV}_{CC, } V_{PRG2} = \text{SGND} \\ \end{array} $ | • | 0.990<br>1.182<br>1.770<br>2.455<br>3.234<br>3.528<br>4.900<br>11.75<br>14.70 | 1.000<br>1.200<br>1.800<br>2.500<br>3.300<br>3.600<br>5.000<br>12.00<br>15.00 | 1.010<br>1.218<br>1.827<br>2.537<br>3.350<br>3.654<br>5.075<br>12.24<br>15.30 | V<br>V<br>V<br>V<br>V<br>V |

|                             | Feedback Input Bias Current                 | V <sub>PRG1</sub> = V <sub>PRG2</sub> = FLOAT<br>V <sub>PRG1</sub> or V <sub>PRG2</sub> Tied to SGND or INTV <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                                               | ±2<br>1.25                                                                    | ±10<br>1.6                                                                    | nA<br>μA                   |

| g <sub>m</sub>              | Error Amplifier g <sub>m</sub>              | I <sub>TH</sub> = 1V, Sink/Source = 5μA (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |                                                                               | 1.52                                                                          |                                                                               | mS                         |

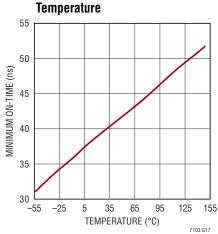

| t <sub>ON,MIN</sub>         | Minimum Controllable ON-Time                | (Note 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • |                                                                               | 40                                                                            | 60                                                                            | ns                         |

| R <sub>DS(ON)TOP</sub>      | Top Switch On-Resistance                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                                                               | 265                                                                           |                                                                               | mΩ                         |

| R <sub>DS(ON)BOT</sub>      | Bottom Switch On-Resistance                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                                                               | 142                                                                           |                                                                               | mΩ                         |

|                             | itrol and Monitoring                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                                                               | ,                                                                             |                                                                               | ļ.                         |

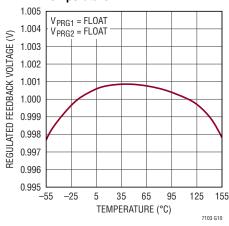

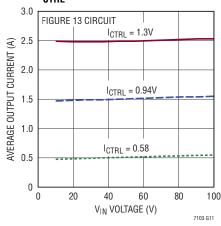

| I <sub>LIM(AVG)</sub>       | Average Output Current Limit                | (Note 6)<br>I <sub>CTRL</sub> = 1.3V<br>I <sub>CTRL</sub> = 0.58V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 2.25<br>0.36                                                                  | 2.50<br>0.5                                                                   | 2.75<br>0.64                                                                  | A                          |

| I <sub>PK</sub>             | Top Switch Peak Current Limit               | I <sub>CTRL</sub> = 1.3V<br>I <sub>CTRL</sub> = 0.58V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 3.32<br>1.56                                                                  | 3.70<br>1.70                                                                  | 4.30<br>2.09                                                                  | А                          |

| V <sub>IMON</sub>           | Current Monitor Output Voltage              | (Note 6)<br>I <sub>SW</sub> = 2A<br>I <sub>SW</sub> = 0.5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 1.04<br>0.54                                                                  | 1.12<br>0.58                                                                  | 1.19<br>0.63                                                                  | V                          |

|                             | I <sub>CTRL</sub> Pin Pull-Up Current       | V <sub>ICTRL</sub> = 0.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • | 18                                                                            | 20                                                                            | 22                                                                            | μА                         |

| Start-Up an                 | d Shutdown                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                                                               |                                                                               |                                                                               |                            |

| I <sub>SS</sub>             | Soft-Start Charge Current                   | SS = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | • | 8                                                                             | 11                                                                            | 14                                                                            | μА                         |

| t <sub>SS(INT)</sub>        | Internal Soft-Start Ramp Time               | SS = FLOAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                                               | 1.2                                                                           |                                                                               | ms                         |

| V <sub>FB(OV)</sub>         | Feedback Overvoltage Protection             | Relative to Regulated V <sub>FB</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 7                                                                             | 10                                                                            | 13                                                                            | %                          |

| V <sub>RUN(ON)</sub>        | RUN Pin ON Threshold                        | V <sub>RUN</sub> Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | • | 1.16                                                                          | 1.21                                                                          | 1.26                                                                          | ٧                          |

|                             | RUN Pin Hysteresis                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                                                               | 100                                                                           |                                                                               | m۷                         |

|                             | RUN Pin Leakage Current                     | RUN = 1.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | -10                                                                           | 0                                                                             | 10                                                                            | nA                         |

| V <sub>OV(R)</sub>          | OVLO Pin Rising Threshold                   | V <sub>OVLO</sub> Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • | 1.16                                                                          | 1.21                                                                          | 1.26                                                                          | V                          |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 2) $V_{IN} = 12V$ unless otherwise noted.

| SYMBOL              | PARAMETER                                                    | CONDITIONS                                                            |   | MIN          | TYP          | MAX          | UNITS |

|---------------------|--------------------------------------------------------------|-----------------------------------------------------------------------|---|--------------|--------------|--------------|-------|

|                     | OVLO Pin Hysteresis                                          |                                                                       |   |              | 65           |              | mV    |

|                     | OVLO Pin Leakage Current                                     | 0VL0 = 1.5V                                                           |   | -10          | 0            | 10           | nA    |

| Bias Regu           | lators and Housekeeping                                      |                                                                       |   |              |              |              |       |

|                     | INTV <sub>CC</sub> Undervoltage Lockout                      | INTV <sub>CC</sub> Rising<br>INTV <sub>CC</sub> Falling               |   |              | 3.00<br>2.80 |              | V     |

| V <sub>EXTVCC</sub> | EXTV <sub>CC</sub> Switchover Voltage                        | EXTV <sub>CC</sub> Rising<br>EXTV <sub>CC</sub> Falling               | • | 3.04<br>2.95 | 3.10<br>3.00 | 3.17<br>3.07 | V     |

|                     | Regulated INTV <sub>CC</sub> Voltage from V <sub>IN</sub>    |                                                                       |   | 3.37         | 3.5          | 3.6          | V     |

|                     | Regulated INTV <sub>CC</sub> Voltage from EXTV <sub>CC</sub> |                                                                       |   | 3.37         | 3.5          | 3.6          | V     |

| Oscillator          | and Phase-Locked Loop                                        |                                                                       |   |              |              |              |       |

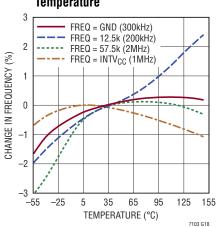

|                     | Programmable Frequency Accuracy                              | R <sub>FREQ</sub> = 12.5k (200kHz) to 57.5k (2MHz)<br>PLLIN/MODE = 0V | • | -15          |              | 15           | %     |

| f <sub>LOW</sub>    | Low Preset Frequency                                         | V <sub>FREQ</sub> = 0V;<br>PLLIN/MODE = 0V                            | • | 270          | 300          | 330          | kHz   |

| f <sub>HIGH</sub>   | High Preset Frequency                                        | V <sub>FREQ</sub> = INTV <sub>CC</sub> ;<br>PLLIN/MODE = 0V           | • | 0.9          | 1.0          | 1.1          | MHz   |

|                     | Synchronizable Frequency                                     | PLLIN/MODE = External Clock                                           | • | 200          |              | 2000         | kHz   |

|                     | PLLIN/MODE Input High Level for Clocking                     | PLLIN/MODE = External Clock                                           | • | 2.0          |              |              | V     |

|                     | PLLIN/MODE Input Low Level for Clocking                      | PLLIN/MODE = External Clock                                           | • |              |              | 0.8          | V     |

| PGOOD Ou            | tput                                                         |                                                                       |   |              | -            |              |       |

|                     | PGOOD Voltage Low                                            | I <sub>PGOOD</sub> = 1mA                                              |   |              | 0.3          | 0.5          | V     |

|                     | PGOOD Leakage Current                                        | V <sub>PGOOD</sub> = 12V                                              |   | -1           |              | 1            | μА    |

|                     | PGOOD Trip Level                                             | V <sub>FB</sub> with Respect to Set Regulated Voltage                 |   |              |              |              |       |

|                     |                                                              | V <sub>FB</sub> Ramping Positive                                      |   | 7            | 10           | 13           | %     |

|                     |                                                              | Hysteresis                                                            |   |              | 2.5          |              | %     |

|                     |                                                              | V <sub>FB</sub> Ramping Negative                                      |   | -13          | -10          | -7           | %     |

|                     |                                                              | Hysteresis                                                            |   |              | 2.5          |              | %     |

| $T_{PG}$            | Delay for Reporting a Fault                                  |                                                                       |   |              | 24           |              | μs    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC7103E is guaranteed to meet specifications from 0°C to 85°C with specifications over the -40°C to 125°C operating junction temperature range assured by design, characterization and correlation with statistical process controls. The LTC7103I is guaranteed over the -40°C to 125°C operating junction temperature range, the LTC7103H is guaranteed over the -40°C to 150°C operating junction temperature range, and the LTC7103MP is tested and guaranteed over the -55°C to 150°C operating junction temperatures degrade operating junction temperature range. High junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than 125°C. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

**Note 3:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:

$$T_J = T_A + (P_D \bullet \theta_{JA} \circ C/W)$$

**Note 4:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. The maximum rated junction temperature will be exceeded when this protection is active. Continuous operation above the specified absolute maximum operating junction temperature may impair device reliability or permanently damage the device. The overtemperature protection level is not production tested.

**Note 5:** The LTC7103 is tested in a feedback loop that servos  $V_{FB}$  to a voltage near the internal reference voltage to obtain the specified  $I_{TH}$  voltage.

**Note 6:** The Average Output Current Limit, the Top Switch Peak Current Limit and the Current Monitor Output Voltage are measured in a test circuit that simulates operation in a typical application.

**Note 7:** The minimum controllable on-time is measured in a test mode. (See Minimum ON-Time Considerations in the Applications Information section.)

**Note 8:** Dynamic supply current is higher due to the internal gate charge being delivered at the switching frequency.

$T_A = 25$ °C, unless otherwise noted.

71031

$T_A = 25$ °C, unless otherwise noted.

Average Output Current vs VIN,

**Average Output Current vs** Temperature

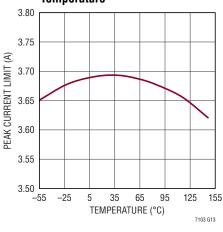

**Peak Current Limit vs Temperature**

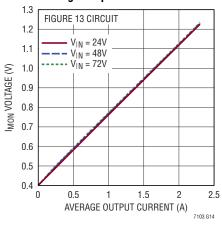

**Output Current Monitor vs Average Output Current**

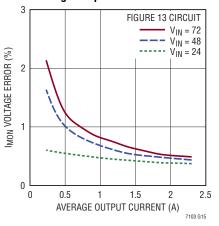

**Output Current Monitor Error vs Average Output Current**

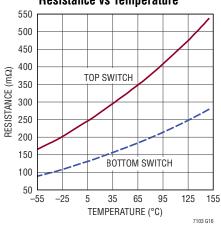

**Top and Bottom Switch** Resistance vs Temperature

Minimum On-Time vs

Oscillator Frequency vs **Temperature**

$T_A = 25$ °C, unless otherwise noted.

#### T<sub>A</sub> = 25°C, unless otherwise noted.

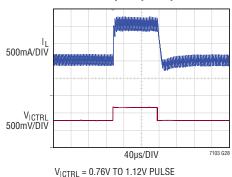

**ICTRL** Voltage to Inductor Current

$V_{ICTRL}$  = 0.76V TO 1.12V PULSE  $V_{IN}$  = 48V,  $V_{OUT}$  = 2V FIGURE 13 CIRCUIT

#### Gain vs Frequency ICTRL VOLTAGE TO INDUCTOR CURRENT GAIN (A/V) 3.5 3.0 2.5 BW = 94kHz2.0 1.5 $V_{\text{IN}} = 24V$ $V_{OUT} = 2V$ $R_{ICTRL} = 38.3k$ I<sub>OUT(AVG)</sub> = 1A f<sub>SW</sub> = 300kHz FIGURE 13 CIRCUIT

10

FREQUENCY (kHz)

300

7103 G29

100

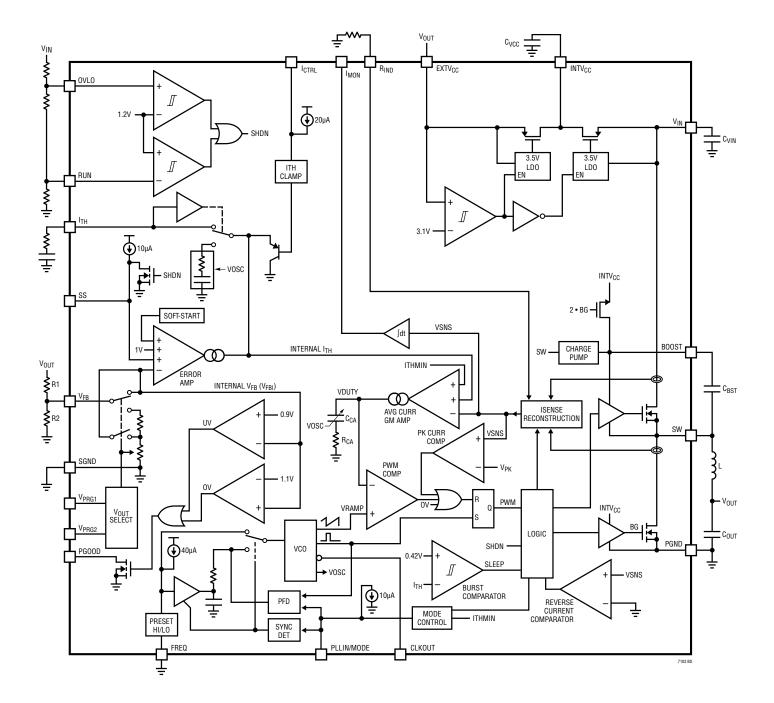

#### Radiated EMI Performance (CISPR25 Radiated **Emission Test with Class 5 Peak Limits)**

#### Radiated EMI Performance (CISPR25 Radiated **Emission Test with Class 5 Peak Limits)**

0.1

### PIN FUNCTIONS

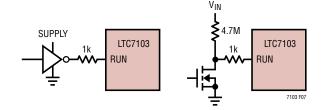

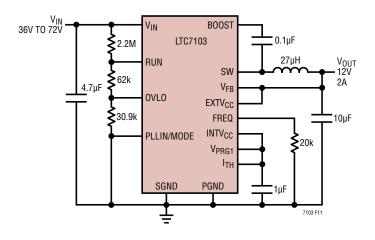

**RUN (Pin 3):** Run Control Input. Holding this pin below 1.1V shuts off the switching regulator. Holding this pin below 0.7V reduces the quiescent current to approximately 0.7 $\mu$ A. Place a resistor divider between V<sub>IN</sub> and this pin to use as an undervoltage lockout. Tie this pin to V<sub>IN</sub> to always enable the LTC7103.

SGND (Pin 6): Signal Ground.

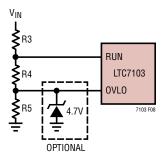

**OVLO (Pin 7):** Overvoltage Shutdown Input. If the voltage on this pin exceeds 1.21V, then the switching regulator is shut down and the SS pin is internally grounded. Tie this pin to SGND to allow operation with  $V_{IN}$  up to 105V.

**R<sub>IND</sub>** (**Pin 8**): Sets the current used to create an internal ramp that replicates the inductor current up-slope for low duty cycle operation. This pin generates a voltage that varies with the switching frequency. Place a resistor to SGND on this pin equal to  $1/(7.5 \cdot L)$  to set the internal ramp current. This pin can be left floating if fixed output voltage mode is selected using the  $V_{PRG1}$  and  $V_{PRG2}$  pins. If  $V_{PRG1}$  and  $V_{PRG2}$  are both floating, then a resistor from  $R_{IND}$  to SGND must be used.

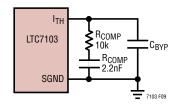

$I_{TH}$  (**Pin 9**): Error Amplifier Output and Switching Regulator Compensation Point. Place compensation components between the  $I_{TH}$  pin and SGND. Tie this pin to INTV<sub>CC</sub> for fixed internal compensation.

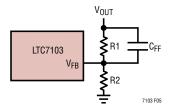

$V_{FB}$  (Pin 10): Regulator Feedback Input. When set to adjustable mode, use an external resistor divider between the regulator output voltage and the  $V_{FB}$  pin. For fixed output voltage mode, tie  $V_{FB}$  directly to the regulator output.

**FREQ (Pin 11):** The frequency control pin for the internal VCO. Connect this pin to SGND for 300kHz operation or to INTV<sub>CC</sub> for 1MHz operation. Place a resistor to SGND on this pin to set the operating frequency between 200kHz and 2MHz. Minimize the capacitance on this pin if Burst Mode operation is used. This pin sources  $40\mu$ A.

**PLLIN/MODE (Pin 12):** External Synchronization Input to Phase Detector and Burst Mode Control Input. When an external clock is applied to this pin, the phase-locked loop will force the rising edge of the SW signal to be synchronized with the rising edge of the external clock, and

the LTC7103 operates in pulse-skipping mode. When not synchronizing to an external clock, this input determines how the LTC7103 operates at light loads. Tie this pin to SGND or float to select Burst Mode operation or tie this pin to INTV $_{\rm CC}$  through a 100k resistor to select pulse-skipping operation. This pin sinks 10 $\mu$ A to SGND. Do not tie this pin directly to INTV $_{\rm CC}$ .

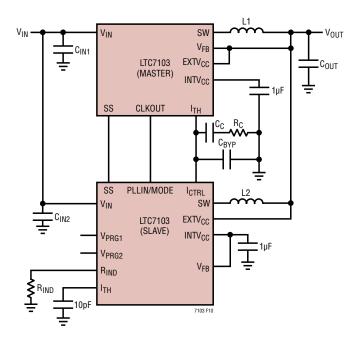

**CLKOUT (Pin 13):** Output clock signal available to synchronize additional regulators for parallel operation. The rising edge of CLKOUT is 180° out of phase with respect to the rising edge of the SW pin. The output level swings from SGND to INTV<sub>CC</sub>.

**PGOOD (Pin 14):** Open-Drain Power Good Output. The  $V_{FB}$  pin is monitored to ensure that the output is in regulation. When the output is not in regulation, the PGOOD pin is pulled low.

SS (Pin 15): Soft-Start and Regulator Timeout Input. The voltage on the SS pin limits the regulated output voltage when the SS voltage is less than 1V. An internal  $10\mu$ A pull-up current source is connected to this pin. A capacitor to ground at this pin sets the ramp time to final regulated output voltage. Leave this pin floating to use the internal 1.2ms soft-start ramp. The SS pin also serves as a timeout to disable switching if the EXTV<sub>CC</sub> voltage is too low. To disable the regulator timeout feature, tie a 75k resistor between SS and INTV<sub>CC</sub>. See Soft-Start and LDO Regulator Timeout in the Applications Information section.

**I**<sub>CTRL</sub> (**Pin 16**): Programs the Average Output Current in Constant Current Mode. The voltage on this pin determines the maximum  $I_{TH}$  voltage, which in turn sets the average output current in constant-current mode. The peak current limit tracks 1.2A above the average current limit set point. Tie this pin to a voltage between 0.4V and 1.3V to program the average output current to a value between 0A and 2.5A. An internal 20μA pull-up on this pin allows a single resistor to SGND to be used to set the voltage.

**I<sub>MON</sub> (Pin 17):** Average Output Current Monitor. This pin generates a voltage between 0.4V and 1.3V that corresponds to an average output current between 0A and 2.5A.

### PIN FUNCTIONS

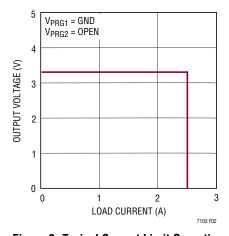

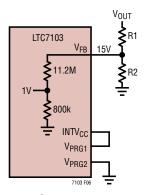

$V_{PRG1}$ ,  $V_{PRG2}$  (Pins 18,19): Output Voltage Programming Pins. These pins set the regulator to adjustable output mode or to fixed output mode. Floating both pins allows the output to be programmed through the  $V_{FB}$  pin using external resistors, regulating  $V_{FB}$  to the 1V reference. Tying one of these pins to SGND or INTV<sub>CC</sub> while the other is tied to SGND, INTV<sub>CC</sub> or floating programs the output to one of eight fixed output voltages. See Output Voltage Programming in the Applications Information section.

**EXTV**<sub>CC</sub> (**Pin 20**): External Power Input to an Internal LDO that Generates INTV<sub>CC</sub>. This LDO supplies INTV<sub>CC</sub> power from EXTV<sub>CC</sub>, bypassing the internal LDO powered from  $V_{IN}$  whenever EXTV<sub>CC</sub> is between 3.1V and 40V. If EXTV<sub>CC</sub> is not used, the regulator timeout feature must be disabled by tying a 75k resistor between SS and INTV<sub>CC</sub>. See INTV<sub>CC</sub> Regulations in the Applications Information section.

**INTV**<sub>CC</sub> (**Pin 21**): Output of the Internal LDO regulator. The driver and control circuits are powered from this voltage source. Must be decoupled to PGND with a  $1\mu F$  to  $4.7\mu F$  ceramic capacitor.

**SW** (**Pins 24, 25, 26**): SW Node connection from the internal MOSFET power switches to the output inductor.

**BOOST (Pin 27):** Bootstrapped Supply to the High Side Floating Gate Driver. Connect a 0.1µF ceramic capacitor between the BOOST and SW pins.

$V_{IN}$  (Pins 30, 31, 32): Power Input Supply. This is the power input to the integrated high side MOSFET switch as well as the input to the internal LDO that generates INTV<sub>CC</sub> voltage. Decouple this pin with a capacitor to PGND.

**PGND/Exposed Pad (Pin 35, 36, 37):** Power Ground. Connect to power ground plane. The exposed pad must be connected to PCB ground for rated electrical and thermal performance.

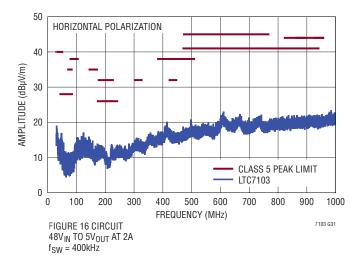

## **FUNCTIONAL DIAGRAM**

#### **Main Control Loop**

The LTC7103 is a high efficiency, monolithic, synchronous step-down DC/DC converter utilizing a constant frequency, average current mode control architecture. Average current mode control enables fast and precise control of the output current without the need for an external sense resistor or current sense amplifier. Instead, the inductor current is sensed internally by losslessly monitoring the top and bottom power switch currents. The LTC7103 also contains a unique circuit that replicates the inductor current immediately after the top switch turn-on and combines this with the sensed switch currents to fully reconstruct the inductor current signal internally. This technique allows for direct control and monitoring of the average output current as well as clean operation at very low duty cycles.

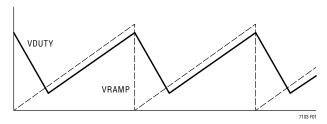

During normal operation, the internal top power switch (N-channel MOSFET) is turned on at the beginning of each clock cycle, causing the inductor current to increase. The sensed inductor current is then delivered to the average current amplifier, whose output (VDUTY) is compared with a saw-tooth ramp (VRAMP). When the VRAMP voltage exceeds the VDUTY voltage, the PWM comparator trips and turns off the top power MOSFET.

After the top power MOSFET turns off, the synchronous power switch (N-channel MOSFET) turns on, causing the inductor current to decrease. The bottom switch stays on until the beginning of the next clock cycle, unless the reverse current limit (0A) is reached and the reverse current comparator trips.

In closed-loop operation, the average current amplifier creates an average current loop that forces the average sensed current signal to be equal to the internal  $I_{TH}$  voltage. Note that the DC gain and compensation of this average current loop is automatically adjusted to maintain an optimum current-loop response. The error amplifier adjusts the  $I_{TH}$  voltage by comparing the divided-down output voltage ( $V_{FBI}$ ) with a 1.0V reference voltage. If the load current changes, the error amplifier adjusts the average inductor current as needed to keep the output voltage in regulation.

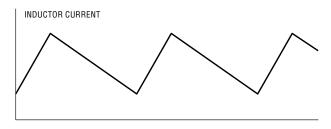

The LTC7103 has been optimized to provide the fastest possible average current loop. To achieve this, the filter on the average current amplifier output ( $C_{CA}$ ,  $R_{CA}$ ) is set to provide high DC gain (provided by integrator capacitor  $C_{CA}$ ) while allowing the inductor current signal to pass through unfiltered. This is accomplished by resistor  $R_{CA}$ , which introduces a zero that is well below the switching frequency. The resulting typical PWM comparator waveforms are shown in Figure 1. Note that the VDUTY signal is an inverted reflection of the inductor current signal, which is essential for obtaining a high speed average current loop.

Figure 1. Typical Current Loop Operating Waveforms

Voltage loop compensation can be set externally using the  $I_{TH}$  pin, taking advantage of OPTI-LOOP compensation to optimize the loop response. The compensation of the voltage loop is essentially the same as for peak current mode control. Alternatively, the  $I_{TH}$  pin can be tied to INTV $_{CC}$  to select internal voltage loop compensation. When internal voltage loop compensation is selected, the LTC7103 automatically adjusts the internal compensation based on switching frequency to maintain a fast and stable voltage loop.

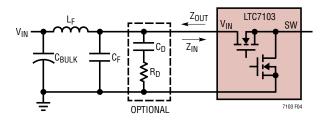

## Power and Bias Supplies ( $V_{IN}$ , SW, BOOST, INTV<sub>CC</sub>, EXTV<sub>CC</sub> Pins)

The  $V_{IN}$  pins on the LTC7103 are used to supply voltage to the drain terminal of the internal high side N-channel MOSFET. These pins also supply bias voltage for an internal

LDO regulator (the  $V_{IN}$  LDO) that generates 3.5V at INTV<sub>CC</sub>. The voltage on INTV<sub>CC</sub> in turn is used for internal chip bias as well as gate drive for the bottom power MOSFETs. The gate drive for the top power MOSFET is supplied by a floating supply ( $C_{BST}$ ) between the BOOST and SW pins, which is charged by an internal synchronous diode from INTV<sub>CC</sub>. In addition, an internal charge pump allows for 100% duty cycle operation by maintaining the BOOST to SW voltage when the top MOSFET is on continuously.

To improve efficiency and limit power dissipation in the  $V_{IN}$  LDO regulator, a second LDO regulator (the EXTV<sub>CC</sub> LDO) allows the INTV<sub>CC</sub> voltage to be derived from the lower-voltage EXTV<sub>CC</sub> pin. In most applications, the EXTV<sub>CC</sub> pin is simply tied directly to the regulated output voltage of the DC/DC converter to enable operation in a high efficiency, bootstrapped configuration. In order to ensure that the power dissipation on the internal  $V_{IN}$  LDO is limited to a safe level, the LTC7103 incorporates a special regulator timeout feature into the soft-start pin.

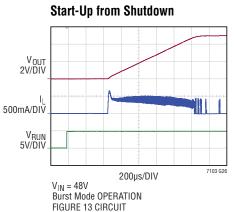

#### Start-Up and Shutdown (RUN, SS, OVLO Pins)

When the RUN pin is below 0.7V, the LTC7103 enters a low current shutdown state, reducing the DC supply current to 0.7µA. When the RUN pin is above 0.7V and the  $V_{IN}$  pin is above than the internal undervoltage threshold ( $V_{IN(UVLO)}$ ) of 4.55V, the INTV<sub>CC</sub> LDO regulators are enabled. However, switching is inhibited until the RUN pin is greater than  $V_{RUN(ON)} = 1.21V$ . This allows the RUN pin to be used to implement a  $V_{IN}$  undervoltage lockout function so that the power supply will not operate below a user-adjustable level. In addition, switching is also inhibited if the voltage on the OVLO pin exceeds  $V_{OV(R)} = 1.21V$ . This feature can be used to implement an input overvoltage lockout function to prevent power supply operation during an overvoltage condition on the input supply.

When appropriate voltages are present on the  $V_{IN}$ , RUN and OVLO pins, the LTC7103 will begin switching and initiate a soft-start ramp of the output voltage. An internal soft-start ramp of 1.2ms will limit the ramp rate of the output voltage to prevent excessive input current during start-up. If a longer ramp time is desired, a capacitor can be placed from the SS pin to ground. The  $10\mu$ A current that is sourced from the SS pin will create a smooth voltage ramp on the capacitor. If this external ramp rate is slower

than the internal 1.2ms soft-start, then the output voltage will be limited by the ramp rate on the SS pin instead. Once both the external and internal soft-start ramps have exceeded 1V, the output voltage will be in regulation. The internal and external soft-start functions are reset during initial start-up and after an undervoltage or overvoltage condition on the input supply.

The soft-start pin is also used to implement a regulator timeout feature. This feature limits die temperature rise due to power dissipation in the internal V<sub>IN</sub> LDO regulator by disabling the top and bottom power MOSFETs after a timeout, if EXTV<sub>CC</sub> voltage is not present. This is useful, for example, if EXTV<sub>CC</sub> is tied to the output of the DC/DC converter, but the converter output gets shorted to ground. During start-up, a regulator timeout begins after both the internal and external soft-start ramps have exceeded 1V. and EXTV<sub>CC</sub> < 3V. If this condition persists for a period of time (approximately 1.4 times the normal soft-start time), then a regulator timeout fault occurs and all switching stops. After a long restart delay (approximately 46 times the normal soft-start time), a restart is initiated. If the regulator timeout feature is not needed, the SS pin should be tied to INTV<sub>CC</sub> through a 75k resistor. See Soft-Start and LDO Regulator Timeout in the Applications Section for more information.

## Output Voltage Programming (V<sub>PRG1</sub>, V<sub>PRG2</sub>, V<sub>FB</sub> Pins)

The  $V_{PRG1}$  and  $V_{PRG2}$  pins provide a great deal of flexibility in programming the output voltage of the power supply. Floating both pins selects adjustable  $V_{OUT}$  mode. In this mode, the output is programmed using external resistors on the  $V_{FB}$  pin, and the  $V_{FB}$  voltage is regulated to the 1V reference. If one of the pins is tied either to SGND or INTV<sub>CC</sub>, then fixed output voltage mode is selected. In this mode, precision internal resistor dividers are used to program the output voltage to one of eight fixed voltage levels. See Output Voltage Programming in the Applications Information Section.

## Inductor Current Replication (R<sub>IND</sub> Pin)

The LTC7103 contains a unique circuit that replicates the inductor current immediately after the top switch turn-on and combines this with the sensed switch currents to fully reconstruct the inductor current signal internally. This

technique allows for direct control and monitoring of the average output current as well as clean operation at very short top switch on-times. In order to replicate the inductor current, the LTC7103 needs to know the approximate value of the inductor. This is achieved by placing a resistor on the  $R_{IND}$  pin that is equal to  $1/(7.5 \, \bullet \, L)$ . The LTC7103 uses the current in the  $R_{IND}$  resistor in conjunction with the voltage on the  $V_{IN}$  and SW pins to generate a replicated inductor current signal. In addition, the  $R_{IND}$  pin current is also used in conjunction with the voltages on  $V_{IN}$  and SW to set the DC gain of the average current amplifier. This is done to maintain optimum current loop performance over all operating conditions.

Note that if fixed output voltage mode is selected using the  $V_{PRG1}$  and  $V_{PRG2}$  pins, then the  $R_{IND}$  pin can be left floating. In this case, the LTC7103 will assume a particular inductor value based on output voltage and switching frequency. See Inductor Value and  $R_{IND}$  Resistor Selection in the Applications Information section.

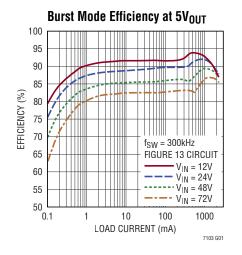

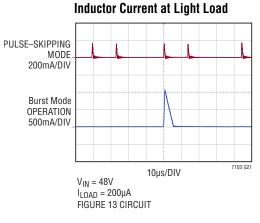

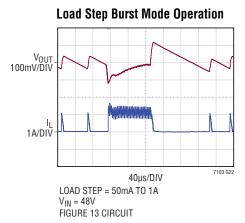

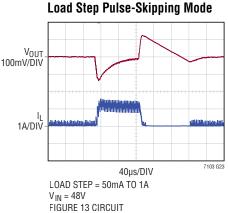

## Light Load Operation: Burst and Pulse-Skipping Modes (PLLIN/MODE Pin)

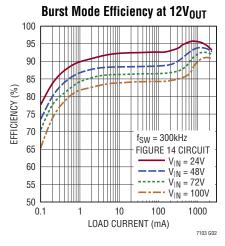

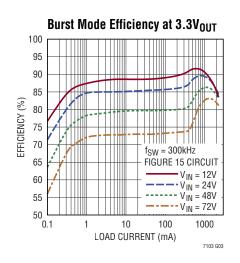

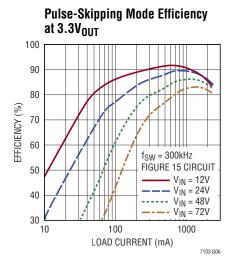

The LTC7103 can be set to enter high efficiency Burst Mode operation or constant frequency pulse-skipping mode at low load currents. To select Burst Mode operation, tie the PLLIN/MODE pin to ground. To select pulse-skipping mode, tie the PLLIN/MODE pin to INTV<sub>CC</sub> through a 100k resistor.

When the LTC7103 is set for Burst Mode operation, the minimum output current is set to approximately 200mA even though the voltage on the  $I_{TH}$  pin might indicate a lower value. If the average inductor current is higher than the load current, the error amplifier will decrease the voltage on the  $I_{TH}$  pin. When the  $I_{TH}$  voltage drops below 0.4V, the internal sleep signal goes high (enabling sleep mode) and both MOSFETs are turned off. The  $I_{TH}$  pin is then disconnected from the output of the error amplifier and parked at 0.43V.

In sleep mode, much of the internal circuitry is turned off, reducing the total quiescent current that the LTC7103 draws to  $9\mu A.$  When EXTV $_{CC}$  is present, the majority of this quiescent current ( $8\mu A$ ) is drawn from the EXTV $_{CC}$  supply and only  $1\mu A$  is drawn from the  $V_{IN}$  supply. This dramatically reduces the sleep mode  $V_{IN}$  supply current in bootstrapped applications where EXTV $_{CC}$  is tied to  $V_{OUT}$  and  $V_{IN} >> V_{OUT}.$  In sleep mode, the load current is supplied by the output capacitor. As the output voltage  $V_{OUT}$  decreases, the error amplifier output begins to rise. When the  $V_{OUT}$  voltage drops enough, the  $I_{TH}$  pin is reconnected to the output of the error amplifier, the sleep signal goes low, and normal operation is resumed by turning on the top MOSFET on the next cycle of the internal oscillator.

When the LTC7103 is set for Burst Mode operation, the inductor current is not allowed to reverse. The reverse current comparator turns off the bottom MOSFET just before the inductor current reaches zero, preventing it from reversing and going negative. Thus, the converter operates with discontinuous inductor current (DCM).

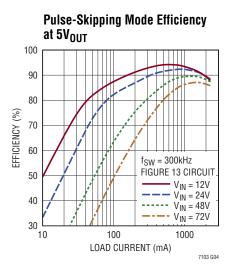

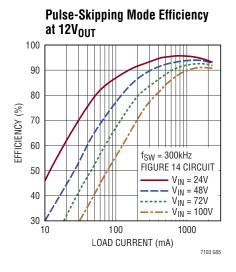

When the PLLIN/MODE pin is connected for pulse-skipping mode, the LTC7103 operates in PWM pulse-skipping mode at light loads. In this mode, constant frequency operation is maintained down to approximately 1% of designed maximum output current. At very light loads, the PWM comparator may remain tripped for several cycles and force the top MOSFET to stay off for the same number of cycles (i.e., skipping pulses). The inductor current is not allowed to reverse (discontinuous operation). This mode, exhibits low output ripple as well as low audio noise and reduced RF interference as compared to Burst Mode operation.

When operating with discontinuous inductor current (DCM) in either burst or pulse-skipping mode, the LTC7103 smoothly transitions from average current to peak current control. This feature eases compensation of the voltage loop in light load DCM operation by removing the pole associated with the average current loop.

To avoid spurious changes in the operating mode, the LTC7103 incorporates a 20µs delay before changing from one mode to another. This is particularly helpful since the PLLIN/MODE pin can be used to select an initial operating mode, and subsequently be used to receive an external clock for synchronization. The 20µs delay avoids changes in mode while the synchronizing signal is recognized. When synchronized, the LTC7103 operates in pulse-skipping mode.

## Frequency Selection and Phase-Locked Loop (FREQ, PLLIN/MODE Pins)

The switching frequency of the LTC7103 can be selected using the FREQ pin, which can be tied to SGND, tied to INTV $_{\rm CC}$ , or programmed through an external resistor. Tying FREQ to SGND selects 300kHz while tying FREQ to INTV $_{\rm CC}$  selects 1MHz. Placing a resistor between FREQ and SGND sends the FREQ pin voltage into the input of the voltage controlled oscillator (VCO), allowing the frequency to be programmed between 200kHz and 2MHz.

A phase-locked loop (PLL) is available on the LTC7103 to synchronize the internal oscillator to an external clock source that is connected to the PLLIN/MODE pin. The LTC7103's phase detector (PFD) and low pass filter adjust the voltage of the VCO input to align the turn-on of the top MOSFET to the rising edge of the synchronizing signal.

When an external clock is detected, the PFD low pass filter is quickly prebiased to the operating frequency set by the FREQ pin before the PLL is allowed to take over the VCO. If prebiased near the external clock frequency, the PLL loop only needs to make slight changes to the VCO input in order to synchronize the rising edge of the external clock's to the top MOSFET turn-on. The ability to prebias the loop filter allows the PLL to lock in rapidly without deviating far from the desired frequency.

The typical capture range of the phase-locked loop is from approximately 160kHz to 2.3MHz, with a guarantee over all manufacturing variations to be between 200kHz and 2MHz. In other words, the LTC7103's PLL is guaranteed to lock to an external clock source whose frequency is between 200kHz and 2MHz.

After the PLL has locked to an external clock, if the external clock is stopped, the LTC7103 will immediately detect this condition and prevent the PFD from adjusting the loop, so that the internal oscillator continues operating at the external clock frequency. After approximately 9µs, the LTC7103 will detect a loss of SYNC, and the oscillator operating frequency returns to the level set by the FREQ pin. This feature prevents the oscillator frequency from dipping momentarily when the external clock is stopped, and enables smooth transitions into and out of synchronization.

The typical input clock thresholds on the PLLIN/MODE pin are 1.5V rising and 1.1V falling, and this input is TTL compatible.

The CLKOUT pin supplies a reference clock that is helpful for synchronizing other switching circuits to the LTC7103 switching frequency. The output high level of this signal is equal to INTV $_{\rm CC}$  (3.5V typical), and the rising edge of the CLKOUT signal is 180° out of phase with respect to the top MOSFET turn-on. This makes it easy to synchronize two LTC7103 converters and operate them out of phase to minimize input current, or to use two LTC7103's together for a higher current, 2-Phase converter. See 2-Phase Operation in the Applications Information section.

## Setting and Monitoring Output Current ( $I_{CTRL}$ , $I_{MON}$ Pins)

Because the LTC7103 utilizes average current mode control, in which the  $I_{TH}$  voltage is proportional to average output current, the setting and monitoring of the average output current is straight-forward.

The average output current limit is set using the  $I_{CTRL}$  pin, whose voltage directly clamps the  $I_{TH}$  voltage to a maximum level. Tie this pin to a voltage between 0.4V and 1.3V to program the average output current to a value between 0A and 2.5A. An internal 20 $\mu$ A pull-up on this pin allows a single resistor to SGND to be used to set the voltage.

By maintaining a fast and optimized current loop over all operating conditions, the LTC7103 responds to changes in the I<sub>CTRL</sub> pin voltage with the greatest possible speed. This is orders of magnitude faster than most competing solutions, where a slow, average current loop is placed outside of the voltage regulation loop. By placing the av-

erage current loop inside of the voltage regulation loop, the LTC7103 allows for current programming on a nearly cycle-by-cycle basis.

The average output current can be monitored at the  $I_{MON}$  pin. The reconstructed inductor current signal ( $V_{SNS}$ ) is run through a low pass filter ( $f_c = 10 \text{kHz}$ ), buffered, and then delivered to the  $I_{MON}$  pin. The voltage on the  $I_{MON}$  normally varies between 0.4V and 1.3V, corresponding to an average output current between 0A and 2.5A. The  $I_{MON}$  voltage may momentarily be less than 0.4V or greater than 1.3V, but eventually is limited to these levels by the average current loop. During SLEEP, this pin is held at 0.4V.

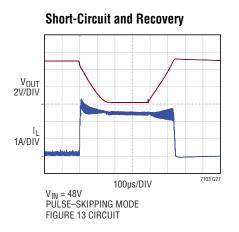

#### **Short-Circuit Protection and Minimum On-Time**

The architecture of the LTC7103 provides inherent protection against short-circuit conditions, without the need for folding back either the output current or the oscillator frequency. This is made possible because the PWM comparator is continuously receiving inductor current information from the average current amplifier. This results in automatic cycle skipping under short-circuit conditions if the minimum on-time of the top switch is too long to maintain control of the inductor current at the full switching frequency. Because a given switching cycle is skipped only as needed to satisfy the high speed average current loop, this creates a brick-wall style current limit without any foldback or hiccups in the operation down to  $V_{OUT} = 0V$ . Figure 2 illustrates the typical operation of this brick-wall current limit.

Figure 2. Typical Current Limit Operation

While the average current loop is extremely fast, a failsafe peak current limit ( $I_{PK}$ ) comparator has also been incorporated to ensure that the inductor current cannot exceed a safe level even momentarily. The peak current limit is internally set to 1.2A above the average current limit, and tracks with the average current limit set by the voltage on the  $I_{CTRL}$  pin. In practice, this peak current limit comparator is only needed when there is an abnormal voltage on the average current amplifier output filter and a short-circuit is simultaneously applied. In this case, the peak current limit comparator may be needed for a few cycles while the average current amplifier filter settles.

When operating at a high step-down ratio from  $V_{IN}$  to  $V_{OUT}$ , care should be taken to choose a switching frequency that is low enough to avoid operation at minimum on-time. However, in the event that a high step-down ratio requires the minimum on-time to be exceeded, the LTC7103 architecture offers inherent protection against output overvoltage. Once again, the PWM comparator will automatically cause the skipping of a cycle as needed to maintain regulation of the output voltage. While this avoids output overvoltage, operation in this mode is undesirable as it increases inductor current ripple.

In addition to this inherent protection, a separate output overvoltage comparator monitors the  $V_{FB}$  voltage and prevents top MOSFET turn-on if an overvoltage condition is present ( $V_{FB}$  exceeds  $V_{FB(OV)}$ ).

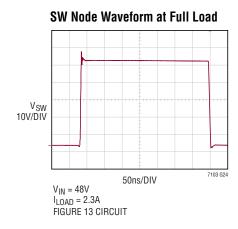

#### **Boost Supply and Dropout Operation**

By making use of an internal charge pump, the LTC7103 is capable of operating at 100% duty cycle, providing the lowest possible dropout voltage and zero switching noise while in dropout. This charge pump delivers the small current required to maintain the static gate voltage on the top MOSFET switch when operating in dropout. When not operating in dropout, the gate drive voltage required for switching the top MOSFET switch is supplied by the charge pump formed by the BOOST capacitor ( $C_{BST}$ ), the bottom MOSFET switch, and an internal switch from INTV<sub>CC</sub> to BOOST. As dropout is approached, the on-time

of the bottom MOSFET switch is lengthened as needed to maintain an adequate supply to the floating gate driver between BOOST and SW.

#### Power Good (PGOOD Pin)

The PGOOD pin is connected to the open drain of an internal N-channel MOSFET. The MOSFET turns on and pulls the PGOOD pin low when the internal feedback voltage ( $V_{FBI}$ ) is not within  $\pm 10\%$  of the 1V reference voltage. The PGOOD pin is also pulled low when the RUN pin is low (shutdown). When  $V_{FBI}$  is within the  $\pm 10\%$  requirement, the MOSFET is turned off and the pin is allowed to be pulled up by an external resistor to a source no greater than 16V. There is a  $20\mu s$  delay ( $T_{PG}$ ) before the PGOOD pin goes low in response to the  $V_{FBI}$  voltage going outside of the  $\pm 10\%$  window.

#### **Overtemperature and Overvoltage Protection**

In addition to the OVLO pin, which provides a user-adjustable protection against  $V_{IN}$  overvoltage, the LTC7103 contains an internal  $V_{IN}$  overvoltage shutdown feature. If the  $V_{IN}$  pin voltage exceeds 118.5V rising (112V falling), then the top and bottom MOSFETs are held off and all switching stops. Likewise, if the internal die temperature exceeds 171°C rising (155°C falling), then the LTC7103 disables switching as well as the LDO regulators until the temperature drops. Note that the internal overvoltage and overtemperature protection features are activated outside of the absolute maximum range of operation, and therefore should not be relied upon operationally. These features are only intended as a secondary failsafe to improve overall system reliability and safety.

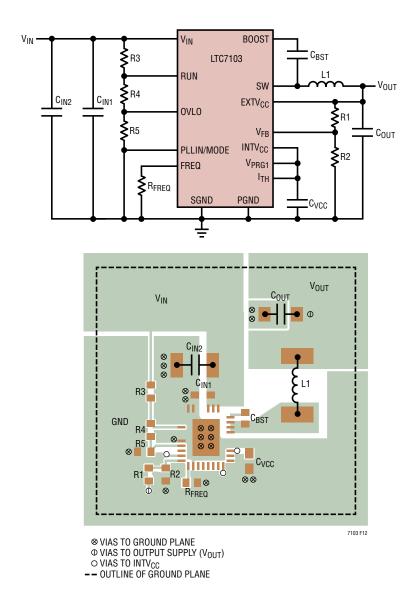

A general LTC7103 application circuit is shown on the first page of this data sheet. External component selection is largely driven by the load requirement and begins with the selection of the operating frequency and light load operating mode. Next, the inductor L is chosen, which also determines the value of resistor  $R_{IND}$ . After the inductor is chosen, the input capacitor  $C_{IN}$ , the output capacitor  $C_{OUT}$ , the internal regulator capacitor  $C_{VCC}$ , and the boost capacitor  $C_{BST}$ , can be selected. Next, either a fixed output voltage or feedback resistors are selected to set the desired output voltage. Finally, the remaining optional external components can be selected for functions such as  $V_{IN}$  undervoltage/overvoltage lock-out, external soft-start, LDO regulator timeout, external loop compensation, average output current monitor and limit, and PGOOD.

#### **Setting the Operating Frequency**

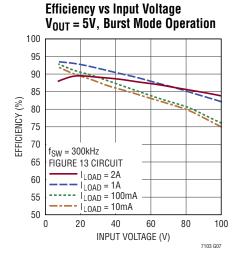

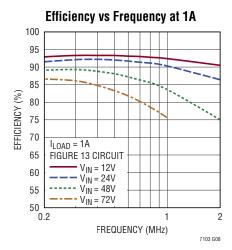

Selection of the operating frequency is a trade-off between efficiency and component size. High frequency operation allows the use of smaller inductor and capacitor values. Operation at lower frequencies improves efficiency by reducing internal gate charge and transition losses, but requires larger inductance values and/or capacitance to maintain low output ripple voltage.

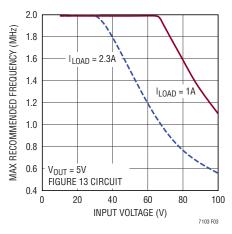

Figure 3. Maximum Recommended Frequency vs Input Voltage

For most LTC7103 applications, a good balance between size and efficiency is achieved with a switching frequency between 300kHz and 750kHz. Operating at higher switching frequencies up to 2MHz is readily possible, but switching

losses generally limit the input voltage to lower levels. This is illustrated in Figure 3, which shows the maximum recommended switching frequency versus input voltage at 1A and 2.3A loads for the application circuit of Figure 13. These lines correspond to a power loss of 2.5W in the LTC7103, which will result in a junction temperature rise of approximately 85°C without air flow. See Efficiency Considerations and Thermal Considerations sections for more information on calculating the power loss and temperature rise.

An additional constraint on operating frequency is the minimum controllable on-time of the LTC7103. While the architecture of the LTC7103 inherently maintains output voltage regulation even if the minimum on-time is exceeded, cycle-skipping will result in increased inductor current ripple. To avoid this, chose a switching frequency such that:

$$f < \frac{V_{OUT}}{V_{IN(MAX)} \cdot t_{ON(MIN)}}$$

The switching frequency is set using the FREQ and/or PLLIN/MODE pins as shown in Table 1.

**Table 1. Frequency Setting**

| FREQ PIN                     | PLLIN/MODE PIN | FREQUENCY(F)                                          |  |

|------------------------------|----------------|-------------------------------------------------------|--|

| SGND                         | DC Voltage     | 300kHz                                                |  |

| INTV <sub>CC</sub>           | DC Voltage     | 1MHz                                                  |  |

| R = (f/40 + 7.5k) to<br>SGND | DC Voltage     | 200kHz to 2MHz                                        |  |

| Any of the Above             | External Clock | Phase-Locked<br>to External Clock<br>(200kHz to 2MHz) |  |

Tying the FREQ pin to SGND selects 300kHz while tying FREQ to INTV<sub>CC</sub> selects 1MHz. Since the FREQ pin sources  $40\mu A$ , placing a resistor between FREQ and SGND allows the frequency to be programmed anywhere between 200kHz and 2MHz. Choose a FREQ pin resistor such that:

$$R_{FREQ} = \frac{f}{40} + 7.5k$$

A phase-locked loop (PLL) is also available on the LTC7103 to synchronize the internal oscillator to an external clock source that is connected to the PLLIN/MODE pin. Once

synchronized, the turn-on of the top MOSFET is aligned to the rising edge of the synchronizing signal. See Phase-Locked Loop and Frequency Synchronization section for details.

#### **Setting the Light-Load Operating Mode**

The LTC7103 can be set to enter high efficiency Burst Mode operation or constant frequency pulse-skipping mode at light load currents. To select Burst Mode operation, tie the PLLIN/MODE pin to ground. To select pulse-skipping mode, tie the PLLIN/MODE pin to INTV<sub>CC</sub> through a 100k resistor. When synchronized, the LTC7103 operates in pulse-skipping mode. Table 2 summarizes the use of the PLLIN/MODE pin to select light-load operating mode.