# PICkit<sup>TM</sup> 3 Starter Kit User's Guide

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION. INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICWorks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620766972

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# MICROCHIP PICkit™ 3 STARTER KIT USER'S GUIDE

# **Table of Contents**

| Chapter 1. Overvie | ew                                  |    |

|--------------------|-------------------------------------|----|

| 1.1                | Introduction                        | 13 |

| 1.2                | Highlights                          | 13 |

| 1.3                | What's New                          | 13 |

| 1.4                | Included Items                      | 13 |

| 1.5                | The Low Pin Count Board             | 14 |

| 1.6                | Software Overview                   | 15 |

| 1.7                | Running the Demonstrations          | 15 |

| Chapter 2. PIC® M  | ICU Architecture                    |    |

| 2.1                | Introduction                        | 17 |

| 2.2                | Core Basics                         | 17 |

| 2.3                | Data/Program Bus                    | 20 |

| 2.4                | Accumulator                         | 20 |

| 2.5                | Instructions                        | 20 |

| 2.6                | Byte                                | 21 |

| 2.7                | Bit                                 | 21 |

| 2.8                | Literal                             | 21 |

| 2.9                | Control                             | 22 |

| 2.10               | Stack Level                         | 25 |

| 2.11               | Memory Organization                 | 25 |

| 2.12               | Program Memory                      | 25 |

|                    | 2.12.1 Flash Program Memory         | 25 |

|                    | 2.12.2 Configuration Words          |    |

|                    | 2.12.3 Device ID                    |    |

|                    | 2.12.4 Revision ID                  |    |

| 2.13               | Data Memory                         |    |

| 2.13               | 2.13.1 Core Registers               |    |

|                    | 2.13.2 Special Function Registers   |    |

|                    | 2.13.3 General Purpose RAM          |    |

|                    | 2.13.4 Common RAM                   | 28 |

| 2.14               | Banks                               | 28 |

| 2.15               | Data EEPROM Memory                  | 34 |

| 2.16               | Programming Basics                  |    |

|                    | 2.16.1 MPASM™ Assembler Operation   |    |

|                    | 2.16.2 XC8 Operation                |    |

|                    | 2.16.3 Numbers in the Assembler     |    |

|                    | 2. 10.7 Numbers in the 700 Compiler |    |

# PICkit™ 3 STARTER KIT USER'S GUIDE

|                | 2.17  |                  | M Assembler Directives                            |    |

|----------------|-------|------------------|---------------------------------------------------|----|

|                |       |                  | cblock                                            |    |

|                |       |                  | Org (addr)                                        |    |

|                |       |                  | End                                               |    |

|                |       |                  |                                                   |    |

|                |       |                  | Errorlevel                                        |    |

| <b>0</b> 1 4 4 |       |                  | #include                                          | 37 |

| Chapter 3      |       |                  | 20                                                | 40 |

|                | 3.1   |                  | ns                                                |    |

|                | 3.2   | 3.2.1            | n 1: Hello World (Turn on an LED)<br>Introduction |    |

|                |       | 3.2.2            | Hardware Effects                                  | 41 |

|                |       | 3.2.3            | Summary                                           | 41 |

|                |       | 3.2.4            | New Registers                                     | 41 |

|                |       | 3.2.5            | New Instructions                                  | 42 |

|                |       | 3.2.6            | Assembly                                          | 43 |

|                |       | 3.2.7            | C Language                                        | 45 |

|                | 3.3   | Lesso            | n 2: Blink                                        | 46 |

|                |       | 3.3.1            | Introduction                                      | 46 |

|                |       | 3.3.2            | Hardware Effects                                  | 46 |

|                |       | 3.3.3            | Summary                                           | 46 |

|                |       | 3.3.4            | New Registers                                     |    |

|                | 3.3.5 | New Instructions |                                                   |    |

|                |       | 3.3.6            | Assembly                                          |    |

|                |       | 3.3.7            | C Language                                        | 49 |

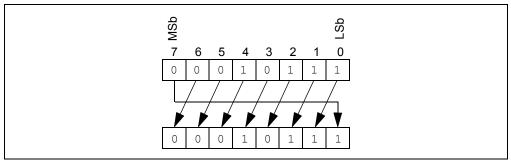

|                | 3.4   |                  | n 3: Rotate                                       |    |

|                |       | 3.4.1            | Introduction                                      |    |

|                |       | 3.4.2            | Hardware Effects                                  |    |

|                |       | 3.4.3            | Summary                                           |    |

|                |       | 3.4.4            | New Registers                                     |    |

|                |       | 3.4.5            | New Instructions                                  |    |

|                |       | 3.4.6            | Assembly                                          |    |

|                | 0.5   | 3.4.7            | C Language                                        |    |

|                | 3.5   | 3.5.1            | n 4: Analog-to-Digital Conversion<br>Introduction |    |

|                |       | 3.5.2            | Hardware Effects                                  |    |

|                |       | 3.5.3            | Summary                                           |    |

|                |       | 3.5.4            | New Registers                                     |    |

|                |       | 3.5.5            | New Instructions                                  |    |

|                |       | 3.5.6            | Assembly                                          |    |

|                |       | 3.5.7            | C Language                                        |    |

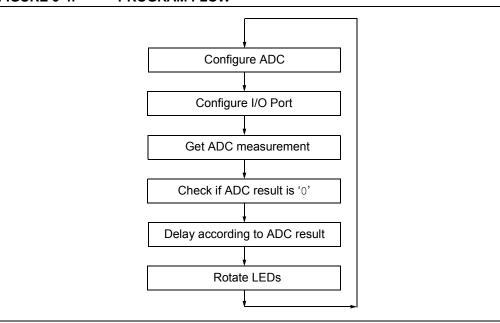

|                | 3.6   | Lesso            | n 5: Variable Speed Rotate                        | 59 |

|                |       | 3.6.1            | Introduction                                      | 59 |

|                |       | 3.6.2            | Hardware Effects                                  | 59 |

|                |       | 3.6.3            | Summary                                           |    |

|                |       | 3.6.4            | New Registers                                     | 59 |

|                |       | 3.6.5            | New Instructions                                  |    |

|                |       | 3.6.6            | Assembly                                          |    |

|                |       | 3.6.7            | C Language                                        | 61 |

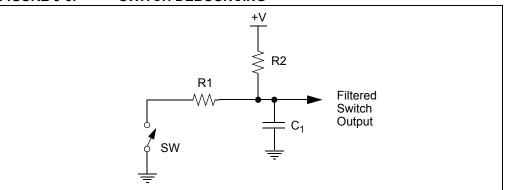

| 3.7  |        | n 6: Debounce                                     |    |

|------|--------|---------------------------------------------------|----|

|      | 3.7.1  | Introduction                                      | 62 |

|      | 3.7.2  | Hardware Effects                                  |    |

|      | 3.7.3  | Summary                                           |    |

|      | 3.7.4  | New Registers                                     |    |

|      | 3.7.5  | New Instructions                                  | 63 |

|      | 3.7.6  | Assembly                                          | 63 |

|      | 3.7.7  | PIC18                                             | 63 |

|      | 3.7.8  | C Language                                        | 63 |

| 3.8  | Lesso  | n 7: Reversible Variable Speed Rotate             | 64 |

| 0.0  | 3.8.1  | Introduction                                      |    |

|      | 3.8.2  | Hardware Effects                                  |    |

|      | 3.8.3  | Summary                                           |    |

|      | 3.8.4  | New Registers                                     |    |

|      | 3.8.5  | New Instructions                                  |    |

|      | 3.8.6  | Assembly                                          |    |

|      | 3.8.7  | C Language                                        |    |

| 2.0  |        |                                                   |    |

| 3.9  | 3.9.1  | n 8: Pulse-Width Modulation (PWM)<br>Introduction |    |

|      | 3.9.1  | Hardware Effects                                  |    |

|      | 3.9.2  |                                                   |    |

|      |        | Summary                                           |    |

|      | 3.9.4  | New Registers                                     |    |

|      | 3.9.5  | Assembly                                          |    |

| 3.10 |        | n 9: Timer0                                       |    |

|      | 3.10.1 | Introduction                                      |    |

|      |        | Hardware Effects                                  |    |

|      | 3.10.3 | Summary                                           |    |

|      | 3.10.4 | New Registers                                     |    |

|      | 3.10.5 | Assembly                                          |    |

|      | 3.10.6 | C Language                                        | 72 |

| 3.11 | Lesso  | n 10: Interrupts and Pull-ups                     | 73 |

|      | 3.11.1 | Introduction                                      | 73 |

|      | 3.11.2 | Hardware Effects                                  | 73 |

|      | 3.11.3 | Summary                                           | 73 |

|      | 3.11.4 | New Registers                                     | 75 |

|      | 3.11.5 | New Instructions                                  | 76 |

|      | 3.11.6 | Assembly                                          | 76 |

|      | 3.11.7 | C Language                                        | 77 |

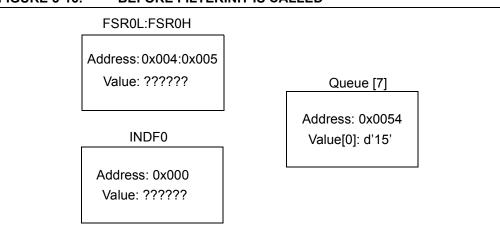

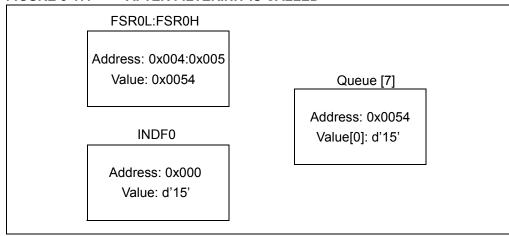

| 3.12 | Lesso  | n 11: Indirect Addressing                         | 78 |

|      |        | Introduction                                      |    |

|      | 3.12.2 | Hardware Effects                                  | 78 |

|      |        | Summary                                           |    |

|      |        | New Registers                                     |    |

|      |        | New Instructions                                  |    |

|      |        | Assembly Language                                 |    |

|      |        | C language                                        |    |

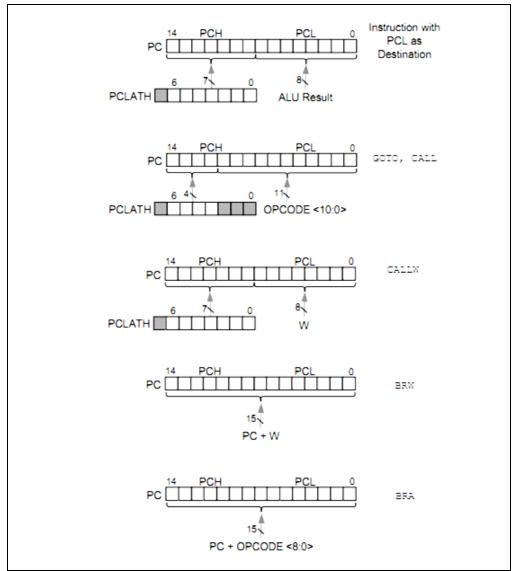

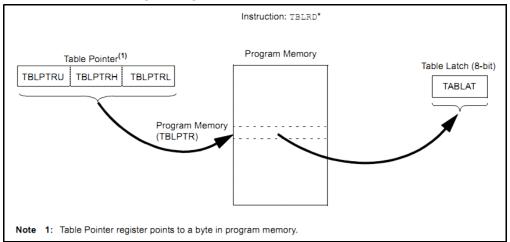

| 3.13 |        | n 12: Look-up Table                               |    |

| 3.13 |        | Intro                                             |    |

|      |        | Hardware Effects                                  |    |

|      |        | Summary                                           |    |

|      | 5.15.5 | Cultillary                                        |    |

# PICkit™ 3 STARTER KIT USER'S GUIDE

|                  | 3.13.4 New Registers               | 85<br>86<br>87 |

|------------------|------------------------------------|----------------|

| 3.14             | Lesson 13: EEPROM                  | 92             |

|                  | 3.14.3 Summary                     | 92<br>93<br>93 |

|                  | 3.14.6 Assembly Language           |                |

| Appendix A. Bloc | k Diagram and MPLAB® X Shortcuts   |                |

| A.1              | Useful MPLAB® X Shortcuts          | 96             |

| A.2              | Finding Register Names             | 96             |

| A.3              | PIC MCU Assembly Coding Practices: |                |

|                  |                                    |                |

# ICROCHIP PICkit™ 3 STARTER KIT USER'S GUIDE

#### **Preface**

#### **NOTICE TO CUSTOMERS**

All documentation becomes dated, and this manual is no exception. Microchip tools and documentation are constantly evolving to meet customer needs, so some actual dialogs and/or tool descriptions may differ from those in this document. Please refer to our web site (www.microchip.com) to obtain the latest documentation available.

Documents are identified with a "DS" number. This number is located on the bottom of each page, in front of the page number. The numbering convention for the DS number is "DSXXXXXA", where "XXXXX" is the document number and "A" is the revision level of the document.

For the most up-to-date information on development tools, see the MPLAB<sup>®</sup> IDE online help. Select the Help menu, and then Topics to open a list of available online help files.

#### INTRODUCTION

This chapter contains general information that will be useful to know before using the PICkit™ 3 Starter Kit User's Guide. Items discussed in this chapter include:

- · Document Layout

- · Conventions Used in this Guide

- Warranty Registration

- Recommended Reading

- · The Microchip Web Site

- Development Systems Customer Change Notification Service

- Customer Support

- Document Revision History

#### **DOCUMENT LAYOUT**

This document describes how to use the PICkit<sup>™</sup> 3 Starter Kit User's Guide as a development tool to emulate and debug firmware on a target board. The manual layout is as follows:

- Section Chapter 1. "Overview"

- Section Chapter 2. "PIC® MCU Architecture"

- · Section Chapter 3. "Lessons"

- Appendix A. "Block Diagram and MPLAB® X Shortcuts"

# PICkit™ 3 Starter Kit User's Guide

#### **CONVENTIONS USED IN THIS GUIDE**

This manual uses the following documentation conventions:

#### **DOCUMENTATION CONVENTIONS**

| Description                                      | Represents                                                                                          | Examples                                     |  |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|

| Arial font:                                      |                                                                                                     |                                              |  |  |  |

| Italic characters                                | Referenced books                                                                                    | MPLAB <sup>®</sup> IDE User's Guide          |  |  |  |

|                                                  | Emphasized text                                                                                     | is the only compiler                         |  |  |  |

| Initial caps                                     | A window                                                                                            | the Output window                            |  |  |  |

|                                                  | A dialog                                                                                            | the Settings dialog                          |  |  |  |

|                                                  | A menu selection                                                                                    | select Enable Programmer                     |  |  |  |

| Quotes                                           | A field name in a window or dialog                                                                  | "Save project before build"                  |  |  |  |

| Underlined, italic text with right angle bracket | A menu path                                                                                         | File>Save                                    |  |  |  |

| Bold characters                                  | A dialog button                                                                                     | Click <b>OK</b>                              |  |  |  |

|                                                  | A tab                                                                                               | Click the <b>Power</b> tab                   |  |  |  |

| N'Rnnnn                                          | A number in verilog format, where N is the total number of digits, R is the radix and n is a digit. | 4'b0010, 2'hF1                               |  |  |  |

| Text in angle brackets < >                       | A key on the keyboard                                                                               | Press <enter>, <f1></f1></enter>             |  |  |  |

| Courier New font:                                | •                                                                                                   |                                              |  |  |  |

| Plain Courier New                                | Sample source code                                                                                  | #define START                                |  |  |  |

|                                                  | Filenames                                                                                           | autoexec.bat                                 |  |  |  |

|                                                  | File paths                                                                                          | c:\mcc18\h                                   |  |  |  |

|                                                  | Keywords                                                                                            | _asm, _endasm, static                        |  |  |  |

|                                                  | Command-line options                                                                                | -Opa+, -Opa-                                 |  |  |  |

|                                                  | Bit values                                                                                          | 0, 1                                         |  |  |  |

|                                                  | Constants                                                                                           | 0xff, 'A'                                    |  |  |  |

| Italic Courier New                               | A variable argument                                                                                 | file.o, where file can be any valid filename |  |  |  |

| Square brackets [ ]                              | Optional arguments                                                                                  | <pre>mcc18 [options] file [options]</pre>    |  |  |  |

| Curly brackets and pipe character: {   }         | Choice of mutually exclusive arguments; an OR selection                                             | errorlevel {0 1}                             |  |  |  |

| Ellipses                                         | Replaces repeated text                                                                              | <pre>var_name [, var_name]</pre>             |  |  |  |

|                                                  | Represents code supplied by user                                                                    | <pre>void main (void) { }</pre>              |  |  |  |

#### WARRANTY REGISTRATION

Please complete the enclosed Warranty Registration Card and mail it promptly. Sending in the Warranty Registration Card entitles users to receive new product updates. Interim software releases are available at the Microchip web site.

#### RECOMMENDED READING

This user's guide describes how to use the PICkit™ 3 Starter Kit User's Guide. Other useful documents are listed below. The following Microchip documents are available and recommended as supplemental reference resources.

#### Readme for PICkit™ 3 Starter Kit User's Guide

For the latest information on using PICkit™ 3 Starter Kit User's Guide, read the "Readme for PICkit™ 3 Starter Kit Board User's Guide.txt" file (an ASCII text file) in the Readmes subdirectory of the MPLAB IDE installation directory. The Readme file contains update information and known issues that may not be included in this user's guide.

#### PIC16(L)F1825/29 Data Sheet (DS41440)

This data sheet summarizes the features of the PIC16F1829.

#### PIC18(L)F1XK22 Data Sheet (DS41365)

This data sheet summarizes the features of the PIC18F14K22.

#### **Readme Files**

For the latest information on using other tools, read the tool-specific Readme files in the Readmes subdirectory of the MPLAB IDE installation directory. The Readme files contain update information and known issues that may not be included in this user's guide.

### PICkit™ 3 Starter Kit User's Guide

#### THE MICROCHIP WEB SITE

Microchip provides online support via our web site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

#### **DEVELOPMENT SYSTEMS CUSTOMER CHANGE NOTIFICATION SERVICE**

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

The Development Systems product group categories are:

- Compilers The latest information on Microchip C compilers and other language tools. These include the HI-TECH C<sup>®</sup> C16, MPLAB C18 and MPLAB C30 C compilers; MPASM™ and MPLAB ASM30 assemblers; MPLINK™ and MPLAB LINK30 object linkers; and MPLIB™ and MPLAB LIB30 object librarians.

- In-Circuit Debuggers The latest information on the Microchip in-circuit debugger, MPLAB ICD 2, MPLAB ICD 3, PICkit™ 3.

- MPLAB<sup>®</sup> IDE The latest information on Microchip MPLAB IDE, the Windows<sup>®</sup> Integrated Development Environment for development systems tools. This list is focused on the MPLAB IDE, MPLAB SIM simulator, MPLAB IDE Project Manager and general editing and debugging features.

- Programmers The latest information on Microchip programmers. These include the MPLAB PM3 device programmers and PICkit™ 3 development programmers.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com

#### **DOCUMENT REVISION HISTORY**

#### **Revision A (October 2012)**

· Initial Release of this Document.

#### **Revision B (November 2012)**

• Revised Sections 3.5.3, 3.5.4.1.1, 3.11.3.2, Table 3-15.

# PICkit™ 3 Starter Kit User's Guide

NOTES:

# PICkit™ 3 STARTER KIT USER'S GUIDE

# Chapter 1. Overview

#### 1.1 INTRODUCTION

This chapter introduces the hardware that is included in the kit, as well as a quick start to downloading and installing the accompanying software.

#### 1.2 HIGHLIGHTS

This chapter discusses:

- What's New

- Included Items

- The Low Pin Count (LPC) Board Hardware

- Software Overview

- Running the Demonstrations

#### 1.3 WHAT'S NEW

This kit is an update to the PICkit™ 2 Starter Kit. Modifications to the previous LPC board (DM164120-1) were made so that the full functionality of the code can be debugged without the need of a debug header. The software has also been rewritten to accommodate new technologies. The following is a list of new features:

- 1. Software is in both the 'C' and assembler language

- 2. Extension of the number of lessons and modules covered

- 3. MPLAB® X support as well as the older MPLAB® 8

- 4. New PIC16 enhanced mid-range and PIC18 routines

- 5. Uses the universal XC8 compiler

The following is a list of hardware changes to the LPC board:

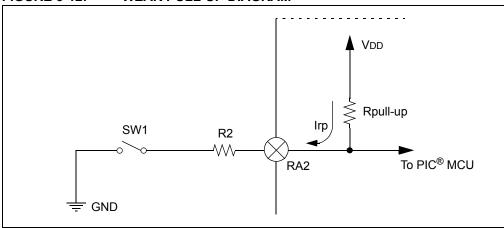

- 1. Potentiometer connected to RA4 (formerly to RA0)

- 2. Switch connected to RA2 (formerly to RA3)

This new LPC board is still backwards compatible. Bridging the old pins to the new pins will restore functionality.

#### 1.4 INCLUDED ITEMS

- 1. 1x PICkit 3 Programmer

- 2. 1x Micro USB cable

- 3. 1x LPC Board (Part Number: DM164130-9)

- 4. 1x PIC16F1829-I/P

- 5. 1x PIC18F14K22 -I/P

The 13 lessons can be downloaded from the web.

The PIC16F1829 is a new enhanced mid-range device, which supports more features than the older mid-range PIC16 parts.

The software associated with the kit supports the PIC16F1829 and PIC18F14K22. The software is intended to run on these two devices, although the software can be easily ported to other devices.

#### 1.5 THE LOW PIN COUNT BOARD

Support for 18-pin devices requires some board modifications. 14- and 20-pin PIC devices will have full access to all of the human interface devices. If an 8-pin part is used, then the LEDs will have to be bridged to the necessary pins on the PIC MCU. The switch and potentiometer are already connected to pins that are supported by an 8-pin device. The board provides holes next to the LEDs that can be easily soldered to in order to create any desired hardware changes.

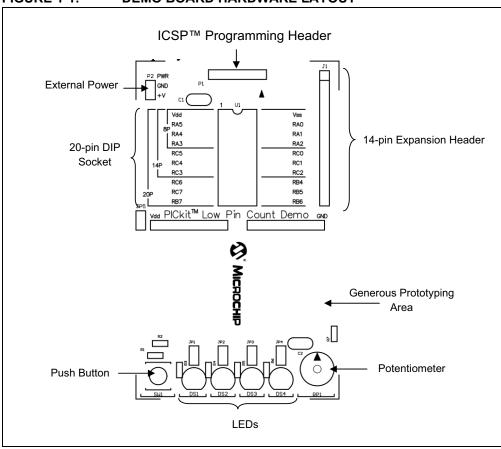

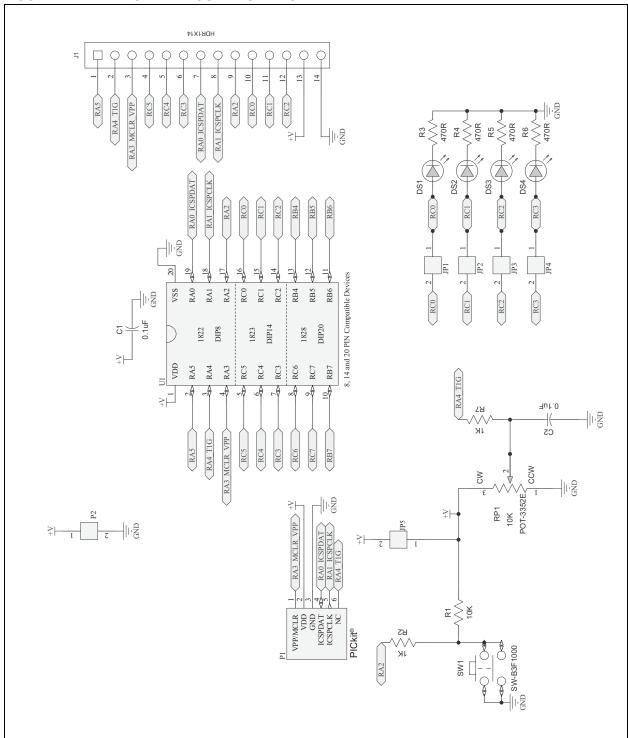

The board is programmable by an In-Circuit Serial Programmer™ (ICSP™), such as a PICkit™ programmer. The board should be supplied with 5V. Figure 1-1 shows the LPC Demo Board.

FIGURE 1-1: DEMO BOARD HARDWARE LAYOUT

Table 1-1 lists the components that are connected to the two PIC devices that come with the board.

TABLE 1-1: PIN ASSIGNMENTS

| Device      | LEDs <ds4:ds1></ds4:ds1> | Switch - SW1 | Potentiometer – RP1 |  |  |  |

|-------------|--------------------------|--------------|---------------------|--|--|--|

| PIC16F1829  | <rc4:rc0></rc4:rc0>      | RA2          | RA4                 |  |  |  |

| PIC18F14K22 | <rc4:rc0></rc4:rc0>      | RA2          | RA4                 |  |  |  |

#### 1.6 SOFTWARE OVERVIEW

This guide will assume that the reader has a basic knowledge of electronics. The reader does not need to have any programming experience with a PIC MCU before reading, although a basic knowledge of programming and what the difference between a bit and byte will help.

The software is written in both assembly and 'C' in the MPLAB X and MPLAB 8 integrated design environment (IDE). The assembly version is more complex and requires more lines of code, however it is closely tied to the PIC device's hardware and the reader will gain a much better understanding by doing these lessons in parallel with the 'C' routines. The 'C' programming language is a higher level language assembly, hence it provides the reader with an easier to read flow of the program. Each lesson has both versions and are functionally equivalent.

It is recommended that the lessons be followed sequentially, as presented, since most of the lessons build up on one another. Each new program will introduce a new peripheral or concept. This guide is not intended to be read without following along in the code.

The PIC18 and enhanced PIC16 programs will be presented side-by-side and their differences and similarities explained.

#### 1.7 RUNNING THE DEMONSTRATIONS

The board comes preprogrammed with a lesson. To use this program, either apply 5V to the power header (P2), or connect a programmer to the programmer header (P1) and apply 5V through the programmer in the IDE. The demo program will blink the four red LEDs in succession. Press the push button (SW1), and the sequence will reverse. Rotate the potentiometer (RP1), and the light sequence will blink at a different rate. This demo program is developed through the first seven lessons in this guide.

| PICkit™ | 3 | Starter | Kit  | User's         | Guide |

|---------|---|---------|------|----------------|-------|

| IIONIL  | v | Otarter | IXIL | <b>U</b> 361 3 | Juluc |

NOTES:

# MICROCHIP PICkit™ 3 STARTER KIT USER'S GUIDE

# Chapter 2. PIC® MCU Architecture

#### 2.1 INTRODUCTION

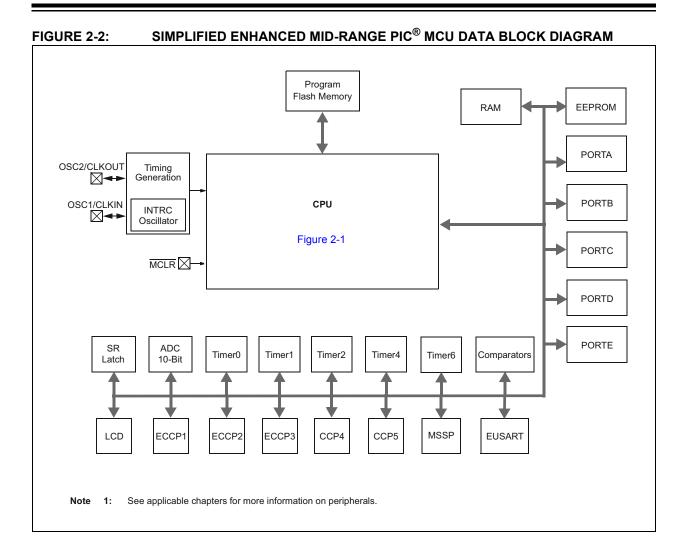

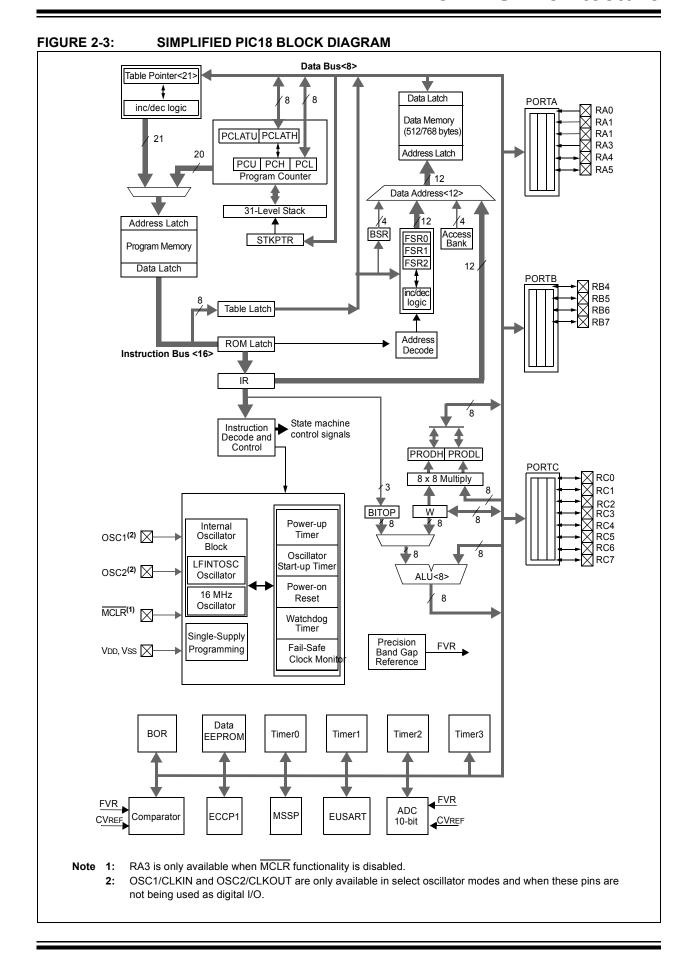

This chapter describes the architecture of the enhanced mid-range PIC16F1829 (DS41440), as well as the PIC18 (DS41365).

#### 2.2 CORE BASICS

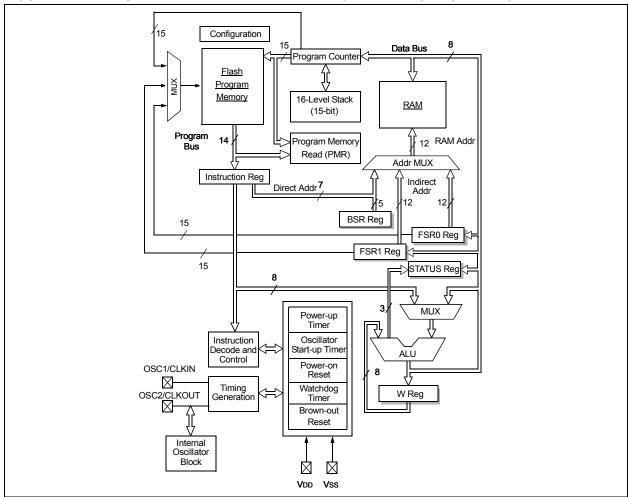

Enhanced PIC16 and PIC18 devices use a modified Harvard architecture, meaning the code memory and data memory are independent. This allows faster execution because code instructions and data can be accessed simultaneously. The subsequent instruction is fetched while decoding and executing the current instruction. In Figure 2-1 and Figure 2-3, the reader should notice the separate lines for data bus and program bus. This guide will cover nearly all of the registers and modules as seen in the following figures. The following block diagrams should be referenced while each lesson is being performed in order to understand the interactions.

FIGURE 2-1: SIMPLIFIED ENHANCED MID-RANGE PIC® MCU BLOCK DIAGRAM

© 2012 Microchip Technology Inc.

### PICkit™ 3 Starter Kit User's Guide

#### 2.3 DATA/PROGRAM BUS

The data bus is connected to the outside world via port pins, as well as all of the peripheral registers (timers, ADC, PWM). The program bus connects to the Flash memory where the program is stored. This is where assembled code is programmed to.

#### 2.4 ACCUMULATOR

There is only one accumulator – the working register (WREG). The accumulator handles all data bus related tasks, such as mathematical operations. The ALU only deals with 8-bit sized data – hence the categorical names of 8/16/32-bit micros.

#### 2.5 INSTRUCTIONS

Instructions tell what the PIC device should do, whether it is shifting a few bits or jumping to a new line in code. They form the very essence of each program in program memory. All enhanced mid-range PIC devices have only 49 instructions. The PIC18 has 75 available instructions. Since there are very few instructions needed to learn, the PIC device can be referred to as a "reduced instruction set computing", or RISC, processor.

Each instruction will be explained in detail as they are introduced in each lesson. For now, the basis of what makes up each instruction will be explained.

One instruction cycle consists of four clock cycles. This means that if the PIC MCU is running at 4 MHz, each instruction will take one microsecond, as seen in Equation 2-1.

#### **EQUATION 2-1: INSTRUCTION TIME**

$$T(clock\ cycle) = \frac{1}{Fosc}$$

$$4 * T = \frac{4}{FOSC} = \frac{4}{4 \ MHz} = 1 \ \mu s$$

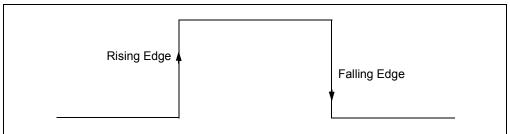

All instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter (PC) is changed. In these cases, the execution takes two instruction cycles, with the additional instruction cycle executed as a NOP (do nothing), see Example 2-1.

#### **EXAMPLE 2-1:**

BTFSS PORTA, RAO

This takes two instruction cycles only if pin RA0 is set (active-high), since the skip operation affects the PC.

The PIC18 has a larger word size than the enhanced PIC16 architecture. The PIC18 has a 16-bit wide word containing the operation code (opcode) and all required operands. The enhanced PIC16 has a 14-bit wide word. An opcode is interpreted by the processor and is unique to each instruction.

The opcodes are broken into four formats:

- 1. Byte oriented

- 2. Bit oriented

- 3. Literal

- 4. Control

#### 2.6 BYTE

All byte instructions on the enhanced PIC16 contain a 6-bit opcode, 7-bit file address, and a destination bit. All PIC18 byte instructions contain a 6-bit opcode, 8-bit file address, a destination bit, and a RAM access bit. The sum of all the bit field sizes confirms that the PIC16 enhanced core does indeed have a 14-bit wide word size for instructions. Likewise, the same can be seen for the PIC18 for its 16-bit wide word length.

The RAM access bit (a) on the PIC18 is set when the user wishes to use the Bank Select Register (BSR) for manually selecting the bank. The PIC16 user will always need to make sure that they are in the correct bank by using the 'banksel' directive. This is explained in the first few lessons.

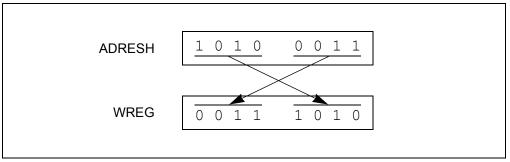

The destination bit (d) specifies whether the result will be stored in WREG or back in the original file register. When 'd' is zero, the result is placed in the WREG resister. Otherwise, the result is placed in the file register.

The file register (f) specifies which register to use. This can be a Special Function Register (SFR) or General Purpose Register (GPR).

#### **EXAMPLE 2-2:**

ADDWF data, f

This adds the contents of WREG and data, with the result being saved back to the file register data.

The PIC18 can move data from one file register directly to another file register, circumventing the WREG. All file moves in the enhanced PIC16 architecture must go through the WREG.

#### 2.7 BIT

Bit instructions operate on a specific bit within a file register. These instructions may set or clear a specific bit within a file register. They may also be used to test a specific bit within a file register. All bit instructions on the enhanced PIC16 contain a 4-bit opcode, 7-bit file address, and a 3-bit bit address. All PIC18 byte instructions contain a 4-bit opcode, 8-bit file address, 3-bit bit address and a RAM access bit.

#### **EXAMPLE 2-3:**

BSF PORTA, RAO

This sets pin RA0 in the PORTA register.

#### 2.8 LITERAL

Literal operations contain the data operand within the instruction. Both architectures use an 8-bit intermediate value. The rest of the bits are reserved for the opcode.

#### **EXAMPLE 2-4:**

MOVLW 'A'

This moves the ASCII value of 'A' (0x41) into WREG.

# PICkit™ 3 Starter Kit User's Guide

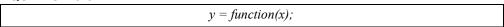

#### 2.9 CONTROL

Instructions that dictate what address the PC will select in program memory are called control instructions. This would include call, goto, and branch. Each has a unique word length. Please refer to the "Instruction Set Summary" chapter in any PIC device data sheet for more information.

#### FIGURE 2-4: **ENHANCED PIC16 GENERAL FORMAT FOR INSTRUCTIONS** Byte-oriented file register operations **Example Instruction** 7 OPCODE f (FILE #) d ADDWF MYREG, d = 0 for destination W d = 1 for destination f f = 7-bit file register address Bit-oriented file register operations 10 9 7 6 13 f (FILE #) **OPCODE** b (BIT #) b = 3-bit bit address f = 7-bit file register address Literal and control operations General 13 **OPCODE** k (literal) BSF MYREG, BIT k = 8-bit immediate value CALL and GOTO instructions only 11 OPCODE k (literal) MOVLW 0x45 k = 11-bit immediate value MOVLP instruction only 13 7 6 OPCODE k (literal) CALL LABEL k = 7-bit immediate value MOVLB instruction only 5 4 13 OPCODE k (literal) MOVLP 15 k = 5-bit immediate value BRA instruction only 13 **OPCODE** k (literal) MOVLB k = 9-bit immediate value FSR Offset instructions 13 6 OPCODE k (literal) n BRA LABEL n = appropriate FSR k = 6-bit immediate value FSR Increment instructions 13 OPCODE m (mode) n ADDFSR FSR1, 3 n = appropriate FSRm = 2-bit mode value **OPCODE** only 13 0 OPCODE MOVIW ++FSR0

#### FIGURE 2-5: PIC18 GENERAL FORMAT FOR INSTRUCTIONS Byte-oriented file register operations **Example Instruction** 10 9 15 8 7 OPCODE d a f (FILE #) ADDWF MYREG, W, B d = 0 for result destination to be WREG register d = 1 for result destination to be file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Byte to Byte move operations (2-word) 12 11 OPCODE f (Source FILE #) MOVFF MYREG1, MYREG2 15 12 11 n f (Destination FILE #) 1111 f = 12-bit file register address Bit-oriented file register operations 12 11 987 OPCODE b (BIT #) a f (FILE #) BSF MYREG, bit, B b = 3-bit position of bit in file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Literal operations **OPCODE** MOVLW 7Fh k (literal) k = 8-bit immediate value **Control** operations CALL, GOTO and Branch operations 15 0 **OPCODE** n<7:0> (literal) GOTO Label 12 11 0 15 1111 n<19:8> (literal) n = 20-bit immediate value 15 **OPCODE** n<7:0> (literal) CALL MYFUNC 0 15 12 11 1111 n<19:8> (literal) S = Fast bit 11 10 0 OPCODE n<10:0> (literal) BRA MYFUNC 8 7 BC MYFUNC OPCODE n<7:0> (literal)

There are some subtle differences between the block diagrams in Figure 2-1 and Figure 2-3. This document will point out a few of the important ones.

#### 2.10 STACK LEVEL

The PIC18 has a deeper stack level of 31, whereas the enhanced core has 16. A deeper stack allows the PIC device to make more calls in the software before returning to the original address where the first call was made.

A call or goto modifies the program counter to point to a different place in code. Without these, the code would execute from the top to the bottom. The lessons will show the significance of this.

The call stack is used to save the return address before going to a new position in program memory.

As a frame of reference, some of the baseline parts (PIC10/12) devices have a call stack that is only two levels deep. It is quite a challenge to create modular code with a limited stack depth.

#### 2.11 MEMORY ORGANIZATION

There are three sections of memory in the PIC16 enhanced mid-range and PIC18 devices:

- 1. Program Memory

- 2. Data RAM

- 3. Data EEPROM

#### 2.12 PROGRAM MEMORY

There are five sections of program memory:

- 1. Flash Program Memory

- 2. Configuration Words

- 3. Device ID

- Revision ID

- User ID

#### 2.12.1 Flash Program Memory

All enhanced mid-range and PIC18 devices use Flash memory for programming. Flash allows the PIC device to be erased and written to hundreds of thousands of times.

#### 2.12.2 Configuration Words

There are several Configuration Word bits, or fuses, that allow different configurations at run-time. Oscillator selections, memory protection, low-voltage detection, etc., are some examples of configuration options. Each device has different configuration options. Enhanced mid-range Configuration bits are read-only during code execution. PIC18 can read all and write most Configuration bits during code execution. The Configuration bits are programmed in a special way, as seen in the lesson source files.

#### 2.12.3 **Device ID**

The Device ID contains the read-only manufacture's ID for the PIC MCU. The PIC16F1829 ID is stored in DEVICEID and the PIC18F14K22 is stored in DEVID1 and DEVID2.

#### 2.12.4 Revision ID

There are five bits in each PIC MCU that indicate the silicon revision of the PIC device. These bits are read-only and found in the DEVID register. There are usually multiple revisions of silicon for each PIC device. The errata document, which points out any errors and their temporary work-arounds, should be read alongside the data sheet.

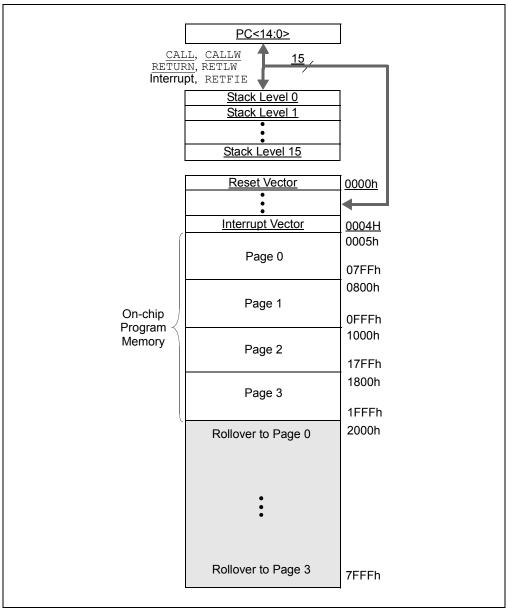

The PIC18 has a program bus that is 21 bits wide, whereas the enhanced core is only 15 bits wide. A larger program bus infers that the program memory is larger, since it allows the core to locate a higher address value. The enhanced core program counter is capable of addressing 32K x 14 program memory space as seen in Figure 2-6.

FIGURE 2-6: ENHANCED MID-RANGE PROGRAM MEMORY MAP AND CALL STACK

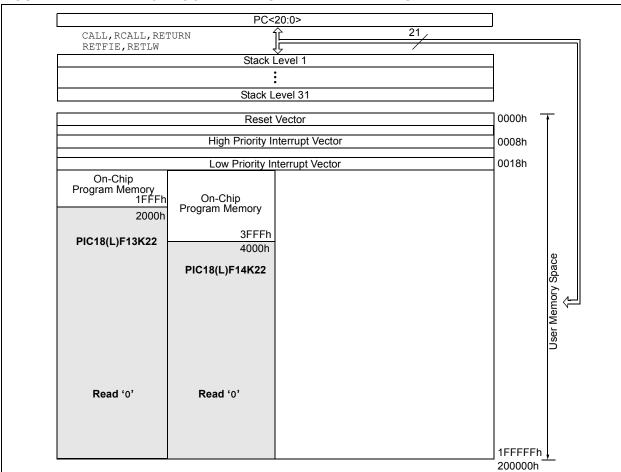

PIC18 devices are capable of addressing a 2-Mbyte program memory space, as seen in Figure 2-7. PIC18 devices also have two interrupt vectors, whereas the enhanced PIC devices only have one. A stark difference is that the PIC18 has no concept of pages, whereas the enhanced core has its program memory split into different pages.

Changing pages is necessary in the enhanced core when changing execution from one page to another. None of the lessons for the enhanced PIC16 occupy more than one page and, therefore, page changes are not necessary. If the code does overflow into another page, the assembler will give a warning, indicating that a pagesel may be required.

#### FIGURE 2-7: PIC18 PROGRAM MEMORY MAP AND CALL STACK

#### 2.12.5 User ID

These four memory locations are designated as ID locations where the programmer can store checksum or other code identification numbers. These are readable and writable during normal execution.

#### 2.13 DATA MEMORY

The data memory layout of the two device families is perhaps the most significant. Data memory on both families can be split into four types:

- 1. Core Registers

- Special Function Registers

- 3. General Purpose RAM

- 4. Common RAM

#### 2.13.1 Core Registers

The core registers contain the registers that directly affect the basic operation of the PIC device, repeated at the top of every data memory bank. Here are three examples of the 12 core registers:

- 1. STATUS

- 2. WREG

- INTCON

The STATUS register contains the arithmetic status of the ALU. The WREG register is used to move bits in and out of registers. The INTCON register contains the various enable and flag bits that would cause the PIC MCU to jump to the Interrupt Vector.

#### 2.13.2 Special Function Registers

The Special Function Registers provide access to the peripheral functions in the device. The Special Function Registers occupy 20 bytes immediately after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh) on the enhanced mid-range core. The PIC18 enhanced core has all of its SFRs in Access RAM, which is discussed in **Section 2.14 "Banks"**.

#### 2.13.3 General Purpose RAM

GPRs are used for data storage and scratchpad operations in the user's application. Think of this as RAM that can be used for your program, but the correct bank must be selected before using. For the enhanced mid-range PIC devices, there are up to 80 bytes of GPR that follow immediately after the SFR space in each data memory bank.

#### 2.13.4 Common RAM

There are 16 bytes of common RAM accessible from all banks in the enhanced core. The PIC18 architecture has something similar called Access RAM, which contains up to 96 bytes.

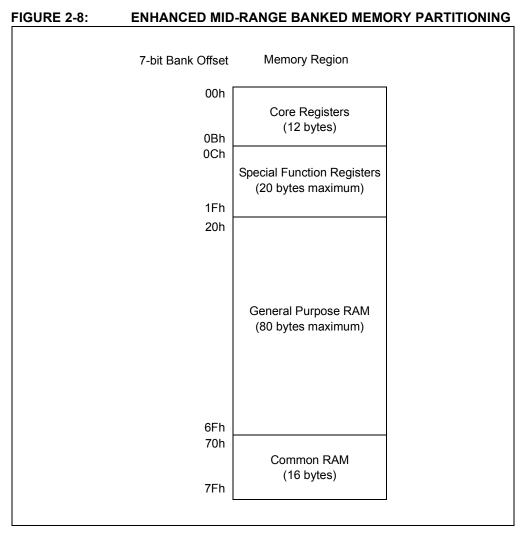

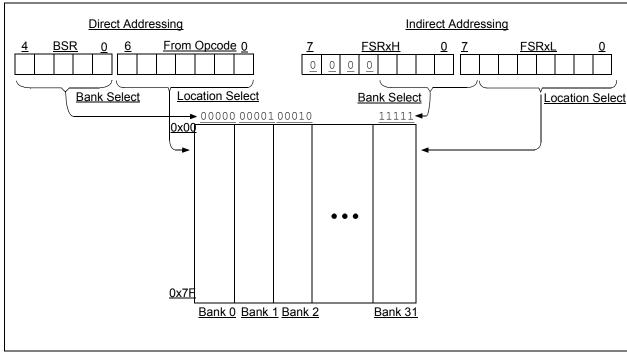

#### **2.14 BANKS**

The PIC18F14K22 data memory is divided into 16 banks that contain 256 bytes each. The PIC16F1829 data memory is partitioned in 32 memory banks with 128 bytes in each bank. For the PIC16 enhanced mid-range, each bank consists of:

- 1. 12 core registers

- 2. 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 4. 16 bytes of shared RAM (accessible by any bank)

Figure 2-8 shows the above information on the enhanced PIC16.

Addresses 70h-7Fh are shared by all of the banks. This is useful for storing a few bytes of RAM without the need to switch banks each time the byte is used. Figure 2-9 shows the first eight banks on the PIC16F1829. Notice how the top 12 core registers are accessible from every bank, as are the 16 bytes of common RAM.

DS41628B-page 30

FIGURE 2-9: PIC16F1829 MEMORY MAP – THE CORRECT BANK MUST BE SELECTED BEFORE WRITING/READING FROM A REGISTER

|              | BANK 0                         |              | BANK 1                                     |               | BANK 2                                     |              | BANK 3                                     |               | BANK 4                                     |              | BANK 5                                     |               | BANK 6                                     |              | BANK 7                                     |

|--------------|--------------------------------|--------------|--------------------------------------------|---------------|--------------------------------------------|--------------|--------------------------------------------|---------------|--------------------------------------------|--------------|--------------------------------------------|---------------|--------------------------------------------|--------------|--------------------------------------------|

| 000h         | INDF0                          | 080h         | INDF0                                      | 100h          | INDF0                                      | 180h         | INDF0                                      | 200h          | INDF0                                      | 280h         | INDF0                                      | 300h          | INDF0                                      | 380h         | INDF0                                      |

| 001h         | INDF1                          | 081h         | INDF1                                      | 101h          | INDF1                                      | 181h         | INDF1                                      | 201h          | INDF1                                      | 281h         | INDF1                                      | 301h          | INDF1                                      | 381h         | INDF1                                      |

| 002h         | PCL                            | 082h         | PCL                                        | 102h          | PCL                                        | 182h         | PCL                                        | 202h          | PCL                                        | 282h         | PCL                                        | 302h          | PCL                                        | 382h         | PCL                                        |

| 003h         | STATUS                         | 083h         | STATUS                                     | 103h          | STATUS                                     | 183h         | STATUS                                     | 203h          | STATUS                                     | 283h         | STATUS                                     | 303h          | STATUS                                     | 383h         | STATUS                                     |

| 004h         | FSR0L                          | 084h         | FSR0L                                      | 104h          | FSR0L                                      | 184h         | FSR0L                                      | 204h          | FSR0L                                      | 284h         | FSR0L                                      | 304h          | FSR0L                                      | 384h         | FSR0L                                      |

| 005h         | FSR0H                          | 085h         | FSR0H                                      | 105h          | FSR0H                                      | 185h         | FSR0H                                      | 205h          | FSR0H                                      | 285h         | FSR0H                                      | 305h          | FSR0H                                      | 385h         | FSR0H                                      |

| 006h         | FSR1L<br>FSR1H                 | 086h<br>087h | FSR1L<br>FSR1H                             | 106h<br>107h  | FSR1L<br>FSR1H                             | 186h<br>187h | FSR1L<br>FSR1H                             | 206h<br>207h  | FSR1L<br>FSR1H                             | 286h<br>287h | FSR1L<br>FSR1H                             | 306h<br>307h  | FSR1L<br>FSR1H                             | 386h<br>387h | FSR1L<br>FSR1H                             |

| 007h<br>008h | BSR                            | 088h         | BSR                                        | 10711<br>108h | BSR                                        | 188h         | BSR                                        | 20711<br>208h | BSR                                        | 288h         | BSR                                        | 30711<br>308h | BSR                                        | 388h         | BSR                                        |

| 009h         | WREG                           | 089h         | WREG                                       | 100h          | WREG                                       | 189h         | WREG                                       | 209h          | WREG                                       | 289h         | WREG                                       | 309h          | WREG                                       | 389h         | WREG                                       |

| 00Ah         | PCLATH                         | 08Ah         | PCLATH                                     | 10Ah          | PCLATH                                     | 18Ah         | PCLATH                                     | 20Ah          | PCLATH                                     | 28Ah         | PCLATH                                     | 30Ah          | PCLATH                                     | 38Ah         | PCLATH                                     |

| 00Bh         | INTCON                         | 08Bh         | INTCON                                     | 10Bh          | INTCON                                     | 18Bh         | INTCON                                     | 20Bh          | INTCON                                     | 28Bh         | INTCON                                     | 30Bh          | INTCON                                     | 38Bh         | INTCON                                     |

| 00Ch         | PORTA                          | 08Ch         | TRISA                                      | 10Ch          | LATA                                       | 18Ch         | ANSELA                                     | 20Ch          | WPUA                                       | 28Ch         | -                                          | 30Ch          | _                                          | 38Ch         | INLVLA                                     |

| 00Dh         | PORTB <sup>(1)</sup>           | 08Dh         | TRISB <sup>(1)</sup>                       | 10Dh          | LATB <sup>(1)</sup>                        | 18Dh         | ANSELB <sup>(1)</sup>                      | 20Dh          | WPUB <sup>(1)</sup>                        | 28Dh         | _                                          | 30Dh          | _                                          | 38Dh         | INLVLB <sup>(1)</sup>                      |

| 00Eh         | PORTC                          | 08Eh         | TRISC                                      | 10Eh          | LATC                                       | 18Eh         | ANSELC                                     | 20Eh          | WPUC                                       | 28Eh         | ı                                          | 30Eh          | _                                          | 38Eh         | INLVLC                                     |

| 00Fh         |                                | 08Fh         | _                                          | 10Fh          |                                            | 18Fh         |                                            | 20Fh          |                                            | 28Fh         |                                            | 30Fh          |                                            | 38Fh         | _                                          |

| 010h         | _                              | 090h         | _                                          | 110h          |                                            | 190h         |                                            | 210h          |                                            | 290h         |                                            | 310h          |                                            | 390h         | _                                          |

| 011h         | PIR1                           | 091h         | PIE1                                       | 111h          | CM1CON0                                    | 191h         | EEADRL                                     | 211h          | SSP1BUF                                    | 291h         | CCPR1L                                     | 311h          | CCPR3L                                     | 391h         | IOCAP                                      |

| 012h         | PIR2                           | 092h         | PIE2                                       | 112h          | CM1CON1                                    | 192h         | EEADRH                                     | 212h          | SSP1ADD                                    | 292h         | CCPR1H                                     | 312h          | CCPR3H                                     | 392h         | IOCAN                                      |

| 013h         |                                | 093h         | _                                          | 113h          | CM2CON0                                    | 193h         | EEDATL                                     | 213h          | SSP1MSK                                    | 293h         | CCP1CON                                    | 313h          | CCP3CON                                    | 393h         | IOCAF                                      |

| 014h         | _                              | 094h         | _                                          | 114h          | CM2CON1                                    | 194h         | EEDATH                                     | 214h          | SSP1STAT                                   | 294h         | PWM1CON                                    | 314h          | _                                          | 394h         | IOCBP <sup>(1)</sup>                       |

| 015h         | TMR0                           | 095h         | OPTION_REG                                 | 115h          | CMOUT                                      | 195h         | EECON1                                     | 215h          | SSP1CON                                    | 295h         | CCP1AS                                     | 315h          | _                                          | 395h         | IOCBN <sup>(1)</sup>                       |

| 016h         | TMR1L                          | 096h         | PCON                                       | 116h          | BORCON                                     | 196h         | EECON2                                     | 216h          | SSP1CON2                                   | 296h         | PSTR1CON                                   | 316h          | _                                          | 396h         | IOCBF <sup>(1)</sup>                       |

| 017h         | TMR1H                          | 097h         | WDTCON                                     | 117h          | FVRCON                                     | 197h         | _                                          | 217h          | SSP1CON3                                   | 297h         | _                                          | 317h          | _                                          | 397h         | -                                          |

| 018h         | T1CON                          | 098h         | OSCTUNE                                    | 118h          | DACCON0                                    | 198h         | _                                          | 218h          | _                                          | 298h         | CCPR2L                                     | 318h          | CCPR4L                                     | 398h         | _                                          |

| 019h         | T1GCON                         | 099h         | OSCCON                                     | 119h          | DACCON1                                    | 199h         | RCREG                                      | 219h          | SSP2BUF <sup>(1)</sup>                     | 299h         | CCPR2H                                     | 319h          | CCPR4H                                     | 399h         | _                                          |

| 01Ah         | TMR2                           | 09Ah         | OSCSTAT                                    | 11Ah          | SRCON0                                     | 19Ah         | TXREG                                      | 21Ah          | SSP2ADD <sup>(1)</sup>                     | 29Ah         | CCP2CON                                    | 31Ah          | CCP4CON                                    | 39Ah         | CLKRCON                                    |

| 01Bh         | PR2                            | 09Bh         | ADRESL                                     | 11Bh          | SRCON1                                     | 19Bh         | SPBRGL                                     | 21Bh          | SSP2MSK <sup>(1)</sup>                     | 29Bh         | PWM2CON                                    | 31Bh          |                                            | 39Bh         | _                                          |

| 01Ch         | T2CON                          | 09Ch         | ADRESH                                     | 11Ch          |                                            | 19Ch         | SPBRGH                                     | 21Ch          | SSP2STAT <sup>(1)</sup>                    | 29Ch         | CCP2AS                                     | 31Ch          |                                            | 39Ch         | MDCON                                      |

| 01Dh         |                                | 09Dh         | ADCON0                                     | 11Dh          | APFCON0                                    | 19Dh         | RCSTA                                      | 21Dh          | SSP2CON <sup>(1)</sup>                     | 29Dh         | PSTR2CON                                   | 31Dh          | _                                          | 39Dh         | MDSRC                                      |

| 01Eh         | CPSCON0                        | 09Eh         | ADCON1                                     | 11Eh          | APFCON1                                    | 19Eh         | TXSTA                                      | 21Eh          | SSP2CON2 <sup>(1)</sup>                    | 29Eh         | CCPTMRS                                    | 31Eh          |                                            | 39Eh         | MDCARL                                     |

| 01Fh         | CPSCON1                        | 09Fh         | _                                          | 11Fh          | _                                          | 19Fh         | BAUDCON                                    | 21Fh          | SSP2CON3 <sup>(1)</sup>                    | 29Fh         | _                                          | 31Fh          | _                                          | 39Fh         | MDCARH                                     |

| 020h         |                                | 0A0h         |                                            | 120h          |                                            | 1A0h         |                                            | 220h          |                                            | 2A0h         |                                            | 320h          |                                            | 3A0h         |                                            |

| 06Fh         | General<br>Purpose<br>Register | 0EFh         | General<br>Purpose<br>Register<br>80 Bytes | 16Fh          | General<br>Purpose<br>Register<br>80 Bytes | 1EFh         | General<br>Purpose<br>Register<br>80 Bytes | 26Fh          | General<br>Purpose<br>Register<br>80 Bytes | 2EFh         | General<br>Purpose<br>Register<br>80 Bytes | 36Fh          | General<br>Purpose<br>Register<br>80 Bytes | 3EFh         | General<br>Purpose<br>Register<br>80 Bytes |

| 070h         | 96 Bytes                       | 0F0h         |                                            | 170h          |                                            | 1F0h         |                                            | 270h          |                                            | 2F0h         |                                            | 370h          |                                            | 3F0h         |                                            |

|              |                                |              | Accesses<br>70h – 7Fh                      |               | Accesses<br>70h – 7Fh                      |              | Accesses<br>70h – 7Fh                      |               | Accesses<br>70h – 7Fh                      |              | Accesses<br>70h – 7Fh                      |               | Accesses<br>70h – 7Fh                      |              | Accesses<br>70h – 7Fh                      |

| 07Fh         |                                | 0FFh         |                                            | 17Fh          |                                            | 1FFh         |                                            | 27Fh          |                                            | 2FFh         |                                            | 37Fh          |                                            | 3FFh         |                                            |

**Legend:** = Unimplemented data memory locations, read as '0'.

Note 1: Available only on PIC16(L)F1829.

# **PIC® MCU Architecture**

When using the PIC16F1829 in assembly, the reader will be constantly referring back to Figure 2-9 to make sure that the right bank is selected before writing to an SFR.

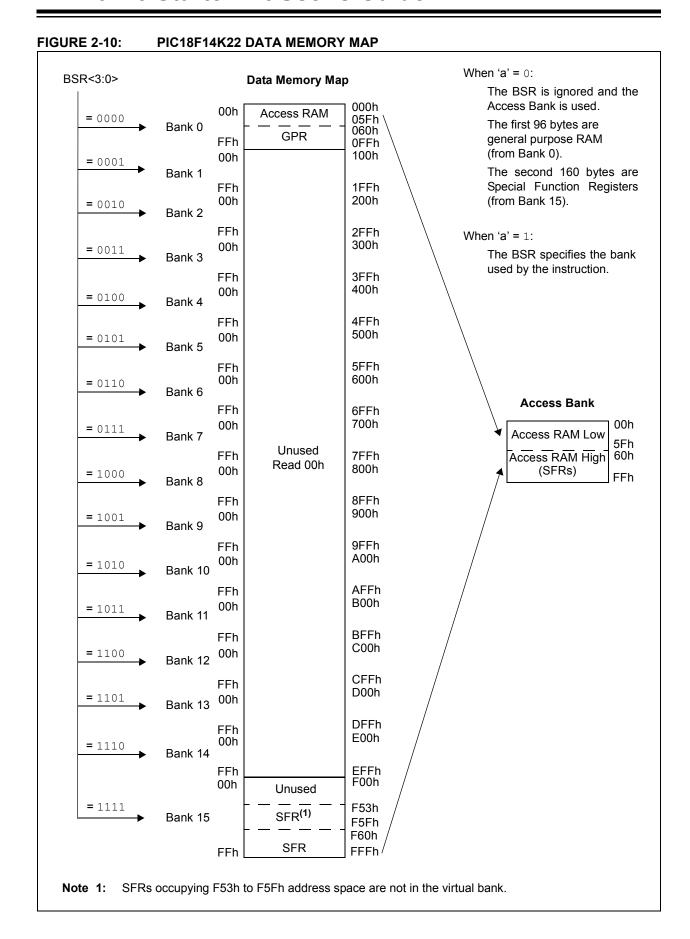

For PIC18 devices, the banking situation was streamlined so that the user does not have to switch banks when using the access SFRs. The data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a Bank Select Register (BSR). The Access Bank consists of the first 96 bytes of memory in Bank 0 and the last 160 bytes of memory in Bank Block 15. This lower half is known as the "Access RAM" and is composed of GPRs. The upper half is where the device's SFRs are mapped (Bank 15). When going through the assembly lessons, the reader will notice the absence of bank switching. Figure 2-10 and Figure 2-11 show this improved mapping scheme.

**FIGURE 2-11:** PIC18F14K22 SPECIAL FUNCTION REGISTER MAP - ALL OF THESE ARE IN BANK 15 WHICH IS INCLUDED IN THE "ACCESS RAM"

| Address  | Name                    | Address     | Name             | Address    | Name                  | Address | Name    | Address | Name |

|----------|-------------------------|-------------|------------------|------------|-----------------------|---------|---------|---------|------|

| FFFh     | TOSU                    | FD7h        | TMR0H            | FAFh       | SPBRG                 | F87h    | (2)     | F5Fh    | (2)  |

| FFEh     | TOSH                    | FD6h        | TMR0L            | FAEh       | RCREG                 | F86h    | (2)     | F5Eh    | (2)  |

| FFDh     | TOSL                    | FD5h        | T0CON            | FADh       | TXREG                 | F85h    | (2)     | F5Dh    | (2)  |

| FFCh     | STKPTR                  | FD4h        | (2)              | FACh       | TXSTA                 | F84h    | (2)     | F5Ch    | (2)  |

| FFBh     | PCLATU                  | FD3h        | OSCCON           | FABh       | RCSTA                 | F83h    | (2)     | F5Bh    | (2)  |

| FFAh     | PCLATH                  | FD2h        | OSCCON2          | FAAh       | (2)                   | F82h    | PORTC   | F5Ah    | (2)  |

| FF9h     | PCL                     | FD1h        | WDTCON           | FA9h       | EEADR                 | F81h    | PORTB   | F59h    | (2)  |

| FF8h     | TBLPTRU                 | FD0h        | RCON             | FA8h       | EEDATA                | F80h    | PORTA   | F58h    | (2)  |

| FF7h     | TBLPTRH                 | FCFh        | TMR1H            | FA7h       | EECON2 <sup>(1)</sup> | F7Fh    | ANSELH  | F57h    | (2)  |

| FF6h     | TBLPTRL                 | FCEh        | TMR1L            | FA6h       | EECON1                | F7Eh    | ANSEL   | F56h    | (2)  |

| FF5h     | TABLAT                  | FCDh        | T1CON            | FA5h       | (2)                   | F7Dh    | (2)     | F55h    | (2)  |

| FF4h     | PRODH                   | FCCh        | TMR2             | FA4h       | (2)                   | F7Ch    | (2)     | F54h    | (2)  |

| FF3h     | PRODL                   | FCBh        | PR2              | FA3h       | (2)                   | F7Bh    | (2)     | F53h    | (2)  |

| FF2h     | INTCON                  | FCAh        | T2CON            | FA2h       | IPR2                  | F7Ah    | IOCB    |         | _    |

| FF1h     | INTCON2                 | FC9h        | SSPBUF           | FA1h       | PIR2                  | F79h    | IOCA    |         |      |

| FF0h     | INTCON3                 | FC8h        | SSPADD           | FA0h       | PIE2                  | F78h    | WPUB    |         |      |

| FEFh     | INDF0 <sup>(1)</sup>    | FC7h        | SSPSTAT          | F9Fh       | IPR1                  | F77h    | WPUA    |         |      |

| FEEh     | POSTINC0 <sup>(1)</sup> | FC6h        | SSPCON1          | F9Eh       | PIR1                  | F76h    | SLRCON  |         |      |

| FEDh     | POSTDEC0 <sup>(1)</sup> | FC5h        | SSPCON2          | F9Dh       | PIE1                  | F75h    | (2)     |         |      |

| FECh     | PREINC0 <sup>(1)</sup>  | FC4h        | ADRESH           | F9Ch       | _(2)                  | F74h    | (2)     |         |      |

| FEBh     | PLUSW0 <sup>(1)</sup>   | FC3h        | ADRESL           | F9Bh       | OSCTUNE               | F73h    | (2)     |         |      |

| FEAh     | FSR0H                   | FC2h        | ADCON0           | F9Ah       | (2)                   | F72h    | (2)     |         |      |

| FE9h     | FSR0L                   | FC1h        | ADCON1           | F99h       | _(2)                  | F71h    | (2)     |         |      |

| FE8h     | WREG                    | FC0h        | ADCON2           | F98h       | (2)                   | F70h    | (2)     |         |      |

| FE7h     | INDF1 <sup>(1)</sup>    | FBFh        | CCPR1H           | F97h       | (2)                   | F6Fh    | SSPMASK |         |      |

| FE6h     | POSTINC1 <sup>(1)</sup> | FBEh        | CCPR1L           | F96h       | (2)                   | F6Eh    | (2)     |         |      |

| FE5h     | POSTDEC1 <sup>(1)</sup> | FBDh        | CCP1CON          | F95h       | (2)                   | F6Dh    | CM1CON0 |         |      |

| FE4h     | PREINC1 <sup>(1)</sup>  | FBCh        | VREFCON2         | F94h       | TRISC                 | F6Ch    | CM2CON1 |         |      |

| FE3h     | PLUSW1 <sup>(1)</sup>   | FBBh        | VREFCON1         | F93h       | TRISB                 | F6Bh    | CM2CON0 |         |      |

| FE2h     | FSR1H                   | FBAh        | VREFCON0         | F92h       | TRISA                 | F6Ah    | (2)     |         |      |

| FE1h     | FSR1L                   | FB9h        | PSTRCON          | F91h       | (2)                   | F69h    | SRCON1  |         |      |

| FE0h     | BSR                     | FB8h        | BAUDCON          | F90h       | (2)                   | F68h    | SRCON0  |         |      |

| FDFh     | INDF2 <sup>(1)</sup>    | FB7h        | PWM1CON          | F8Fh       | (2)                   | F67h    | (2)     |         |      |

| FDEh     | POSTINC2 <sup>(1)</sup> | FB6h        | ECCP1AS          | F8Eh       | (2)                   | F66h    | (2)     |         |      |

| FDDh     | POSTDEC2 <sup>(1)</sup> | FB5h        | (2)              | F8Dh       | (2)                   | F65h    | (2)     |         |      |

| FDCh     | PREINC2 <sup>(1)</sup>  | FB4h        | (2)              | F8Ch       | (2)                   | F64h    | (2)     |         |      |

| FDBh     | PLUSW2 <sup>(1)</sup>   | FB3h        | TMR3H            | F8Bh       | LATC                  | F63h    | (2)     |         |      |

| FDAh     | FSR2H                   | FB2h        | TMR3L            | F8Ah       | LATB                  | F62h    | (2)     |         |      |

| FD9h     | FSR2L                   | FB1h        | T3CON            | F89h       | LATA                  | F61h    | (2)     |         |      |

| FD8h     | STATUS                  | FB0h        | SPBRGH           | F88h       | (2)                   | F60h    | (2)     |         |      |

| I egend: | = Unimplement           | ed data men | nory locations r | ead as '∩' |                       |         |         |         |      |

**Legend:** = Unimplemented data memory locations, read as '0',

Note 1: This is not a physical register.

2: Unimplemented registers are read as '0'.

All of the SFRs in Figure 2-9 are in Bank 15 and do not require banking since this bank is covered by the Access Bank. Switching banks in the enhanced mid-range core requires two instructions, so this could potentially save a great number of instructions in the overall program.

#### 2.15 DATA EEPROM MEMORY

The data EEPROM is a nonvolatile memory array, separate from both the data RAM, and program memory, which is used for long-term storage of program data. The EEPROM is not directly mapped in either the register file or program memory space, but is indirectly addressed through special SFRs. The EEPROM is readable and writable during normal operation.

The PIC16F1829 and PIC18F14K22 have 256 bytes of EEPROM on board.

The EEPROM is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data. Please see **Section 3.14 "Lesson 13: EEPROM"** for more information.

#### 2.16 PROGRAMMING BASICS

This section will briefly discuss essential assembler and 'C' basics. There are better suited tutorials on 'C' programming on the web if the user wishes to learn more.

This guide uses the XC8 compiler v.1.00 for both the PIC16F1829 and PIC18F14K22. Later versions of the compiler will also work. Looking at the XC8 user's guide would be a very good start. One of the great benefits of using 'C' is that it is very portable and will build in most compilers with no problem.

The assembly is not compiled, but rather assembled by a utility called MPASM. This guide uses MPASM assembler v5.43, which is a universal assembler for all PIC1X devices.

A key advantage of using a high-level language (such as C) is that the programmer does not need to understand the architecture of the microprocessor being used. Knowledge of the architecture is left to the compiler which will take the 'C' and compile it into assembly. When using assembly, the programmer must use the PIC device's instruction set and understand the memory map. A positive benefit of assembly is not only the knowledge gained, but also the code size will be considerably smaller.

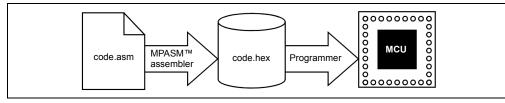

#### 2.16.1 MPASM™ Assembler Operation

All of the lessons written in are absolute code. This means that everything that the assembler needs is contained in the source files. This process is shown below.

FIGURE 2-12: MPASM ASSEMBLER OPERATION

When a source file is assembled in this manner, all variables and routines used in the source file must be defined within that source file, or in files that have been explicitly included by that source file. If assembly proceeds without errors, a hex file will be generated that contains the executable machine code for the targeted PIC device. This file can then be used by the debugger to test code execution, and by a device programmer to program the microcontroller.

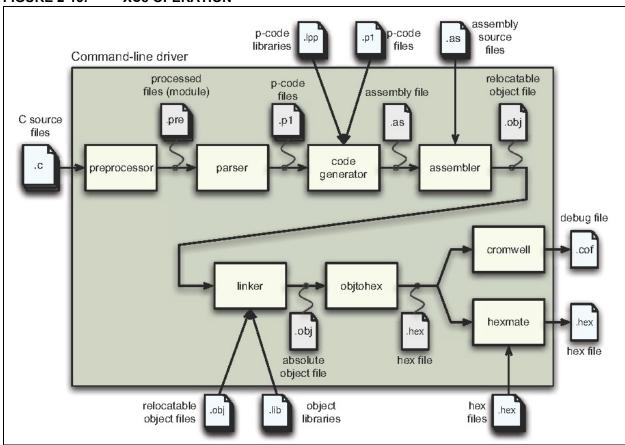

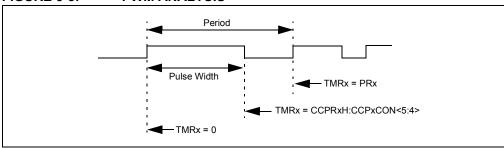

#### 2.16.2 XC8 Operation