# MICROCHIP SST26VF064B / SST26VF064BA

## 2.5V/3.0V 64 Mbit Serial Quad I/O (SQI) Flash Memory

### Features

- Single Voltage Read and Write Operations

2.7-3.6V or 2.3-3.6V

- Serial Interface Architecture

- Nibble-wide multiplexed I/O's with SPI-like serial command structure

- Mode 0 and Mode 3

- x1/x2/x4 Serial Peripheral Interface (SPI) Protocol

- High Speed Clock Frequency

- 2.7-3.6V: 104 MHz max

- 2.3-3.6V: 80 MHz max

- Burst Modes

- Continuous linear burst

- 8/16/32/64 Byte linear burst with wrap-around

- Superior Reliability

- Endurance: 100,000 Cycles (min)

- Greater than 100 years Data Retention

- Low Power Consumption:

- Active Read current: 15 mA (typical @ 104 MHz)

- Standby Current: 15 µA (typical)

- Fast Erase Time

- Sector/Block Erase: 18 ms (typ), 25ms (max)

- Chip Erase: 35 ms (typ), 50 ms (max)

- Page-Program

- 256 Bytes per page in x1 or x4 mode

- End-of-Write Detection

- Software polling the BUSY bit in status register

- Flexible Erase Capability

- Uniform 4 KByte sectors

- Four 8 KByte top and bottom parameter overlay blocks

- One 32 KByte top and bottom overlay block

- Uniform 64 KByte overlay blocks

- Write-Suspend

- Suspend Program or Erase operation to access another block/sector

- Software Reset (RST) mode

- Software Protection

- Individual-Block Write Protection with permanent lock-down capability

- 64 KByte blocks, two 32 KByte blocks, and eight 8 KByte parameter blocks

- Read Protection on top and bottom 8 KByte parameter blocks

- Security ID

- One-Time Programmable (OTP) 2 KByte, Secure ID

- 64 bit unique, factory pre-programmed identifier

- User-programmable area

- Temperature Range

- Industrial: -40°C to +85°C

- Extended: -40°C to +105°C

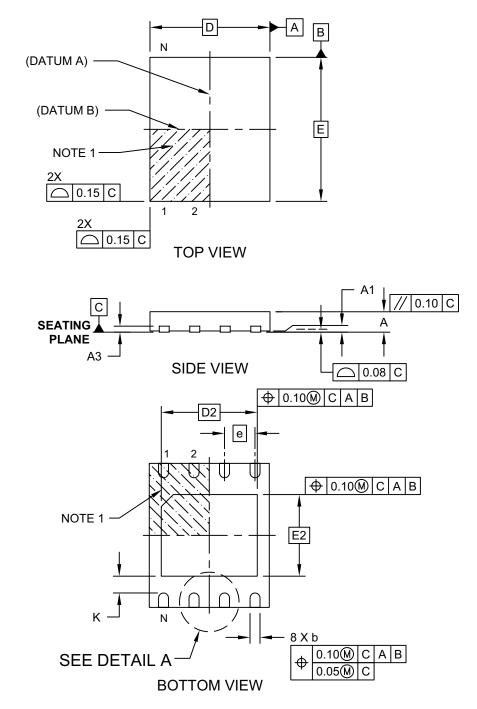

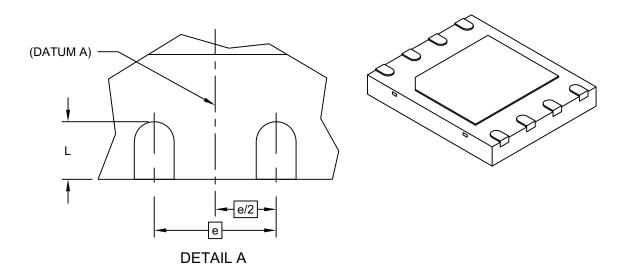

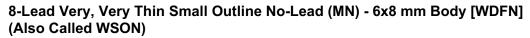

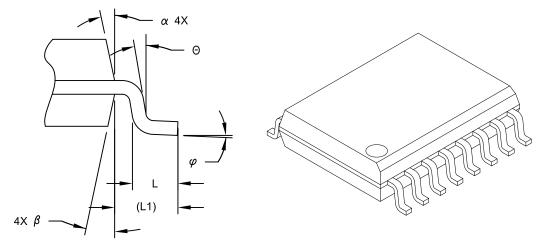

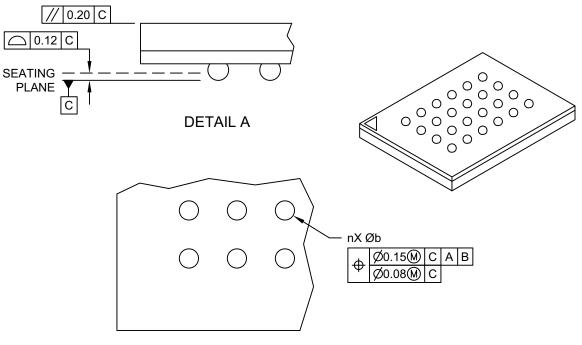

- · Packages Available

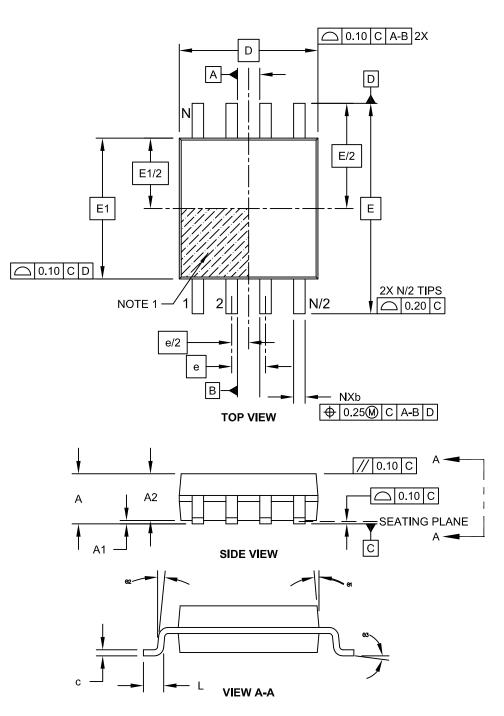

- 8-contact WDFN (6mm x 5mm)

- 8-contact WDFN (6mm x 8 mm)

- 8-lead SOIJ (5.28 mm)

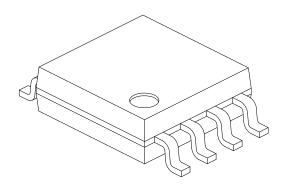

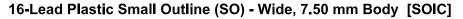

- 16-lead SOIC (7.50 mm)

- 24-ball TBGA (6mm x 8mm)

- All devices are RoHS compliant

### **Product Description**

The Serial Quad I/O<sup>™</sup> (SQI<sup>™</sup>) family of flash-memory devices features a six-wire, 4-bit I/O interface that allows for low-power, high-performance operation in a low pin-count package. SST26VF064B/064BA also support full command-set compatibility to traditional Serial Peripheral Interface (SPI) protocol. System designs using SQI flash devices occupy less board space and ultimately lower system costs.

All members of the 26 Series, SQI family are manufactured with proprietary, high-performance CMOS Super-Flash® technology. The split-gate cell design and thickoxide tunneling injector attain better reliability and manufacturability compared with alternate approaches.

SST26VF064B/064BA significantly improve performance and reliability, while lowering power consumption. These devices write (Program or Erase) with a single power supply of 2.3-3.6V. The total energy consumed is a function of the applied voltage, current, and time of application. Since for any given voltage range, the SuperFlash technology uses less current to program and has a shorter erase time, the total energy consumed during any Erase or Program operation is less than alternative flash memory technologies.

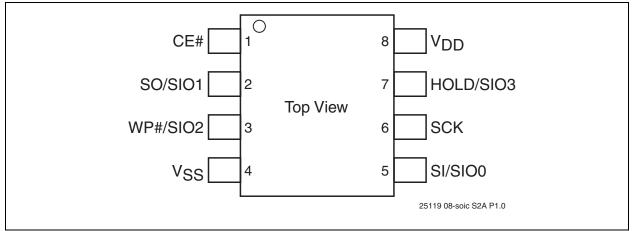

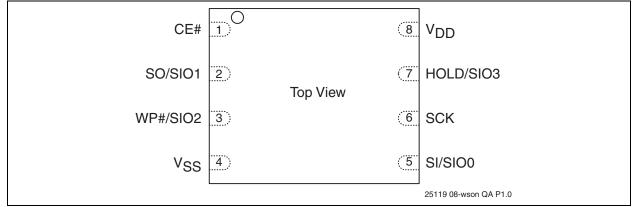

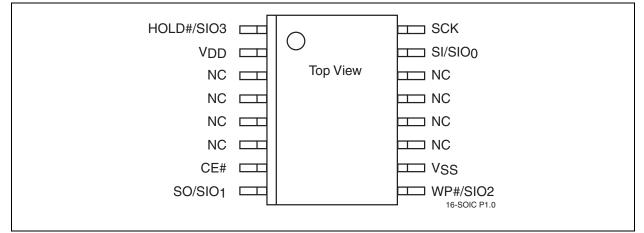

SST26VF064B/064BA are offered in 8-contact WDFN (6 mm x 5 mm or 6mm x 8mm), 8-lead SOIJ (5.28 mm), 16-lead SOIC (7.50 mm), and 24-ball TBGA. See Figure 2-2 for pin assignments.

Two configurations are available upon order. SST26VF064B default at power-up has the WP# and HOLD# pins enabled, and the SIO2 and SIO3 pins disabled, to initiate SPI-protocol operations. SST26VF064BA default at power-up has the WP# and HOLD# pins disabled, and the SIO2 and SIO3 pins enabled, to initiate Quad I/O operations. See "I/O Configuration (IOC)" on page 12 for more information about configuring WP#/HOLD# and SIO3/SIO4 pins

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

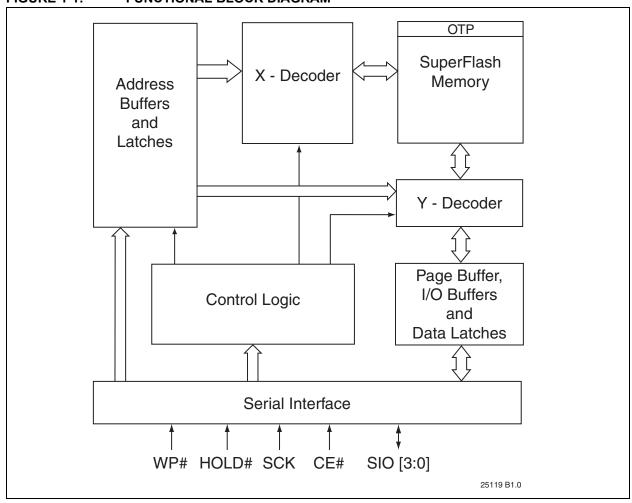

### 1.0 BLOCK DIAGRAM

FIGURE 1-1: FUNCTIONAL BLOCK DIAGRAM

### 2.0 PIN DESCRIPTION

### FIGURE 2-1: PIN DESCRIPTION FOR 8-LEAD SOIJ

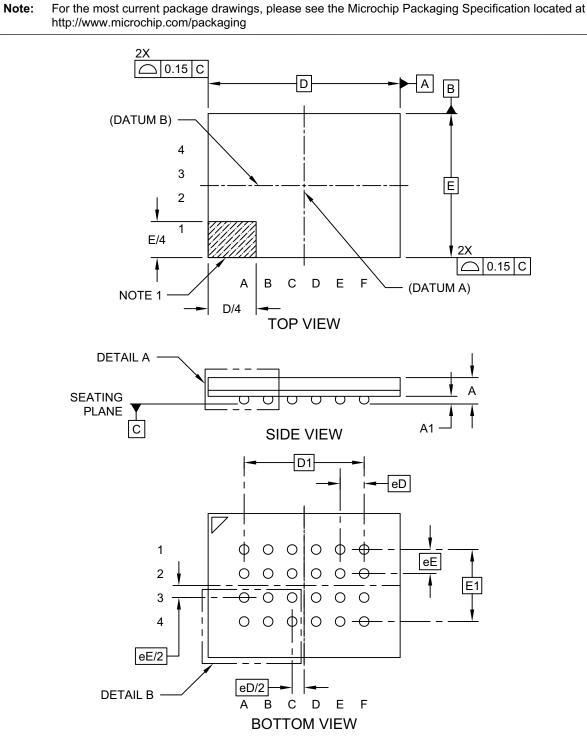

FIGURE 2-3: PIN DES

PIN DESCRIPTION FOR 16-LEAD SOIC

| FIGURE 2-4: | P | IN DESCRIPT | ION FC                 | JR 24-B    |                                                         | A        |          |          |  |  |

|-------------|---|-------------|------------------------|------------|---------------------------------------------------------|----------|----------|----------|--|--|

|             |   |             |                        | Тор        | View                                                    |          |          |          |  |  |

|             | 4 | ())<br>NC   | ())<br>V <sub>DD</sub> | ()<br>WP#/ | ()<br>HOLD#/                                            | ()<br>NC | ()<br>NC |          |  |  |

|             | 3 | ()<br>NC    | V <sub>SS</sub>        | SIQ2<br>NC | ())#/<br>HOLD3<br>SIO<br>SIO<br>SIO<br>SIO<br>SIO<br>NC | ()<br>NC | NC       |          |  |  |

| :           | 2 | ()<br>NC    | SCK                    | ()<br>CE#  | SIO1                                                    | NC       | NC       |          |  |  |

|             | 1 | ()<br>NC    | NC                     | ()<br>NC   | NC                                                      | NC       | NC       |          |  |  |

|             |   |             |                        |            |                                                         |          |          |          |  |  |

|             |   | А           | В                      | С          | D                                                       | Е        | F        | T4D-P1.0 |  |  |

### FIGURE 2-4: PIN DESCRIPTION FOR 24-BALL TBGA

### TABLE 2-1: PIN DESCRIPTION

| Symbol          | Pin Name                           | Functions                                                                                                                                                                                                                                                                                                    |

|-----------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK             | Serial Clock                       | To provide the timing of the serial interface.<br>Commands, addresses, or input data are latched on the rising edge of the clock<br>input, while output data is shifted out on the falling edge of the clock input.                                                                                          |

| SIO[3:0]        | Serial Data<br>Input/Output        | To transfer commands, addresses, or data serially into the device or data out of the device. Inputs are latched on the rising edge of the serial clock. Data is shifted out on the falling edge of the serial clock. The Enable Quad I/O (EQIO) command instruction configures these pins for Quad I/O mode. |

| SI              | Serial Data Input<br>for SPI mode  | To transfer commands, addresses or data serially into the device. Inputs are latched on the rising edge of the serial clock. SI is the default state after a power on reset.                                                                                                                                 |

| SO              | Serial Data Output<br>for SPI mode | To transfer data serially out of the device. Data is shifted out on the falling edge of the serial clock. SO is the default state after a power on reset.                                                                                                                                                    |

| CE#             | Chip Enable                        | The device is enabled by a high to low transition on CE#. CE# must remain low for the duration of any command sequence; or in the case of Write operations, for the command/data input sequence.                                                                                                             |

| WP#             | Write Protect                      | The WP# is used in conjunction with the WPEN and IOC bits in the Configura-<br>tion register to prohibit write operations to the Block-Protection register. This pin<br>only works in SPI, single-bit and dual-bit Read mode.                                                                                |

| HOLD#           | Hold                               | Temporarily stops serial communication with the SPI Flash memory while the device is selected. This pin only works in SPI, single-bit and dual-bit Read mode and must be tied high when not in use.                                                                                                          |

| V <sub>DD</sub> | Power Supply                       | To provide power supply voltage.                                                                                                                                                                                                                                                                             |

| V <sub>SS</sub> | Ground                             |                                                                                                                                                                                                                                                                                                              |

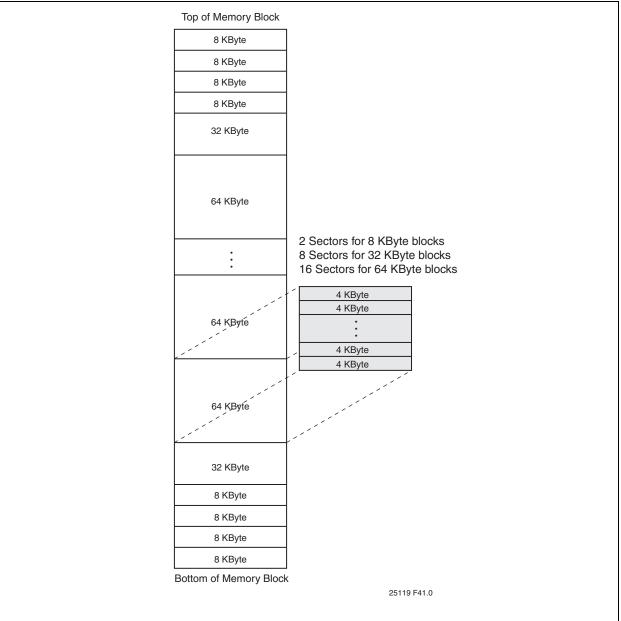

### 3.0 MEMORY ORGANIZATION

The SST26VF064B/064BA SQI memory array is organized in uniform, 4 KByte erasable sectors with the following erasable blocks: eight 8 KByte parameter, two 32 KByte overlay, and one-hundred twenty-six 64 KByte overlay blocks. See Figure 3-1.

### FIGURE 3-1: MEMORY MAP

#### 4.0 **DEVICE OPERATION**

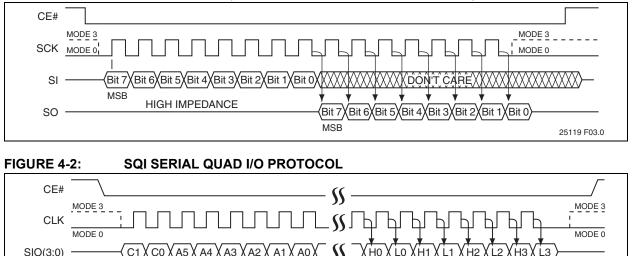

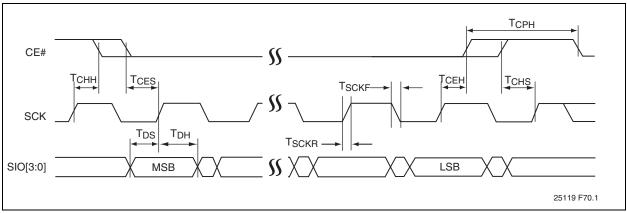

SST26VF064B/064BA support both Serial Peripheral Interface (SPI) bus protocol and a 4-bit multiplexed SQI bus protocol. To provide backward compatibility to traditional SPI Serial Flash devices, the device's initial state after a power-on reset is SPI mode which supports multi-I/O (x1/x2/x4) Read/Write commands. A command instruction configures the device to SQI mode. The dataflow in the SQI mode is similar to the SPI mode, except it uses four multiplexed I/O signals for command, address, and data sequence.

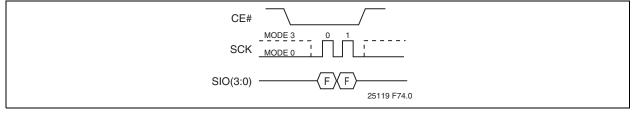

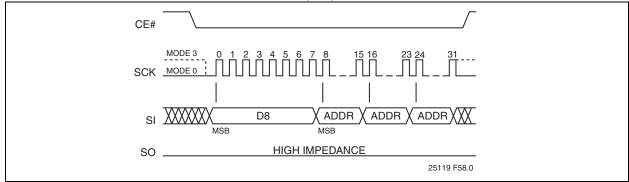

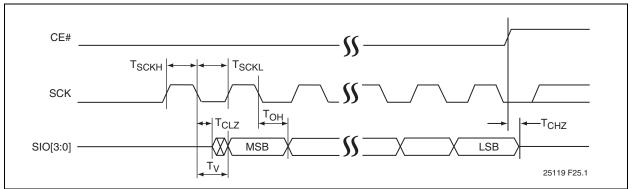

SQI Flash Memory supports both Mode 0 (0,0) and Mode 3 (1,1) bus operations. The difference between the two modes is the state of the SCK signal when the

bus master is in stand-by mode and no data is being transferred. The SCK signal is low for Mode 0 and SCK signal is high for Mode 3. For both modes, the Serial Data I/O (SIO[3:0]) is sampled at the rising edge of the SCK clock signal for input, and driven after the falling edge of the SCK clock signal for output. The traditional SPI protocol uses separate input (SI) and output (SO) data signals as shown in Figure 4-1. The SQI protocol uses four multiplexed signals, SIO[3:0], for both data in and data out, as shown in Figure 4-2. This means the SQI protocol quadruples the traditional bus transfer speed at the same clock frequency, without the need for more pins on the package.

H<sub>0</sub> 10

MSB

#### 4.1 **Device Protection**

SIO(3:0)

SST26VF064B/064BA offer a flexible memory protection scheme that allows the protection state of each individual block to be controlled separately. In addition, the Write-Protection Lock-Down register prevents any change of the lock status during device operation. To avoid inadvertent writes during power-up, the device is write-protected by default after a power-on reset cycle. A Global Block-Protection Unlock command offers a single command cycle that unlocks the entire memory array for faster manufacturing throughput.

For extra protection, there is an additional non-volatile register that can permanently write-protect the Block-Protection register bits for each individual block. Each of the corresponding lock-down bits are one time programmable (OTP)-once written, they cannot be erased. Data that had been previously programmed into these blocks cannot be altered by programming or erase and is not reversible

#### 4.1.1 INDIVIDUAL BLOCK PROTECTION

SST26VF064B/064BA have a Block-Protection register which provides a software mechanism to write-lock the individual memory blocks and write-lock, and/or read-lock, the individual parameter blocks. The Block-Protection register is 144 bits wide: two bits each for the eight 8 KByte parameter blocks (write-lock and readlock), and one bit each for the remaining 32 KByte and 64 KByte overlay blocks (write-lock). See Table 5-6 for address range protected per register bit.

Each bit in the Block-Protection register (BPR) can be written to a '1' (protected) or '0' (unprotected). For the parameter blocks, the most significant bit is for readlock, and the least significant bit is for write-lock. Readlocking the parameter blocks provides additional security for sensitive data after retrieval (e.g., after initial boot). If a block is read-locked all reads to the block return data 00H.

25119 F04.0

The Write Block-Protection Register command is a two-cycle command which requires that Write-Enable (WREN) is executed prior to the Write Block-Protection Register command. The Global Block-Protection Unlock command clears all write protection bits in the Block-Protection register.

### 4.1.2 WRITE-PROTECTION LOCK-DOWN (VOLATILE)

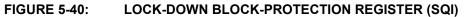

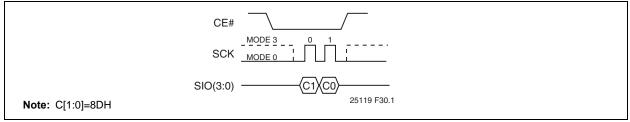

To prevent changes to the Block-Protection register, use the Lock-Down Block-Protection Register (LBPR) command to enable Write-Protection Lock-Down. Once Write-Protection Lock-Down is enabled, the Block-Protection register can not be changed. To avoid inadvertent lock down, the WREN command must be executed prior to the LBPR command.

To reset Write-Protection Lock-Down, performing a power cycle on the device is required. The Write-Protection Lock-Down status may be read from the Status register.

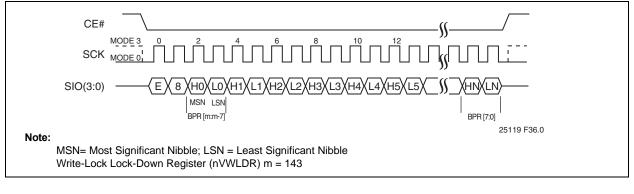

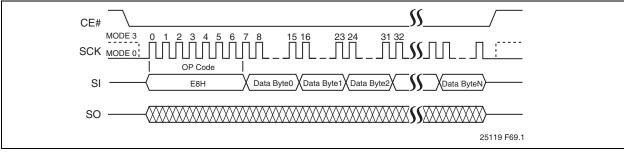

### 4.1.3 WRITE-LOCK LOCK-DOWN (NON-VOLATILE)

The non-Volatile Write-Lock Lock-Down register is an alternate register that permanently prevents changes to the block-protect bits. The non-Volatile Write-Lock Lock-Down register (nVWLDR) is 136 bits wide per device: one bit each for the eight 8-KByte parameter blocks, and one bit each for the remaining 32 KByte and 64 KByte overlay blocks. See Table 5-6 for address range protected per register bit.

Writing '1' to any or all of the nVWLDR bits disables the change mechanism for the corresponding Write-Lock bit in the BPR, and permanently sets this bit to a '1' (protected) state. After this change, both bits will be set to '1', regardless of the data entered in subsequent writes to either the nVWLDR or the BPR. Subsequent writes to the nVWLDR can only alter available locations that have not been previously written to a '1'. This method provides write-protection for the corresponding memory-array block by protecting it from future program or erase operations.

Writing a '0' in any location in the nVWLDR has no effect on either the nVWLDR or the corresponding Write-Lock bit in the BPR.

Note that if the Block-Protection register had been previously locked down, see "Write-Protection Lock-Down (Volatile)", the device must be power cycled before using the nVWLDR. If the Block-Protection register is locked down and the Write nVWLDR command is accessed, the command will be ignored.

### 4.2 Hardware Write Protection

The hardware Write Protection pin (WP#) is used in conjunction with the WPEN and IOC bits in the configuration register to prohibit write operations to the Block-Protection and Configuration registers. The WP# pin function only works in SPI single-bit and dual-bit read mode when the IOC bit in the configuration register is set to '0'.

The WP# pin function is disabled when the WPEN bit in the configuration register is '0'. This allows installation of the SST26VF064B/064BA in a system with a grounded WP# pin while still enabling Write to the Block-Protection register. The Lock-Down function of the Block-Protection Register supersedes the WP# pin, see Table 4-1 for Write Protection Lock-Down states.

The factory default setting at power-up of the WPEN bit is '0', disabling the Write Protect function of the WP# after power-up. WPEN is a non-volatile bit; once the bit is set to '1', the Write Protect function of the WP# pin continues to be enabled after power-up. The WP# pin only protects the Block-Protection Register and Configuration Register from changes. Therefore, if the WP# pin is set to low before or after a Program or Erase command, or while an internal Write is in progress, it will have no effect on the Write command.

The IOC bit takes priority over the WPEN bit in the configuration register. When the IOC bit is '1', the function of the WP# pin is disabled and the WPEN bit serves no function. When the IOC bit is '0' and WPEN is '1', setting the WP# pin active low prohibits Write operations to the Block Protection Register.

|     |                |                | •••• |                          |                               |

|-----|----------------|----------------|------|--------------------------|-------------------------------|

| WP# | IOC            | WPEN           | WPLD | Execute WBPR Instruction | <b>Configuration Register</b> |

| L   | 0              | 1              | 1    | Not Allowed              | Protected                     |

| L   | 0              | 0              | 1    | Not Allowed              | Writable                      |

| L   | 0              | 1              | 0    | Not Allowed              | Protected                     |

| L   | 0 <sup>1</sup> | 0 <sup>2</sup> | 0    | Allowed                  | Writable                      |

| Н   | 0              | Х              | 1    | Not Allowed              | Writable                      |

| Н   | 0              | Х              | 0    | Allowed                  | Writable                      |

| Х   | 1              | Х              | 1    | Not Allowed              | Writable                      |

| Х   | 1 <sup>3</sup> | 0 <sup>2</sup> | 0    | Allowed                  | Writable                      |

TABLE 4-1:WRITE PROTECTION LOCK-DOWN STATES

1. Default at power-up Register settings for SST26VF064B

2. Factory default setting is '0'. This is a non-volatile bit; default at power-up is the value set prior to power-down.

3. Default at power-up Register settings for SST26VF064BA

### 4.3 Security ID

SST26VF064B/064BA offer a 2 KByte Security ID (Sec ID) feature. The Security ID space is divided into two parts – one factory-programmed, 64-bit segment and one user-programmable segment. The factory-programmed segment is programmed during manufacturing with a unique number and cannot be changed. The user-programmable segment is left unprogrammed for the customer to program as desired.

Use the Program Security ID (PSID) command to program the Security ID using the address shown in Table 5-5. The Security ID can be locked using the Lockout Security ID (LSID) command. This prevents any future write operations to the Security ID.

The factory-programmed portion of the Security ID can't be programmed by the user; neither the factory-programmed nor user-programmable areas can be erased.

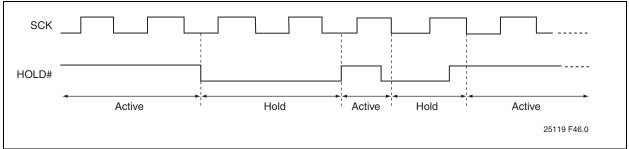

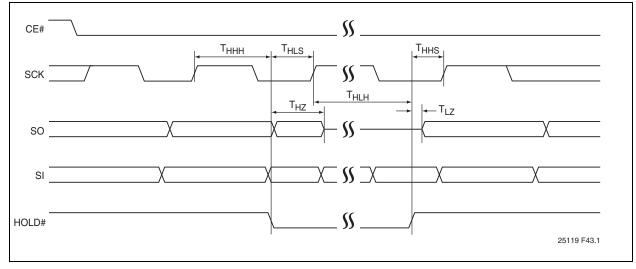

### 4.4 Hold Operation

The HOLD# pin pauses active serial sequences without resetting the clocking sequence. **This pin is active after every power up and only operates during SPI single-bit and dual-bit modes**. Two factory configurations are available: SST26VF064B ships with the IOC bit set to '0' and the HOLD# pin function enabled; SST26VF064BA ships with the IOC bit set to '1' and the HOLD# pin function disabled. The HOLD# pin is always disabled in SQI mode and only works in SPI single-bit and dual-bit read mode.

To activate the Hold mode, CE# must be in active low state. The Hold mode begins when the SCK active low state coincides with the falling edge of the HOLD# signal. The Hold mode ends when the HOLD# signal's rising edge coincides with the SCK active low state.

If the falling edge of the HOLD# signal does not coincide with the SCK active low state, then the device enters Hold mode when the SCK next reaches the active low state. Similarly, if the rising edge of the HOLD# signal does not coincide with the SCK active low state, then the device exits Hold mode when the SCK next reaches the active low state. See Figure 4-3.

Once the device enters Hold mode, SO will be in high impedance state while SI and SCK can be VIL or VIH.

If CE# is driven active high during a Hold condition, it resets the internal logic of the device. As long as HOLD# signal is low, the memory remains in the Hold condition. To resume communication with the device, HOLD# must be driven active high, and CE# must be driven active low.

### FIGURE 4-3: HOLD CONDITION WAVEFORM.

### 4.5 Status Register

The Status register is a read-only register that provides the following status information: whether the flash memory array is available for any Read or Write operation, if the device is write-enabled, whether an erase or program operation is suspended, and if the BlockProtection register and/or Security ID are locked down. During an internal Erase or Program operation, the Status register may be read to determine the completion of an operation in progress. Table 4-2 describes the function of each bit in the Status register.

| Bit | Name             | Function                                                                                                                | Default at<br>Power-up | Read/Write (R/<br>W) |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|

| 0   | BUSY             | Write operation status<br>1 = Internal Write operation is in progress<br>0 = No internal Write operation is in progress | 0                      | R                    |

| 1   | WEL              | Write-Enable Latch status<br>1 = Device is write-enabled<br>0 = Device is not write-enabled                             | 0                      | R                    |

| 2   | WSE              | Write Suspend-Erase status<br>1 = Erase suspended<br>0 = Erase is not suspended                                         | 0                      | R                    |

| 3   | WSP              | Write Suspend-Program status<br>1 = Program suspended<br>0 = Program is not suspended                                   | 0                      | R                    |

| 4   | WPLD             | Write Protection Lock-Down status<br>1 = Write Protection Lock-Down enabled<br>0 = Write Protection Lock-Down disabled  | 0                      | R                    |

| 5   | SEC <sup>1</sup> | Security ID status<br>1 = Security ID space locked<br>0 = Security ID space not locked                                  | 0 <sup>1</sup>         | R                    |

| 6   | RES              | Reserved for future use                                                                                                 | 0                      | R                    |

| 7   | BUSY             | Write operation status<br>1 = Internal Write operation is in progress<br>0 = No internal Write operation is in progress | 0                      | R                    |

### TABLE 4-2: STATUS REGISTER

1. The Security ID status will always be '1' at power-up after a successful execution of the Lockout Security ID instruction, otherwise default at power-up is '0'.

### 4.5.1 WRITE-ENABLE LATCH (WEL)

The Write-Enable Latch (WEL) bit indicates the status of the internal memory's Write-Enable Latch. If the WEL bit is set to '1', the device is write enabled. If the bit is set to '0' (reset), the device is not write enabled and does not accept any memory Program or Erase, Protection Register Write, or Lock-Down commands. The Write-Enable Latch bit is automatically reset under the following conditions:

- Power-up

- Reset

- Write-Disable (WRDI) instruction

- Page-Program instruction completion

- Sector-Erase instruction completion

- Block-Erase instruction completion

- Chip-Erase instruction completion

- Write-Block-Protection register instruction

- Lock-Down Block-Protection register instruction

- Program Security ID instruction completion

- Lockout Security ID instruction completion

- Write-Suspend instruction

- SPI Quad Page program instruction completion

- Write Status Register

# 4.5.2 WRITE SUSPEND ERASE STATUS (WSE)

The Write Suspend-Erase status (WSE) indicates when an Erase operation has been suspended. The WSE bit is '1' after the host issues a suspend command during an Erase operation. Once the suspended Erase resumes, the WSE bit is reset to '0'.

### 4.5.3 WRITE SUSPEND PROGRAM STATUS (WSP)

The Write Suspend-Program status (WSP) bit indicates when a Program operation has been suspended. The WSP is '1' after the host issues a suspend command during the Program operation. Once the suspended Program resumes, the WSP bit is reset to '0'.

### 4.5.4 WRITE PROTECTION LOCK-DOWN STATUS (WPLD)

The Write Protection Lock-Down status (WPLD) bit indicates when the Block-Protection register is lockeddown to prevent changes to the protection settings. The WPLD is '1' after the host issues a Lock-Down Block-Protection command. After a power cycle, the WPLD bit is reset to '0'.

### 4.5.5 SECURITY ID STATUS (SEC)

The Security ID Status (SEC) bit indicates when the Security ID space is locked to prevent a Write command. The SEC is '1' after the host issues a Lockout SID command. Once the host issues a Lockout SID command, the SEC bit can never be reset to '0.'

### 4.5.6 BUSY

The Busy bit determines whether there is an internal Erase or Program operation in progress. If the BUSY bit is '1', the device is busy with an internal Erase or Program operation. If the bit is '0', no Erase or Program operation is in progress.

### 4.5.7 CONFIGURATION REGISTER

The Configuration register is a Read/Write register that stores a variety of configuration information. See Table 4-3 for the function of each bit in the register.

| Bit | Name | Function                                                                                                                          | Default at Power-up | Read/Write (R/W) |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|

| 0   | RES  | Reserved                                                                                                                          | 0                   | R                |

| 1   | IOC  | I/O Configuration for SPI Mode<br>1 = WP# and HOLD# pins disabled<br>0 = WP# and HOLD# pins enabled                               | 0 <sup>1</sup>      | R/W              |

| 2   | RES  | Reserved                                                                                                                          | 0                   | R                |

| 3   | BPNV | Block-Protection Volatility State<br>1 = No memory block has been permanently locked<br>0 = Any block has been permanently locked | 1                   | R                |

| 4   | RES  | Reserved                                                                                                                          | 0                   | R                |

| 5   | RES  | Reserved                                                                                                                          | 0                   | R                |

| 6   | RES  | Reserved                                                                                                                          | 0                   | R                |

| 7   | WPEN | Write-Protection Pin (WP#) Enable<br>1 = WP# enabled<br>0 = WP# disabled                                                          | 0 <sup>2</sup>      | R/W              |

### TABLE 4-3: CONFIGURATION REGISTER

1. SST26VF064B default at Power-up is '0'

SST26VF064BA default at Power-up is '1'

2. Factory default setting. This is a non-volatile bit; default at power-up will be the setting prior to power-down.

### 4.5.8 I/O CONFIGURATION (IOC)

The I/O Configuration (IOC) bit re-configures the I/O pins. The IOC bit is set by writing a '1' to Bit 1 of the Configuration register. When IOC bit is '0' the WP# pin and HOLD# pin are enabled (SPI or Dual Configuration setup). When IOC bit is set to '1' the SIO2 pin and SIO3 pin are enabled (SPI Quad I/O Configuration setup). The IOC bit must be set to '1' before issuing the following SPI commands: SQOR (6BH), SQIOR (EBH), RBSPI (ECH), and SPI Quad page program (32H). Without setting the IOC bit to '1', those SPI commands are not valid. The I/O configuration bit does not apply when in SQI mode. The default at power-up for SST26VF064B is '0' and for SST26VF064BA is '1'.

### 4.5.9 BLOCK-PROTECTION VOLATILITY STATE (BPNV)

The Block-Protection Volatility State bit indicates whether any block has been permanently locked with the nVWLDR. When no bits in the nVWLDR have been set, the BPNV is '1'; this is the default state from the factory. When one or more bits in the nVWLDR are set to '1', the BPNV bit will also be '0' from that point forward, even after power-up.

### 4.5.10 WRITE-PROTECT ENABLE (WPEN)

The Write-Protect Enable (WPEN) bit is a non-volatile bit that enables the WP# pin.

The Write-Protect (WP#) pin and the Write-Protect Enable (WPEN) bit control the programmable hardware write-protect feature. Setting the WP# pin to low, and the WPEN bit to '1', enables Hardware write-protection. To disable Hardware write protection, set either the WP# pin to high or the WPEN bit to '0'. There is latency associated with writing to the WPEN bit. Poll the BUSY bit in the Status register, or wait T<sub>WPEN</sub>, for the completion of the internal, self-timed Write operation. When the chip is hardware write protected, only Write operations to Block-Protection and Configuration registers are disabled. See "Hardware Write Protection" on page 8 and Table 4-1 on page 9 for more information about the functionality of the WPEN bit.

### 5.0 INSTRUCTIONS

Instructions are used to read, write (erase and program), and configure the SST26VF064B/064BA. The complete list of the instructions is provided in Table 5-1.

|                             |                                             | Command            | Mo  | ode | Address                  | Dummy                 | Data                  | Max                |

|-----------------------------|---------------------------------------------|--------------------|-----|-----|--------------------------|-----------------------|-----------------------|--------------------|

| Instruction                 | Description                                 | Cycle <sup>1</sup> | SPI | SQI | Cycle(s) <sup>2, 3</sup> | Cycle(s) <sup>3</sup> | Cycle(s) <sup>3</sup> | Freq <sup>4</sup>  |

| Configurat                  | tion                                        | •                  |     | •   | •                        | •                     | · ·                   |                    |

| NOP                         | No Operation                                | 00H                | Х   | Х   | 0                        | 0                     | 0                     |                    |

| RSTEN                       | Reset Enable                                | 66H                | Х   | Х   | 0                        | 0                     | 0                     |                    |

| RST <sup>5</sup>            | Reset Memory                                | 99H                | Х   | Х   | 0                        | 0                     | 0                     |                    |

| EQIO                        | Enable Quad I/O                             | 38H                | Х   |     | 0                        | 0                     | 0                     |                    |

| RSTQIO <sup>6</sup>         | Reset Quad I/O                              | FFH                | Х   | Х   | 0                        | 0                     | 0                     | 104 MHz/           |

| RDSR                        | Read Status Register                        | 05H                | Х   |     | 0                        | 0                     | 1 to ∞                | 80 MHz             |

|                             |                                             |                    |     | Х   | 0                        | 1                     | 1 to ∞                |                    |

| WRSR                        | Write Status Register                       | 01H                | Х   | Х   | 0                        | 0                     | 2                     |                    |

| RDCR                        | Read Configuration                          | 35H                | Х   |     | 0                        | 0                     | 1 to ∞                |                    |

|                             | Register                                    |                    |     | Х   | 0                        | 1                     | 1 to ∞                |                    |

| Read                        |                                             |                    |     |     |                          |                       |                       |                    |

| Read                        | Read Memory                                 | 03H                | Х   |     | 3                        | 0                     | 1 to ∞                | 40 MHz             |

| High-                       | Read Memory at Higher                       | 0BH                |     | Х   | 3                        | 3                     | 1 to ∞                |                    |

| Speed<br>Read               | Speed                                       |                    | Х   |     | 3                        | 1                     | 1 to ∞                |                    |

| SQOR <sup>7</sup>           | SPI Quad Output Read                        | 6BH                | Х   |     | 3                        | 1                     | 1 to ∞                |                    |

| SQIOR <sup>8</sup>          | SPI Quad I/O Read                           | EBH                | Х   |     | 3                        | 3                     | 1 to ∞                | 104 MHz/           |

| SDOR <sup>9</sup>           | SPI Dual Output Read                        | 3BH                | Х   |     | 3                        | 1                     | 1 to ∞                | 80 MHz             |

| SDIOR <sup>10</sup>         | SPI Dual I/O Read                           | BBH                | Х   |     | 3                        | 1                     | 1 to ∞                |                    |

| SB                          | Set Burst Length                            | COH                | Х   | Х   | 0                        | 0                     | 1                     |                    |

| RBSQI                       | SQI Read Burst with Wrap                    | 0CH                |     | Х   | 3                        | 3                     | n to ∞                |                    |

| RBSPI <sup>8</sup>          | SPI Read Burst with Wrap                    | ECH                | Х   |     | 3                        | 3                     | n to ∞                |                    |

| Identificati                | on                                          |                    |     |     |                          |                       |                       |                    |

| JEDEC-ID                    | JEDEC-ID Read                               | 9FH                | Х   |     | 0                        | 0                     | 3 to ∞                |                    |

| Quad J-ID                   | Quad I/O J-ID Read                          | AFH                |     | Х   | 0                        | 1                     | 3 to ∞                | 104 MHz/           |

| SFDP                        | Serial Flash Discoverable<br>Parameters     | 5AH                | х   |     | 3                        | 1                     | 1 to ∞                | 80 MHz             |

| Write                       |                                             |                    |     |     |                          |                       |                       |                    |

| WREN                        | Write Enable                                | 06H                | Х   | Х   | 0                        | 0                     | 0                     |                    |

| WRDI                        | Write Disable                               | 04H                | Х   | Х   | 0                        | 0                     | 0                     |                    |

| SE <sup>11</sup>            | Erase 4 KBytes of Memory<br>Array           | 20H                | Х   | Х   | 3                        | 0                     | 0                     |                    |

| BE <sup>12</sup>            | Erase 64, 32 or 8 KBytes of<br>Memory Array | D8H                | Х   | Х   | 3                        | 0                     | 0                     | 104 MHz/<br>80 MHz |

| CE                          | Erase Full Array                            | C7H                | Х   | Х   | 0                        | 0                     | 0                     |                    |

| PP                          | Page Program                                | 02H                | Х   | Х   | 3                        | 0                     | 1 to 256              |                    |

| SPI Quad<br>PP <sup>7</sup> | SQI Quad Page<br>Program                    | 32H                | Х   |     | 3                        | 0                     | 1 to 256              |                    |

### TABLE 5-1: DEVICE OPERATION INSTRUCTIONS FOR SST26VF064B/064BA

|             |                                           | Command            | Mode |     | Address                  | Dummy                 | Data                  | Мах               |

|-------------|-------------------------------------------|--------------------|------|-----|--------------------------|-----------------------|-----------------------|-------------------|

| Instruction | Description                               | Cycle <sup>1</sup> | SPI  | SQI | Cycle(s) <sup>2, 3</sup> | Cycle(s) <sup>3</sup> | Cycle(s) <sup>3</sup> | Freq <sup>4</sup> |

| WRSU        | Suspends Program/Erase                    | B0H                | Х    | Х   | 0                        | 0                     | 0                     | 104 MHz/          |

| WRRE        | Resumes Program/Erase                     | 30H                | Х    | Х   | 0                        | 0                     | 0                     | 80 MHz            |

| Protection  | l                                         |                    |      |     |                          |                       |                       |                   |

| RBPR        | Read Block-Protection                     | 72H                | Х    |     | 0                        | 0                     | 1 to 18               |                   |

|             | Register                                  |                    |      | Х   | 0                        | 1                     | 1 to 18               |                   |

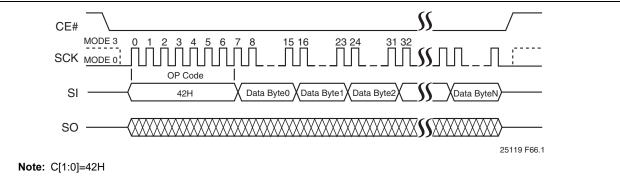

| WBPR        | Write Block-Protection<br>Register        | 42H                | Х    | Х   | 0                        | 0                     | 1 to 18               |                   |

| LBPR        | Lock Down<br>Block-Protection<br>Register | 8DH                | х    | х   | 0                        | 0                     | 0                     |                   |

| nVWLDR      | non-Volatile Write Lock-<br>Down Register | E8H                | Х    | Х   | 0                        | 0                     | 1 to 18               | 104 MHz/          |

| ULBPR       | Global Block Protection<br>Unlock         | 98H                | Х    | Х   | 0                        | 0                     | 0                     | 80 MHz            |

| RSID        | Read Security ID                          | 88H                | Х    |     | 2                        | 1                     | 1 to 2048             |                   |

|             |                                           |                    |      | Х   | 2                        | 3                     | 1 to 2048             |                   |

| PSID        | Program User<br>Security ID area          | A5H                | Х    | Х   | 2                        | 0                     | 1 to 256              | ]                 |

| LSID        | Lockout Security ID Pro-<br>gramming      | 85H                | х    | х   | 0                        | 0                     | 0                     |                   |

### TABLE 5-1: DEVICE OPERATION INSTRUCTIONS FOR SST26VF064B/064BA

1. Command cycle is two clock periods in SQI mode and eight clock periods in SPI mode.

2. Address bits above the most significant bit of each density can be  $\rm V_{IL}$  or  $\rm V_{IH.}$

3. Address, Dummy/Mode bits, and Data cycles are two clock periods in SQI and eight clock periods in SPI mode.

4. The max frequency for all instructions is up to 104 MHz from 2.7-3.6V and up to 80 MHz from 2.3-3.6V unless otherwise noted.

5. RST command only executed if RSTEN command is executed first. Any intervening command will disable Reset.

6. Device accepts eight-clock command in SPI mode, or two-clock command in SQI mode.

7. Data cycles are two clock periods. IOC bit must be set to '1' before issuing the command.

8. Address, Dummy/Mode bits, and data cycles are two clock periods. IOC bit must be set to '1' before issuing the command.

9. Data cycles are four clock periods.

10. Address, Dummy/Mode bits, and Data cycles are four clock periods.

11. Sector Addresses: Use A<sub>MS</sub> - A<sub>12</sub>, remaining address are don't care, but must be set to V<sub>IL</sub> or V<sub>IH</sub>.

12. Blocks are 64 KByte, 32 KByte, or 8KByte, depending on location. Block Erase Address: A<sub>MS</sub> - A<sub>16</sub> for 64 KByte; A<sub>MS</sub> - A<sub>15</sub> for 32 KByte; A<sub>MS</sub> - A<sub>13</sub> for 8 KByte. Remaining addresses are don't care, but must be set to V<sub>IL</sub> or V<sub>IH</sub>.

### 5.1 No Operation (NOP)

The No Operation command only cancels a Reset Enable command. NOP has no impact on any other command.

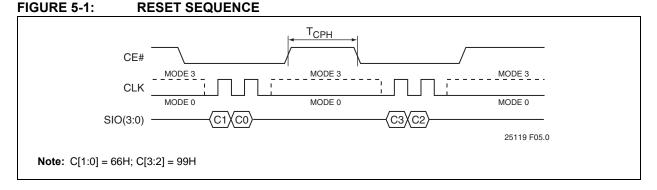

# 5.2 Reset-Enable (RSTEN) and Reset (RST)

The Reset operation is used as a system (software) reset that puts the device in normal operating Ready mode. This operation consists of two commands: Reset-Enable (RSTEN) followed by Reset (RST).

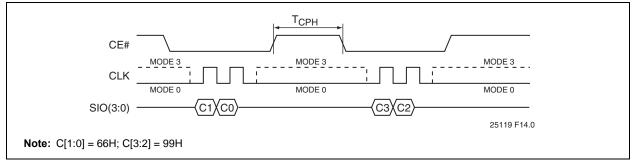

To reset the SST26VF064B/064BA, the host drives CE# low, sends the Reset-Enable command (66H), and drives CE# high. Next, the host drives CE# low again, sends the Reset command (99H), and drives CE# high, see Figure 5-1.

The Reset operation requires the Reset-Enable command followed by the Reset command. Any command other than the Reset command after the Reset-Enable command will disable the Reset-Enable.

Once the Reset-Enable and Reset commands are successfully executed, the device returns to normal operation Read mode and then does the following: resets the protocol to SPI mode, resets the burst length to 8 Bytes, clears all the bits, except for bit 4 (WPLD) and bit 5 (SEC), in the Status register to their default states, and clears bit 1 (IOC) in the configuration register to its default state. A device reset during an active Program or Erase operation aborts the operation, which can cause the data of the targeted address range to be corrupted or lost. Depending on the prior operation, the reset timing may vary. Recovery from a Write operation requires more latency time than recovery from other operations. See Table 8-2 on page 49 for Rest timing parameters.

### 5.3 Read (40 MHz)

The Read instruction, 03H, is supported in SPI bus protocol only with clock frequencies up to 40 MHz. This command is not supported in SQI bus protocol. The device outputs the data starting from the specified address location, then continuously streams the data output through all addresses until terminated by a lowto-high transition on CE#. The internal address pointer will automatically increment until the highest memory address is reached. Once the highest memory address is reached, the address pointer will automatically return to the beginning (wrap-around) of the address space.

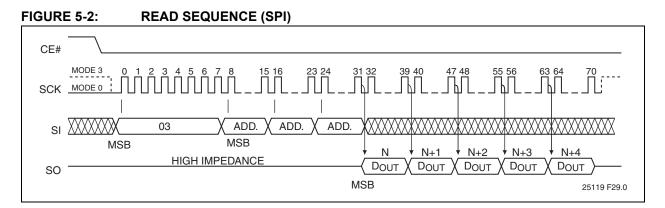

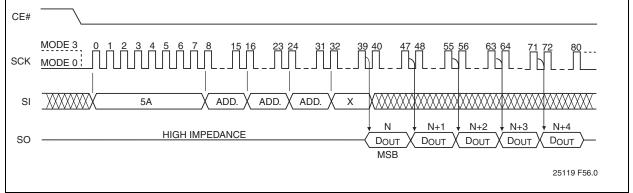

Initiate the Read instruction by executing an 8-bit command, 03H, followed by address bits A[23:0]. CE# must remain active low for the duration of the Read cycle. See Figure 5-2 for Read Sequence.

### © 2015 Microchip Technology Inc.

### 5.4 Enable Quad I/O (EQIO)

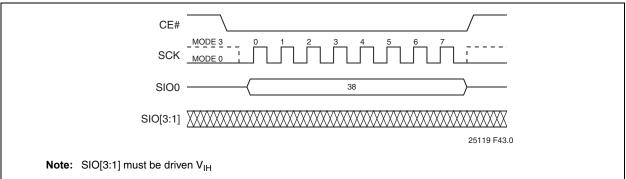

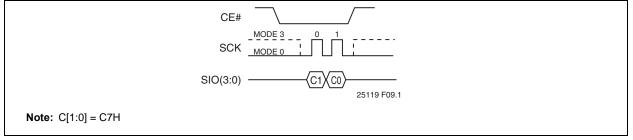

The Enable Quad I/O (EQIO) instruction, 38H, enables the flash device for SQI bus operation. Upon completion of the instruction, all instructions thereafter are expected to be 4-bit multiplexed input/output (SQI mode) until a power cycle or a "Reset Quad I/O instruction" is executed. See Figure 5-3.

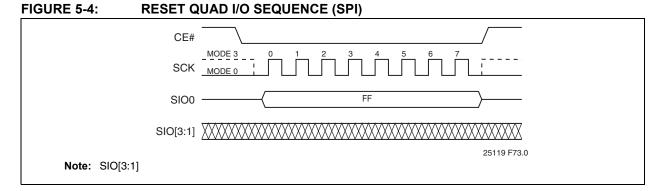

### 5.5 Reset Quad I/O (RSTQIO)

The Reset Quad I/O instruction, FFH, resets the device to 1-bit SPI protocol operation or exits the Set Mode configuration during a read sequence. This command allows the flash device to return to the default I/O state (SPI) without a power cycle, and executes in either 1bit or 4-bit mode. If the device is in the Set Mode configuration, while in SQI High-Speed Read mode, the RSTQIO command will only return the device to a state where it can accept new command instruction. An additional RSTQIO is required to reset the device to SPI mode.

To execute a Reset Quad I/O operation, the host drives CE# low, sends the Reset Quad I/O command cycle (FFH) then, drives CE# high. Execute the instruction in either SPI (8 clocks) or SQI (2 clocks) command cycles. For SPI, SIO[3:1] are don't care for this command, but should be driven to  $V_{IH}$  or  $V_{IL}$ . See Figures 5-4 and 5-5.

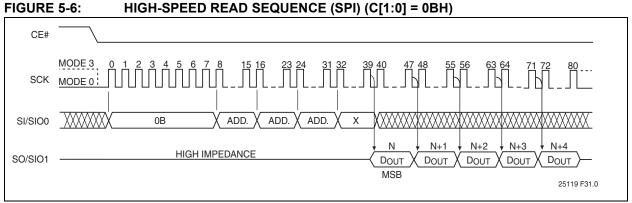

#### 5.6 **High-Speed Read**

The High-Speed Read instruction, 0BH, is supported in both SPI bus protocol and SQI protocol. This instruction supports frequencies of up to 104 MHz from 2.7-3.6V and up to 80 MHz from 2.3-3.6V.On power-up, the device is set to use SPI.

Initiate High-Speed Read by executing an 8-bit command, 0BH, followed by address bits A[23-0] and a dummy byte. CE# must remain active low for the duration of the High-Speed Read cycle. See Figure 5-6 for the High-Speed Read sequence for SPI bus protocol.

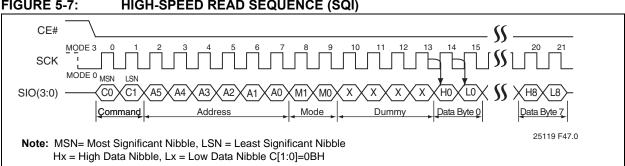

In SQI protocol, the host drives CE# low then send the Read command cycle command, 0BH, followed by three address cycles, a Set Mode Configuration cycle, and two dummy cycles. Each cycle is two nibbles (clocks) long, most significant nibble first.

After the dummy cycles, the device outputs data on the falling edge of the SCK signal starting from the specified address location. The device continually streams data output through all addresses until terminated by a low-to-high transition on CE#. The internal address pointer automatically increments until the highest memory address is reached, at which point the address pointer returns to address location 000000H. During this operation, blocks that are Read-locked will output data 00H.

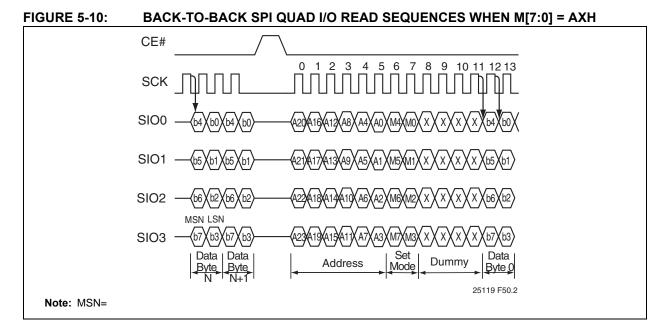

The Set Mode Configuration bit M[7:0] indicates if the next instruction cycle is another SQI High-Speed Read command. When M[7:0] = AXH, the device expects the next continuous instruction to be another Read command, 0BH, and does not require the op-code to be entered again. The host may initiate the next Read cycle by driving CE# low, then sending the four-bits input for address A[23:0], followed by the Set Mode configuration bits M[7:0], and two dummy cycles. After the two dummy cycles, the device outputs the data starting from the specified address location. There are no restrictions on address location access.

When M[7:0] is any value other than AXH, the device expects the next instruction initiated to be a command instruction. To reset/exit the Set Mode configuration, execute the Reset Quad I/O command, FFH. While in the Set Mode configuration, the RSTQIO command will only return the device to a state where it can accept new command instruction. An additional RSTQIO is required to reset the device to SPI mode. See Figure 5-10 for the SPI Quad I/O Mode Read sequence when M[7:0] = AXH.

#### FIGURE 5-7: **HIGH-SPEED READ SEQUENCE (SQI)**

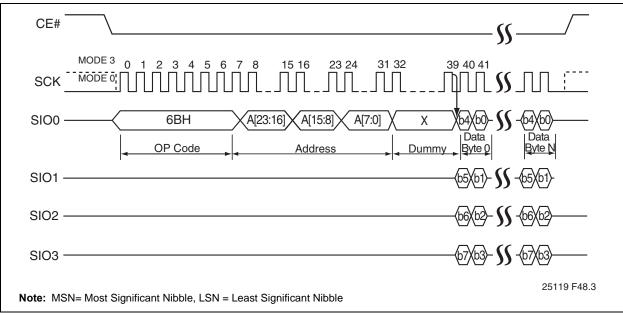

### 5.7 SPI Quad-Output Read

The SPI Quad-Output Read instruction supports frequencies of up to 104 MHz from 2.7-3.6V and up to 80 MHz from 2.3-3.6V. SST26VF064B requires the IOC bit in the configuration register to be set to '1' prior to executing the command. Initiate SPI Quad-Output Read by executing an 8-bit command, 6BH, followed by address bits A[23-0] and a dummy byte. CE# must remain active low for the duration of the SPI Quad Mode Read. See Figure 5-8 for the SPI Quad Output Read sequence. Following the dummy byte, the device outputs data from SIO[3:0] starting from the specified address location. The device continually streams data output through all addresses until terminated by a low-to-high transition on CE#. The internal address pointer automatically increments until the highest memory address is reached, at which point the address pointer returns to the beginning of the address space.

### FIGURE 5-8: SPI QUAD OUTPUT READ

### 5.8 SPI Quad I/O Read

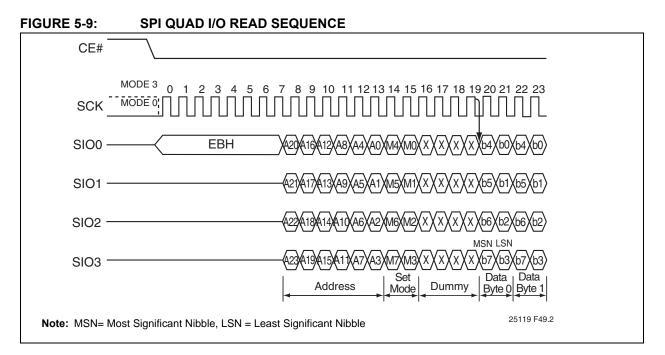

The SPI Quad I/O Read (SQIOR) instruction supports frequencies of up to 104 MHz from 2.7-3.6V and up to 80 MHz from 2.3-3.6V. SST26VF064B requires the IOC bit in the configuration register to be set to '1' prior to executing the command. Initiate SQIOR by executing an 8-bit command, EBH. The device then switches to 4-bit I/O mode for address bits A[23-0], followed by the Set Mode configuration bits M[7:0], and two dummy bytes.CE# must remain active low for the duration of the SPI Quad I/O Read. See Figure 5-9 for the SPI Quad I/O Read sequence.

Following the dummy bytes, the device outputs data from the specified address location. The device continually streams data output through all addresses until terminated by a low-to-high transition on CE#. The internal address pointer automatically increments until the highest memory address is reached, at which point the address pointer returns to the beginning of the address space. The Set Mode Configuration bit M[7:0] indicates if the next instruction cycle is another SPI Quad I/O Read command. When M[7:0] = AXH, the device expects the next continuous instruction to be another Read command, EBH, and does not require the op-code to be entered again. The host may set the next SQIOR cycle by driving CE# low, then sending the four-bit wide input for address A[23:0], followed by the Set Mode configuration bits M[7:0], and two dummy cycles. After the two dummy cycles, the device outputs the data starting from the specified address location. There are no restrictions on address location access.

When M[7:0] is any value other than AXH, the device expects the next instruction initiated to be a command instruction. To reset/exit the Set Mode configuration, execute the Reset Quad I/O command, FFH. See Figure 5-10 for the SPI Quad I/O Mode Read sequence when M[7:0] = AXH.

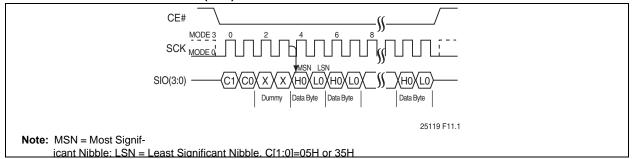

### 5.9 Set Burst

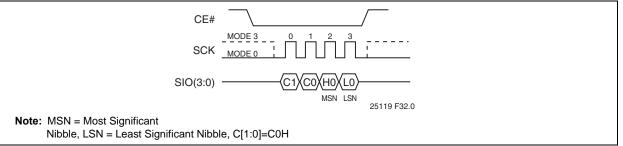

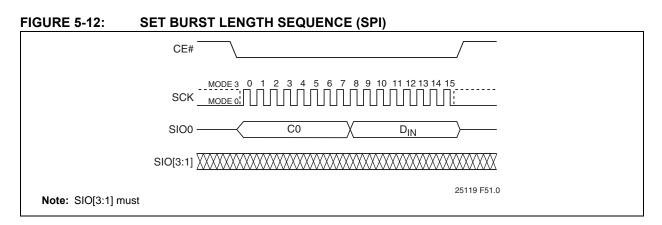

The Set Burst command specifies the number of bytes to be output during a Read Burst command before the device wraps around. It supports both SPI and SQI protocols. To set the burst length the host drives CE# low,

### TABLE 5-2: BURST LENGTH DATA

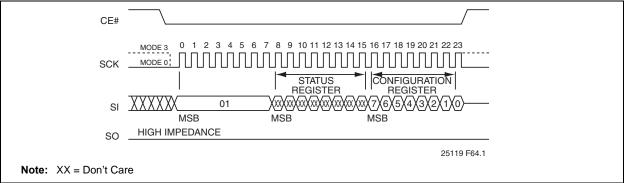

sends the Set Burst command cycle (C0H) and one data cycle, then drives CE# high. After power-up or reset, the burst length is set to eight Bytes (00H). See Table 5-2 for burst length data and Figures 5-11 and 5-12 for the sequences.

| Burst Length | High Nibble (H0) | Low Nibble (L0) |

|--------------|------------------|-----------------|

| 8 Bytes      | Oh               | Oh              |

| 16 Bytes     | Oh               | 1h              |

| 32 Bytes     | Oh               | 2h              |

| 64 Bytes     | Oh               | 3h              |

### FIGURE 5-11: SET BURST LENGTH SEQUENCE (SQI)

### 5.10 SQI Read Burst with Wrap (RBSQI)

SQI Read Burst with wrap is similar to High Speed Read in SQI mode, except data will output continuously within the burst length until a low-to-high transition on CE#. To execute a SQI Read Burst operation, drive CE# low then send the Read Burst command cycle (0CH), followed by three address cycles, and then three dummy cycles. Each cycle is two nibbles (clocks) long, most significant nibble first.

After the dummy cycles, the device outputs data on the falling edge of the SCK signal starting from the specified address location. The data output stream is continuous through all addresses until terminated by a low-to-high transition on CE#.

During RBSQI, the internal address pointer automatically increments until the last byte of the burst is reached, then it wraps around to the first byte of the burst. All bursts are aligned to addresses within the burst length, see Table 5-3. For example, if the burst length is eight Bytes, and the start address is 06h, the burst sequence would be: 06h, 07h, 00h, 01h, 02h, 03h, 04h, 05h, 06h, etc. The pattern repeats until the command is terminated by a low-to-high transition on CE#.

During this operation, blocks that are Read-locked will output data 00H.

### 5.11 SPI Read Burst with Wrap (RBSPI)

SPI Read Burst with Wrap (RBSPI) is similar to SPI Quad I/O Read except the data will output continuously within the burst length until a low-to-high transition on CE#. To execute a SPI Read Burst with Wrap operation, drive CE# low, then send the Read Burst command cycle (ECH), followed by three address cycles, and then three dummy cycles.

After the dummy cycle, the device outputs data on the falling edge of the SCK signal starting from the specified address location. The data output stream is continuous through all addresses until terminated by a low-to-high transition on CE#.

During RBSPI, the internal address pointer automatically increments until the last byte of the burst is reached, then it wraps around to the first byte of the burst. All bursts are aligned to addresses within the burst length, see Table 5-3. For example, if the burst length is eight Bytes, and the start address is 06h, the burst sequence would be: 06h, 07h, 00h, 01h, 02h, 03h, 04h, 05h, 06h, etc. The pattern repeats until the command is terminated by a low-to-high transition on CE#.

During this operation, blocks that are Read-locked will output data 00H.

| Burst Length | Burst Address Ranges           |

|--------------|--------------------------------|

| 8 Bytes      | 00-07H, 08-0FH, 10-17H, 18-1FH |

| 16 Bytes     | 00-0FH, 10-1FH, 20-2FH, 30-3FH |

| 32 Bytes     | 00-1FH, 20-3FH, 40-5FH, 60-7FH |

| 64 Bytes     | 00-3FH, 40-7FH, 80-BFH, C0-FFH |

| TABLE 5-3: | BURST ADDRESS RANGES |

|------------|----------------------|

|------------|----------------------|

0

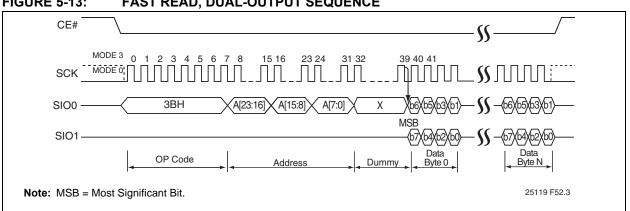

#### 5.12 SPI Dual-Output Read

The SPI Dual-Output Read instruction supports frequencies of up to 104 MHz from 2.7-3.6V and up to 80 MHz from 2.3-3.6V. Initiate SPI Dual-Output Read by executing an 8-bit command, 3BH, followed by address bits A[23-0] and a dummy byte. CE# must remain active low for the duration of the SPI Dual-Output Read operation. See Figure 5-13 for the SPI Quad Output Read sequence.

Following the dummy byte, the SST26VF064B/064BA outputs data from SIO[1:0] starting from the specified address location. The device continually streams data output through all addresses until terminated by a lowto-high transition on CE#. The internal address pointer automatically increments until the highest memory address is reached, at which point the address pointer returns to the beginning of the address space.

#### **FIGURE 5-13:** FAST READ, DUAL-OUTPUT SEQUENCE

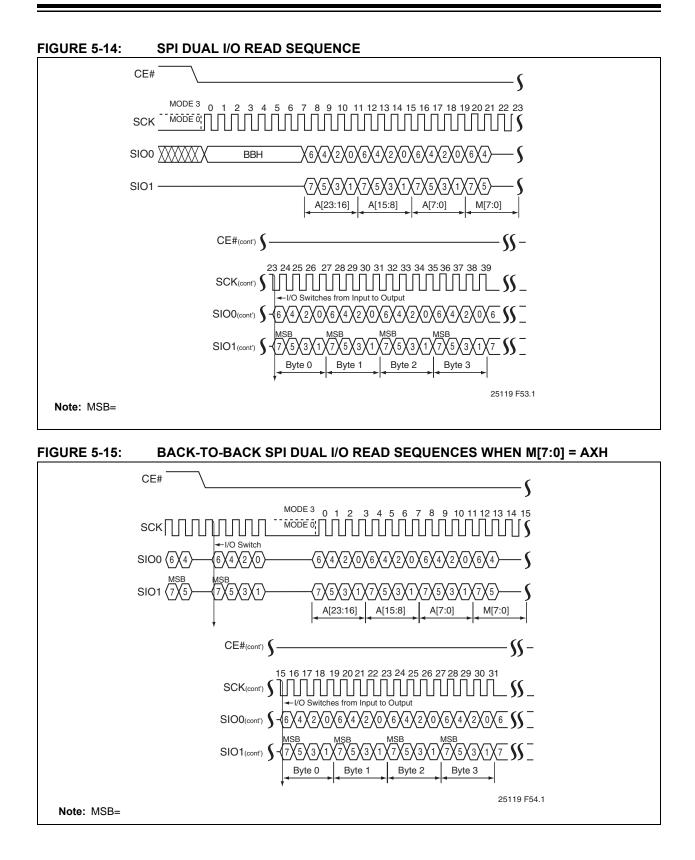

#### 5.13 SPI Dual I/O Read

The SPI Dual I/O Read (SDIOR) instruction supports up to 80 MHz frequency. Initiate SDIOR by executing an 8-bit command, BBH. The device then switches to 2-bit I/O mode for address bits A[23-0], followed by the Set Mode configuration bits M[7:0]. CE# must remain active low for the duration of the SPI Dual I/O Read. See Figure 5-14 for the SPI Dual I/O Read sequence.

Following the Set Mode configuration bits, the SST26VF064B/064BA outputs data from the specified address location. The device continually streams data output through all addresses until terminated by a lowto-high transition on CE#. The internal address pointer automatically increments until the highest memory address is reached, at which point the address pointer returns to the beginning of the address space.

The Set Mode Configuration bit M[7:0] indicates if the next instruction cycle is another SPI Dual I/O Read command. When M[7:0] = AXH, the device expects the next continuous instruction to be another SDIOR command, BBH, and does not require the op-code to be entered again. The host may set the next SDIOR cycle by driving CE# low, then sending the two-bit wide input for address A[23:0], followed by the Set Mode configuration bits M[7:0]. After the Set Mode configuration bits, the device outputs the data starting from the specified address location. There are no restrictions on address location access.

When M[7:0] is any value other than AXH, the device expects the next instruction initiated to be a command instruction. To reset/exit the Set Mode configuration, execute the Reset Quad I/O command, FFH. See Figure 5-15 for the SPI Dual I/O Read sequence when M[7:0] = AXH.

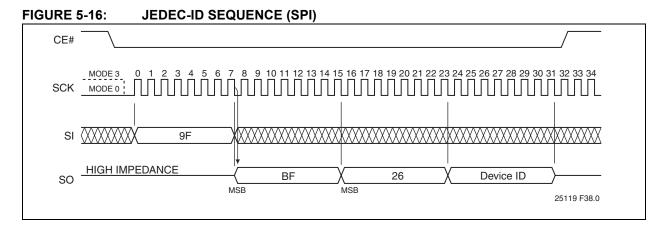

### 5.14 JEDEC-ID Read (SPI Protocol)

Using traditional SPI protocol, the JEDEC-ID Read instruction identifies the device as SST26VF064B/ 064BA and the manufacturer as Microchip®. To execute a JECEC-ID operation the host drives CE# low then sends the JEDEC-ID command cycle (9FH).

Immediately following the command cycle, SST26VF064B/064BA output data on the falling edge of the SCK signal. The data output stream is continuous until terminated by a low-to-high transition on CE#. The device outputs three bytes of data: manufacturer, device type, and device ID, see Table 5-4. See Figure 5-16 for instruction sequence.

|    |                 |                          | Devie                | ce ID              |

|----|-----------------|--------------------------|----------------------|--------------------|

|    | Product         | Manufacturer ID (Byte 1) | Device Type (Byte 2) | Device ID (Byte 3) |

| SS | T26VF064B/064BA | BFH                      | 26H                  | 43H                |

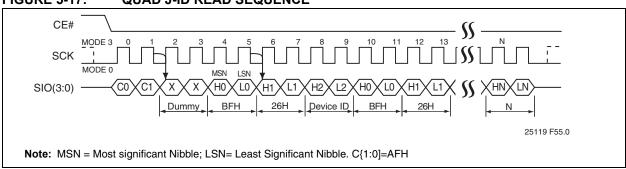

### 5.15 Read Quad J-ID Read (SQI Protocol)

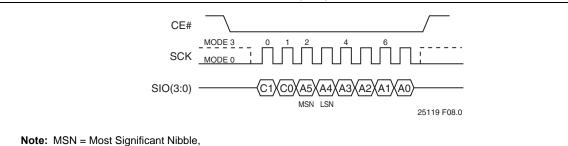

The Read Quad J-ID Read instruction identifies the device as SST26VF064B/064BA and manufacturer as Microchip. To execute a Quad J-ID operation the host drives CE# low and then sends the Quad J-ID command cycle (AFH). Each cycle is two nibbles (clocks) long, most significant nibble first.

Immediately following the command cycle and one dummy cycle, SST26VF064B/064BA output data on the falling edge of the SCK signal. The data output stream is continuous until terminated by a low-to-high transition of CE#. The device outputs three bytes of data: manufacturer, device type, and device ID, see Table 5-4. See Figure 5-17 for instruction sequence.

### 5.16 Serial Flash Discoverable Parameters (SFDP)

The Serial Flash Discoverable Parameters (SFDP) contain information describing the characteristics of the device. This allows device-independent, JEDEC ID-independent, and forward/backward compatible soft-

ware support for all future Serial Flash device families. See Table 11-1 on page 66 for address and data values.

Initiate SFDP by executing an 8-bit command, 5AH, followed by address bits A[23-0] and a dummy byte. CE# must remain active low for the duration of the SFDP cycle. For the SFDP sequence, see Figure 5-18.

### 5.17 Sector-Erase

The Sector-Erase instruction clears all bits in the selected 4 KByte sector to '1,' but it does not change a protected memory area. Prior to any write operation, the Write-Enable (WREN) instruction must be executed.

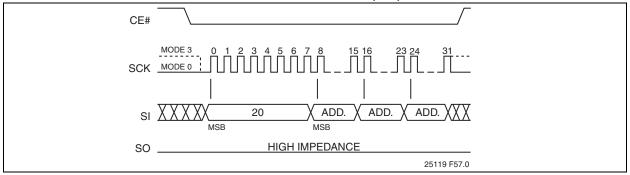

To execute a Sector-Erase operation, the host drives CE# low, then sends the Sector Erase command cycle (20H) and three address cycles, and then drives CE# high. Address bits  $[A_{MS}:A_{12}]$  ( $A_{MS}$  = Most Significant Address) determine the sector address (SA<sub>X</sub>); the remaining address bits can be V<sub>IL</sub> or V<sub>IH</sub>. To identify the completion of the internal, self-timed, Write operation, poll the BUSY bit in the Status register, or wait T<sub>SE</sub>. See Figures 5-19 and 5-20 for the Sector-Erase sequence.

### FIGURE 5-19: 4 KBYTE SECTOR-ERASE SEQUENCE– SQI MODE

### FIGURE 5-20: 4 KBYTE SECTOR-ERASE SEQUENCE (SPI)

### 5.18 Block-Erase

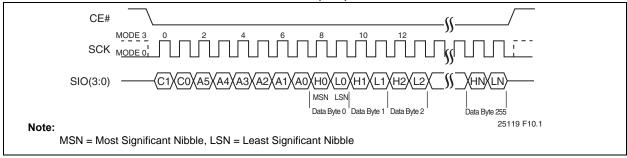

FIGURE 5-21:

The Block-Erase instruction clears all bits in the selected block to '1'. Block sizes can be 8 KByte, 32 KByte or 64 KByte depending on address, see Figure 3-1, Memory Map, for details. A Block-Erase instruction applied to a protected memory area will be ignored. Prior to any write operation, execute the WREN instruction. Keep CE# active low for the duration of any command sequence.

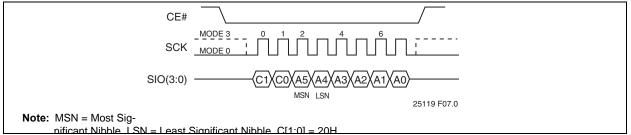

To execute a Block-Erase operation, the host drives CE# low then sends the Block-Erase command cycle (D8H), three address cycles, then drives CE# high. Address bits  $A_{MS}$ - $A_{13}$  determine the block address (BA<sub>X</sub>); the remaining address bits can be  $V_{IL}$  or  $V_{IH}$ . For 32 KByte blocks,  $A_{14}$ : $A_{13}$  can be  $V_{IL}$  or  $V_{IH}$ ; for 64 KByte blocks,  $A_{15}$ : $A_{13}$  can be  $V_{IL}$  or  $V_{IH}$ . Poll the BUSY bit in the Status register, or wait  $T_{BE}$ , for the completion of the internal, self-timed, Block-Erase operation. See Figures 5-21 and 5-22 for the Block-Erase sequence.

**BLOCK-ERASE SEQUENCE (SQI)**

Note: MSN = Most Significant Nibble, LSN = Least Significant Nibble C[1:0] = D8H

### FIGURE 5-22: BLOCK-ERASE SEQUENCE (SPI)

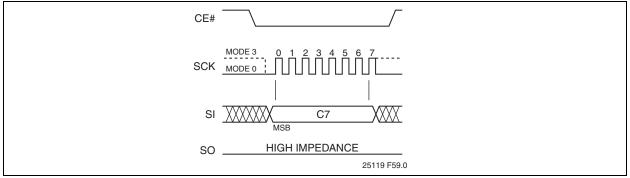

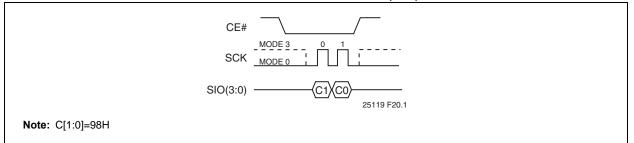

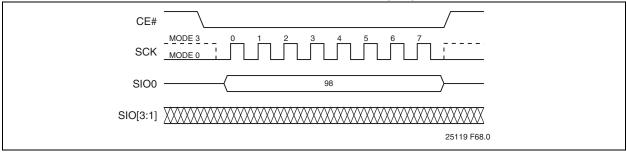

### 5.19 Chip-Erase

The Chip-Erase instruction clears all bits in the device to '1.' The Chip-Erase instruction is ignored if any of the memory area is protected. Prior to any write operation, execute the WREN instruction. To execute a Chip-Erase operation, the host drives CE# low, sends the Chip-Erase command cycle (C7H), then drives CE# high. Poll the BUSY bit in the Status register, or wait  $T_{SCE}$ , for the completion of the internal, self-timed, Write operation. See Figures 5-23 and 5-24 for the Chip Erase sequence.

### FIGURE 5-24: CHIP-ERASE SEQUENCE (SPI)

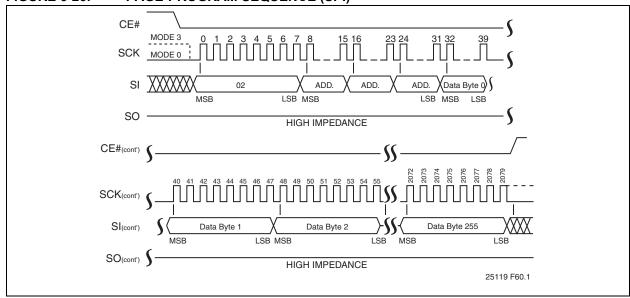

### 5.20 Page-Program

The Page-Program instruction programs up to 256 Bytes of data in the memory, and supports both SPI and SQI protocols. The data for the selected page address must be in the erased state (FFH) before initiating the Page-Program operation. A Page-Program applied to a protected memory area will be ignored. Prior to the program operation, execute the WREN instruction.

To execute a Page-Program operation, the host drives CE# low then sends the Page Program command cycle (02H), three address cycles followed by the data to be programmed, then drives CE# high. The programmed data must be between 1 to 256 Bytes and in whole Byte increments; sending less than a full Byte will cause the

partial Byte to be ignored. Poll the BUSY bit in the Status register, or wait  $T_{PP}$  for the completion of the internal, self-timed, Write operation. See Figures 5-25 and 5-26 for the Page-Program sequence.

When executing Page-Program, the memory range for the SST26VF064B/064BA is divided into 256 Byte page boundaries. The device handles shifting of more than 256 Bytes of data by maintaining the last 256 Bytes of data as the correct data to be programmed. If the target address for the Page-Program instruction is not the beginning of the page boundary (A[7:0] are not all zero), and the number of bytes of data input exceeds or overlaps the end of the address of the page boundary, the excess data inputs wrap around and will be programmed at the start of that target page.

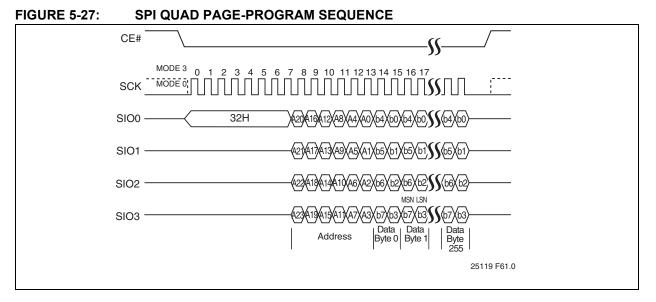

### 5.21 SPI Quad Page-Program

The SPI Quad Page-Program instruction programs up to 256 Bytes of data in the memory. The data for the selected page address must be in the erased state (FFH) before initiating the SPI Quad Page-Program operation. A SPI Quad Page-Program applied to a protected memory area will be ignored. SST26VF064B requires the ICO bit in the configuration register to be set to '1' prior to executing the command. Prior to the program operation, execute the WREN instruction.

To execute a SPI Quad Page-Program operation, the host drives CE# low then sends the SPI Quad Page-Program command cycle (32H), three address cycles followed by the data to be programmed, then drives CE# high. The programmed data must be between 1 to 256 Bytes and in whole Byte increments. The command cycle is eight clocks long, the address and data cycles are each two clocks long, most significant bit first. Poll the BUSY bit in the Status register, or wait  $T_{PP}$ , for the completion of the internal, self-timed, Write operation.See Figure 5-27.

When executing SPI Quad Page-Program, the memory range for the SST26VF064B/064BA is divided into 256 Byte page boundaries. The device handles shifting of more than 256 Bytes of data by maintaining the last 256 Bytes of data as the correct data to be programmed. If the target address for the SPI Quad Page-Program instruction is not the beginning of the page boundary (A[7:0] are not all zero), and the of bytes of data input exceeds or overlaps the end of the address of the page boundary, the excess data inputs wrap around and will be programmed at the start of that target page.

### 5.22 Write-Suspend and Write-Resume

Write-Suspend allows the interruption of Sector-Erase, Block-Erase, SPI Quad Page-Program, or Page-Program operations in order to erase, program, or read data in another portion of memory. The original operation can be continued with the Write-Resume command. This operation is supported in both SQI and SPI protocols.

Only one write operation can be suspended at a time; if an operation is already suspended, the device will ignore the Write-Suspend command. Write-Suspend during Chip-Erase is ignored; Chip-Erase is not a valid command while a write is suspended. The Write-Resume command is ignored until any write operation (Program or Erase) initiated during the Write-Suspend is complete. The device requires a minimum of 500 µs between each Write-Suspend command.

### 5.23 Write-Suspend During Sector-Erase or Block-Erase

Issuing a Write-Suspend instruction during Sector-Erase or Block-Erase allows the host to program or read any sector that was not being erased. The device will ignore any programming commands pointing to the suspended sector(s). Any attempt to read from the suspended sector(s) will output unknown data because the Sector- or Block-Erase will be incomplete.

To execute a Write-Suspend operation, the host drives CE# low, sends the Write Suspend command cycle (B0H), then drives CE# high. The Status register indicates that the erase has been suspended by changing the WSE bit from '0' to '1,' but the device will not accept another command until it is ready. To determine when the device will accept a new command, poll the BUSY bit in the Status register or wait  $T_{WS}$ .

### 5.24 Write Suspend During Page Programming or SPI Quad Page Programming

Issuing a Write-Suspend instruction during Page Programming allows the host to erase or read any sector that is not being programmed. Erase commands pointing to the suspended sector(s) will be ignored. Any attempt to read from the suspended page will output unknown data because the program will be incomplete.

To execute a Write Suspend operation, the host drives CE# low, sends the Write Suspend command cycle (B0H), then drives CE# high. The Status register indicates that the programming has been suspended by changing the WSP bit from '0' to '1,' but the device will not accept another command until it is ready. To determine when the device will accept a new command, poll the BUSY bit in the Status register or wait  $T_{WS}$ .

### 5.25 Write-Resume

Write-Resume restarts a Write command that was suspended, and changes the suspend status bit in the Status register (WSE or WSP) back to '0'.

To execute a Write-Resume operation, the host drives CE# low, sends the Write Resume command cycle (30H), then drives CE# high. To determine if the internal, self-timed Write operation completed, poll the BUSY bit in the Status register, or wait the specified time  $T_{SE}$ ,  $T_{BE}$  or  $T_{PP}$  for Sector-Erase, Block-Erase, or Page-Programming, respectively. The total write time before suspend and after resume will not exceed the uninterrupted write times  $T_{SE}$ ,  $T_{BE}$  or  $T_{PP}$

### 5.26 Read Security ID

The Read Security ID operation is supported in both SPI and SQI modes. To execute a Read Security ID (SID) operation in SPI mode, the host drives CE# low, sends the Read Security ID command cycle (88H), two address cycles, and then one dummy cycle. To execute

TABLE 5-5: PROGRAM SECURITY ID

| a Read Security ID operation in SQI mode, the host |  |  |  |  |  |

|----------------------------------------------------|--|--|--|--|--|

| drives CE# low and then sends the Read Security ID |  |  |  |  |  |

| command, two address cycles, and three dummy       |  |  |  |  |  |

| cvcles.                                            |  |  |  |  |  |

After the dummy cycles, the device outputs data on the falling edge of the SCK signal, starting from the specified address location. The data output stream is continuous through all SID addresses until terminated by a low-to-high transition on CE#. See Table 5-5 for the Security ID address range.

### 5.27 Program Security ID

The Program Security ID instruction programs one to 2040 Bytes of data in the user-programmable, Security ID space. This Security ID space is one-time programmable (OTP). The device ignores a Program Security ID instruction pointing to an invalid or protected address, see Table 5-5. Prior to the program operation, execute WREN.

To execute a Program SID operation, the host drives CE# low, sends the Program Security ID command cycle (A5H), two address cycles, the data to be programmed, then drives CE# high. The programmed data must be between 1 to 256 Bytes and in whole Byte increments.

The device handles shifting of more than 256 Bytes of data by maintaining the last 256 Bytes of data as the correct data to be programmed. If the target address for the Program Security ID instruction is not the beginning of the page boundary, and the number of data input exceeds or overlaps the end of the address of the page boundary, the excess data inputs wrap around and will be programmed at the start of that target page.

The Program Security ID operation is supported in both SPI and SQI mode. To determine the completion of the internal, self-timed Program SID operation, poll the BUSY bit in the software status register, or wait  $T_{PSID}$  for the completion of the internal self-timed Program Security ID operation.

| Program Security ID                 | Address Range |

|-------------------------------------|---------------|

| Unique ID Pre-Programmed at factory | 0000 – 0007H  |

| User Programmable                   | 0008H – 07FFH |

### 5.28 Lockout Security ID

The Lockout Security ID instruction prevents any future changes to the Security ID, and is supported in both SPI and SQI modes. Prior to the operation, execute WREN.

To execute a Lockout SID, the host drives CE# low, sends the Lockout Security ID command cycle (85H), then drives CE# high. Poll the BUSY bit in the software status register, or wait  $T_{PSID}$ , for the completion of the Lockout Security ID operation.

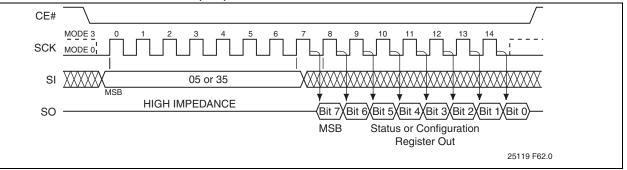

### 5.29 Read-Status Register (RDSR) and Read-Configuration Register (RDCR)

The Read-Status Register (RDSR) and Read-Configuration Register (RDCR) commands output the contents of the Status and Configuration registers. These commands function in both SPI and SQI modes. The Status register may be read at any time, even during a Write operation. When a Write is in progress, poll the BUSY bit before sending any new commands to assure that the new commands are properly received by the device.

To Read the Status or Configuration registers, the host drives CE# low, then sends the Read-Status-Register command cycle (05H) or the Read Configuration Register command (35H). A dummy cycle is required in SQI mode. Immediately after the command cycle, the device outputs data on the falling edge of the SCK signal. The data output stream continues until terminated by a low-to-high transition on CE#. See Figures 5-28 and 5-29 for the instruction sequence.

### FIGURE 5-29: READ-STATUS-REGISTER AND READ-CONFIGURATION REGISTER SEQUENCE (SPI)

### 5.30 Write-Status Register (WRSR)

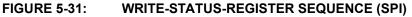

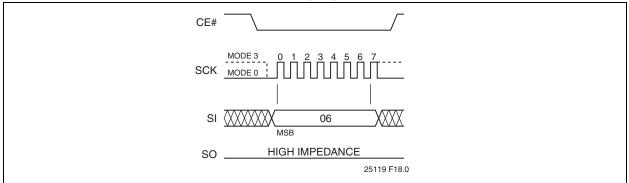

The Write-Status Register (WRSR) command writes new values to the Configuration register. To execute a Write-Status Register operation, the host drives CE# low, then sends the Write-Status Register command cycle (01H), two cycles of data, and then drives CE# high. Values in the second data cycle will be accepted by the device. See Figures 5-30 and 5-31.

### FIGURE 5-30: WRITE-STATUS-REGISTER SEQUENCE (SQI)

Protection Register, Lock-Down Block-Protection Register, Non-Volatile Write-Lock Lock-Down Register, SPI

Quad Page program, and Write-Status Register. To

execute a Write Enable the host drives CE# low then

sends the Write Enable command cycle (06H) then

drives CE# high. See Figures 5-32 and 5-33 for the

WREN instruction sequence.

### 5.31 Write-Enable (WREN)

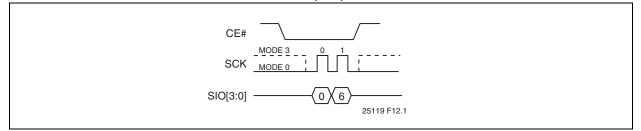

The Write Enable (WREN) instruction sets the Write-Enable-Latch bit in the Status register to '1,' allowing Write operations to occur. The WREN instruction must be executed prior to any of the following operations: Sector Erase, Block Erase, Chip Erase, Page Program, Program Security ID, Lockout Security ID, Write Block-

FIGURE 5-32: WRITE-ENABLE SEQUENCE (SQI)

FIGURE 5-33: WRITE-ENABLE SEQUENCE (SPI)

### 5.32 Write-Disable (WRDI)

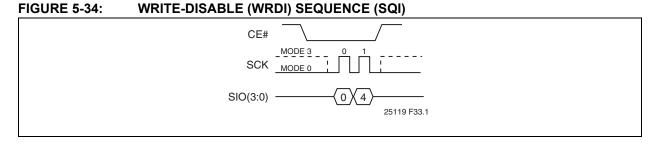

The Write-Disable (WRDI) instruction sets the Write-Enable-Latch bit in the Status register to '0,' preventing Write operations. The WRDI instruction is ignored during any internal write operations. Any Write operation started before executing WRDI will complete. Drive CE# high before executing WRDI.

To execute a Write-Disable, the host drives CE# low, sends the Write Disable command cycle (04H), then drives CE# high. See Figures 5-34 and 5-35.

### FIGURE 5-35: WRITE-DISABLE (WRDI) SEQUENCE (SPI)

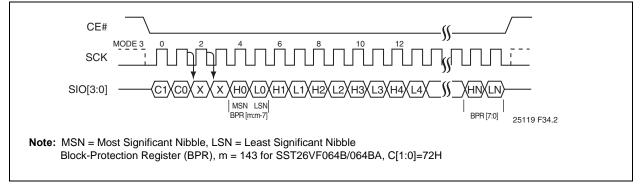

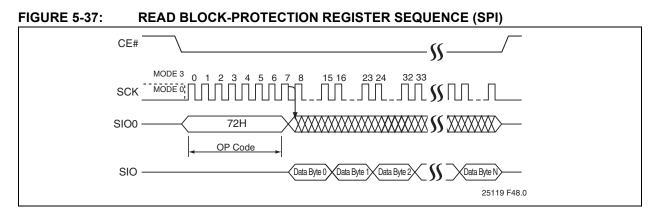

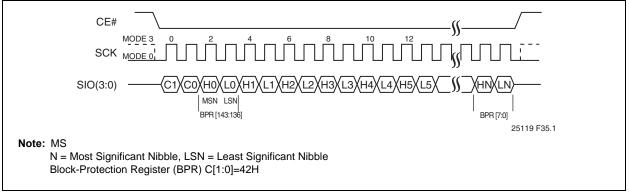

# 5.33 Read Block-Protection Register (RBPR)

The Read Block-Protection Register instruction outputs the Block-Protection register data which determines the protection status. To execute a Read Block-Protection Register operation, the host drives CE# low, and then sends the Read Block-Protection Register command cycle (72H). A dummy cycle is required in SQI mode. After the command cycle, the device outputs data on the falling edge of the SCK signal starting with the most significant bit(s), see Table 5-6 for definitions of each bit in the Block-Protection register. The RBPR command does not wrap around. After all data has been output, the device will output 0H until terminated by a low-tohigh transition on CE#. Figures 5-36 and 5-37.

### FIGURE 5-36: READ BLOCK-PROTECTION REGISTER SEQUENCE (SQI)