# **USB3315**

# Hi-Speed USB Transceiver with 1.8V-3.3V ULPI Interface -24MHz Reference Clock

## **PRODUCT FEATURES**

#### Datasheet

- USB-IF "Hi-Speed" compliant to the Universal Serial Bus Specification Rev 2.0

- Interface compliant with the ULPI Specification revision 1.1 as a Single Data Rate (SDR) PHY

- 1.8V to 3.3V IO Voltage (±10%)

- flexPWR<sup>®</sup> Technology

- Low current design ideal for battery powered applications

- "Sleep" mode tri-states all ULPI pins and places the part in a low current state

- Supports FS pre-amble for FS hubs with a LS device attached (UTMI+ Level 3)

- Supports HS SOF and LS keep-alive pulse

- Includes full support for the optional On-The-Go (OTG) protocol detailed in the On-The-Go Supplement Revision 2.0 specification

- Supports the OTG Host Negotiation Protocol (HNP) and Session Request Protocol (SRP)

- Allows host to turn VBUS off to conserve battery power in OTG applications

- Support OTG monitoring of VBUS levels with internal comparators

- "Wrapper-less" design for optimal timing performance and design ease

- Low Latency Hi-Speed Receiver (43 Hi-Speed clocks Max) allows use of legacy UTMI Links with a ULPI bridge

- Internal 5V cable short-circuit protection of ID, DP and DM lines to VBUS or ground

- 24MHz Reference Clock Operation

- 0 to 3.6V input drive tolerant

- Able to accept "noisy" clock sources

- Internal low jitter PLL for 480MHz Hi-Speed USB operation

- Internal detection of the value of resistance to ground on the ID pin

- Integrated battery to 3.3V LDO regulator

- 2.2uF bypass capacitor

100mV dropout voltage

- Integrated ESD protection circuits

- Up to ±15kV without any external devices

- Carkit UART mode for non-USB serial data transfers

- Industrial Operating Temperature -40°C to +85°C

- Packaging Options

- 24 pin QFN lead-free RoHS compliant package (4 x 4 x 0.90 mm height)

## Applications

The USB3315 is targeted for any application where a Hi-Speed USB connection is desired and when board space, power, and interface pins must be minimized.

The USB3315 is well suited for:

- Cell Phones

- PDAs

- MP3 Players

- GPS Personal Navigation

- Scanners

- External Hard Drives

- Digital Still and Video Cameras

- Portable Media Players

- Entertainment Devices

- Printers

- Set Top Boxes

- Video Record/Playback Systems

- IP and Video Phones

- Gaming Consoles

- POS Terminals

## DATASHEET

Order Number(s):

USB3315C-CP-TR FOR 24 PIN, QFN LEAD-FREE ROHS COMPLIANT PACKAGE (TAPE AND REEL) REEL SIZE IS 4000 PIECES.

This product meets the halogen maximum concentration values per IEC61249-2-21 For RoHS compliance and environmental information, please visit www.smsc.com/rohs

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

#### Copyright © 2010 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

## 0.1 Reference Documents

- Universal Serial Bus Specification, Revision 2.0, April 27, 2000

- On-The-Go Supplement to the USB 2.0 Specification, Revision 2.0, May 8, 2009

- 27% Resistor ECN

- USB 2.0 Transceiver Macrocell Interface (UTMI) Specification, Version 1.02, May 27, 2000

- UTMI+ Specification, Revision 1.0, February 2, 2004

- UTMI+ Low Pin Interface (ULPI) Specification, Revision 1.1, October 20, 2004

- Technical Requirements and Test Methods of Charger and Interface for Mobile Telecommunication Terminal Equipment (Chinese Charger Specification Approval Draft 11/29/2006)

# **Table of Contents**

| 0.1                                                          | Reference Documents                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 3                                                                        |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Chap                                                         | ter 1 General Description                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 8                                                                        |

| <b>Chap</b><br>2.1                                           | ter 2USB3315 Pin Locations and DefinitionsUSB3315 Pin Locations and Descriptions2.1.1Package Diagram with Pin Locations2.1.2Pin Definitions                                                                                                                                                                                                                                                                                                                   | .9<br>.9                                                                   |

| <b>Chap</b><br>3.1<br>3.2                                    | ter 3 Limiting Values                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12                                                                         |

| Chap<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8 | ter 4 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                              | 14<br>15<br>15<br>15<br>16<br>18<br>18                                     |

| Chap<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6               | ULPI Digital Operation and Interface .<br>Interface to DP/DM .<br>5.2.1 USB Transceiver .<br>5.2.2 Termination Resistors .<br>Bias Generator .<br>Integrated Low Jitter PLL .<br>5.4.1 Reference Clock Requirements .<br>Internal Regulators and POR .<br>5.5.1 Integrated Low Dropout Regulator .<br>5.5.2 Power On Reset (POR) .<br>5.5.3 Recommended Power Supply Sequence .<br>5.5.4 Start-Up .<br>USB On-The-Go (OTG) .<br>5.6.1 ID Resistor Detection . | 20<br>20<br>21<br>23<br>23<br>23<br>24<br>24<br>26<br>26<br>27<br>28<br>29 |

| 5.7<br>5.8<br>Chap                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33<br>34<br>34<br><b>35</b>                                                |

| 6.1<br>6.2                                                   | Overview.         6.1.1       ULPI Interface Signals.         6.1.2       ULPI Interface Timing in Synchronous Mode         ULPI Register Access.         6.2.1       ULPI Register Write.         6.2.2       ULPI Register Read.         6.2.3       ULPI RXCMD         6.2.4       USB3315 Transmitter                                                                                                                                                     | 36<br>37<br>37<br>38<br>40<br>41                                           |

| Cha | pter 10 | Datasheet Revision History73                              |

|-----|---------|-----------------------------------------------------------|

| Cha | pter 9  | Package Outline, Tape & Reel Drawings, Package Markings69 |

|     | 8.4.4   | Contact Discharge                                         |

|     | 8.4.3   | Air Discharge                                             |

|     | 8.4.2   | EN/IEC 61000-4-2 Performance                              |

|     | 8.4.1   | Human Body Model (HBM) Performance67                      |

| 8.4 | ESD P   | erformance                                                |

| 8.3 | Refere  | nce Designs                                               |

|     | 8.2.2   | Detecting DP Shorted to DM                                |

|     | 8.2.1   | Detecting the ID Resistor in a Charger                    |

| 8.2 |         | harger Detection                                          |

| 8.1 | -       | ation Diagram                                             |

| Cha | pter 8  | Application Notes                                         |

|     | 7.1.4   | Vendor Register Access                                    |

|     | 7.1.3   | Extended Register Access 61                               |

|     | 7.1.2   | Carkit Control Registers                                  |

|     | 7.1.1   | ULPI Register Set                                         |

| 7.1 |         | Register Array                                            |

| Cha | pter 7  | ULPI Register Map                                         |

| 6.6 | Heads   | et Audio Mode                                             |

| 6.5 | RID Co  | onverter Operation                                        |

|     | 6.4.1   | USB UART Mode                                             |

| 6.4 | Carkit  | Mode                                                      |

|     | 6.3.2   | 6pin FS/LS Serial Mode                                    |

| 0.0 | 6.3.1   | 3pin FS/LS Serial Mode                                    |

| 6.3 |         | eed/Low Speed Serial Modes                                |

|     | 6.2.6   | Low Power Mode                                            |

|     | 6.2.5   | USB Receiver                                              |

# List of Figures

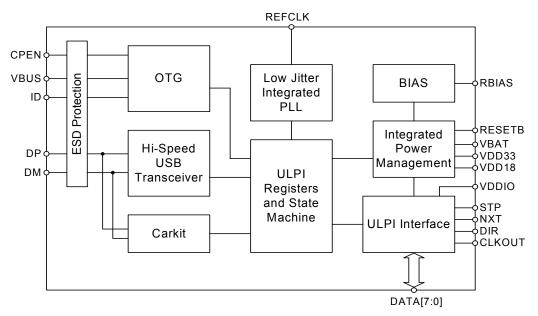

| Figure 1.1  | USB3315 Block Diagram                                                        | 8  |

|-------------|------------------------------------------------------------------------------|----|

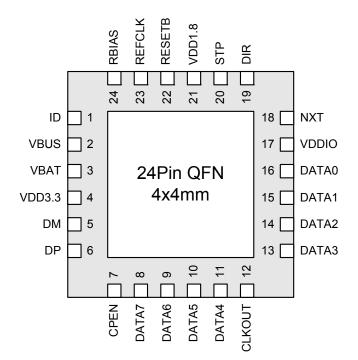

| Figure 2.1  | USB3315 QFN Pinout - Top View                                                | 9  |

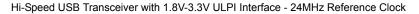

| Figure 4.1  | External Reference Clock                                                     | 16 |

| Figure 5.1  | USB3315 System Diagram                                                       |    |

| Figure 5.2  | Example of circuit used to shift a reference clock common-mode voltage level | 23 |

| Figure 5.3  | USB3315 Allowable REFCLK Jitter vs. Frequency                                | 24 |

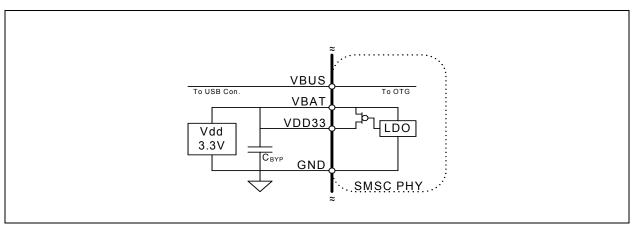

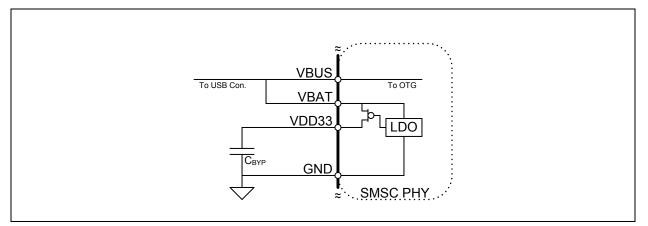

| Figure 5.4  | Powering the USB3315 from a Battery                                          | 25 |

| Figure 5.5  | Powering the USB3315 from a 3.3V Supply                                      |    |

| Figure 5.6  | Powering the USB3315 from the USB Cable Vbus                                 | 26 |

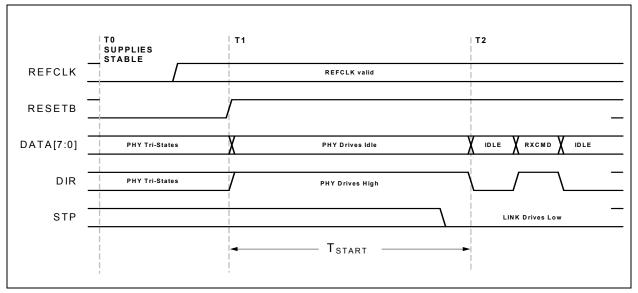

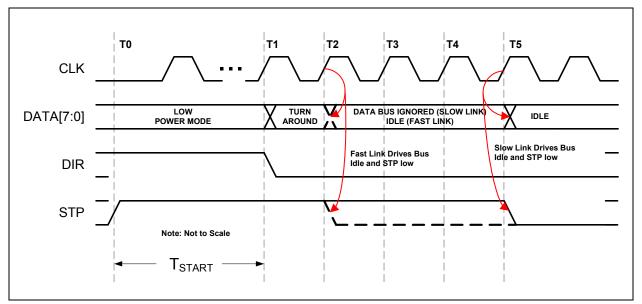

| Figure 5.7  | ULPI Start-up Timing                                                         | 28 |

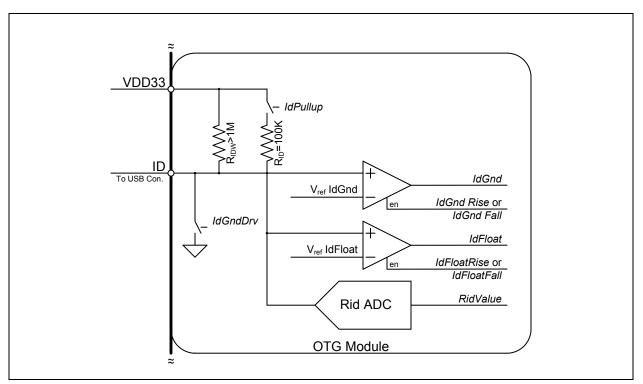

| Figure 5.8  | USB3315 ID Resistor Detection Circuitry.                                     | 29 |

| Figure 5.9  | USB3315 OTG Vbus Block                                                       |    |

| Figure 5.10 | USB3315 Drives External Vbus Supply or Switch                                | 33 |

| Figure 6.1  | ULPI Digital Block Diagram                                                   |    |

| Figure 6.2  | ULPI Single Data Rate Timing Diagram in Synchronous Mode                     |    |

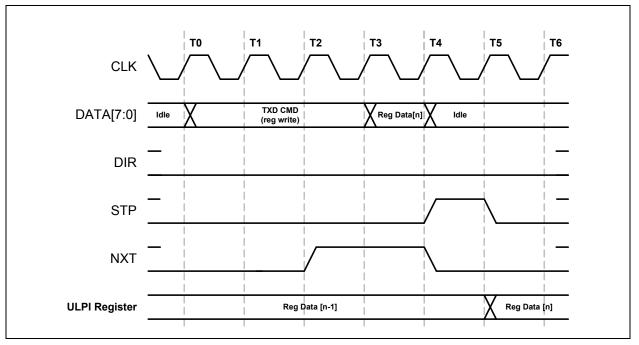

| Figure 6.3  | ULPI Register Write in Synchronous Mode                                      |    |

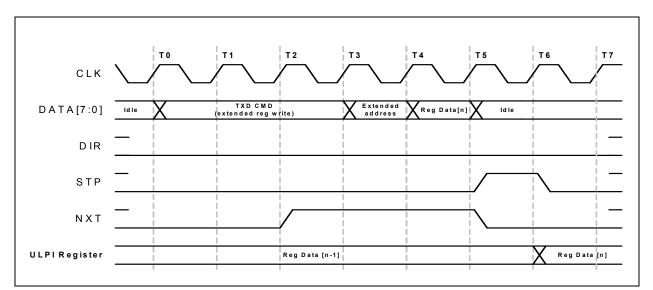

| Figure 6.4  | ULPI Extended Register Write in Synchronous Mode                             | 39 |

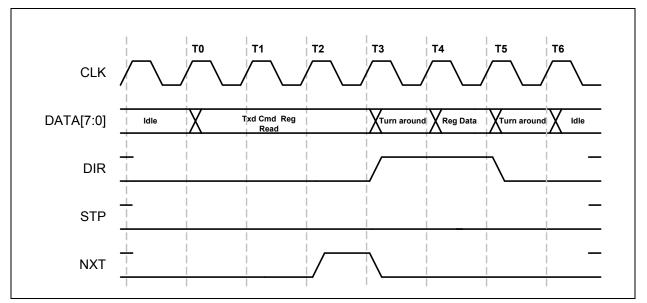

| Figure 6.5  | ULPI Register Read in Synchronous Mode                                       | 40 |

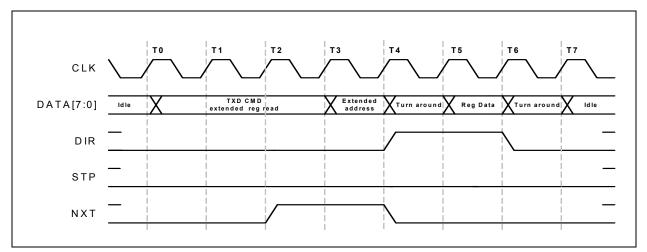

| Figure 6.6  | ULPI Extended Register Read in Synchronous Mode                              | 41 |

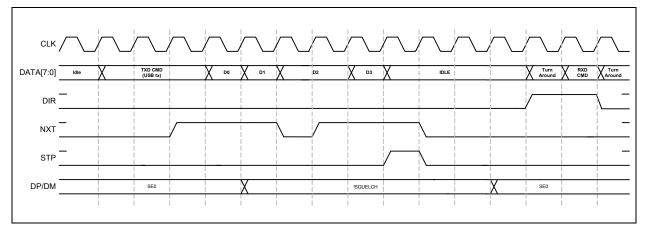

| Figure 6.7  | ULPI Transmit in Synchronous Mode                                            | 44 |

| Figure 6.8  | ULPI Receive in Synchronous Mode                                             | 45 |

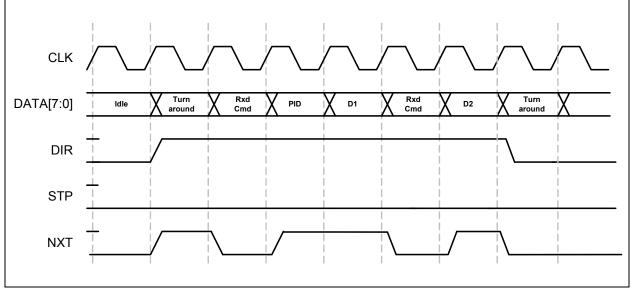

| Figure 6.9  | Entering Low Power Mode from Synchronous Mode                                | 46 |

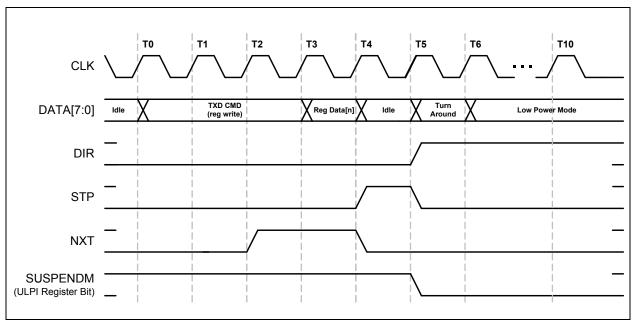

| Figure 6.10 | Exiting Low Power Mode                                                       | 47 |

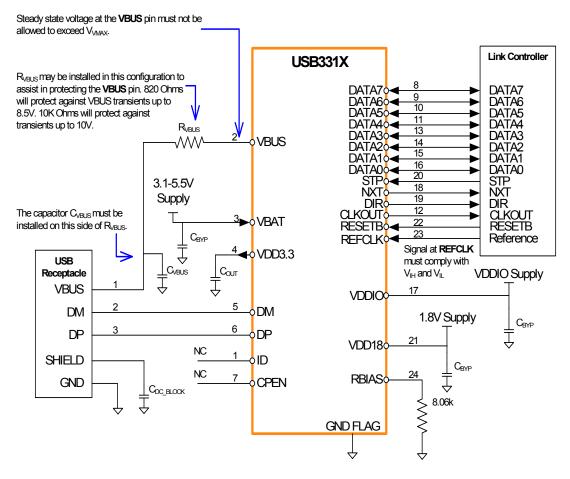

| Figure 8.1  | USB3315 QFN Application Diagram (Device)                                     | 65 |

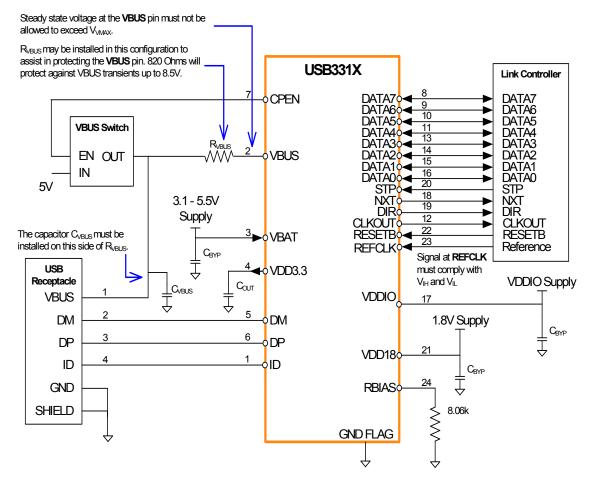

| Figure 8.2  | USB3315 QFN Application Diagram (Host or OTG)                                | 66 |

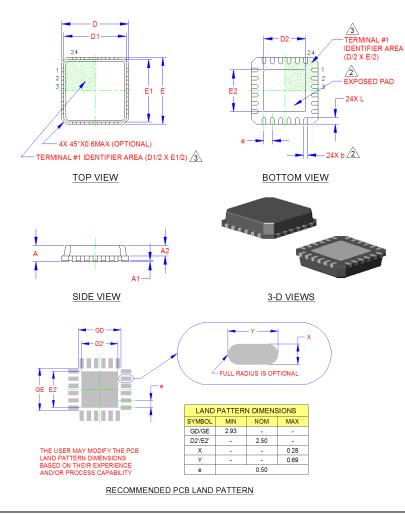

| Figure 9.1  | 24-pin QFN, 4x4mm Body, 0.5mm Pitch                                          | 69 |

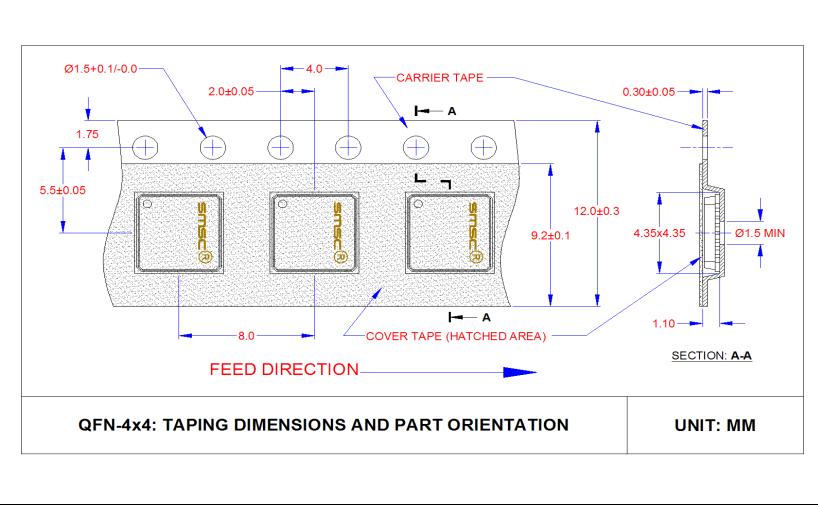

| Figure 9.2  | QFN, 4x4 Tape & Reel                                                         | 70 |

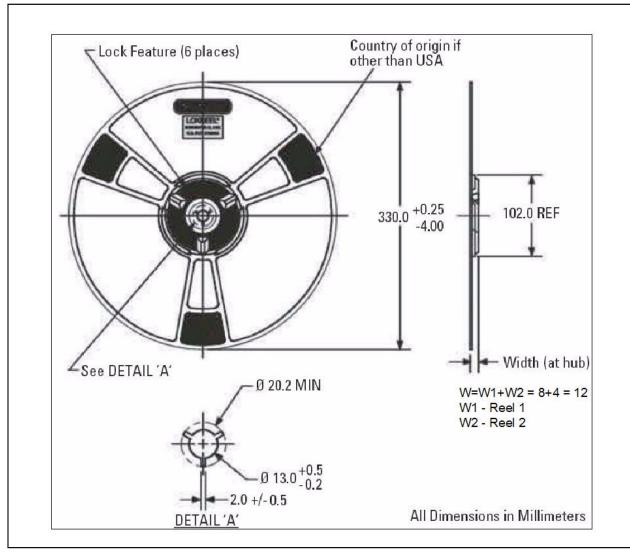

| Figure 9.3  | Reel Dimensions                                                              | 71 |

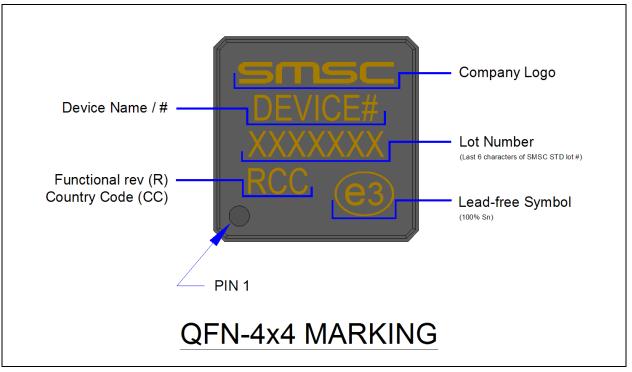

| Figure 9.4  | QFN, 4x4 Package Marking                                                     | 72 |

# **List of Tables**

| Table 2.1  | USB3315 Pin Description                                                           | 9    |

|------------|-----------------------------------------------------------------------------------|------|

| Table 3.1  | Absolute Maximum Ratings                                                          | . 12 |

| Table 3.2  | Recommended Operating Conditions.                                                 | . 13 |

| Table 4.1  | Electrical Characteristics: Operating Current                                     | . 14 |

| Table 4.2  | Electrical Characteristics: CLKOUT Specifications                                 | . 15 |

| Table 4.3  | ULPI Interface Timing                                                             | . 15 |

| Table 4.4  | Digital IO Characteristics: RESETB, CLKOUT, STP, DIR, NXT, DATA[7:0] and XI Pins. | . 15 |

| Table 4.5  | DC Characteristics: Analog I/O Pins (DP/DM)                                       | . 16 |

| Table 4.6  | Dynamic Characteristics: Analog I/O Pins (DP/DM)                                  | . 18 |

| Table 4.7  | OTG Electrical Characteristics                                                    | . 18 |

| Table 4.8  | Regulator Output Voltages and Capacitor Requirement                               | . 19 |

| Table 4.9  | ESD and LATCH-UP Performance                                                      |      |

| Table 5.1  | DP/DM Termination vs. Signaling Mode                                              | . 21 |

| Table 5.2  | Operating Mode vs. Power Supply Configuration                                     | . 27 |

| Table 5.3  | Valid Values of ID Resistance to Ground                                           | . 30 |

| Table 5.4  | IdGnd and IdFloat vs. ID Resistance to Ground                                     |      |

| Table 5.5  | External Vbus Indicator Logic                                                     |      |

| Table 5.6  | USB Weak Pull-up Enable                                                           | . 34 |

| Table 6.1  | ULPI Interface Signals                                                            |      |

| Table 6.2  | ULPI TXD CMD Byte Encoding                                                        | . 38 |

| Table 6.3  | ULPI RX CMD Encoding.                                                             | . 42 |

| Table 6.4  | Interface Signal Mapping During Low Power Mode                                    |      |

| Table 6.5  | Pin Definitions in 3 pin Serial Mode                                              |      |

| Table 6.6  | Pin Definitions in 6 pin Serial Mode                                              | . 49 |

| Table 6.7  | Pin Definitions in Carkit Mode.                                                   |      |

| Table 6.8  | Pin Definitions in Headset Audio Mode                                             |      |

| Table 7.1  | ULPI Register Map                                                                 |      |

| Table 8.1  | Component Values in Application Diagrams                                          |      |

| Table 8.2  | Capacitance Values at VBUS of USB Connector                                       | . 64 |

| Table 10.1 | Customer Revision History                                                         | . 73 |

# **Chapter 1 General Description**

The USB3315 is a highly integrated Hi-Speed USB 2.0 Transceiver (PHY) that supports systems architectures based on a 24MHz reference clock. It is designed to be used in both commercial and industrial temperature applications.

The USB3315 meets all of the electrical requirements to be used as a Hi-Speed USB Host, Device, or an On-the-Go (OTG) device. In addition to the supporting USB signaling the USB3315 also provides USB UART mode

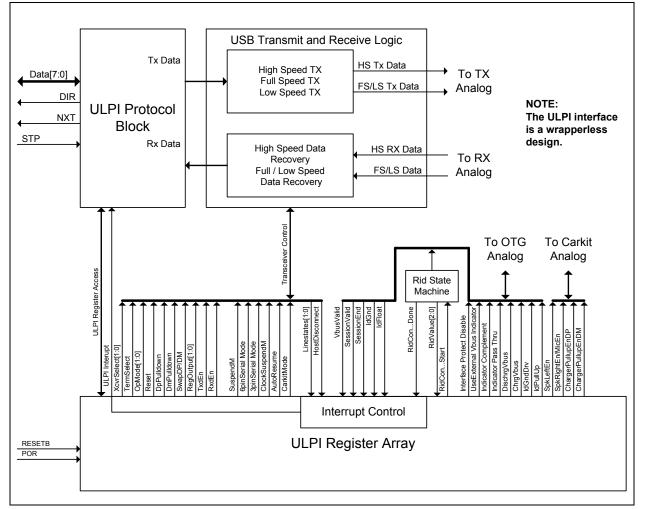

USB3315 uses the industry standard UTMI+ Low Pin Interface (ULPI) to connect the USB PHY to the Link. The industry standard ULPI interface uses a method of in-band signaling and status byte transfers between the Link and PHY, to facilitate a USB session. By using in-band signaling and status byte transfers the ULPI interface requires only 12 pins.

The USB3315 uses SMSC's "wrapper-less" technology to implement the ULPI interface. This "wrapperless" technology allows the PHY to achieve a low latency transmit and receive time. SMSC's low latency transceiver allows an existing UTMI Link to be reused by adding a UTMI to ULPI bridge. By adding a bridge to the ASIC the existing and proven UTMI Link IP can be reused.

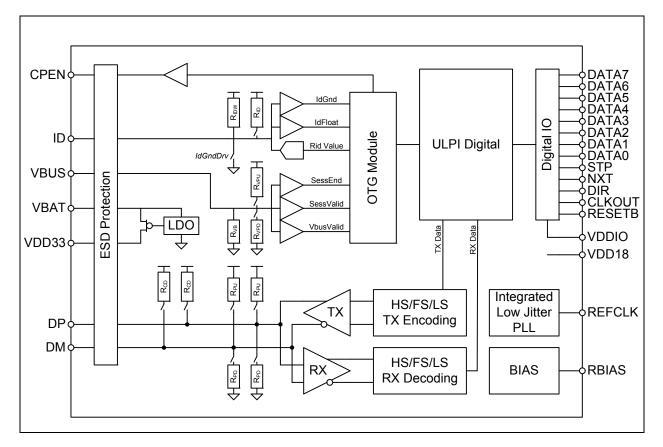

Figure 1.1 USB3315 Block Diagram

The USB3315 is designed to run with a 24MHz reference clock. By using a reference clock from the Link the USB3315 is able to remove the cost of a crystal reference from the design.

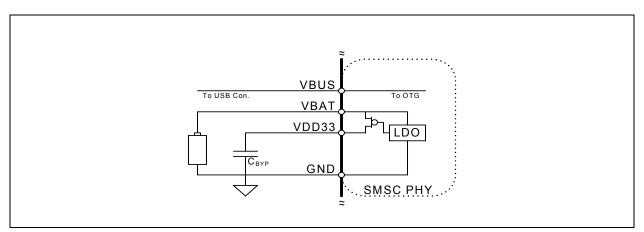

The USB3315 includes a integrated 3.3V LDO regulator to generate its own supply from power applied at the **VBAT** pin. The voltage on the **VBAT** pin can range from 3.1 to 5.5V. The regulator dropout voltage is less than 100mV which allows the PHY to continue USB signaling when the voltage on **VBAT** drops to 3.1V. The USB transceiver will continue to operate at lower voltages, although some parameters may be outside the limits of the USB specifications. If the user would like to provide a 3.3V supply to the USB3315, the **VBAT** and **VDD33** pins should be connected together as described in Section 5.5.1.

The USB3315 also includes integrated pull-up resistors that can be used for detecting the attachment of a USB Charger. By sensing the attachment to a USB Charger, a product using the USB3315 can charge its battery at more than the 500mA allowed when charging from a USB Host as described in Section 8.2.

**Chapter 2 USB3315 Pin Locations and Definitions**

# 2.1 USB3315 Pin Locations and Descriptions

## 2.1.1 Package Diagram with Pin Locations

The pinout below is viewed from the top of the package.

Figure 2.1 USB3315 QFN Pinout - Top View

## 2.1.2 Pin Definitions

The following table details the pin definitions for the figure above.

| PIN | NAME | DIRECTION/<br>TYPE | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                   |

|-----|------|--------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ID   | Input,<br>Analog   | N/A             | <b>ID</b> pin of the USB cable. For non-OTG applications this pin can be floated. For an A-Device <b>ID</b> is grounded. For a B-Device <b>ID</b> is floated. |

| 2   | VBUS | l/O,<br>Analog     | N/A             | <b>VBUS</b> pin of the USB cable. This pin is used for the Vbus comparator inputs and for Vbus pulsing during session request protocol.                       |

| 3   | VBAT | Power              | N/A             | Regulator input. The regulator supply can be from 5.5V to 3.1V.                                                                                               |

Table 2.1 USB3315 Pin Description

| PIN | NAME    | DIRECTION/<br>TYPE | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                    |

|-----|---------|--------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | VDD3.3  | Power              | N/A             | 3.3V Regulator Output. A 2.2uF (<1 ohm<br>ESR) bypass capacitor to ground is<br>required for regulator stability. The<br>bypass capacitor should be placed as<br>close as possible to the USB3315.                                                             |

| 5   | DM      | I/O,<br>Analog     | N/A             | D- pin of the USB cable.                                                                                                                                                                                                                                       |

| 6   | DP      | I/O,<br>Analog     | N/A             | D+ pin of the USB cable.                                                                                                                                                                                                                                       |

| 7   | CPEN    | Output,<br>CMOS    | High            | External 5 volt supply enable. This pin is<br>used to enable the external Vbus power<br>supply. The <b>CPEN</b> pin is low on POR.<br>This pad uses VDD3.3 logic level.                                                                                        |

| 8   | DATA[7] | I/O,<br>CMOS       | N/A             | ULPI bi-directional data bus. DATA[7] is the MSB.                                                                                                                                                                                                              |

| 9   | DATA[6] | I/O,<br>CMOS       | N/A             | ULPI bi-directional data bus.                                                                                                                                                                                                                                  |

| 10  | DATA[5  | I/O,<br>CMOS       | N/A             | ULPI bi-directional data bus.                                                                                                                                                                                                                                  |

| 11  | DATA[4] | I/O,<br>CMOS       | N/A             | ULPI bi-directional data bus.                                                                                                                                                                                                                                  |

| 12  | CLKOUT  | Output,<br>CMOS    | N/A             | 60MHz reference clock output. All ULPI signals are driven synchronous to the rising edge of this clock.<br>Following POR or hardware reset, the voltage at <b>CLKOUT</b> must not exceed V <sub>IH ED</sub> as provided in Table 4.4.                          |

| 13  | DATA[3] | I/O,<br>CMOS       | N/A             | ULPI bi-directional data bus.                                                                                                                                                                                                                                  |

| 14  | DATA[2] | I/O,<br>CMOS       | N/A             | ULPI bi-directional data bus.                                                                                                                                                                                                                                  |

| 15  | DATA[1] | I/O,<br>CMOS       | N/A             | ULPI bi-directional data bus.                                                                                                                                                                                                                                  |

| 16  | DATA[0] | I/O,<br>CMOS       | N/A             | ULPI bi-directional data bus. <b>DATA[0]</b> is the LSB.                                                                                                                                                                                                       |

| 17  | VDDIO   | Power              | N/A             | 1.8V to 3.3V ULPI interface supply voltage. This voltage sets the value of $V_{OH}$ for the ULPI interface.                                                                                                                                                    |

| 18  | NXT     | Output,<br>CMOS    | High            | The PHY asserts <b>NXT</b> to throttle the data.<br>When the Link is sending data to the<br>PHY, <b>NXT</b> indicates when the current<br>byte has been accepted by the PHY. The<br>Link places the next byte on the data bus<br>in the following clock cycle. |

### Table 2.1 USB3315 Pin Description (continued)

## Table 2.1 USB3315 Pin Description (continued)

| PIN  | NAME   | DIRECTION/<br>TYPE | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                  |

|------|--------|--------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19   | DIR    | Output,<br>CMOS    | N/A             | Controls the direction of the data bus.<br>When the PHY has data to transfer to the<br>Link, it drives <b>DIR</b> high to take ownership<br>of the bus. When the PHY has no data to<br>transfer it drives <b>DIR</b> low and monitors<br>the bus for commands from the Link. |

| 20   | STP    | Input,<br>CMOS     | High            | The Link asserts <b>STP</b> for one clock cycle<br>to stop the data stream currently on the<br>bus. If the Link is sending data to the<br>PHY, <b>STP</b> indicates the last byte of data<br>was on the bus in the previous cycle.                                           |

| 21   | VDD1.8 | Power              | N/A             | External 1.8V Supply input pin. This pad<br>needs to be bypassed with a 0.1uF<br>capacitor to ground, placed as close as<br>possible to the USB3315.                                                                                                                         |

| 22   | RESETB | Input,<br>CMOS,    | N/A             | When low, the part is suspended with all<br>of the I/O tri-stated. When high the<br>USB3315 will operate as a normal ULPI<br>device.                                                                                                                                         |

| 23   | REFCLK | Input,<br>CMOS     | N/A             | 24MHz Reference Clock input.                                                                                                                                                                                                                                                 |

| 24   | RBIAS  | Analog,<br>CMOS    | N/A             | Rbias pin. This pin requires an $8.06k\Omega$ (±1%) resistor to ground, placed as close as possible to the USB3315.                                                                                                                                                          |

| FLAG | GND    | Ground             | N/A             | Ground.<br><u>QFN only:</u> The flag should be connected<br>to the ground plane with a via array<br>under the exposed flag. This is the main<br>ground for the IC.                                                                                                           |

# **Chapter 3 Limiting Values**

# 3.1 Absolute Maximum Ratings

| PARAMETER                                                     | SYMBOL                | CONDITIONS                          | MIN  | ТҮР | МАХ                     | UNITS |

|---------------------------------------------------------------|-----------------------|-------------------------------------|------|-----|-------------------------|-------|

| Maximum VBUS, VBAT,<br>ID, DP, DM, and CPEN<br>voltage to GND | V <sub>MAX_5V</sub>   |                                     | -0.5 |     | +6.0                    | V     |

| Maximum <b>VDD18</b> voltage to Ground                        | V <sub>MAX_1.8V</sub> |                                     | -0.5 |     | 2.5                     | V     |

| Maximum <b>VDDIO</b> voltage to Ground                        | V <sub>MAX_IOV</sub>  | <b>VDD18</b> = V <sub>DD18</sub>    | -0.5 |     | 4.0                     | V     |

| Maximum <b>VDDIO</b> voltage to Ground                        | V <sub>MAX_IOV</sub>  | <b>VDD18</b> = 0V                   | -0.5 |     | 0.7                     | V     |

| Maximum <b>VDD33</b> voltage to Ground                        | V <sub>MAX_3.3V</sub> |                                     | -0.5 |     | 4.0                     | V     |

| Maximum I/O voltage to Ground                                 | V <sub>MAX_IN</sub>   |                                     | -0.5 |     | V <sub>DDIO</sub> + 0.7 | V     |

| QFN Package Junction to Ambient ( $\theta_{JA}$ )             |                       | Thermal vias per Layout Guidelines. |      | 58  |                         | °C/W  |

| QFN Package Junction to Case $(\theta_{JC})$                  |                       |                                     |      | 11  |                         | °C/W  |

| Operating Temperature                                         | T <sub>MAX_OP</sub>   |                                     | -40  |     | 85                      | С     |

| Storage Temperature                                           | T <sub>MAX_STG</sub>  |                                     | -55  |     | 150                     | С     |

### Table 3.1 Absolute Maximum Ratings

**Note:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 3.2 Recommended Operating Conditions

| PARAMETER                                                                                          | SYMBOL              | CONDITIONS         | MIN | ТҮР     | MAX               | UNITS |

|----------------------------------------------------------------------------------------------------|---------------------|--------------------|-----|---------|-------------------|-------|

| VBAT to GND                                                                                        | V <sub>VBAT</sub>   |                    | 3.1 |         | 5.5               | V     |

| VDD33 to GND                                                                                       | V <sub>DD33</sub>   |                    | 3.0 | 3.3     | 3.6               | V     |

| VDDIO to GND                                                                                       | V <sub>DDIO</sub>   | VDDIO ≥ VDD18(min) | 1.6 | 1.8-3.3 | 3.6               | V     |

| VDD18 to GND                                                                                       | V <sub>DD18</sub>   |                    | 1.6 | 1.8     | 2.0               | V     |

| Input Voltage on Digital<br>Pins (RESETB, STP,<br>DIR, NXT, DATA[7:0])                             | VI                  |                    | 0.0 |         | V <sub>DDIO</sub> | V     |

| Voltage on Analog I/O<br>Pins ( <b>DP</b> , <b>DM</b> , <b>ID</b> , <b>CPEN</b> )<br><b>CPEN</b> , | V <sub>I(I/O)</sub> |                    | 0.0 |         | V <sub>DD33</sub> | V     |

| VBUS to GND                                                                                        | V <sub>VMAX</sub>   |                    | 0.0 |         | 5.5               | V     |

| Ambient Temperature                                                                                | Τ <sub>Α</sub>      |                    | -40 |         | 85                | С     |

### Table 3.2 Recommended Operating Conditions

# **Chapter 4 Electrical Characteristics**

The following conditions are assumed unless otherwise specified:

$V_{VBAT}$  = 3.1 to 5.5V;  $V_{DD18}$  = 1.6 to 2.0V;  $V_{DDIO}$  = 1.6 to 2.0V;  $V_{SS}$  = 0V;  $T_A$  = -40C to +85C

The current for 3.3V circuits is sourced at the VBAT pin, except when using an external 3.3V supply as shown in Figure 5.5.

# 4.1 **Operating Current**

| PARAMETER                                         | SYMBOL                   | CONDITIONS                                                                       | MIN  | ТҮР  | MAX  | UNITS |

|---------------------------------------------------|--------------------------|----------------------------------------------------------------------------------|------|------|------|-------|

| Synchronous Mode Current                          | I <sub>33AVG(SYNC)</sub> | Start-up sequence defined<br>in Section 5.5.4 has<br>completed.                  | 5.0  | 5.5  | 8.0  | mA    |

| (Default Configuration)                           | I <sub>18AVG(SYNC)</sub> |                                                                                  | 17.5 | 22.0 | 27.0 | mA    |

|                                                   | I <sub>IOAVG(SYNC)</sub> |                                                                                  | 2.5  | 3.0  | 4.0  | mA    |

| Synchronous Mode Current                          | I <sub>33AVG(HS)</sub>   | Active USB Transfer                                                              | 7.0  | 10.0 | 14.0 | mA    |

| (HS USB operation)                                | I <sub>18AVG(HS)</sub>   |                                                                                  | 23.0 | 28.0 | 34.0 | mA    |

|                                                   | I <sub>IOAVG(HS)</sub>   |                                                                                  | 2.5  | 3.0  | 4.0  | mA    |

| Synchronous Mode Current<br>(FS/LS USB operation) | I <sub>33AVG(FS)</sub>   | Active USB Transfer                                                              | 5.0  | 8.5  | 13.0 | mA    |

|                                                   | I <sub>18AVG(FS)</sub>   |                                                                                  | 19.0 | 22.0 | 27.0 | mA    |

|                                                   | I <sub>IOAVG(FS)</sub>   |                                                                                  | 2.5  | 3.0  | 4.0  | mA    |

| Serial Mode Current<br>(FS/LS USB)                | I <sub>33AVG(FS_S)</sub> |                                                                                  | 5.0  | 5.5  | 7.0  | mA    |

| Note 4.1                                          | I <sub>18AVG(FS_S)</sub> |                                                                                  | 1.5  | 2.2  | 3.5  | mA    |

| Note 4.1                                          | I <sub>IOAVG(FS_S)</sub> |                                                                                  |      |      | 0.1  | mA    |

| USB UART Current                                  | I <sub>33AVG(UART)</sub> |                                                                                  | 5.0  | 5.5  | 7.0  | mA    |

| Note 4.1                                          | I <sub>18AVG(UART)</sub> |                                                                                  | 1.4  | 2.1  | 3.5  | mA    |

|                                                   | I <sub>IOAVG(UART)</sub> |                                                                                  |      |      | 0.1  | mA    |

| Low Power Mode                                    | I <sub>DD33(LPM)</sub>   | V <sub>VBAT</sub> = 4.2V<br>V <sub>DD18</sub> = 1.8V<br>V <sub>DDI0</sub> = 1.8V | 14.0 | 20.0 | 25.0 | uA    |

| Note 4.2                                          | I <sub>DD18(LPM)</sub>   | $V_{DD18} = 1.8V$<br>$V_{DD10} = 1.8V$                                           |      | 0.3  | 10.0 | uA    |

|                                                   | I <sub>DDIO(LPM)</sub>   |                                                                                  |      |      | 1.5  | uA    |

| Standby Mode                                      | I <sub>DD33(RSTB)</sub>  | RESETB = 0                                                                       | 14.0 | 20.0 | 25.0 | uA    |

|                                                   | I <sub>DD18(RSTB)</sub>  | $V_{VBAT} = 4.2V$<br>$V_{DD18} = 1.8V$                                           |      | 0.3  | 10.0 | uA    |

|                                                   | I <sub>DDIO(RSTB)</sub>  | $V_{\text{DDIO}}^{\text{DDIO}} = 1.8 \text{V}$                                   |      |      | 1.5  | uA    |

#### Table 4.1 Electrical Characteristics: Operating Current

**Note 4.1** *ClockSuspendM* bit = 0.

Note 4.2 SessEnd, VbusVld, and IdFloat comparators disabled. STP Interface protection disabled.

# 4.2 CLKOUT Specifications

#### Table 4.2 Electrical Characteristics: CLKOUT Specifications

| PARAMETER                         | SYMBOL               | CONDITIONS | MIN  | ТҮР  | MAX  | UNITS |

|-----------------------------------|----------------------|------------|------|------|------|-------|

| Suspend Recovery Time<br>Note 4.3 | T <sub>START</sub>   |            |      | 1.12 | 2.37 | ms    |

| CLKOUT Duty Cycle                 | DC <sub>CLKOUT</sub> |            | 45   |      | 55   | %     |

| REFCLK Duty Cycle                 | DC <sub>REFCLK</sub> |            | 20   |      | 80   | %     |

| <b>REFCLK</b> Frequency Accuracy  | F <sub>REFCLK</sub>  |            | -500 |      | +500 | PPM   |

**Note 4.3** The USB3315 uses the *AutoResume* feature, Section 5.4, to allow a host start-up time of less than 1ms

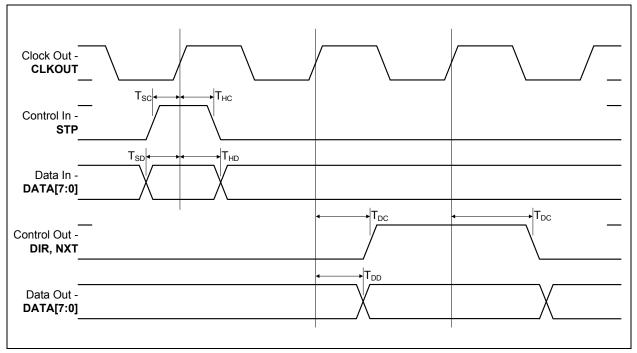

# 4.3 ULPI Interface Timing

| PARAMETER                                  | SYMBOL                            | MIN | MAX | UNITS |

|--------------------------------------------|-----------------------------------|-----|-----|-------|

| Setup time (STP, data in)                  | T <sub>SC</sub> , T <sub>SD</sub> | 5.0 |     | nS    |

| Hold time (STP, data in)                   | T <sub>HC</sub> , T <sub>HD</sub> | 0.0 |     | nS    |

| Output delay (control out, 8-bit data out) | T <sub>DC</sub> , T <sub>DD</sub> | 1.5 | 3.5 | nS    |

### Table 4.3 ULPI Interface Timing

Note:  $V_{DDIO}$  = 1.6 to 3.6V;  $V_{SS}$  = 0V;  $T_A$  = -40C to 85C;  $C_{Load}$  = 10pF

# 4.4 Digital IO Pins

#### Table 4.4 Digital IO Characteristics: RESETB, CLKOUT, STP, DIR, NXT, DATA[7:0] and XI Pins

| PARAMETER                               | SYMBOL            | CONDITIONS             | MIN                         | TYP                     | MAX                        | UNITS |

|-----------------------------------------|-------------------|------------------------|-----------------------------|-------------------------|----------------------------|-------|

| Low-Level Input Voltage                 | V <sub>IL</sub>   |                        | V <sub>SS</sub>             |                         | 0.4 *<br>V <sub>DDIO</sub> | V     |

| High-Level Input Voltage                | V <sub>IH</sub>   |                        | 0.68 *<br>V <sub>DDIO</sub> |                         | V <sub>DDIO</sub>          | V     |

| High-Level Input Voltage<br>REFCLK only | V <sub>IH</sub>   |                        | 0.68 *<br>V <sub>DD18</sub> |                         | V <sub>DD33</sub>          | V     |

| Clock High<br>REFCLK only               | T <sub>HIGH</sub> |                        | 0.3 *<br>T <sub>P</sub>     | 0.5 *<br>T <sub>P</sub> | 0.7 * T <sub>P</sub>       |       |

| Clock Low<br>REFCLK only                | T <sub>LOW</sub>  |                        | 0.3 *<br>T <sub>P</sub>     | 0.5 *<br>T <sub>P</sub> | 0.7 * T <sub>P</sub>       |       |

| Low-Level Output Voltage                | V <sub>OL</sub>   | I <sub>OL</sub> = 8mA  |                             |                         | 0.4                        | V     |

| High-Level Output Voltage               | V <sub>OH</sub>   | I <sub>OH</sub> = -8mA | V <sub>DDIO</sub> -<br>0.4  |                         |                            | V     |

| High-Level Output Voltage CPEN Only     | V <sub>OH</sub>   | I <sub>OH</sub> = -8mA | V <sub>DD33</sub><br>- 0.4  |                         |                            | V     |

| Input Leakage Current                   | ILI               |                        |                             |                         | ±10                        | uA    |

| Pin Capacitance                         | Cpin              |                        |                             |                         | 4                          | pF    |

Table 4.4 Digital IO Characteristics: RESETB, CLKOUT, STP, DIR, NXT, DATA[7:0] and XI Pins (continued)

| PARAMETER                    | SYMBOL               | CONDITIONS                     | MIN | ТҮР | MAX                        | UNITS |

|------------------------------|----------------------|--------------------------------|-----|-----|----------------------------|-------|

| STP pull-up resistance       | R <sub>STP</sub>     | InterfaceProtectDisable = 0    | 51  | 60  | 65                         | kΩ    |

| DATA[7:0] pull-dn resistance | R <sub>DATA_PD</sub> | ULPI Synchronous Mode          | 55  | 67  | 79                         | kΩ    |

| CLKOUT External Drive        | V <sub>IH_ED</sub>   | At start-up or following reset |     |     | 0.4 *<br>V <sub>DDIO</sub> | V     |

Figure 4.1 External Reference Clock

# 4.5 DC Characteristics: Analog I/O Pins

| Table 4.5 | <b>DC Characteristics:</b> | Analog I/O Pins | (DP/DM) |

|-----------|----------------------------|-----------------|---------|

|-----------|----------------------------|-----------------|---------|

| PARAMETER                                         | SYMBOL             | CONDITIONS                                                                    | MIN   | TYP  | MAX   | UNITS |

|---------------------------------------------------|--------------------|-------------------------------------------------------------------------------|-------|------|-------|-------|

| LS/FS FUNCTIONALITY                               |                    |                                                                               |       |      |       |       |

| Input levels                                      |                    |                                                                               |       |      |       |       |

| Differential Receiver Input<br>Sensitivity        | V <sub>DIFS</sub>  | V(DP) - V(DM)                                                                 | 0.2   |      |       | V     |

| Differential Receiver<br>Common-Mode Voltage      | V <sub>CMFS</sub>  |                                                                               | 0.8   |      | 2.5   | V     |

| Single-Ended Receiver Low<br>Level Input Voltage  | V <sub>ILSE</sub>  | Note 4.5                                                                      |       |      | 0.8   | V     |

| Single-Ended Receiver High<br>Level Input Voltage | V <sub>IHSE</sub>  | Note 4.5                                                                      | 2.0   |      |       | V     |

| Single-Ended Receiver<br>Hysteresis               | V <sub>HYSSE</sub> |                                                                               | 0.050 |      | 0.150 | V     |

| Output Levels                                     |                    |                                                                               |       |      |       |       |

| Low Level Output Voltage                          | V <sub>FSOL</sub>  | Pull-up resistor on DP;<br>R <sub>L</sub> = $1.5k\Omega$ to V <sub>DD33</sub> |       |      | 0.3   | V     |

| High Level Output Voltage                         | V <sub>FSOH</sub>  | Pull-down resistor on DP,<br>DM; Note 4.5<br>$R_L = 15k\Omega$ to GND         | 2.8   |      | 3.6   | V     |

| Termination                                       |                    |                                                                               |       |      |       |       |

| Driver Output Impedance for<br>HS and FS          | Z <sub>HSDRV</sub> | Steady state drive                                                            | 40.5  | 45   | 49.5  | Ω     |

| Input Impedance                                   | Z <sub>INP</sub>   | RX, RPU, RPD disabled                                                         | 1.0   |      |       | MΩ    |

| Pull-up Resistor Impedance                        | R <sub>PU</sub>    | Bus Idle, Note 4.4                                                            | 0.900 | 1.24 | 1.575 | kΩ    |

| PARAMETER                                                                    | SYMBOL              | CONDITIONS                                                                    | MIN   | ТҮР  | MAX  | UNITS |

|------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------|-------|------|------|-------|

| Pull-up Resistor Impedance                                                   | R <sub>PU</sub>     | Device Receiving,<br>Note 4.4                                                 | 1.425 | 2.26 | 3.09 | kΩ    |

| Pull-dn Resistor Impedance                                                   | R <sub>PD</sub>     | Note 4.4                                                                      | 14.25 | 16.9 | 20   | kΩ    |

| Weak Pull-up Resistor<br>Impedance                                           | R <sub>CD</sub>     | Configured by bits 4 and 5<br>in USB IO & Power<br>Management register.       | 128   | 170  | 212  | kΩ    |

| HS FUNCTIONALITY                                                             |                     |                                                                               |       |      |      |       |

| Input levels                                                                 |                     |                                                                               |       |      |      |       |

| HS Differential Input<br>Sensitivity                                         | V <sub>DIHS</sub>   | V(DP) - V(DM)                                                                 | 100   |      |      | mV    |

| HS Data Signaling Common<br>Mode Voltage Range                               | V <sub>CMHS</sub>   |                                                                               | -50   |      | 500  | mV    |

| High-Speed Squelch<br>Detection Threshold<br>(Differential Signal Amplitude) | V <sub>HSSQ</sub>   | Note 4.6                                                                      | 100   |      | 150  | mV    |

| Output Levels                                                                |                     |                                                                               |       |      |      |       |

| Hi-Speed Low Level<br>Output Voltage (DP/DM<br>referenced to GND)            | V <sub>HSOL</sub>   | 45Ω load                                                                      | -10   |      | 10   | mV    |

| Hi-Speed High Level<br>Output Voltage (DP/DM<br>referenced to GND)           | V <sub>HSOH</sub>   | 45Ω load                                                                      | 360   |      | 440  | mV    |

| Hi-Speed IDLE Level<br>Output Voltage (DP/DM<br>referenced to GND)           | V <sub>OLHS</sub>   | 45Ω load                                                                      | -10   |      | 10   | mV    |

| Chirp-J Output Voltage<br>(Differential)                                     | V <sub>CHIRPJ</sub> | HS termination resistor<br>disabled, pull-up resistor<br>connected. 45Ω load. | 700   |      | 1100 | mV    |

| Chirp-K Output Voltage<br>(Differential)                                     | V <sub>CHIRPK</sub> | HS termination resistor<br>disabled, pull-up resistor<br>connected. 45Ω load. | -900  |      | -500 | mV    |

| Leakage Current                                                              |                     |                                                                               |       |      |      |       |

| OFF-State Leakage Current                                                    | I <sub>LZ</sub>     |                                                                               |       |      | ±10  | uA    |

| Port Capacitance                                                             |                     |                                                                               |       |      |      |       |

| Transceiver Input<br>Capacitance                                             | C <sub>IN</sub>     | Pin to GND                                                                    |       | 5    | 10   | pF    |

Note 4.4 The resistor value follows the 27% Resistor ECN published by the USB-IF.

- **Note 4.5** The values shown are valid when the *USB RegOutput* bits in the USB IO & Power Management register are set to the default value.

- **Note 4.6** An automatic waiver up to 200mV is granted to accommodate system-level elements such as measurement/test fixtures, captive cables, EMI components, and ESD suppression.

# 4.6 Dynamic Characteristics: Analog I/O Pins

| PARAMETER                                           | SYMBOL            | CONDITIONS                                                                       | MIN | TYP | MAX   | UNITS |

|-----------------------------------------------------|-------------------|----------------------------------------------------------------------------------|-----|-----|-------|-------|

| FS Output Driver Timing                             |                   |                                                                                  |     |     |       |       |

| FS Rise Time                                        | T <sub>FR</sub>   | $C_{L}$ = 50pF; 10 to 90% of $ V_{OH} - V_{OL} $                                 | 4   |     | 20    | ns    |

| FS Fall Time                                        | T <sub>FF</sub>   | $C_{L}$ = 50pF; 10 to 90% of $ V_{OH} - V_{OL} $                                 | 4   |     | 20    | ns    |

| Output Signal Crossover<br>Voltage                  | V <sub>CRS</sub>  | Excluding the first transition from IDLE state                                   | 1.3 |     | 2.0   | V     |

| Differential Rise/Fall Time<br>Matching             | T <sub>FRFM</sub> | Excluding the first transition from IDLE state                                   | 90  |     | 111.1 | %     |

| LS Output Driver Timing                             |                   |                                                                                  |     |     |       |       |

| LS Rise Time                                        | T <sub>LR</sub>   | C <sub>L</sub> = 50-600рF;<br>10 to 90% of<br> V <sub>OH</sub> - V <sub>OL</sub> | 75  |     | 300   | ns    |

| LS Fall Time                                        | T <sub>LF</sub>   | C <sub>L</sub> = 50-600pF;<br>10 to 90% of<br> V <sub>OH</sub> - V <sub>OL</sub> | 75  |     | 300   | ns    |

| Differential Rise/Fall Time<br>Matching             | T <sub>LRFM</sub> | Excluding the first transition from IDLE state                                   | 80  |     | 125   | %     |

| HS Output Driver Timing                             |                   |                                                                                  |     |     |       |       |

| Differential Rise Time                              | T <sub>HSR</sub>  |                                                                                  | 500 |     |       | ps    |

| Differential Fall Time                              | T <sub>HSF</sub>  |                                                                                  | 500 |     |       | ps    |

| Driver Waveform<br>Requirements                     |                   | Eye pattern of Template 1<br>in USB 2.0 specification                            |     |     |       |       |

| Hi-Speed Mode Timing                                |                   |                                                                                  |     |     |       |       |

| Receiver Waveform<br>Requirements                   |                   | Eye pattern of Template 4<br>in USB 2.0 specification                            |     |     |       |       |

| Data Source Jitter and<br>Receiver Jitter Tolerance |                   | Eye pattern of Template 4<br>in USB 2.0 specification                            |     |     |       |       |

### Table 4.6 Dynamic Characteristics: Analog I/O Pins (DP/DM)

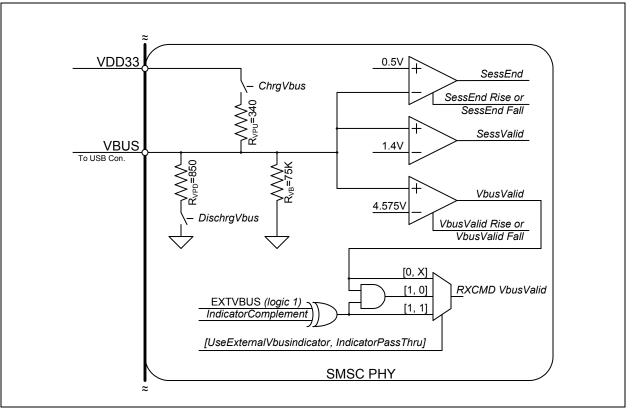

# 4.7 OTG Electrical Characteristics

|  | Table 4.7 | OTG | Electrical | Characteristics |

|--|-----------|-----|------------|-----------------|

|--|-----------|-----|------------|-----------------|

| PARAMETER           | SYMBOL               | CONDITIONS                                                  | MIN | TYP  | MAX  | UNITS |

|---------------------|----------------------|-------------------------------------------------------------|-----|------|------|-------|

| SessEnd trip point  | V <sub>SessEnd</sub> |                                                             | 0.2 | 0.5  | 0.8  | V     |

| SessVId trip point  | V <sub>SessVld</sub> |                                                             | 0.8 | 1.4  | 2.0  | V     |

| VbusVld trip point  | V <sub>VbusVld</sub> |                                                             | 4.4 | 4.58 | 4.75 | V     |

| A-Device Impedance  | R <sub>ldGnd</sub>   | Maximum A device<br>Impedance to ground on <b>ID</b><br>pin |     |      | 100  | kΩ    |

| ID Float trip point | V <sub>IdFloat</sub> |                                                             | 1.9 | 2.2  | 2.5  | V     |

| Vbus Pull-Up        | R <sub>VPU</sub>     | VBUS to VDD33<br>(ChargeVbus = 1)                           | 281 | 340  | 450  | Ω     |

| Table 4.7 | <b>OTG Electrical Characteristics</b> | (continued) | ) |

|-----------|---------------------------------------|-------------|---|

|           |                                       |             |   |

| PARAMETER                  | SYMBOL            | CONDITIONS                         | MIN | ТҮР | MAX  | UNITS |

|----------------------------|-------------------|------------------------------------|-----|-----|------|-------|

| Vbus Pull-down             | R <sub>VPD</sub>  | VBUS to GND<br>(DisChargeVbus = 1) | 656 | 850 | 1100 | Ω     |

| Vbus Impedance             | R <sub>VB</sub>   | VBUS to GND                        | 40  | 75  | 100  | kΩ    |

| ID pull-up resistance      | R <sub>ID</sub>   | IdPullup = 1                       | 80  | 100 | 120  | kΩ    |

| ID weak pull-up resistance | R <sub>IDW</sub>  | IdPullup = 0                       | 1   |     |      | MΩ    |

| ID pull-dn resistance      | R <sub>IDPD</sub> | ldGndDrv = 1                       |     |     | 1000 | Ω     |

# 4.8 Regulator Output Voltages and Capacitor Requirement

| PARAMETER                  | SYMBOL            | CONDITIONS                                                      | MIN  | TYP  | MAX  | UNITS |

|----------------------------|-------------------|-----------------------------------------------------------------|------|------|------|-------|

| Regulator Output Voltage   | V <sub>DD33</sub> | 6V > VBAT > 3.1V                                                | 3.0  | 3.3  | 3.6  | V     |

| Regulator Output Voltage   | V <sub>DD33</sub> | USB UART Mode & UART<br>RegOutput[1:0] = 01<br>6V > VBAT > 3.1V | 2.7  | 3.0  | 3.3  | V     |

| Regulator Output Voltage   | V <sub>DD33</sub> | USB UART Mode & UART<br>RegOutput[1:0] = 10<br>6V > VBAT > 3.1V | 2.47 | 2.75 | 3.03 | V     |

| Regulator Output Voltage   | V <sub>DD33</sub> | USB UART Mode & UART<br>RegOutput[1:0] = 11<br>6V > VBAT > 3.1V | 2.25 | 2.5  | 2.75 | V     |

| Regulator Bypass Capacitor | C <sub>BYP</sub>  |                                                                 | 2.2  |      |      | uF    |

| Bypass Capacitor ESR       | C <sub>ESR</sub>  |                                                                 |      |      | 1    | Ω     |

Table 4.8 Regulator Output Voltages and Capacitor Requirement

#### Table 4.9 ESD and LATCH-UP Performance

| PARAMETER            | CONDITIONS                            |  | TYP | MAX | UNITS | COMMENTS              |  |  |

|----------------------|---------------------------------------|--|-----|-----|-------|-----------------------|--|--|

|                      | ESD PERFORMANCE                       |  |     |     |       |                       |  |  |

| Note 4.7             | Human Body Model                      |  |     | ±8  | kV    | Device                |  |  |

| System               | EN/IEC 61000-4-2 Contact<br>Discharge |  |     | ±8  | kV    | 3rd party system test |  |  |

| System               | EN/IEC 61000-4-2 Air-gap<br>Discharge |  |     | ±15 | kV    | 3rd party system test |  |  |

| LATCH-UP PERFORMANCE |                                       |  |     |     |       |                       |  |  |

| All Pins             | EIA/JESD 78, Class II                 |  | 150 |     | mA    |                       |  |  |

Note 4.7 REFCLK pin ±5kV Human Body Model.

# **Chapter 5 Architecture Overview**

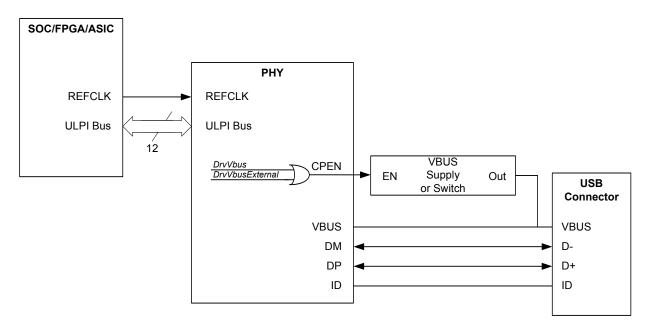

The USB3315 consists of the blocks shown in the diagram below. All pull-up resistors shown in Figure 5.1 are connected to VDD33.

Figure 5.1 USB3315 System Diagram

# 5.1 ULPI Digital Operation and Interface

This section of the USB3315 is covered in detail in Chapter 6, ULPI Operation Overview.

## 5.2 Interface to DP/DM

The blocks in the lower left-hand corner of Figure 5.1 interface to the DP/DM pins.

## 5.2.1 USB Transceiver

The USB3315 transceiver includes the receivers and transmitters required to be compliant to the Universal Serial Bus Specification Rev 2.0. The DP/DM signals in the USB cable connect directly to the receivers and transmitters.

The RX block consists of separate differential receivers for HS and FS/LS mode. Depending on the mode, the selected receiver provides the serial data stream through the multiplexer to the RX Logic block. For HS mode support, the HS RX block contains a squelch circuit to insure that noise is not interpreted as data. The RX block also includes a single-ended receiver on each of the data lines to determine the correct FS linestate.

Data from the TX Logic block is encoded, bit stuffed, serialized and transmitted onto the USB cable by the TX block. Separate differential FS/LS and HS transmitters are included to support all modes.

The USB3315 TX block meets the HS signalling level requirements in the USB 2.0 Specification when the PCB traces from the **DP** and **DM** pins to the USB connector have very little loss. In some systems, it may be desirable to compensate for loss by adjusting the HS transmitter amplitude. The *Boost* bits in the HS TX Boost register may be configured to adjust the HS transmitter amplitude at the **DP** and **DM** pins.

## 5.2.2 Termination Resistors

The USB3315 transceiver fully integrates all of the USB termination resistors on both **DP** and **DM**. This includes  $1.5k\Omega$  pull-up resistors,  $15k\Omega$  pull-down resistors and the  $45\Omega$  high speed termination resistors. These resistors require no tuning or trimming by the Link. The state of the resistors is determined by the operating mode of the PHY when operating in synchronous mode.

The *XcvrSelect*[1:0], *TermSelect* and *OpMode*[1:0] bits in the Function Control register, and the *DpPulldown* and *DmPulldown* bits in the OTG Control register control the configuration. The possible valid resistor combinations are shown in Table 5.1, and operation is guaranteed in only the configurations shown. If a ULPI Register Setting is configured that does not match a setting in the table, the transceiver operation is not guaranteed and the settings in the last row of Table 5.1 will be used.

- RPU\_DP\_EN activates the 1.5kΩ DP pull-up resistor

- RPU\_DM\_EN activates the 1.5kΩ DM pull-up resistor

- RPD\_DP\_EN activates the 15kΩ DP pull-down resistor

- RPD\_DM\_EN activates the 15kΩ DM pull-down resistor

- HSTERM\_EN activates the 45Ω DP and DM high speed termination resistors

The USB3315 also includes two  $125k\Omega$  DP and DM pull-up resistors described in Section 5.8.

|                                         | ULP             | ULPI REGISTER SETTINGS |             |            | USB3315 TERMINATION<br>RESISTOR SETTINGS |           |           |           |           |           |

|-----------------------------------------|-----------------|------------------------|-------------|------------|------------------------------------------|-----------|-----------|-----------|-----------|-----------|

| SIGNALING MODE                          | XCVRSELECT[1:0] | TERMSELECT             | OPMODE[1:0] | DPPULLDOWN | DMPULLDOWN                               | RPU_DP_EN | RPU_DM_EN | RPD_DP_EN | RPD_DM_EN | HSTERM_EN |

| General Settings                        |                 |                        |             |            |                                          |           |           |           |           |           |

| Tri-State Drivers                       | XXb             | Xb                     | 01b         | Xb         | Xb                                       | 0b        | 0b        | 0b        | 0b        | 0b        |

| Power-up or Vbus < V <sub>SESSEND</sub> | 01b             | 0b                     | 00b         | 1b         | 1b                                       | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host Settings                           |                 |                        |             |            |                                          |           |           |           |           |           |

| Host Chirp                              | 00b             | 0b                     | 10b         | 1b         | 1b                                       | 0b        | 0b        | 1b        | 1b        | 1b        |

| Host Hi-Speed                           | 00b             | 0b                     | 00b         | 1b         | 1b                                       | 0b        | 0b        | 1b        | 1b        | 1b        |

| Host Full Speed                         | X1b             | 1b                     | 00b         | 1b         | 1b                                       | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host HS/FS Suspend                      | 01b             | 1b                     | 00b         | 1b         | 1b                                       | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host HS/FS Resume                       | 01b             | 1b                     | 10b         | 1b         | 1b                                       | 0b        | 0b        | 1b        | 1b        | 0b        |

|                                            | ULPI REGISTER SETTINGS |            |             | USB3315 TERMINATION<br>RESISTOR SETTINGS |            |           |           |           |           |           |

|--------------------------------------------|------------------------|------------|-------------|------------------------------------------|------------|-----------|-----------|-----------|-----------|-----------|

| SIGNALING MODE                             | XCVRSELECT[1:0]        | TERMSELECT | OPMODE[1:0] | DPPULLDOWN                               | DMPULLDOWN | RPU_DP_EN | RPU_DM_EN | RPD_DP_EN | RPD_DM_EN | HSTERM_EN |

| Host low Speed                             | 10b                    | 1b         | 00b         | 1b                                       | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host LS Suspend                            | 10b                    | 1b         | 00b         | 1b                                       | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host LS Resume                             | 10b                    | 1b         | 10b         | 1b                                       | 1b         | 0b        | 0b        | 1b        | 1b        | 0b        |

| Host Test J/Test_K                         | 00b                    | 0b         | 10b         | 1b                                       | 1b         | 0b        | 0b        | 1b        | 1b        | 1b        |

| Peripheral Settings                        |                        |            |             |                                          |            |           |           |           |           |           |

| Peripheral Chirp                           | 00b                    | 1b         | 10b         | 0b                                       | 0b         | 1b        | 0b        | 0b        | 0b        | 0b        |

| Peripheral HS                              | 00b                    | 0b         | 00b         | 0b                                       | 0b         | 0b        | 0b        | 0b        | 0b        | 1b        |

| Peripheral FS                              | 01b                    | 1b         | 00b         | 0b                                       | 0b         | 1b        | 0b        | 0b        | 0b        | 0b        |

| Peripheral HS/FS Suspend                   | 01b                    | 1b         | 00b         | 0b                                       | 0b         | 1b        | 0b        | 0b        | 0b        | 0b        |

| Peripheral HS/FS Resume                    | 01b                    | 1b         | 10b         | 0b                                       | 0b         | 1b        | 0b        | 0b        | 0b        | 0b        |

| Peripheral LS                              | 10b                    | 1b         | 00b         | 0b                                       | 0b         | 0b        | 1b        | 0b        | 0b        | 0b        |

| Peripheral LS Suspend                      | 10b                    | 1b         | 00b         | 0b                                       | 0b         | 0b        | 1b        | 0b        | 0b        | 0b        |

| Peripheral LS Resume                       | 10b                    | 1b         | 10b         | 0b                                       | 0b         | 0b        | 1b        | 0b        | 0b        | 0b        |

| Peripheral Test J/Test K                   | 00b                    | 0b         | 10b         | 0b                                       | 0b         | 0b        | 0b        | 0b        | 0b        | 1b        |

| OTG device, Peripheral Chirp               | 00b                    | 1b         | 10b         | 0b                                       | 1b         | 1b        | 0b        | 0b        | 1b        | 0b        |

| OTG device, Peripheral HS                  | 00b                    | 0b         | 00b         | 0b                                       | 1b         | 0b        | 0b        | 0b        | 1b        | 1b        |

| OTG device, Peripheral FS                  | 01b                    | 1b         | 00b         | 0b                                       | 1b         | 1b        | 0b        | 0b        | 1b        | 0b        |

| OTG device, Peripheral HS/FS Suspend       | 01b                    | 1b         | 00b         | 0b                                       | 1b         | 1b        | 0b        | 0b        | 1b        | 0b        |

| OTG device, Peripheral HS/FS Resume        | 01b                    | 1b         | 10b         | 0b                                       | 1b         | 1b        | 0b        | 0b        | 1b        | 0b        |

| OTG device, Peripheral Test J/Test K       | 00b                    | 0b         | 10b         | 0b                                       | 1b         | 0b        | 0b        | 0b        | 1b        | 1b        |

| Any combination not defined above Note 5.1 |                        |            |             |                                          |            | 0b        | 0b        | 0b        | 0b        | 0b        |

| Table 5.1 DP/DM Termination vs. Sign | naling Mode (continued) |

|--------------------------------------|-------------------------|

|--------------------------------------|-------------------------|

Note: This is the same as Table 40, Section 4.4 of the ULPI 1.1 specification.

Note: USB3315 does not support operation as an upstream hub port. See Section 6.2.4.3.

**Note 5.1** The transceiver operation is not guaranteed in a combination that is not defined.

The USB3315 uses the 27% resistor ECN resistor tolerances. The resistor values are shown in Table 4.5.

## 5.3 Bias Generator

This block consists of an internal bandgap reference circuit used for generating the driver current and the biasing of the analog circuits. This block requires an external 8.06K $\Omega$ , 1% tolerance, reference resistor connected from **RBIAS** to ground. This resistor should be placed as close as possible to the USB3315 to minimize the trace length. The nominal voltage at **RBIAS** is 0.8V and therefore the resistor will dissipate approximately 80 $\mu$ W of power.

## 5.4 Integrated Low Jitter PLL

The USB3315 uses an integrated low jitter phase locked loop (PLL) to provide a clean 480MHz clock. This clock is used by the PHY during both transmit and receive. The USB3315 requires a 24MHz reference clock to be driven on the **REFCLK** pin.

After the PLL has locked to the correct frequency, the USB3315 will de-assert **DIR** and the Link can begin using the ULPI interface. The USB3315 is guaranteed to start the clock within the time specified in Table 4.2. For Host applications, the ULPI *AutoResume* bit should be enabled. This is described in Section 6.2.4.4.

The system must not drive voltage on the CLKOUT pin following POR or hardware reset that exceeds the value of  $V_{IH\ ED}$  provided in Table 4.4.

## 5.4.1 Reference Clock Requirements

The reference clock is connected to the REFCLK pins as shown in the application diagram, Figure 8.1. The REFCLK pin is designed to be driven with a square wave from 0V to  $V_{DDIO}$ , but can be driven with a square wave from 0V to as high as 3.6V.

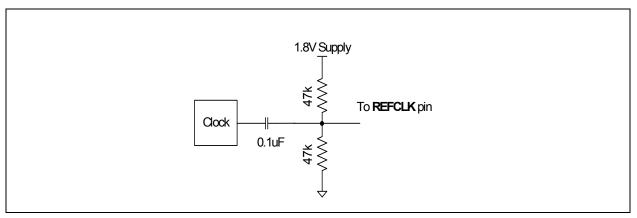

When using an external reference clock, the USB3315 only uses the positive edge of the clock. The signal must comply with the V<sub>IH</sub> and V<sub>IL</sub> parameters provided in Table 4.4. It may be possible to AC couple the reference clock to change the common-mode voltage level when it is sourced by a device that does not comply with the V<sub>IH</sub> and V<sub>IL</sub> parameters. A DC bias network must be provided at the REFCLK pin when the reference clock is AC coupled. The component values provided in Figure 5.2 are for example only. The actual values should be selected to satisfy system requirements.

Figure 5.2 Example of circuit used to shift a reference clock common-mode voltage level.

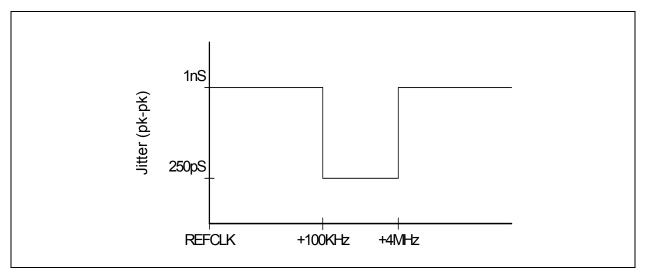

The jitter of the reference clock at certain frequencies can directly affect the HS eye diagram. The USB3315 is tolerant to reference clock jitter below 100Khz and jitter above 4MHz. If the REFCLK

contains jitter in the 100KHz to 4MHz band the peak to peak amplitude of this jitter should be limited to 250pS peak to peak. This requirement is illustrated in Figure 5.3 below.

Figure 5.3 USB3315 Allowable REFCLK Jitter vs. Frequency

The edges of the reference clock do not need to be aligned in any way to the ULPI interface signals. The reference clock is used by a PLL to generate the 60MHz CLKOUT for the ULPI digital. There is no need to align the phase of the REFCLK and the 60MHz CLKOUT.

The REFCLK should be enabled when the RESETB pin is brought high. The ULPI interface will start running after the time specified in Table 4.2. If the REFCLK enable is delayed relative to the RESETB pin, the ULPI interface will start operation delayed by the same amount. The REFCLK can be run at anytime the RESETB pin is low without causing the USB3315 to start-up or draw current.

When the USB3315 is placed in Low Power Mode or carkit mode the REFCLK can be stopped after the final ULPI register write is complete. The STP pin is asserted to bring the USB3315 out of Low Power Mode. The REFCLK should be started at the same time STP is asserted to minimize the USB3315 start-up time.