# UCS1002-1

# Programmable USB Port Power Controller with Charger Emulation

### PRODUCT FEATURES

Datasheet

### **General Description**

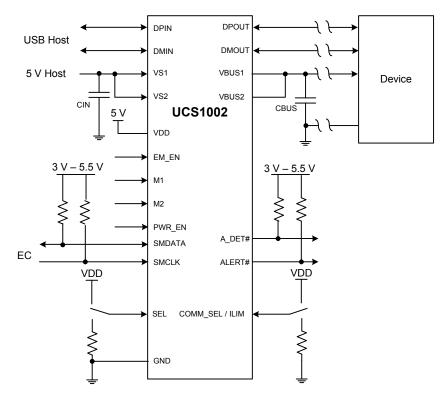

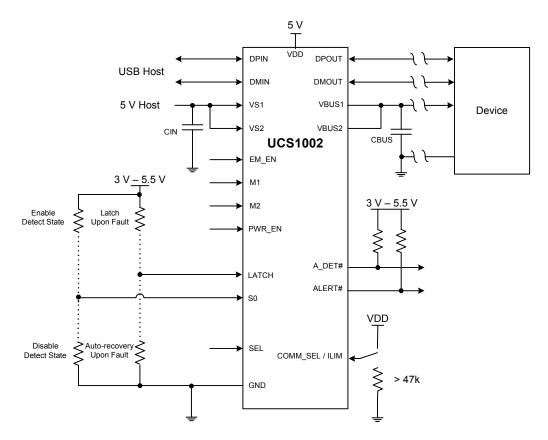

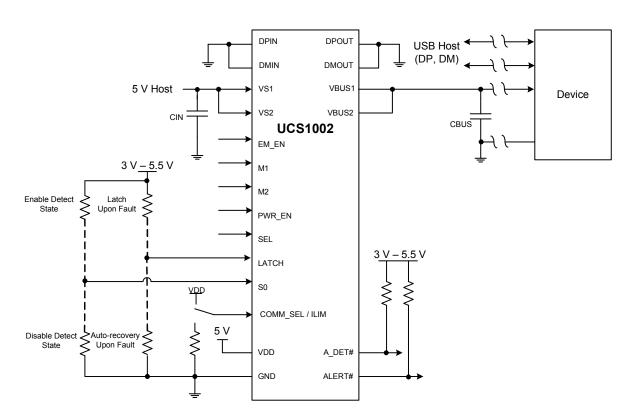

The UCS1002 provides a USB port power switch for precise control of up to 2.5 amperes continuous current with over-current limit (OCL), dynamic thermal management, latch or auto-recovery (low test current) fault handling, selectable active low or high enable, under- and over-voltage lockout, back-drive protection, and back-voltage protection.

Split supply support for VS and VDD is an option for low power in system standby states. This gives battery operated applications, like notebook PCs, the ability to detect attachments from a sleep or off state. After the Attach Detection is flagged, the system can decide to wake up and/or provide charging.

In addition to power switching and current limiting modes, the UCS1002 will automatically charge a wide variety of portable devices, including USB-IF BC1.2, YD/T-1591 (2009), most Apple<sup>®</sup> and RIM<sup>®</sup>, and many others. Nine preloaded charger emulation profiles maximize compatibility coverage of peripheral devices.

As well, a customizable charger emulation profile is available to accommodate unique existing and future portable device handshaking / signature requirements. This custom profile uses a unique stimulus and response method referenced below.\*

The UCS1002 also provides current monitoring to allow intelligent management of system power and a Battery Full option for controlled delivery of current regardless of the host power state. This is especially important for battery operated applications that want to provide power in a standby and/or off state but do not want to drain the battery excessively.

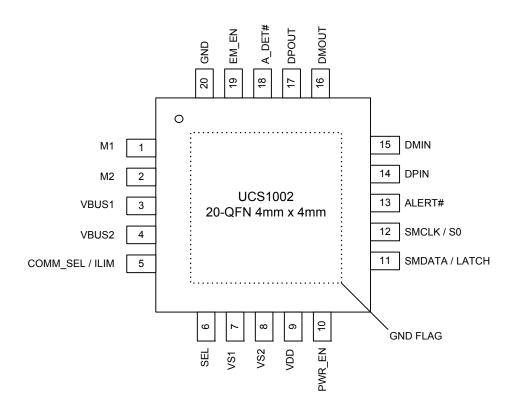

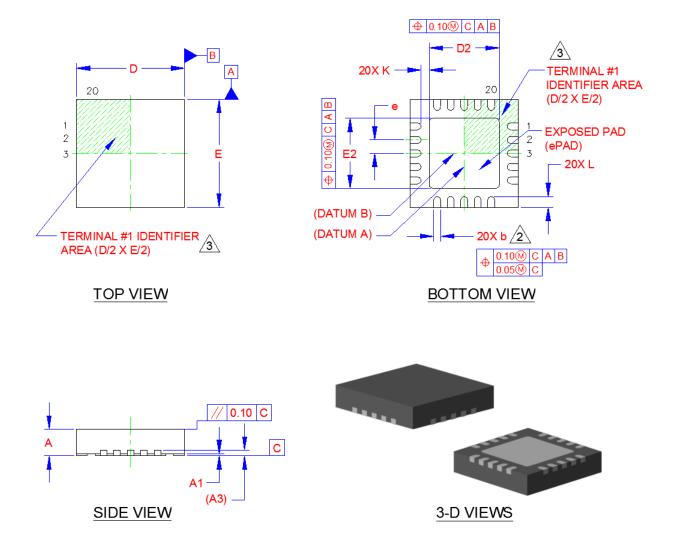

The UCS1002 is available in a 20-pin QFN 4 mm x 4 mm package.

#### **Applications**

- Notebook and Netbook Computers

- Tablets and E-book readers

- Desktops and Monitors

- Docking Stations and Printers

- AC-DC wall adapters

#### Features

- Port power switch with two current limit behaviors

- 2.9 V to 5.5 V source voltage range

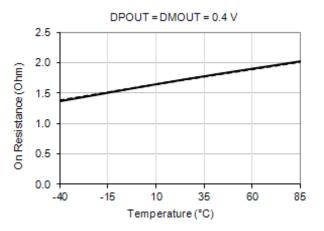

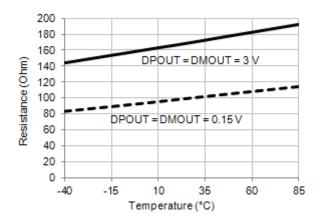

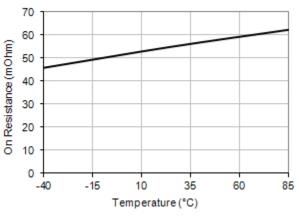

- Up to 2.5 A current with 55 m $\Omega$  On Resistance

- Over-current trip or constant current limiting

- Soft turn-on circuitry

- Programmable current limit

- Dynamic thermal management

- Under- and over-voltage lockout

- Back-drive, back-voltage protection

- Latch or auto-recovery (low test current) fault handling

- Selectable active high or low power switch enable

- BC1.2 VBUS discharge port renegotiation function

- Selectable / automatic cycling of USB data line charger emulation profiles

- Customizable emulation profile uses a unique stimulus and response method useful for future profiles\*

- Supports charger emulation

- Allows for active cables

- USB-IF BC1.2 charging downstream port (CDP) & dedicated charging port (DCP) modes, YD/T-1591, and most Apple and RIM protocols standard; others as defined via the SMBus 2.0 / I<sup>2</sup>C<sup>®</sup>

- USB 2.0 compliant high-speed data switch (in Passthrough and CDP modes)

- Nine preloaded charger emulation profiles for maximum compatibility coverage of peripheral devices

- One custom programmable charger emulation profile for portable device support for fully host controlled charger emulation

- Fault Alert open-drain output

- Self-contained current monitoring

- Low power Attach Detection and open-drain A\_DET# pin

- Ultra low power Sleep state

- Optional split supply support for VBUS and VDD for low power in system standby states

- Wake on Attach USB

- SMBus 2.0 / I<sup>2</sup>C communications

Supports Block Write and Read

Multiple SMBus addresses

- Wide operating temperature range: -40 °C to +85 °C

- IEC61000-4-2 8 / 15 kV ESD immunity

- UL recognized and EN/IEC 60950-1 (CB) certified

\* Unique technology covered under the following US patents pending: 13/109,446; 13/149,529; 13/173,287; 13/233,949; 13/157,282; 12/978,371; 13/232,965.

SMSC UCS1002

### DATASHEET

Revision 1.4 (07-16-13)

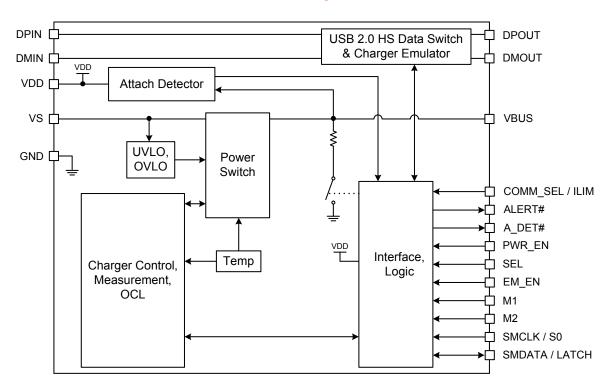

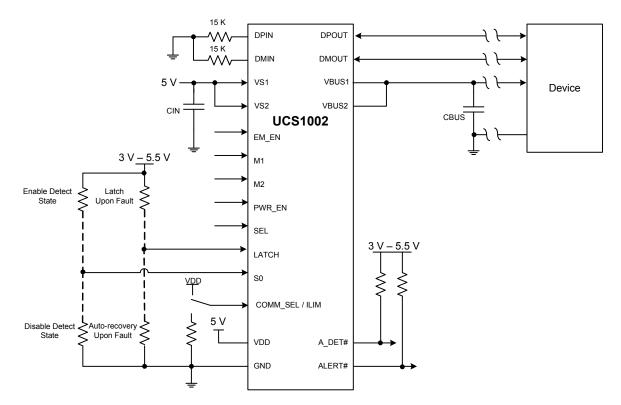

### **Block Diagram**

| ORDERING INFORMATION: |                                          |                                                                                                                                                                                 |  |

|-----------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ORDERING NUMBER       | PACKAGE                                  | FEATURES                                                                                                                                                                        |  |

| UCS1002-1-BP-TR       | 20 pin QFN 4mm x 4mm<br>(RoHS compliant) | USB Port Power Controller with Charge<br>Emulation, 10W Emulation support,<br>Attachment Detection, Current<br>Monitoring, Current Rationing, and<br>Programmable SMBus address |  |

### **REEL SIZE IS 4,000 PIECES**

This product meets the halogen maximum concentration values per IEC61249-2-21

For RoHS compliance and environmental information, please visit www.smsc.com/rohs

Please contact your SMSC sales representative for additional documentation related to this product such as application notes, anomaly sheets, and design guidelines.

Copyright © 2013 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

The Microchip name and logo, and the Microchip logo are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| Chapter 1 Terms and Abbreviations               | . 10 |

|-------------------------------------------------|------|

| Chapter 2 Pin Description                       | . 12 |

| Chapter 3 Electrical Specifications             |      |

| 3.1 ESD & Transient Performance                 |      |

| 3.1.1 Human Body Model (HBM) Performance        | . 26 |

| 3.1.2 Charged Device Model (CDM) Performance    | . 26 |

| 3.1.3 IEC61000-4-2 Performance                  | . 26 |

| Chapter 4 Communications                        | . 27 |

| 4.1 Operating Mode                              |      |

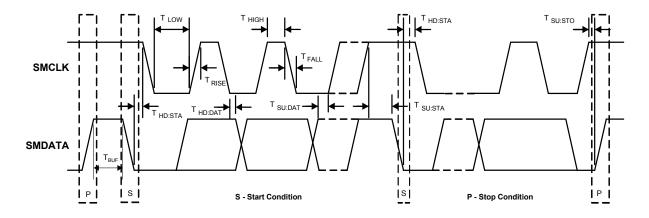

| 4.2 SMBus Operating Mode                        |      |

| 4.2.1 System Management Bus                     |      |

| 4.2.2 SMBus and I <sup>2</sup> C Compatibility  |      |

| 4.2.3 SMBus Protocols                           |      |

| 4.2.4 I <sup>2</sup> C Protocols                |      |

| 4.3 Stand-alone Operating Mode                  |      |

| Chapter 5 General Description                   | 34   |

| 5.1 UCS1002 Power States.                       | 38   |

| 5.1.1 Off State Operation                       |      |

| 5.1.2 Sleep State Operation                     |      |

| 5.1.3 Detect State Operation                    |      |

| 5.1.4 Active State Operation                    |      |

| 5.1.5 Error State Operation.                    |      |

| 5.2 Supply Voltages.                            |      |

| 5.2.1 VDD Supply Voltage                        |      |

| 5.2.2 VS Source Voltage                         |      |

| 5.2.3 Back-voltage Detection                    |      |

| 5.2.4 Back-drive Current Protection             |      |

| 5.2.5 Under-voltage Lockout on VS               |      |

| 5.2.6 Over-voltage Detection and Lockout on VS. |      |

| 5.3 Discrete Input Pins                         |      |

| 5.3.1 COMM_SEL / ILIM Input                     |      |

| 5.3.2 SEL Input                                 |      |

| 5.3.3 M1, M2, and EM_EN Inputs                  | . 45 |

| 5.3.4 PWR_EN Input                              |      |

| 5.3.5 Latch Input.                              |      |

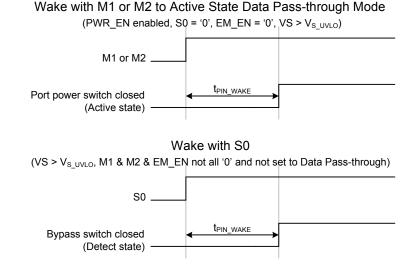

| 5.3.6 S0 Input                                  |      |

| 5.4 Discrete Output Pins                        |      |

| 5.4.1 ALERT# and A DET# Output Pins             |      |

| 5.4.2 Interrupt Blanking.                       |      |

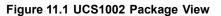

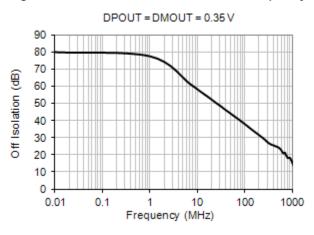

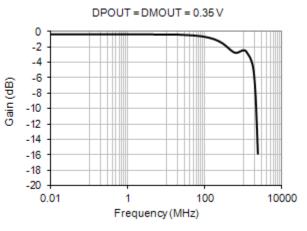

| Chapter 6 USB High-speed Data Switch            | 17   |

| 6.1 USB High-speed Data Switch                  |      |

| 6.1.1 USB-IF High-speed Compliance              |      |

|                                                 | . 47 |

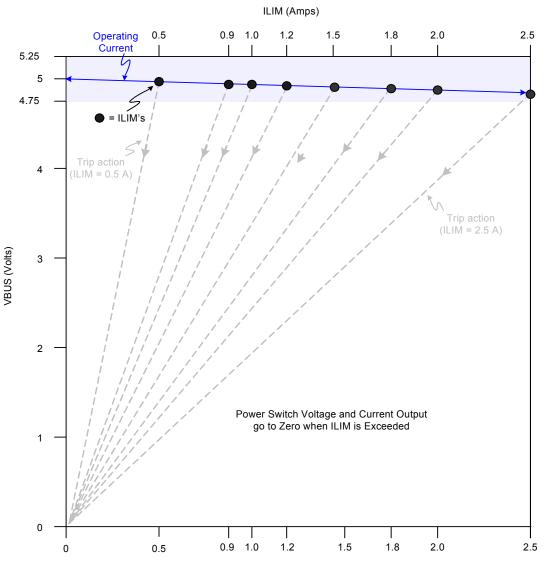

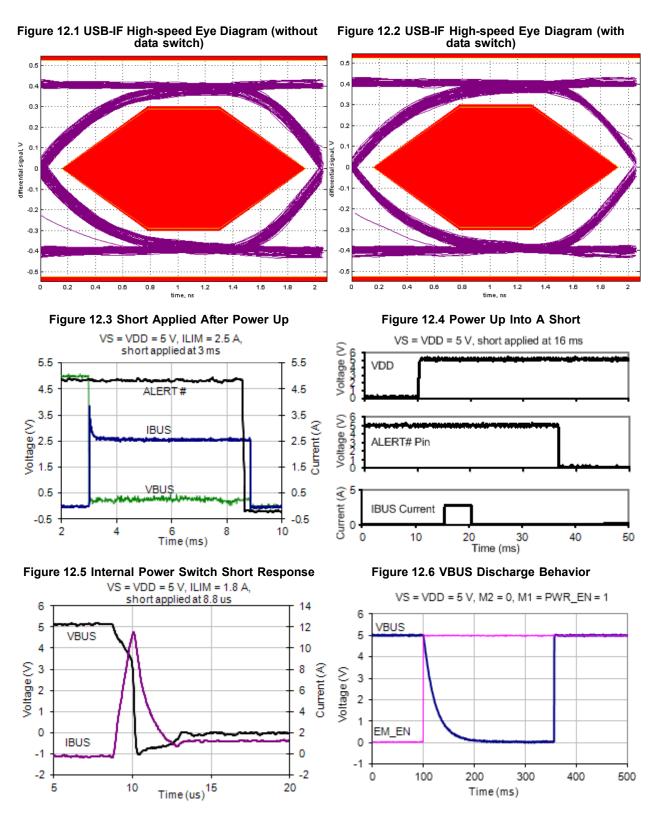

| 1 ÚŠB Port Power Switch.       48         7.2 Current Limiting.       48         7.2.1 Current Limiti Setting.       48         7.2.2 Short Circuit Output Current Limiting.       48         7.2.3 Short Start       48         7.2.4 Current Limiting Modes       48         7.3.1 Thermal Management and Voltage Protection       51         7.3.1 Thermal Management       51         7.4 VBUS Discharge       53         7.5.1 Charge Rationing Interactions.       55         7.6.1 Auto-recovery Fault Handling       57         7.6.2 Latched Fault Handling       58         8.1 Device Attach / Removal Detection       58         8.3 Attach Detect State       58         8.4 Removal Detection       58         8.3 Attach Detection       58         9.3 BC1.2 Detector State       60         9.4 Active State Overview       60         9.3 BC1.2 Detector Renge Emulation)       60         9.4 Latch / Removal Detection       58         9.5 BC1.2 SDP (No Charger Emulation Profile       61         9.6 Declacted Charger       62 <th>Chapter 7 USB Port Power Switch</th> <th>. 48</th>      | Chapter 7 USB Port Power Switch              | . 48 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------|

| 7.2.1 Current Limit Setting       48         7.2.2 Soft Start       48         7.2.3 Soft Start       48         7.3.1 Thermal Management and Voltage Protection       51         7.3.1 Thermal Management       51         7.3.5 Battery Full       53         7.5.1 Charge Rationing Interactions       55         7.5.1 Charge Rationing Interactions       55         7.6.2 Latched Fault Handling       57         7.6.2 Latched Fault Handling       57         7.6.2 Latched Fault Handling       57         7.6.2 Latched Fault Handling       56         7.6.4 Removal Detection       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Sypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         9.3 BC1.2 Detecton Renegotiation       60         9.1 Active State       60         9.3 BC1.2 Detecton Renegotiation       61         9.4 Date Pass-through (No Charger Emulation)       61         9.4 Date Pass-through (No Charger Emulation Profile       61         9.7 BC1.2 DCP Charger Emulation Profile       62         9.8.1 Emulation Reset       62                                                                |                                              |      |

| 7.2.2 Short Circuit Output Current Limiting.       48         7.2.3 Soft Start       48         7.2.4 Current Limiting Modes       48         7.3.1 hormal Management and Voltage Protection       51         7.3.1 hormal Management       51         7.4 VBUS Discharge       53         7.5 Battery Full       53         7.5.1 Charge Rationing Interactions       55         7.6 Fault Handling Mechanism       56         7.6.1 Auto-recovery Fault Handling       57         7.6.2 Latched Fault Handling       57         7.6.2 Latched Fault Handling       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       60         9.1 Active State       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation)       60         9.4 Detve Mode Selection       60         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.7 BC1.2 DCP Charger Emulation Profile       62         9.8 1 Emulation Reset       62         9.8 2 Emulation C                                                                          | 7.2 Current Limiting                         | . 48 |

| 7.2.3 Soft Start       48         7.2.4 Current Limiting Modes       48         7.3 Thermal Management and Voltage Protection       51         7.3.1 Thermal Management       51         7.4 VBUS Discharge       53         7.5 Battery Full       53         7.5 Fault Handling Mechanism       56         7.6.1 Auto-recovery Fault Handling       57         7.6.2 Latched Fault Handling       57         7.6.2 Latched Fault Handling       57         7.6.2 Latched Fault Handling       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         9.1 Active State       60         9.1 Active State Overview       60         9.1 Active State Overview       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Date Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation Profile       61         9.6 BC1.2 CDP       62         9.7 T BC1.2 DCP Charger Emulation Profile       62         9.8.1 Emulation                                                                          | 7.2.1 Current Limit Setting                  | . 48 |

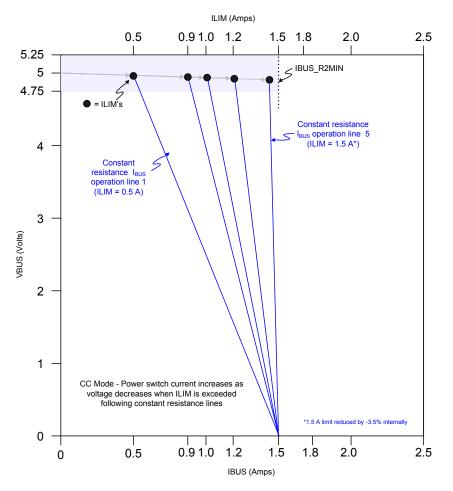

| 7.2.4 Current Limiting Modes       48         7.3 Thermal Management and Voltage Protection       51         7.4 VBUS Discharge       53         7.5 Battery Full       53         7.5 Lonarge Rationing Interactions       55         7.6 Fault Handling Mechanism       56         7.6.1 Auto-recovery Fault Handling       57         7.6.2 Latched Fault Handling       57         7.6.2 Latched Fault Handling       57         7.6.2 Latched Fault Handling       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       60         9.1 Active State       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.4 Data Pass-through (No Charger Emulation Profile       61         9.6 1 BC1.2 CDP Charger Emulation Profile       62         9.7 BC1.2 DCP Charger Emulation Profile       62         9.8 1 Emulation Reset       62         9.8 2 Emulation Cycling       6                                                | 7.2.2 Short Circuit Output Current Limiting. | . 48 |

| 7.3 Thermal Management and Voltage Protection       51         7.3 Thermal Management       51         7.4 VBUS Discharge       53         7.5 Battery Full       53         7.5 To Charge Rationing Interactions       55         7.6 Fault Handling Mechanism       56         7.6.1 Auto-recovery Fault Handling       57         7.6.2 Latched Fault Handling       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         Chapter 9 Active State       60         9.1 Active State Overview       60         9.2 Active Mode Sel                                                                          | 7.2.3 Soft Start                             | . 48 |

| 7.3.1 Thermal Management.       51         7.4 VBUS Discharge       53         7.5 Battery Full       53         7.5 Fault Handling Mechanism       56         7.6.1 Charge Rationing Interactions       56         7.6.2 Latched Fault Handling       57         Chapter 8 Detect State       58         8.1 Device Attach / Removal Detection       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.6 BC1.2 CDP       62         9.7 1 BC1.2 DCP Charger Emulation Profile       62         9.8 1 Bculation Reset       62         9.8.1 Bculation Reset       62 <td></td> <td></td>                                                                   |                                              |      |

| 7.4 VBUS Discharge       53         7.5 Battery Full       53         7.5 Charge Rationing Interactions       55         7.6 Fault Handling Mechanism       56         7.6.1 Auto-recovery Fault Handling       57         7.6.2 Latched Fault Handling       57         7.6.2 Latched Fault Handling       57         Chapter 8 Detect State       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 1 BC1.2 CDP       61         9.7 BC1.2 DCP Charger Emulation Profile       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Reset       62         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.11 DC1 2 DCP Charger Emu                                                                          |                                              |      |

| 7.5 Battery Full       53         7.5.1 Chapter Rationing Interactions       55         7.6 Fault Handling Mechanism       56         7.6.1 Auto-recovery Fault Handling       57         7.6.2 Latched Fault Handling       57         Chapter 8 Detect State       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       60         9.1 Active State       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Date Pass-through (No Charger Emulation)       61         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 1 BC1.2 CDP Charger Emulation Profile       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Reset       62         9.8.3 DCE Cycle Retry       63         9.8.3 DCE Cycle Retry       63         9.8.3 DCE Cycle Retry       63         9.9.1 Theloaded Charger Emulation Profile       64         9.                                                                          |                                              |      |

| 7.5.1 Charge Rationing Interactions       55         7.6 Fault Handling Mechanism       56         7.6.1 Auto-recovery Fault Handling       57         7.6.2 Latched Fault Handling       57         Chapter 8 Detect State       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.7 BC1.2 DCP Charger Emulation Profile       61         9.7 BC1.2 DCP       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Reset       62         9.8.3 DCE Cycle Retry       63         9.9.4 Carger Emulation Profile       65         9.1.1 BC1.2 DCP Charger Emulation Profile       65         9.1.2 Legacy 2 Charger Emulation Profile       62         9.8.1 Emulation Reset       62 <td< td=""><td>6</td><td></td></td<>                                             | 6                                            |      |

| 7.6 Fault Handling Mechanism       56         7.6.1 Auto-recovery Fault Handling       57         7.6.2 Latched Fault Handling       57         Chapter 8 Detect State       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.6 BC1.2 CDP       61         9.7 BC1.2 DCP       62         9.7 1 BC1.2 DCP Charger Emulation Profile       62         9.7 1 BC1.2 DCP Charger Emulation Profile       62         9.8 1 Emulation Reset       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.4.1 Emulation Profile       65         9.11 Preloaded Charger Emulation Profile       65         9.11 Preloaded Charger Emulation Profil                                                                          |                                              |      |

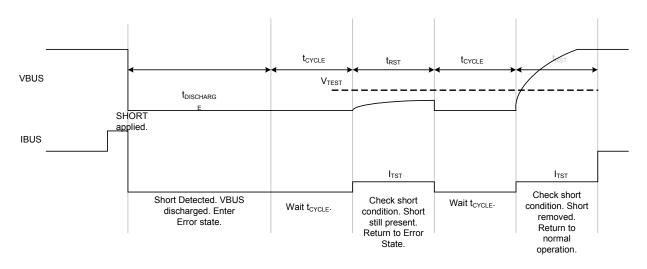

| 7.6.1 Auto-recovery Fault Handling       57         7.6.2 Latched Fault Handling       57         7.6.2 Latched Fault Handling       57         Chapter 8 Detect State       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         9.1 Active State       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.7 A BC1.2 CDP       62         9.7 A BC1.2 DCP Charger Emulation Profile       62         9.8 Deticated Charger       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.3 DC12 DCP Charger Emulation Profile       63         9.4.1 Preloaded Charger Emulation Profile       64         9.10 No Handshake.       64         9.11 Preloaded Charger Emulation Profile       65         9.11.1                                                                           |                                              |      |

| 7.6.2 Latched Fault Handling       57         Chapter 8 Detect State       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         Chapter 9 Active State       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.7 BC1.2 DCP Charger Emulation Profile       61         9.7 BC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8.2 Emulation Reset       62         9.8.2 Emulation Reset       62         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.11 Preloaded Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.1 Bc1.2 acccy Charger Emulation Profile <td< td=""><td></td><td></td></td<>                  |                                              |      |

| Chapter 8 Detect State       58         8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         Chapter 9 Active State       60         9.1 Active State Overview       60         9.3 BC1.2 Detection Renegotiation       60         9.3 BC1.2 DDP (No Charger Emulation)       60         9.4 Data Pass-through (No Charger Emulation Profile       61         9.6 BC1.2 CDP       61         9.6 1 BC1.2 CDP Charger Emulation Profile       62         9.7 1 BC1.2 DCP Charger Emulation Profile       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9.4 Landashake       64         9.11 Preloaded Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.4 Legacy 5 Charger Emulation Profile       65 </td <td></td> <td></td>                                   |                                              |      |

| 8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         Chapter 9 Active State         60         Of the state         Chapter 9 Active State         60         9.1 Active State Overview         9.2 Active Mode Selection         9.1 Active State Overview         9.2 Active Mode Selection         9.1 Active State Overview         9.2 Active Mode Selection         9.2 Detection Renegotiation         9.2 Detection Renegotiation         9.2 Detection Renegotiation         9.3 BC1.2 DCP Charger Emulation)         9.6 1 BC1.2 CDP Charger Emulation Profile         9.6 1 BC1.2 CDP Charger Emulation Profile         9.7 1 BC1.2 DCP Charger Emulation Profile         9.8 1 Emulation Reset         9.8 2 Emulation Reset         9.8 2 Emulation Reset         9.8 2 Emulation Profile         9.8 1 Emulation Reset         9.9 1.1 BC1.2 DCP Charger Emulation Profile Within DCE Cy                                                                                                                                                                                                                                 | 7.6.2 Latched Fault Handling                 | . 57 |

| 8.1 Device Attach / Removal Detection       58         8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         Chapter 9 Active State         60         Of the state         Chapter 9 Active State         60         9.1 Active State Overview         9.2 Active Mode Selection         9.1 Active State Overview         9.2 Active Mode Selection         9.1 Active State Overview         9.2 Active Mode Selection         9.2 Detection Renegotiation         9.2 Detection Renegotiation         9.2 Detection Renegotiation         9.3 BC1.2 DCP Charger Emulation)         9.6 1 BC1.2 CDP Charger Emulation Profile         9.6 1 BC1.2 CDP Charger Emulation Profile         9.7 1 BC1.2 DCP Charger Emulation Profile         9.8 1 Emulation Reset         9.8 2 Emulation Reset         9.8 2 Emulation Reset         9.8 2 Emulation Profile         9.8 1 Emulation Reset         9.9 1.1 BC1.2 DCP Charger Emulation Profile Within DCE Cy                                                                                                                                                                                                                                 |                                              | =0   |

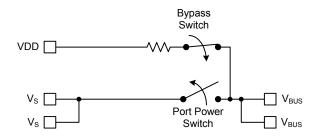

| 8.2 VBUS Bypass Switch       58         8.3 Attach Detection       58         8.4 Removal Detection       58         Chapter 9 Active State       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.4 Data Pass-through (No Charger Emulation)       61         9.6 BC1.2 SDP (No Charger Emulation Profile       61         9.6 BC1.2 CDP       61         9.7 BC1.2 DCP       61         9.7 BC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.10 No Handshake       64         9.11 Proloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       64         9.10 No Handshake       64         9.11 Proloaded Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65                                                     | Chapter 8 Detect State                       | . 58 |

| 8.3 Attach Detection       58         8.4 Removal Detection       58         8.4 Removal Detection       58         Chapter 9 Active State       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.7 BC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 1, 3, 4, and 6 Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 7, Charger Emulation Profile       66                                 |                                              |      |

| 8.4 Removal Detection       58         Chapter 9 Active State       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 1 BC1.2 CDP       61         9.6.1 BC1.2 CDP Charger Emulation Profile       61         9.7 BC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Reset       62         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       64         9.10 No Handshake       64         9.11 Preloaded Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.4 Legacy 5 Charger Emulation Profile       66                             |                                              |      |

| Chapter 9 Active State       60         9.1 Active State Overview       60         9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation)       60         9.6 BC1.2 CDP       61         9.6.1 BC1.2 CDP Charger Emulation Profile       61         9.7 BC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Reset       62         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations.       64         9.10 No Handshake.       64         9.11 BC1.2 DCP Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       63         9.9 Current Limit Mode Associations.       64         9.10 No Handshake.       64         9.11 Preloaded Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.4 Legacy 7 (3, 4, and 6 Charger Emulation Profile       66 <t< td=""><td></td><td></td></t<> |                                              |      |

| 9.1 Active State Overview609.2 Active Mode Selection609.3 BC1.2 Detection Renegotiation609.4 Data Pass-through (No Charger Emulation)609.5 BC1.2 SDP (No Charger Emulation)619.6 BC1.2 CDP619.6 1 BC1.2 CDP Charger Emulation Profile619.7 BC1.2 DCP629.7.1 BC1.2 DCP Charger Emulation Profile629.8.1 Emulation Reset629.8.2 Emulation Cycling639.8.3 DCE Cycle Retry639.9 Current Limit Mode Associations649.11 Preloaded Charger Emulation Profile659.11.1 BC1.2 DCP Charger Emulation Profile659.11.2 Legacy 2 Charger Emulation Profile659.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profile659.11.4 Legacy 5 Charger Emulation Profile669.11.5 Legacy 7 Charger Emulation Profile669.11.6 Legacy 7 Charger Emulation Profile669.11.7 Legacy 7 Charger Emulation Profile6771717110.2 Total Accumulated Charge Registers72                                                                                                                                                                                                                                                                                         | 8.4 Removal Detection                        | . 58 |

| 9.1 Active State Overview609.2 Active Mode Selection609.3 BC1.2 Detection Renegotiation609.4 Data Pass-through (No Charger Emulation)609.5 BC1.2 SDP (No Charger Emulation)619.6 BC1.2 CDP619.6 1 BC1.2 CDP Charger Emulation Profile619.7 BC1.2 DCP629.7.1 BC1.2 DCP Charger Emulation Profile629.8.1 Emulation Reset629.8.2 Emulation Cycling639.8.3 DCE Cycle Retry639.9 Current Limit Mode Associations649.11 Preloaded Charger Emulation Profile659.11.1 BC1.2 DCP Charger Emulation Profile659.11.2 Legacy 2 Charger Emulation Profile659.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profile659.11.4 Legacy 5 Charger Emulation Profile669.11.5 Legacy 7 Charger Emulation Profile669.11.6 Legacy 7 Charger Emulation Profile669.11.7 Legacy 7 Charger Emulation Profile6771717110.2 Total Accumulated Charge Registers72                                                                                                                                                                                                                                                                                         | Character 0 A stine State                    | ()   |

| 9.2 Active Mode Selection       60         9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.6.1 BC1.2 CDP Charger Emulation Profile       61         9.7 BC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8 Dedicated Charger       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.10 No Handshake       64         9.11.1 BC1.2 DCP Charger Emulation Profiles       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 1, 3, 4, and 6 Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       66         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profile       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.4 Legacy 7 Charger Emulation Profile       66         9.11.2 Legacy 7 Charger Emulation Profile       67         9.11.4 Legacy     |                                              |      |

| 9.3 BC1.2 Detection Renegotiation       60         9.4 Data Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.6.1 BC1.2 CDP Charger Emulation Profile       61         9.7 BC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8 Dedicated Charger       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.10 No Handshake       64         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profile       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         9.12 Custom Cha    |                                              |      |

| 9.4 Data Pass-through (No Charger Emulation)       60         9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.6.1 BC1.2 CDP Charger Emulation Profile       61         9.7 DC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8 Dedicated Charger       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations.       64         9.10 No Handshake.       64         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.2 Legacy 1, 3, 4, and 6 Charger Emulation Profile       66         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description                                                                                                                                                                                                                                                                          |                                              |      |

| 9.5 BC1.2 SDP (No Charger Emulation)       61         9.6 BC1.2 CDP       61         9.6.1 BC1.2 CDP Charger Emulation Profile       61         9.7 BC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8 Dedicated Charger       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations.       64         9.11 Preloaded Charger Emulation Profiles       64         9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.3 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profile       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description                                                                                                                                                                                                   |                                              |      |

| 9.6 BC1.2 CDP       61         9.6.1 BC1.2 CDP Charger Emulation Profile       61         9.7 BC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8 Dedicated Charger       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.10 No Handshake       64         9.11.1 BC1.2 DCP Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profile       65         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description                                                                                                                                                                                                                                                                                    |                                              |      |

| 9.6.1 BC1.2 CDP Charger Emulation Profile619.7 BC1.2 DCP629.7.1 BC1.2 DCP Charger Emulation Profile629.8 Dedicated Charger629.8.1 Emulation Reset629.8.2 Emulation Cycling639.8.3 DCE Cycle Retry639.9 Current Limit Mode Associations649.10 No Handshake649.11.1 BC1.2 DCP Charger Emulation Profiles659.11.2 Legacy 2 Charger Emulation Profile659.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profile669.11.4 Legacy 5 Charger Emulation Profile669.11.5 Legacy 7 Charger Emulation Profile669.12 Custom Charger Emulation Profile669.12 Custom Charger Emulation Profile669.12 Custom Charger Emulation Profile67Chapter 10 Register Description0.1 Current Measurement Register7110.2 Total Accumulated Charge Registers72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                              |      |

| 9.7 BC1.2 DCP       62         9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8 Dedicated Charger       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.10 No Handshake       64         9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profile       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         68         10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                         |                                              |      |

| 9.7.1 BC1.2 DCP Charger Emulation Profile       62         9.8 Dedicated Charger       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.10 No Handshake       64         9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profile       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         68         10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                          | 5                                            |      |

| 9.8 Dedicated Charger       62         9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations.       64         9.10 No Handshake.       64         9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile Within DCE Cycle       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profiles       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |      |

| 9.8.1 Emulation Reset       62         9.8.2 Emulation Cycling       63         9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.10 No Handshake       64         9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile Within DCE Cycle       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profiles       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         68         10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |      |

| 9.8.2 Emulation Cycling639.8.3 DCE Cycle Retry639.9 Current Limit Mode Associations649.10 No Handshake649.11 Preloaded Charger Emulation Profiles659.11.1 BC1.2 DCP Charger Emulation Profile Within DCE Cycle659.11.2 Legacy 2 Charger Emulation Profile659.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profiles669.11.4 Legacy 5 Charger Emulation Profile669.11.5 Legacy 7 Charger Emulation Profile669.12 Custom Charger Emulation Profile67Chapter 10 Register Description6810.1 Current Measurement Register7110.2 Total Accumulated Charge Registers72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |      |

| 9.8.3 DCE Cycle Retry       63         9.9 Current Limit Mode Associations       64         9.10 No Handshake       64         9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile Within DCE Cycle       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profiles       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         68         10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |      |

| 9.9 Current Limit Mode Associations       64         9.10 No Handshake       64         9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile Within DCE Cycle       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profiles       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         68       10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |      |

| 9.10 No Handshake.       64         9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile Within DCE Cycle       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profiles       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         68       10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                              |      |

| 9.11 Preloaded Charger Emulation Profiles       65         9.11.1 BC1.2 DCP Charger Emulation Profile Within DCE Cycle       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profiles       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         68         10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |      |

| 9.11.1 BC1.2 DCP Charger Emulation Profile Within DCE Cycle       65         9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profiles       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         0.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |      |

| 9.11.2 Legacy 2 Charger Emulation Profile       65         9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profiles       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         0.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |      |

| 9.11.3 Legacy 1, 3, 4, and 6 Charger Emulation Profiles       66         9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         68       10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |      |

| 9.11.4 Legacy 5 Charger Emulation Profile       66         9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |      |

| 9.11.5 Legacy 7 Charger Emulation Profile       66         9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         0.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |      |

| 9.12 Custom Charger Emulation Profile       67         Chapter 10 Register Description         68       10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |      |

| Chapter 10 Register Description       68         10.1 Current Measurement Register       71         10.2 Total Accumulated Charge Registers       72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |      |

| 10.1 Current Measurement Register    71      10.2 Total Accumulated Charge Registers    72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |      |

| 10.1 Current Measurement Register    71      10.2 Total Accumulated Charge Registers    72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chapter 10 Register Description              | . 68 |

| 10.2 Total Accumulated Charge Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                              |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |      |

| Chapter 14 Document Revision History                                 | 112 |

|----------------------------------------------------------------------|-----|

| Chapter 13 References                                                | 111 |

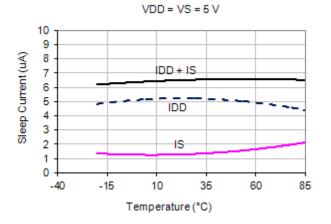

| Chapter 12 Typical Operating Curves                                  | 107 |

| Chapter 11 Package Information                                       | 105 |

| 10.17 Revision Register                                              |     |

| 10.16 Manufacturer ID Register                                       |     |

| 10.15 Product ID Register                                            |     |

| 10.14.2 Custom Current Limiting Behavior Configuration - 51h         | 102 |

| 10.14.1 Applied Current Limiting Behavior - 50h                      |     |

| 10.14 Current Limiting Behavior Configuration Registers              |     |

| 10.13.5 Custom Stimulus / Response Pair X - Config 4 - 44h, 48h, 4Ch |     |

| 10.13.4 Custom Stimulus / Response Pair X - Config 3 - 43h, 47h, 4Bh |     |

| 10.13.3 Custom Stimulus / Response Pair X - Config 2 - 42h, 46h, 4Ah |     |

| 10.13.2 Custom Stimulus / Response Pair X - Config 1 - 41h, 45h, 49h |     |

| 10.13.1 Custom Emulation Configuration - 40h                         |     |

| 10.13 Custom Emulation Configuration Registers.                      |     |

| 10.12.6 Emulation Stimulus X - Config 4 - 34h, 38h                   |     |

| 10.12.5 Emulation Stimulus X - Config 3 - 33h, 37h, 3Bh              |     |

| 10.12.4 BC1.2 Emulation Stimulus X - Config 2 - 32h, 36h, 3Ah        |     |

| 10.12.3 Preloaded Emulation Stimulus X - Config 1 - 31h, 35h, 39h    |     |

| 10.12.2 Preloaded Emulation Configuration Registers 31h - 3Bh        |     |

| 10.12.1 Applied Charger Emulation - 30h                              |     |

| 10.12 Preloaded Emulation Configuration Registers.                   | 90  |

| 10.11.3 Legacy Emulation Timeout Config 2 - 24h                      |     |

| 10.11.2 Legacy Emulation Timeout Config 1 - 23h                      |     |

| 10.11.1 BCS Emulation Timeout Config - 22h                           | 88  |

| 10.11 Preloaded Emulation Timeout Configuration Registers            | 88  |

| 10.10.2 Legacy Emulation Enable - 21h                                |     |

| 10.10.1 BCS Emulation Enable - 20h                                   |     |

| 10.10 Preloaded Emulation Enable Registers                           | 87  |

| 10.9 tDET_CHARGE Configuration Register                              |     |

| 10.8 IBUS_CHG Configuration Register                                 | 85  |

| 10.7 Auto-recovery Configuration Register                            |     |

| 10.6 Charge Rationing Threshold Registers                            |     |

| 10.5 Current Limit Register                                          |     |

| 10.4.5 High-speed Switch Configuration - 25h                         |     |

| 10.4.4 Attach Detection Configuration - 18h.                         |     |

| 10.4.3 Switch Configuration - 17h.                                   |     |

| 10.4.2 Emulation Configuration - 16h                                 |     |

| 10.4.1 General Configuration - 15h                                   |     |

| 10.3 Configuration Registers                                         |     |

| 10.3.6 Pin Status Register - 14h                                     |     |

| 10.3.4 Profile Status 1 - 12h                                        |     |

| 10.3.3 General Status - 11h                                          |     |

| 10.3.2 Interrupt Status - 10h                                        |     |

| 10.3.1 Other Status - 0Fh                                            |     |

|                                                                      | 70  |

## **List of Tables**

|            | Terms and Abbreviations.                                       |    |

|------------|----------------------------------------------------------------|----|

|            | UCS1002 Pin Description                                        |    |

|            | Pin Types.                                                     |    |

|            | Absolute Maximum Ratings                                       |    |

|            | Power Dissipation Summary                                      |    |

| Table 3.3  | Electrical Specifications                                      | 16 |

| Table 3.4  | ESD Ratings                                                    | 26 |

| Table 4.1  | UCS1002 Communication Mode and ILIM Selection                  | 27 |

| Table 4.2  | SEL Pin Decode                                                 | 29 |

| Table 4.3  | Protocol Format                                                | 30 |

| Table 4.4  | Write Byte Protocol                                            | 31 |

|            | Read Byte Protocol                                             |    |

|            | Send Byte Protocol                                             |    |

|            | Receive Byte Protocol                                          |    |

|            | Block Write Protocol                                           |    |

|            | Block Read Protocol                                            |    |

|            | Stand-alone Fault and Attach Detection Selection               |    |

|            | Power States Control Settings.                                 |    |

|            | Charge Rationing Behavior                                      |    |

|            | Charge Rationing Reset Behavior                                |    |

|            | Effects of Changing Rationing Behavior after Threshold Reached |    |

|            | Active Mode Selection                                          |    |