#### Freescale Semiconductor

Order this document by MC68HC16ZUM/AD

# M68HC16Z Series

MC68HC16Z1 MC68CK16Z1 MC68CM16Z2 MC68HC16Z3 MC68HC16Z4 MC68CK16Z4 User's Manual

© Freescale Semiconductor, Inc., 2004. All rights reserved.

**User's Manual**

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

© Motorola, Inc., 1997

User's Manual

M68HC16Z Series

### **TABLE OF CONTENTS**

Paragraph

Title

Page

#### SECTION 1 INTRODUCTION

#### SECTION 2 NOMENCLATURE

| 2.1 | Symbols and Operators    | 2-1 |

|-----|--------------------------|-----|

| 2.2 | CPU16 Register Mnemonics |     |

|     | Register Mnemonics       |     |

| 2.4 | Conventions              | 2-6 |

|     |                          |     |

#### SECTION 3 OVERVIEW

| Central Processor Unit (CPU16/CPU16L)            | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Integration Module (SIM/SIML)             | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Masked ROM Module (MRM) — (MC68HC16Z2/Z3 Only) . | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Analog-to-Digital Converter (ADC)                | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Queued Serial Module (QSM)                       | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Multichannel Communication Interface (MCCI) —    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (MC68HC16Z4/CKZ4 Only)                           | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| General-Purpose Timer (GPT)                      | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Intermodule Bus                                  | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| System Block Diagram and Pin Assignment Diagrams | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin Descriptions                                 | 3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Signal Descriptions                              | 3-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Address Space Maps                               | 3-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                  | M68HC16 Z-Series MCU Features<br>Central Processor Unit (CPU16/CPU16L)<br>System Integration Module (SIM/SIML)<br>Standby RAM (SRAM)<br>Masked ROM Module (MRM) — (MC68HC16Z2/Z3 Only)<br>Analog-to-Digital Converter (ADC)<br>Queued Serial Module (QSM)<br>Multichannel Communication Interface (MCCI) —<br>(MC68HC16Z4/CKZ4 Only)<br>General-Purpose Timer (GPT)<br>Intermodule Bus<br>System Block Diagram and Pin Assignment Diagrams<br>Pin Descriptions<br>Signal Descriptions<br>Internal Register Map<br>Address Space Maps |

### SECTION 4 CENTRAL PROCESSOR UNIT

| 4.1   | General                                                 | 4-1 |

|-------|---------------------------------------------------------|-----|

| 4.2   | Register Model                                          | 4-1 |

| 4.2.1 | Accumulators                                            |     |

| 4.2.2 | Index Registers                                         | 4-3 |

| 4.2.3 | Stack Pointer                                           |     |

| 4.2.4 | Program Counter                                         | 4-3 |

| 4.2.5 | Condition Code Register                                 | 4-4 |

| 4.2.6 | Address Extension Register and Address Extension Fields |     |

M68HC16 Z SERIES USER'S MANUAL

> For More Information On This Product, Go to: www.freescale.com

### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

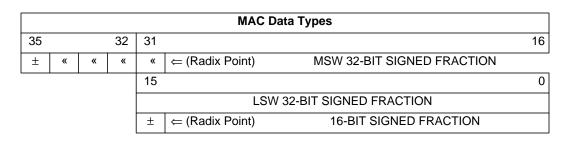

| 4.2.7    | Multiply and Accumulate Registers                        | 1-5  |

|----------|----------------------------------------------------------|------|

| 4.3      | Memory Management                                        |      |

| 4.3.1    | Address Extension                                        |      |

| 4.3.1    | Extension Fields                                         |      |

| 4.3.2    | Data Types                                               |      |

| 4.4      | Memory Organization                                      |      |

| 4.5      | Addressing Modes                                         |      |

| 4.6.1    | Immediate Addressing Modes                               |      |

| 4.6.2    | Extended Addressing Modes                                |      |

| 4.6.3    | Indexed Addressing Modes                                 |      |

| 4.6.4    | Inherent Addressing Mode                                 |      |

| 4.6.5    | Accumulator Offset Addressing Mode                       |      |

| 4.6.6    | Relative Addressing Modes                                |      |

| 4.6.7    | Post-Modified Index Addressing Mode                      |      |

| 4.6.8    | Use of CPU16 Indexed Mode to Replace M68HC11 Direct Mode |      |

| 4.0.8    | Instruction Set                                          |      |

| 4.7.1    | Instruction Set Summary                                  |      |

| 4.8      | Comparison of CPU16 and M68HC11 CPU Instruction Sets     |      |

| 4.0      | Instruction Format                                       |      |

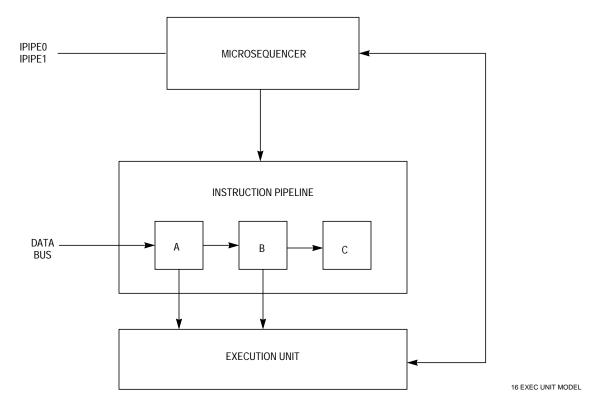

| 4.10     | Execution Model                                          |      |

| 4.10.1   | Microsequencer                                           |      |

| 4.10.1   | Instruction Pipeline                                     |      |

| 4.10.2   | Execution Unit                                           |      |

| 4.11     | Execution Process                                        |      |

| 4.11.1   | Changes in Program Flow                                  |      |

| 4.12     | Instruction Timing                                       |      |

| 4.13     | Exceptions                                               |      |

| 4.13.1   | Exception Vectors                                        |      |

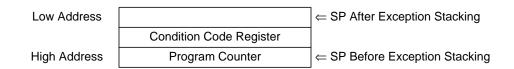

| 4.13.2   | Exception Stack Frame                                    |      |

| 4.13.3   | Exception Processing Sequence                            |      |

| 4.13.4   | Types of Exceptions                                      |      |

| 4.13.4.1 | 21 1                                                     |      |

| 4.13.4.2 |                                                          |      |

| 4.13.5   | Multiple Exceptions                                      |      |

| 4.13.6   | RTI Instruction                                          |      |

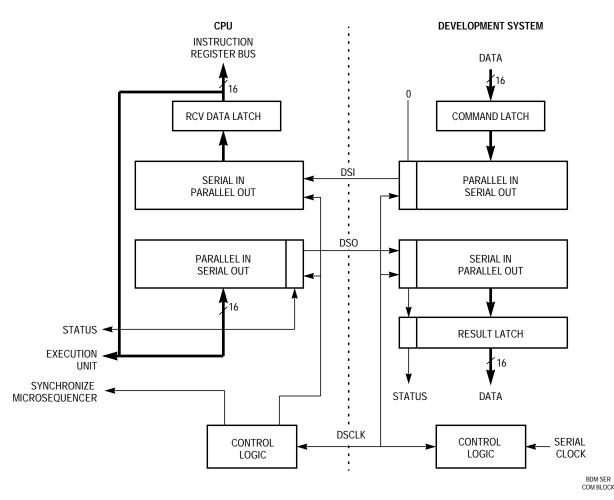

| 4.14     | Development Support                                      | 4-40 |

| 4.14.1   | Deterministic Opcode Tracking                            |      |

| 4.14.1.1 |                                                          |      |

| 4.14.1.2 | 2 Combining Opcode Tracking with Other Capabilities      | 4-41 |

| 4.14.2   | Breakpoints                                              | 4-41 |

| 4.14.3   | Opcode Tracking and Breakpoints                          | 4-42 |

### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

| 4.14.4   | Background Debug Mode      | 4-42 |

|----------|----------------------------|------|

| 4.14.4.1 | Enabling BDM               | 4-42 |

| 4.14.4.2 | BDM Sources                | 4-42 |

| 4.14.4.3 | Entering BDM               | 4-42 |

| 4.14.4.4 |                            |      |

| 4.14.4.5 | Returning from BDM         | 4-43 |

| 4.14.4.6 |                            |      |

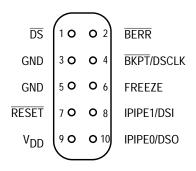

| 4.15     | Recommended BDM Connection | 4-45 |

| 4.16     | Digital Signal Processing  | 4-45 |

|          |                            |      |

### SECTION 5 SYSTEM INTEGRATION MODULE

| 5.1     | General                          | 5-1  |

|---------|----------------------------------|------|

| 5.2     | System Configuration             | 5-2  |

| 5.2.1   | Module Mapping                   | 5-2  |

| 5.2.2   | Interrupt Arbitration            | 5-3  |

| 5.2.3   | Show Internal Cycles             | 5-3  |

| 5.2.4   | Register Access                  | 5-3  |

| 5.2.5   | Freeze Operation                 | 5-3  |

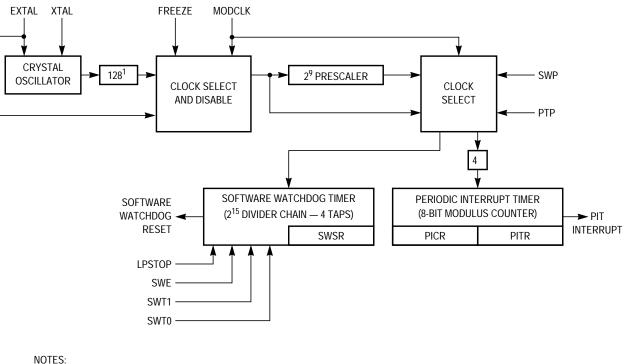

| 5.3     | System Clock                     | 5-4  |

| 5.3.1   | Clock Sources                    | 5-5  |

| 5.3.2   | Clock Synthesizer Operation      | 5-6  |

| 5.3.3   | External Bus Clock               | 5-21 |

| 5.3.4   | Low-Power Operation              | 5-21 |

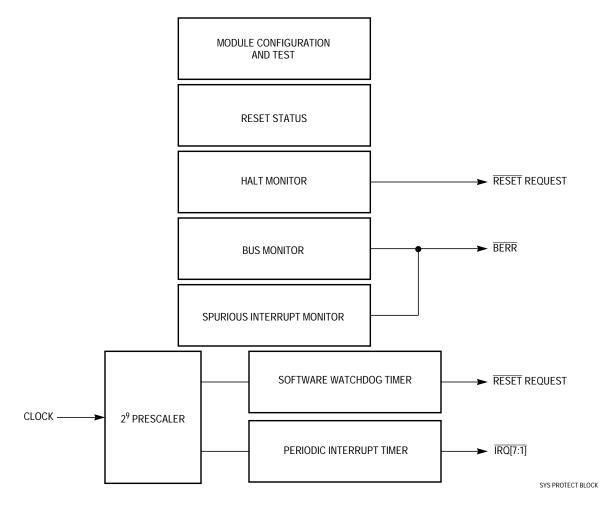

| 5.4     | System Protection                | 5-24 |

| 5.4.1   | Reset Status                     | 5-24 |

| 5.4.2   | Bus Monitor                      | 5-24 |

| 5.4.3   | Halt Monitor                     | 5-25 |

| 5.4.4   | Spurious Interrupt Monitor       | 5-25 |

| 5.4.5   | Software Watchdog                | 5-25 |

| 5.4.6   | Periodic Interrupt Timer         | 5-27 |

| 5.4.7   | Interrupt Priority and Vectoring | 5-28 |

| 5.4.8   | Low-Power STOP Operation         | 5-29 |

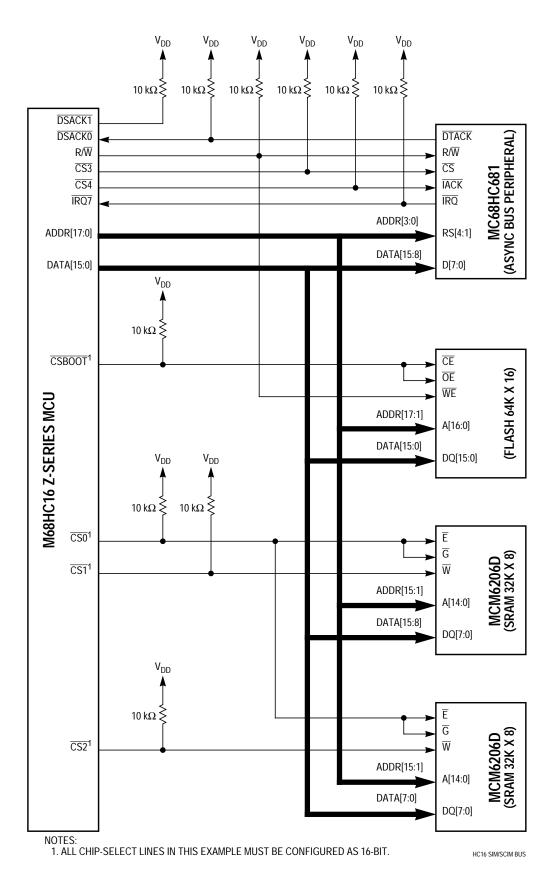

| 5.5     | External Bus Interface           | 5-29 |

| 5.5.1   | Bus Control Signals              | 5-31 |

| 5.5.1.1 | Address Bus                      | 5-31 |

| 5.5.1.2 | Address Strobe                   | 5-31 |

| 5.5.1.3 | Data Bus                         | 5-31 |

| 5.5.1.4 | Data Strobe                      | 5-31 |

| 5.5.1.5 | Read/Write Signal                | 5-32 |

| 5.5.1.6 | Size Signals                     | 5-32 |

### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

| 5.5.1.7  | Function Codes5-32                                     |

|----------|--------------------------------------------------------|

| 5.5.1.8  | Data Size Acknowledge Signals5-32                      |

| 5.5.1.9  | Bus Error Signal5-33                                   |

| 5.5.1.10 |                                                        |

| 5.5.1.11 | Autovector Signal5-33                                  |

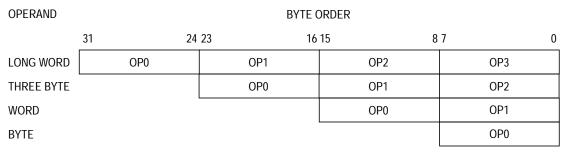

| 5.5.2    | Dynamic Bus Sizing5-33                                 |

| 5.5.3    | Operand Alignment5-35                                  |

| 5.5.4    | Misaligned Operands5-35                                |

| 5.5.5    | Operand Transfer Cases5-35                             |

| 5.6      | Bus Operation                                          |

| 5.6.1    | Synchronization to CLKOUT5-36                          |

| 5.6.2    | Regular Bus Cycle5-37                                  |

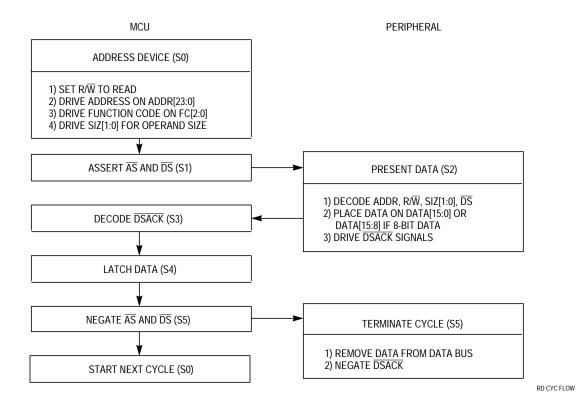

| 5.6.2.1  | Read Cycle5-37                                         |

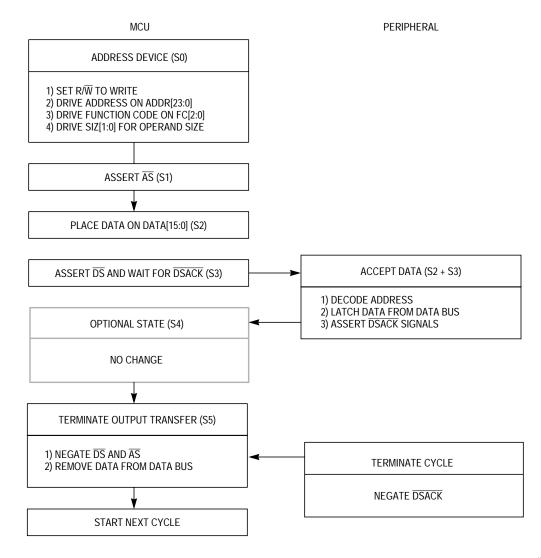

| 5.6.2.2  | Write Cycle5-38                                        |

| 5.6.3    | Fast Termination Cycles5-39                            |

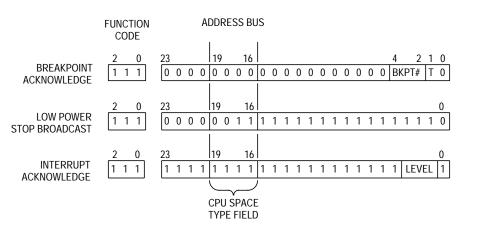

| 5.6.4    | CPU Space Cycles5-40                                   |

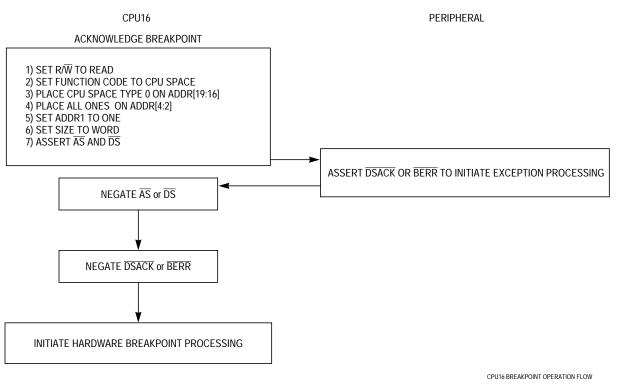

| 5.6.4.1  | Breakpoint Acknowledge Cycle5-41                       |

| 5.6.4.2  | LPSTOP Broadcast Cycle5-42                             |

| 5.6.5    | Bus Exception Control Cycles5-43                       |

| 5.6.5.1  | Bus Errors5-44                                         |

| 5.6.5.2  | Double Bus Faults5-45                                  |

| 5.6.5.3  | Halt Operation5-45                                     |

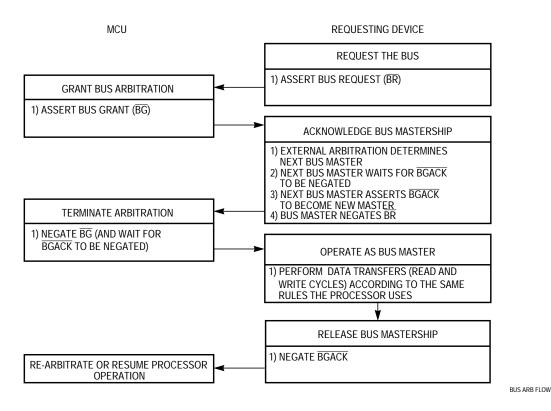

| 5.6.6    | External Bus Arbitration5-46                           |

| 5.6.6.1  | Show Cycles5-47                                        |

| 5.7      | Reset                                                  |

| 5.7.1    | Reset Exception Processing5-48                         |

| 5.7.2    | Reset Control Logic5-48                                |

| 5.7.3    | Reset Mode Selection5-49                               |

| 5.7.3.1  | Data Bus Mode Selection5-50                            |

| 5.7.3.2  | Clock Mode Selection5-52                               |

| 5.7.3.3  | Breakpoint Mode Selection5-52                          |

| 5.7.4    | MCU Module Pin Function During Reset                   |

| 5.7.5    | Pin State During Reset5-53                             |

| 5.7.5.1  | Reset States of SIM Pins5-54                           |

| 5.7.5.2  | Reset States of Pins Assigned to Other MCU Modules5-54 |

| 5.7.6    | Reset Timing5-55                                       |

| 5.7.7    | Power-On Reset5-55                                     |

| 5.7.8    | Use of the Three-State Control Pin5-56                 |

| 5.7.9    | Reset Processing Summary5-57                           |

| 5.7.10   | Reset Status Register5-57                              |

| 5.8      | Interrupts                                             |

### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

| Interrupt Exception Processing                      | 5-58                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     |                                                                                                                                                                                                                                                                             |

|                                                     |                                                                                                                                                                                                                                                                             |

|                                                     |                                                                                                                                                                                                                                                                             |

|                                                     |                                                                                                                                                                                                                                                                             |

|                                                     |                                                                                                                                                                                                                                                                             |

|                                                     |                                                                                                                                                                                                                                                                             |

|                                                     |                                                                                                                                                                                                                                                                             |

| Chip-Select Base Address Registers                  |                                                                                                                                                                                                                                                                             |

| Chip-Select Option Registers                        | 5-66                                                                                                                                                                                                                                                                        |

| PORTC Data Register                                 |                                                                                                                                                                                                                                                                             |

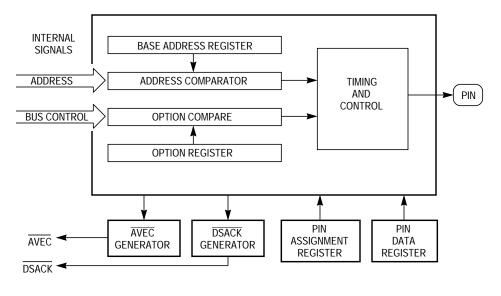

| Chip-Select Operation                               | 5-67                                                                                                                                                                                                                                                                        |

| Using Chip-Select Signals for Interrupt Acknowledge | 5-68                                                                                                                                                                                                                                                                        |

| Chip-Select Reset Operation                         | 5-69                                                                                                                                                                                                                                                                        |

|                                                     |                                                                                                                                                                                                                                                                             |

| Pin Assignment Registers                            | 5-70                                                                                                                                                                                                                                                                        |

|                                                     |                                                                                                                                                                                                                                                                             |

|                                                     |                                                                                                                                                                                                                                                                             |

| Factory Test                                        |                                                                                                                                                                                                                                                                             |

|                                                     | Chip-Select Option Registers<br>PORTC Data Register<br>Chip-Select Operation<br>Using Chip-Select Signals for Interrupt Acknowledge<br>Chip-Select Reset Operation<br>Parallel Input/Output Ports<br>Pin Assignment Registers<br>Data Direction Registers<br>Data Registers |

### SECTION 6 STANDBY RAM MODULE

| 6.1 | SRAM Register Block                  | 6-1 |

|-----|--------------------------------------|-----|

| 6.2 | SRAM Array Address Mapping           |     |

| 6.3 | SRAM Array Address Space Type        |     |

| 6.4 | Normal Access                        |     |

| 6.5 | Standby and Low-Power Stop Operation | 6-2 |

| 6.6 | Reset                                | 6-3 |

#### SECTION 7 MASKED ROM MODULE

| 7.1 | MRM Register Block            | 7-1 |

|-----|-------------------------------|-----|

| 7.2 | MRM Array Address Mapping     | 7-1 |

| 7.3 | MRM Array Address Space Type  |     |

| 7.4 | Normal Access                 |     |

| 7.5 | Low-Power Stop Mode Operation |     |

| 7.6 | ROM Signature                 |     |

| 7.7 | Reset                         |     |

### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

### SECTION 8 ANALOG-TO-DIGITAL CONVERTER

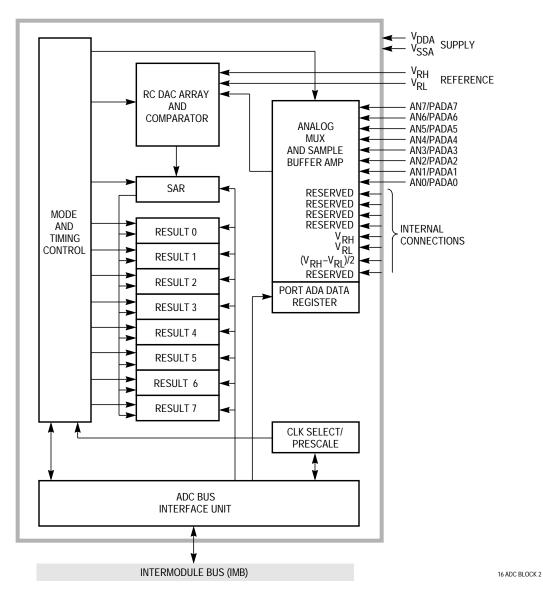

| 8.1     | General                                           | 8-1  |

|---------|---------------------------------------------------|------|

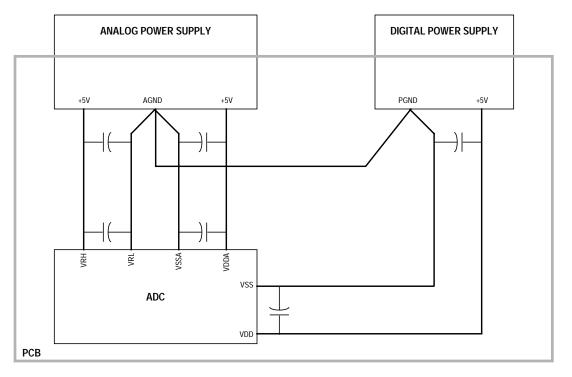

| 8.2     | External Connections                              | 8-1  |

| 8.2.1   | Analog Input Pins                                 | 8-2  |

| 8.2.2   | Analog Reference Pins                             | 8-3  |

| 8.2.3   | Analog Supply Pins                                | 8-3  |

| 8.3     | Programmer's Model                                | 8-3  |

| 8.4     | ADC Bus Interface Unit                            | 8-3  |

| 8.5     | Special Operating Modes                           | 8-3  |

| 8.5.1   | Low-Power Stop Mode                               | 8-3  |

| 8.5.2   | Freeze Mode                                       | 8-4  |

| 8.6     | Analog Subsystem                                  | 8-4  |

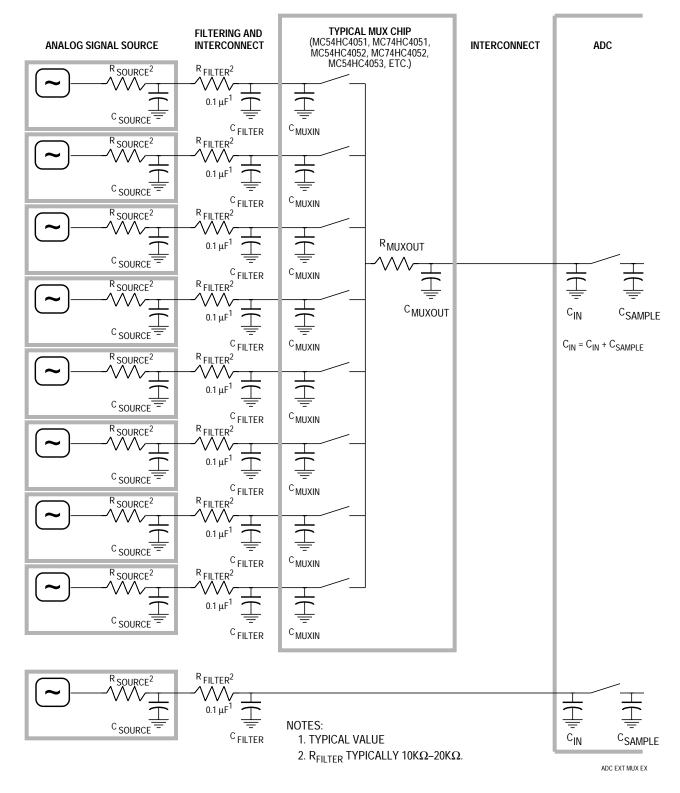

| 8.6.1   | Multiplexer                                       | 8-4  |

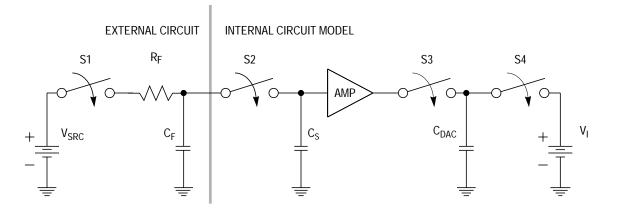

| 8.6.2   | Sample Capacitor and Buffer Amplifier             | 8-5  |

| 8.6.3   | RC DAC Array                                      | 8-5  |

| 8.6.4   | Comparator                                        | 8-6  |

| 8.7     | Digital Control Subsystem                         |      |

| 8.7.1   | Control/Status Registers                          |      |

| 8.7.2   | Clock and Prescaler Control                       | 8-6  |

| 8.7.3   | Sample Time                                       | 8-7  |

| 8.7.4   | Resolution                                        |      |

| 8.7.5   | Conversion Control Logic                          | 8-7  |

| 8.7.5.1 | Conversion Parameters                             | 8-8  |

| 8.7.5.2 | Conversion Modes                                  |      |

| 8.7.6   | Conversion Timing                                 |      |

| 8.7.7   | Successive Approximation Register                 |      |

| 8.7.8   | Result Registers                                  |      |

| 8.8     | Pin Considerations                                |      |

| 8.8.1   | Analog Reference Pins                             |      |

| 8.8.2   | Analog Power Pins                                 |      |

| 8.8.3   | Analog Supply Filtering and Grounding             |      |

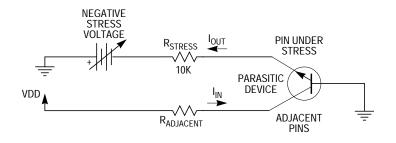

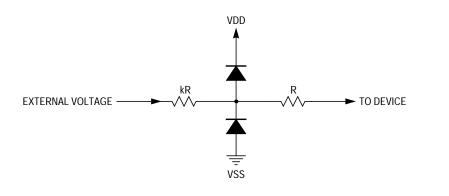

| 8.8.4   | Accommodating Positive/Negative Stress Conditions |      |

| 8.8.5   | Analog Input Considerations                       |      |

| 8.8.6   | Analog Input Pins                                 |      |

| 8.8.6.1 | Settling Time for the External Circuit            |      |

| 8.8.6.2 | Error Resulting from Leakage                      | 8-23 |

### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

#### SECTION 9 QUEUED SERIAL MODULE

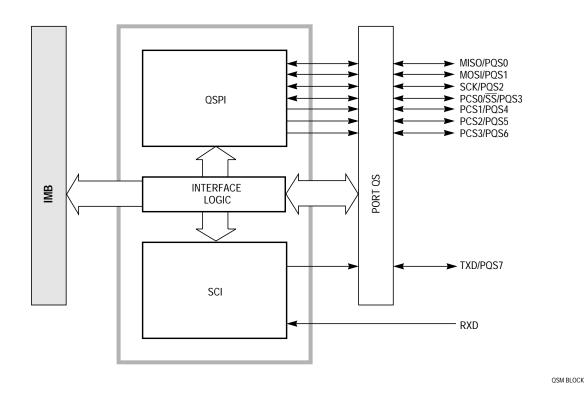

| 9.1     | General                            | 9-1   |

|---------|------------------------------------|-------|

| 9.2     | QSM Registers and Address Map      | 9-2   |

| 9.2.1   | QSM Global Registers               | 9-2   |

| 9.2.1.1 | Low-Power Stop Mode Operation      | 9-2   |

| 9.2.1.2 | Freeze Operation                   | 9-3   |

| 9.2.1.3 | QSM Interrupts                     | 9-3   |

| 9.2.2   | QSM Pin Control Registers          | 9-4   |

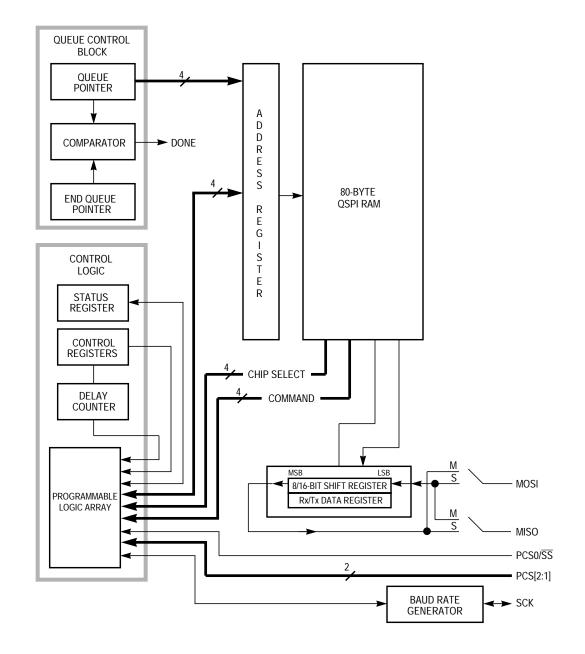

| 9.3     | Queued Serial Peripheral Interface |       |

| 9.3.1   | QSPI Registers                     |       |

| 9.3.1.1 | Control Registers                  |       |

| 9.3.1.2 | Status Register                    | 9-7   |

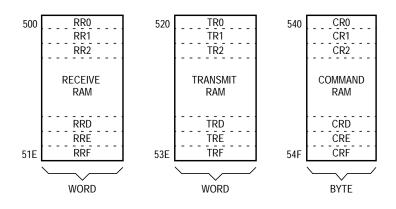

| 9.3.2   | QSPI RAM                           | 9-7   |

| 9.3.2.1 | Receive RAM                        | 9-7   |

| 9.3.2.2 | Transmit RAM                       | 9-7   |

| 9.3.2.3 | Command RAM                        | 9-8   |

| 9.3.3   | QSPI Pins                          | 9-8   |

| 9.3.4   | QSPI Operation                     | 9-8   |

| 9.3.5   | QSPI Operating Modes               | 9-9   |

| 9.3.5.1 | Master Mode                        | .9-16 |

| 9.3.5.2 | Master Wrap-Around Mode            | .9-19 |

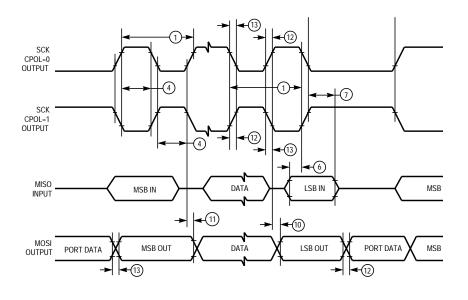

| 9.3.5.3 | Slave Mode                         | .9-20 |

| 9.3.5.4 | Slave Wrap-Around Mode             | .9-21 |

| 9.3.6   | Peripheral Chip Selects            | .9-21 |

| 9.4     | Serial Communication Interface     | .9-21 |

| 9.4.1   | SCI Registers                      | .9-24 |

| 9.4.1.1 | Control Registers                  | .9-24 |

| 9.4.1.2 | Status Register                    | .9-24 |

| 9.4.1.3 | Data Register                      | .9-24 |

| 9.4.2   | SCI Pins                           | .9-25 |

| 9.4.3   | SCI Operation                      | .9-25 |

| 9.4.3.1 | Definition of Terms                | .9-25 |

| 9.4.3.2 | Serial Formats                     | .9-25 |

| 9.4.3.3 | Baud Clock                         | .9-26 |

| 9.4.3.4 | Parity Checking                    | .9-26 |

| 9.4.3.5 | Transmitter Operation              | .9-27 |

| 9.4.3.6 | Receiver Operation                 |       |

| 9.4.3.7 | Idle-Line Detection                | .9-29 |

| 9.4.3.8 | Receiver Wake-Up                   | .9-29 |

| 9.4.3.9 | Internal Loop Mode                 | .9-30 |

#### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

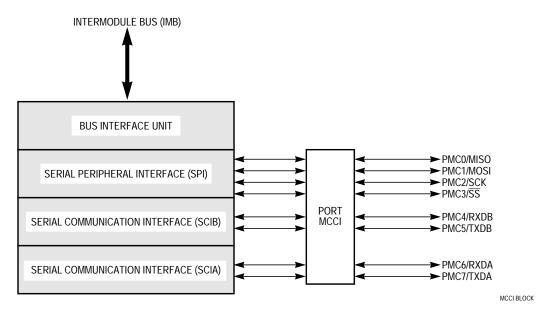

### SECTION 10 MULTICHANNEL COMMUNICATION INTERFACE

| 10.1     | General                               |       |

|----------|---------------------------------------|-------|

| 10.2     | MCCI Registers and Address Map        | 10-2  |

| 10.2.1   | MCCI Global Registers                 | 10-2  |

| 10.2.1.1 | Low-Power Stop Mode                   | 10-2  |

| 10.2.1.2 | Privilege Levels                      | 10-3  |

| 10.2.1.3 |                                       |       |

| 10.2.2   | Pin Control and General-Purpose I/O   | 10-4  |

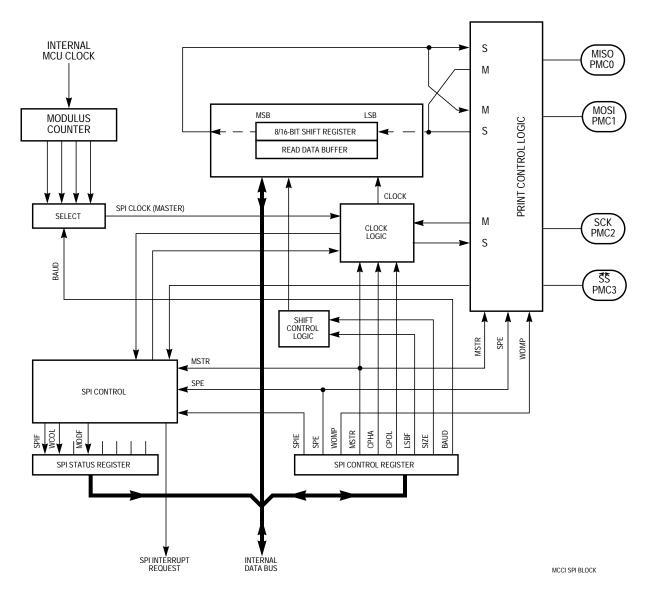

| 10.3     | Serial Peripheral Interface (SPI)     | 10-4  |

| 10.3.1   | SPI Registers                         |       |

| 10.3.1.1 | SPI Control Register (SPCR)           | 10-6  |

| 10.3.1.2 | SPI Status Register (SPSR)            | 10-6  |

| 10.3.1.3 | SPI Data Register (SPDR)              | 10-6  |

| 10.3.2   | SPI Pins                              |       |

| 10.3.3   | SPI Operating Modes                   |       |

| 10.3.3.1 | Master Mode                           |       |

| 10.3.3.2 |                                       |       |

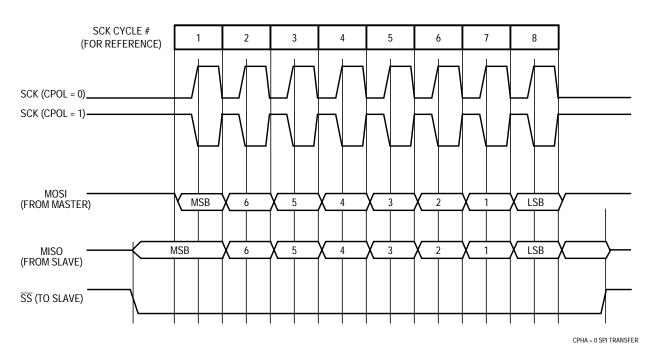

| 10.3.4   | SPI Clock Phase and Polarity Controls | 10-8  |

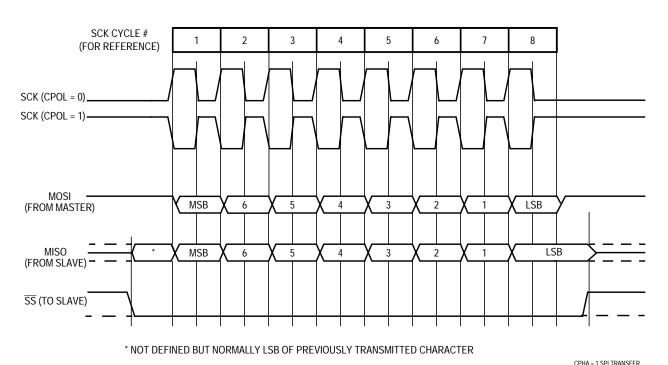

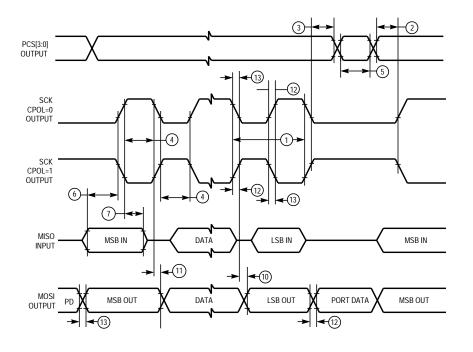

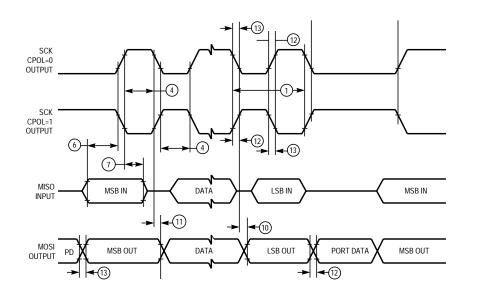

| 10.3.4.1 | CPHA = 0 Transfer Format              | 10-9  |

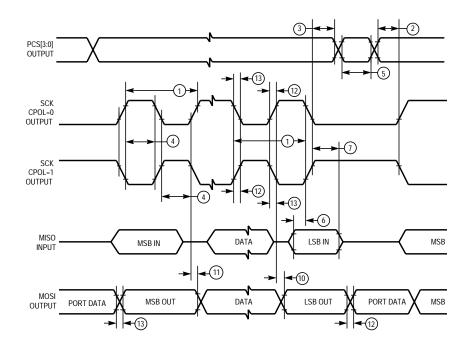

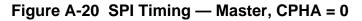

| 10.3.4.2 |                                       |       |

| 10.3.5   | SPI Serial Clock Baud Rate            |       |

| 10.3.6   | Wired-OR Open-Drain Outputs           |       |

| 10.3.7   | Transfer Size and Direction           |       |

| 10.3.8   | Write Collision                       |       |

| 10.3.9   | Mode Fault                            |       |

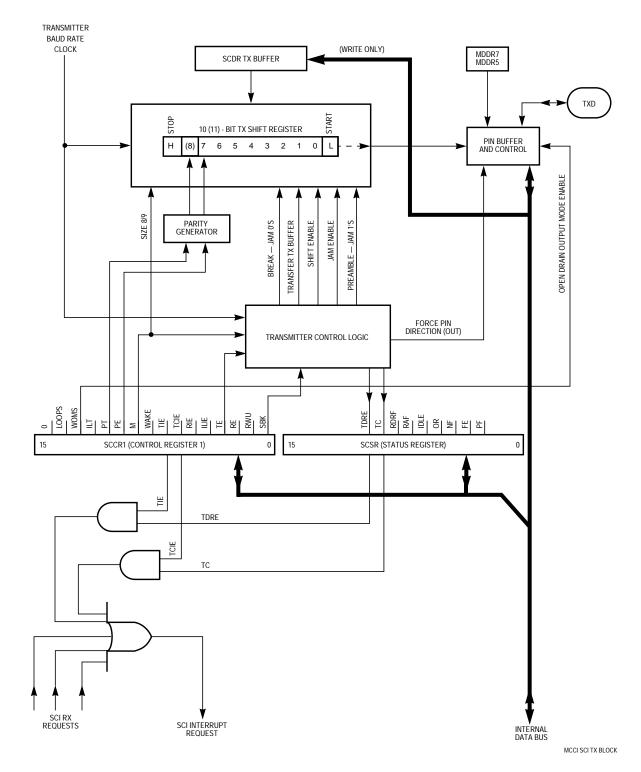

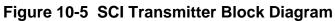

| 10.4     | Serial Communication Interface (SCI)  |       |

| 10.4.1   | SCI Registers                         |       |

| 10.4.1.1 | SCI Control Registers                 |       |

| 10.4.1.2 |                                       |       |

| 10.4.1.3 | 5                                     |       |

| 10.4.2   | SCI Pins                              |       |

| 10.4.3   | Receive Data Pins (RXDA, RXDB)        |       |

| 10.4.4   | Transmit Data Pins (TXDA, TXDB)       |       |

| 10.4.5   | SCI Operation                         |       |

| 10.4.5.1 | Definition of Terms                   |       |

| 10.4.5.2 |                                       |       |

| 10.4.5.3 |                                       |       |

| 10.4.5.4 |                                       |       |

| 10.4.5.5 |                                       |       |

| 10.4.5.6 | Receiver Operation                    | 10-20 |

### TABLE OF CONTENTS (Continued) Title

### Paragraph

Page

| 10.4.5.7     | Idle-Line Detection |  |

|--------------|---------------------|--|

| 10.4.5.8     | Receiver Wake-Up    |  |

| 10.4.5.9     | Internal Loop       |  |

| 10.5 MCCI Ir | nitialization       |  |

### SECTION 11 GENERAL-PURPOSE TIMER

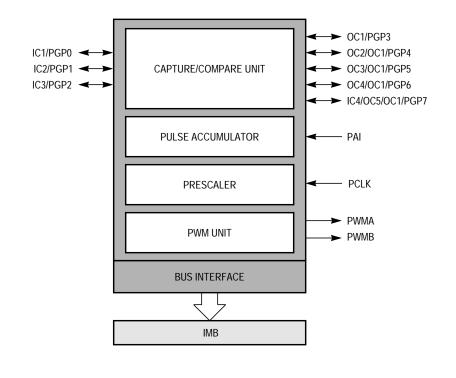

| 11.1     | General                               | 11-1  |

|----------|---------------------------------------|-------|

| 11.2     | GPT Registers and Address Map         | 11-2  |

| 11.3     | Special Modes of Operation            | 11-3  |

| 11.3.1   | Low-Power Stop Mode                   | 11-3  |

| 11.3.2   | Freeze Mode                           | 11-3  |

| 11.3.3   | Single-Step Mode                      | 11-4  |

| 11.3.4   | Test Mode                             | 11-4  |

| 11.4     | Polled and Interrupt-Driven Operation | 11-4  |

| 11.4.1   | Polled Operation                      | 11-4  |

| 11.4.2   | GPT Interrupts                        | 11-5  |

| 11.5     | Pin Descriptions                      | 11-7  |

| 11.5.1   | Input Capture Pins                    | 11-7  |

| 11.5.2   | Input Capture/Output Compare Pin      | 11-7  |

| 11.5.3   | Output Compare Pins                   | 11-7  |

| 11.5.4   | Pulse Accumulator Input Pin           |       |

| 11.5.5   | Pulse-Width Modulation                | 11-8  |

| 11.5.6   | Auxiliary Timer Clock Input           | 11-8  |

| 11.6     | General-Purpose I/O                   | 11-8  |

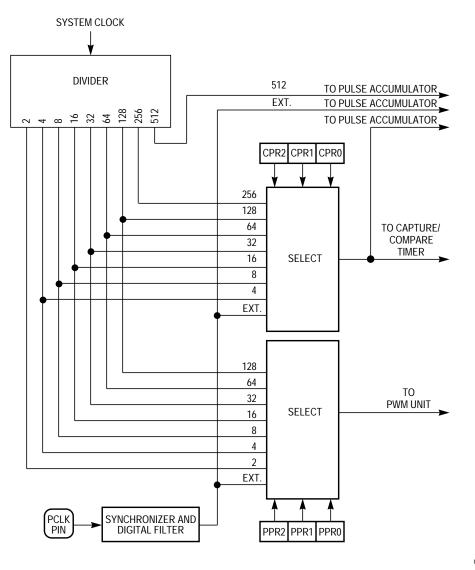

| 11.7     | Prescaler                             | 11-8  |

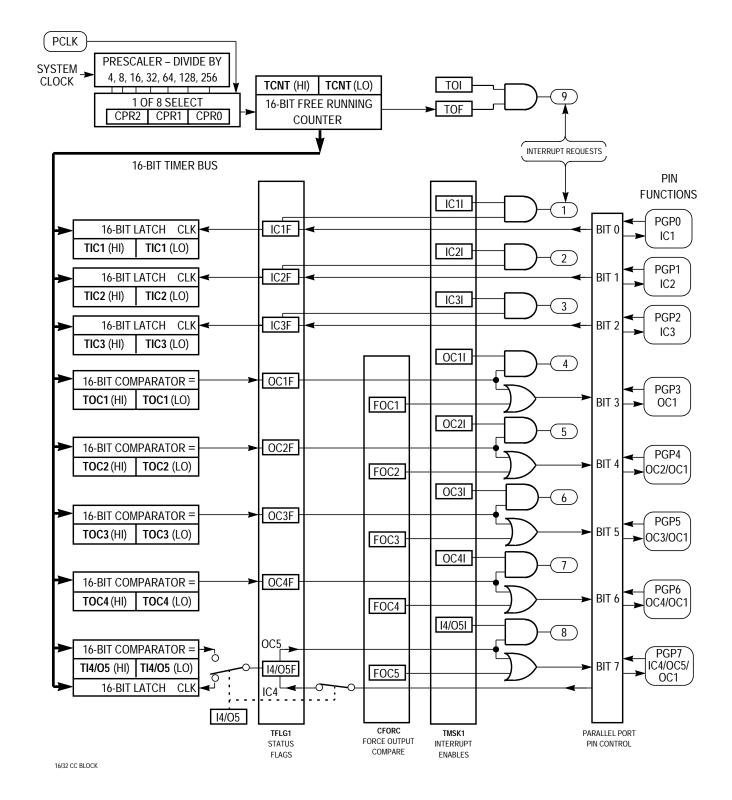

| 11.8     | Capture/Compare Unit                  | 11-10 |

| 11.8.1   | Timer Counter                         | 11-10 |

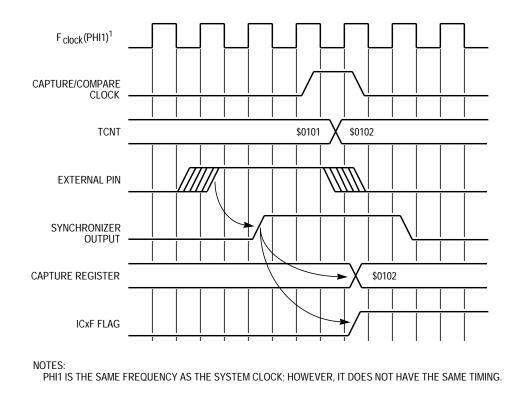

| 11.8.2   | Input Capture Functions               |       |

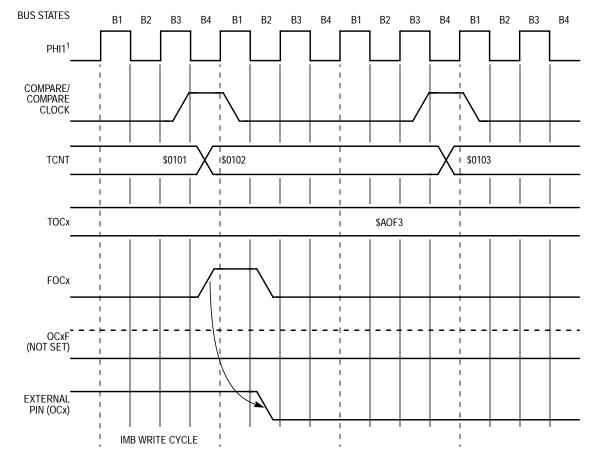

| 11.8.3   | Output Compare Functions              | 11-13 |

| 11.8.3.1 |                                       |       |

| 11.8.3.2 |                                       |       |

| 11.9     | Input Capture 4/Output Compare 5      |       |

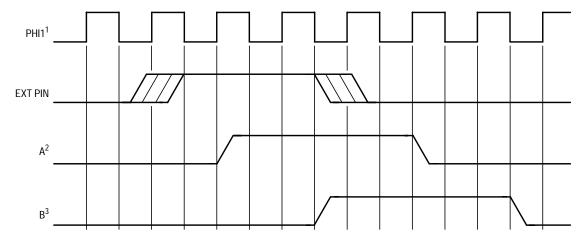

| 11.10    | Pulse Accumulator                     |       |

| 11.11    | Pulse-Width Modulation Unit           |       |

| 11.11.1  | PWM Counter                           | -     |

| 11.11.2  | PWM Function                          | 11-18 |

#### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

### APPENDIX A ELECTRICAL CHARACTERISTICS

#### APPENDIX B MECHANICAL DATA AND ORDERING INFORMATION

| B.1 | Obtaining Updated M68HC16 Z-Series MCU Mechanical Information | <mark>B-</mark> 8 |

|-----|---------------------------------------------------------------|-------------------|

| B.2 | Ordering Information                                          | <mark>B-</mark> 8 |

### APPENDIX C DEVELOPMENT SUPPORT

| C.1 | M68MMDS1632 Modular Development System | C-1 |

|-----|----------------------------------------|-----|

| C.2 | M68MEVB1632 Modular Evaluation Board   | C-2 |

### APPENDIX D REGISTER SUMMARY

| D.1    | Central Processing Unit                | D-1  |

|--------|----------------------------------------|------|

| D.1.1  | Condition Code Register                |      |

| D.2    | System Integration Module              | D-4  |

| D.2.1  | SIM Module Configuration Register      | D-6  |

| D.2.2  | System Integration Test Register       | D-7  |

| D.2.3  | Clock Synthesizer Control Register     |      |

| D.2.4  | Reset Status Register                  |      |

| D.2.5  | System Integration Test Register E     |      |

| D.2.6  | Port E Data Register                   |      |

| D.2.7  | Port E Data Direction Register         |      |

| D.2.8  | Port E Pin Assignment Register         | D-10 |

| D.2.9  | Port F Data Register                   |      |

| D.2.10 | Port F Data Direction Register         | D-11 |

| D.2.11 | Port F Pin Assignment Register         |      |

| D.2.12 | System Protection Control Register     | D-12 |

| D.2.13 | Periodic Interrupt Control Register    |      |

| D.2.14 | Periodic Interrupt Timer Register      |      |

| D.2.15 | Software Watchdog Service Register     |      |

| D.2.16 | Port C Data Register                   |      |

| D.2.17 | Chip-Select Pin Assignment Registers   |      |

| D.2.18 | Chip-Select Base Address Register Boot |      |

| D.2.19 | Chip-Select Base Address Registers     | D-17 |

| D.2.20 | Chip-Select Option Register Boot       |      |

| D.2.21 | Chip-Select Option Registers           |      |

|        |                                        |      |

### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

| D.2.22 | Master Shift Registers                                  | D-22 |

|--------|---------------------------------------------------------|------|

| D.2.23 | Test Module Shift Count Register                        | D-22 |

| D.2.24 | Test Module Repetition Count Register                   |      |

| D.2.25 | Test Module Control Register                            |      |

| D.2.26 | Test Module Distributed Register                        |      |

| D.3    | Standby RAM Module                                      | D-23 |

| D.3.1  | RAM Module Configuration Register                       | D-23 |

| D.3.2  | RAM Test Register                                       |      |

| D.3.3  | Array Base Address Register High                        | D-24 |

| D.3.4  | Array Base Address Register Low                         |      |

| D.4    | Masked ROM Module                                       |      |

| D.4.1  | Masked ROM Module Configuration Register                | D-25 |

| D.4.2  | ROM Array Base Address Registers                        |      |

| D.4.3  | ROM Signature Registers High                            | D-27 |

| D.4.4  | ROM Bootstrap Words                                     | D-28 |

| D.5    | Analog-to-Digital Converter Module                      | D-29 |

| D.5.1  | ADC Module Configuration Register                       |      |

| D.5.2  | ADC Test Register                                       |      |

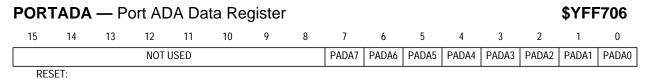

| D.5.3  | Port ADA Data Register                                  | D-30 |

| D.5.4  | ADC Control Register 0                                  | D-31 |

| D.5.5  | ADC Control Register 1                                  | D-32 |

| D.5.6  | ADC Status Register                                     | D-36 |

| D.5.7  | Right Justified, Unsigned Result Register               | D-36 |

| D.6    | Queued Serial Module                                    | D-38 |

| D.6.1  | QSM Configuration Register                              | D-38 |

| D.6.2  | QSM Test Register                                       | D-39 |

| D.6.3  | QSM Interrupt Level Register/Interrupt Vector Register  | D-39 |

| D.6.4  | SCI Control Register                                    | D-40 |

| D.6.5  | SCI Control Register 1                                  | D-41 |

| D.6.6  | SCI Status Register                                     | D-43 |

| D.6.7  | SCI Data Register                                       | D-44 |

| D.6.8  | Port QS Data Register                                   | D-44 |

| D.6.9  | Port QS Pin Assignment Register/Data Direction Register | D-45 |

| D.6.10 | QSPI Control Register 0                                 | D-46 |

| D.6.11 | QSPI Control Register 1                                 | D-48 |

| D.6.12 | QSPI Control Register 2                                 |      |

| D.6.13 | QSPI Control Register 3                                 |      |

| D.6.14 | Receive Data RAM                                        |      |

| D.6.15 | Transmit Data RAM                                       |      |

| D.6.16 | Command RAM                                             |      |

| D.7    | Multichannel Communication Interface Module             | D-54 |

Paragraph

### Freescale Semiconductor, Inc.

### TABLE OF CONTENTS (Continued) Title

Page

| D.7.1  | MCCI Module Configuration RegisterD-54                           |

|--------|------------------------------------------------------------------|

| D.7.2  | MCCI Test Register D-55                                          |

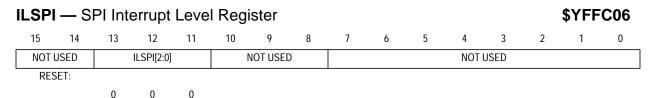

| D.7.3  | SCI Interrupt Level Register/MCCI Interrupt Vector Register D-55 |

| D.7.4  | MCCI Interrupt Vector Register D-56                              |

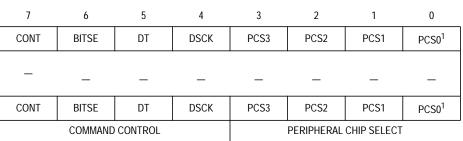

| D.7.5  | SPI Interrupt Level Register                                     |

| D.7.6  | MCCI Pin Assignment Register                                     |

| D.7.7  | MCCI Data Direction Register                                     |

| D.7.8  | MCCI Port Data RegistersD-59                                     |

| D.7.9  | SCI Control Register 0 D-59                                      |

| D.7.11 | SCI Status Register                                              |

| D.7.12 | SCI Data Register                                                |

| D.7.13 | SPI Control Register                                             |

| D.7.14 | SPI Status Register                                              |

| D.7.15 | SPI Data Register                                                |

| D.8    | General-Purpose Timer                                            |

| D.8.1  | GPT Module Configuration RegisterD-67                            |

| D.8.2  | GPT Test Register                                                |

| D.8.3  | GPT Interrupt Configuration Register                             |

| D.8.4  | Port GP Data Direction Register/Data Register                    |

| D.8.5  | OC1 Action Mask Register/Data Register                           |

| D.8.6  | Timer Counter Register                                           |

| D.8.7  | Pulse Accumulator Control Register/Counter                       |

| D.8.8  | Input Capture Registers 1–3                                      |

| D.8.9  | Output Compare Registers 1–4D-71                                 |

| D.8.10 | Input Capture 4/Output Compare 5 RegisterD-72                    |

| D.8.11 | Timer Control Registers 1 and 2 D-72                             |

| D.8.12 | Timer Interrupt Mask Registers 1 and 2 D-72                      |

| D.8.13 | Timer Interrupt Flag Registers 1 and 2D-74                       |

| D.8.14 | Compare Force Register/PWM Control Register C D-74               |

| D.8.15 | PWM Registers A/B D-76                                           |

| D.8.16 | PWM Count Register                                               |

| D.8.17 | PWM Buffer Registers A/B D-76                                    |

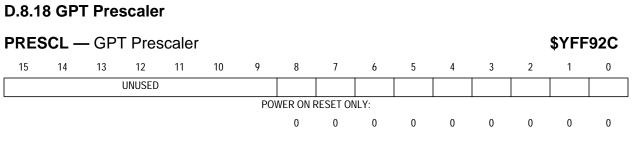

| D.8.18 | GPT Prescaler                                                    |

|        |                                                                  |

### APPENDIX E INITIALIZATION AND PROGRAMMING EXAMPLES

| E.1   | Initialization Programs |      |

|-------|-------------------------|------|

| E.1.1 | EQUATES.ASM .           |      |

| E.1.2 | ORG00000.ASM            | E-6  |

| E.1.3 | ORG00008.ASM            |      |

| E.1.4 | INITSYS.ASM             | E-11 |

### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

| E.1.5   | INITRAM.ASM                                        | E-11 |

|---------|----------------------------------------------------|------|

| E.1.6   | INITSCI.ASM                                        | E-12 |

| E.2     | Programming Examples                               | E-12 |

| E.2.1   | SIM Programming Examples                           | E-13 |

| E.2.1.1 | Example 1 - Using Ports E and F                    | E-13 |

| E.2.1.2 | Example 2 - Using Chip-Selects                     | E-14 |

| E.2.1.3 | Example 3 - Changing Clock Frequencies             | E-16 |

| E.2.1.4 | Example 4 - Software Watchdog, Periodic Interrupt, |      |

|         | and Autovector Demo                                | E-18 |

| E.2.2   | CPU16 Programming Example                          | E-23 |

| E.2.2.1 | Example 5 - Indexed and Extended Addressing        | E-23 |

| E.2.3   | QSM/SCI Programming Example                        | E-24 |

| E.2.3.1 | Example 6 - Using an SCI Port                      | E-24 |

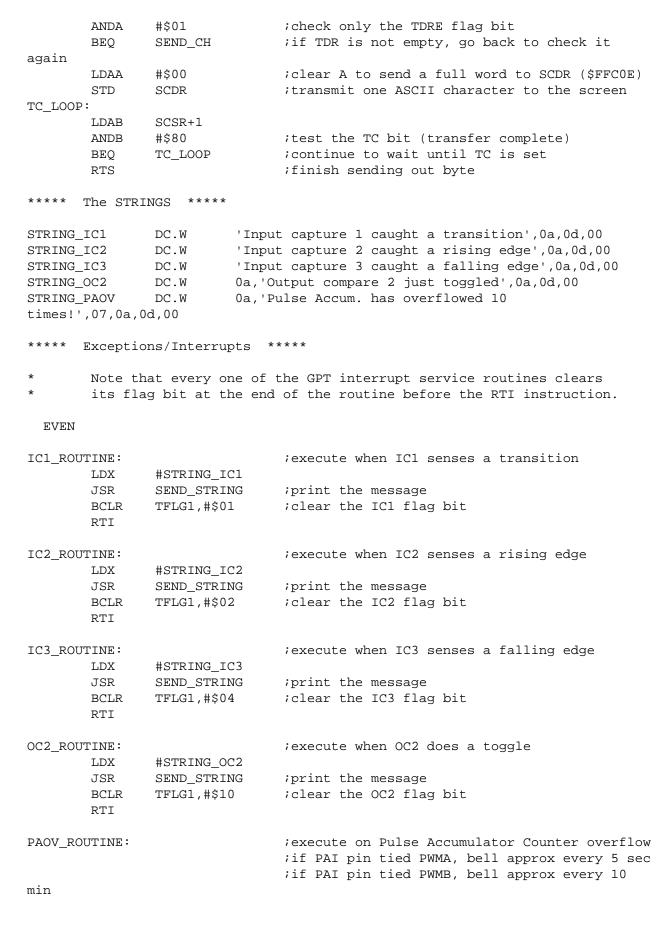

| E.2.4   | GPT Programming Example                            | E-25 |

| E.2.4.1 | Example 7 - Basic GPT Functions                    | E-25 |

|         |                                                    |      |

### LIST OF ILLUSTRATIONS

| Figure | Title                                                             | Page |

|--------|-------------------------------------------------------------------|------|

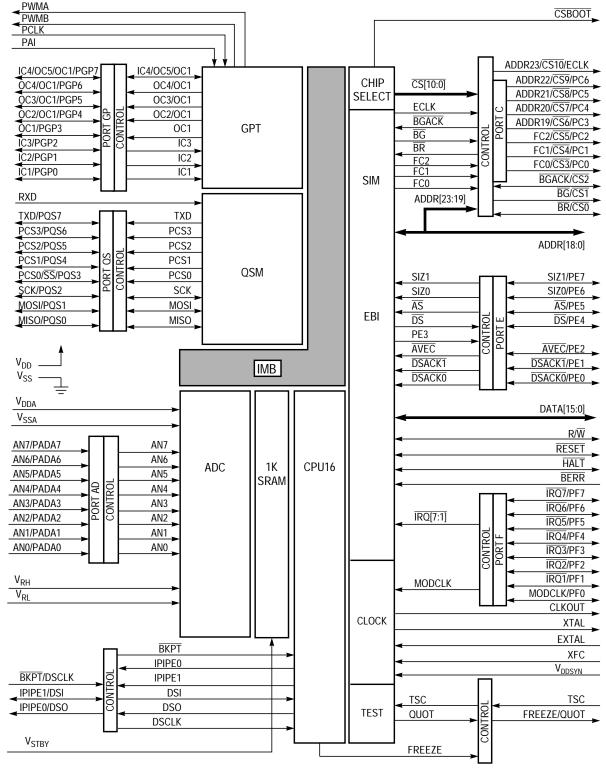

| 3-1    | MC68HC16Z1/CK16Z1/CM16Z1 Block Diagram                            |      |

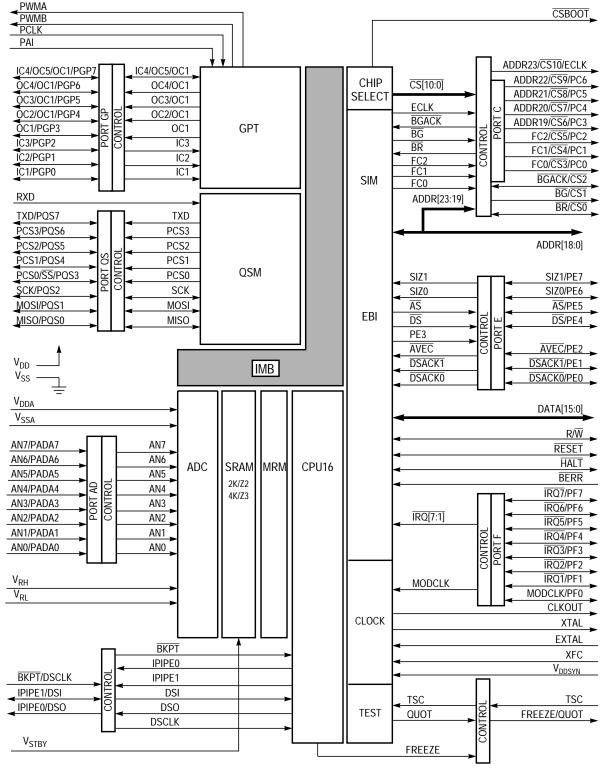

| 3-2    | MC68HC16Z2/Z3 Block Diagram                                       |      |

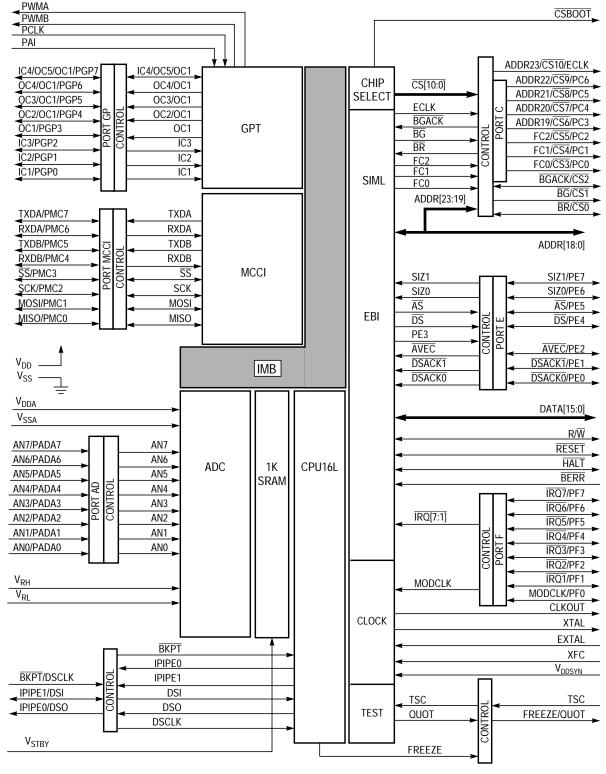

| 3-3    | MC68HC16Z4/CK16Z4 Block Diagram                                   |      |

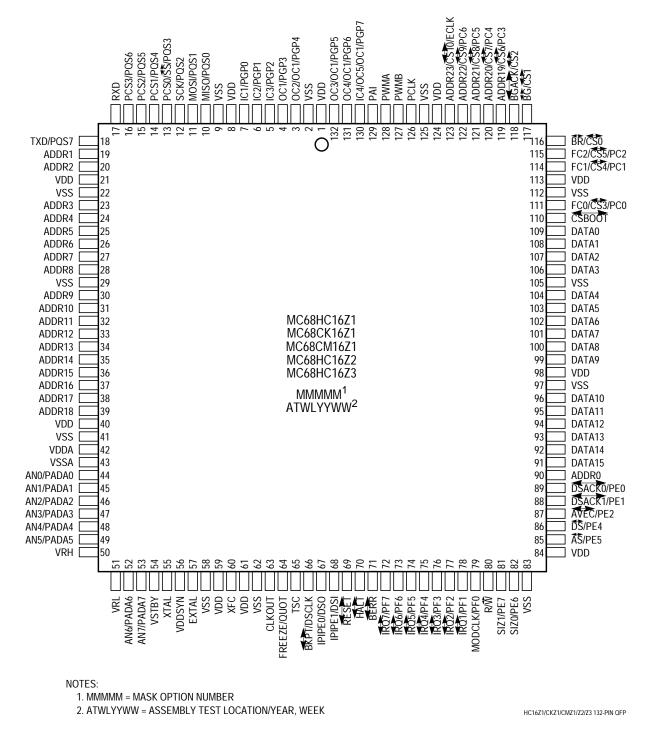

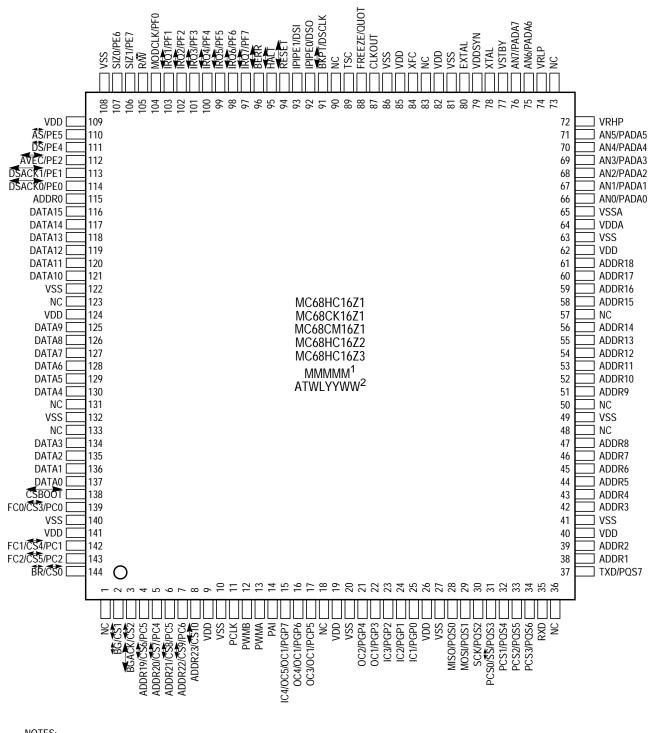

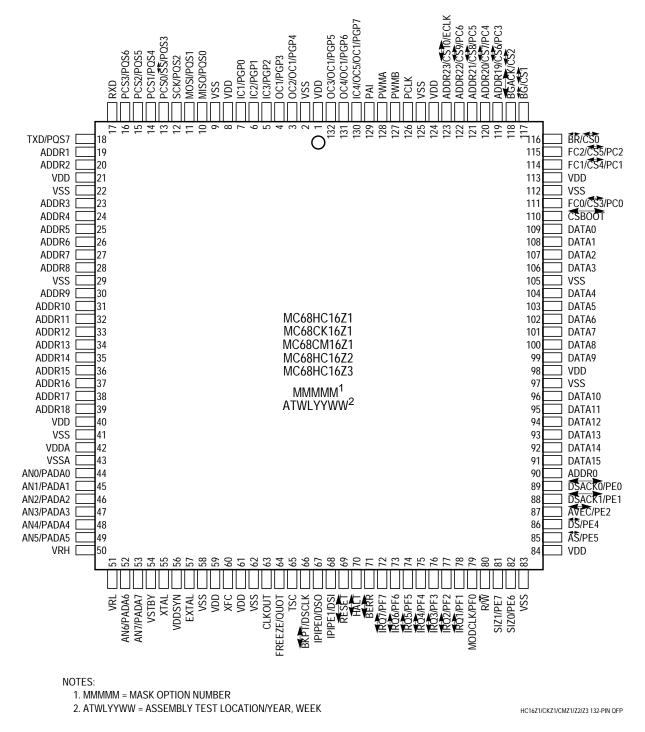

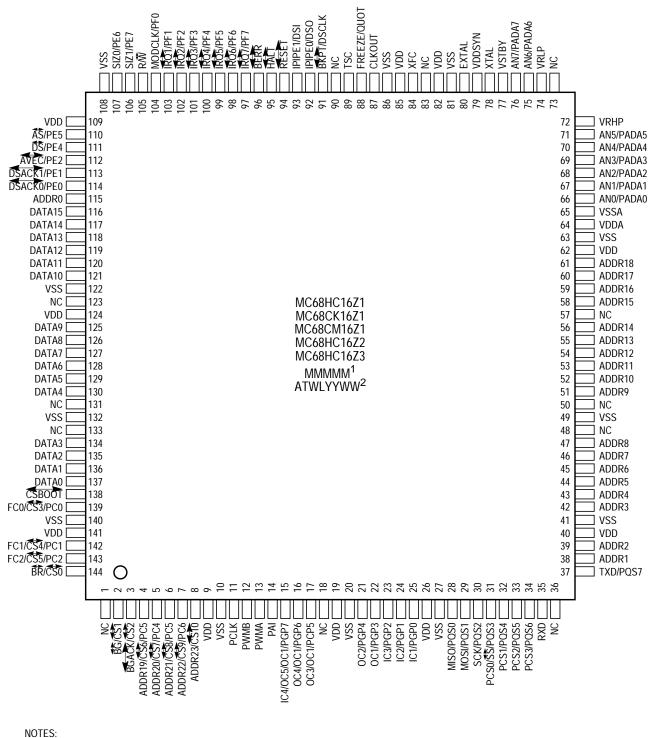

| 3-4    | MC68HC16Z1/CKZ1/CMZ1/Z2/Z3 Pin Assignments                        | 2 7  |

| 3-5    | for 132-Pin Package<br>MC68HC16Z1/CKZ1/CMZ1/Z2/Z3 Pin Assignments |      |

| 00     | for 144-Pin Package                                               |      |

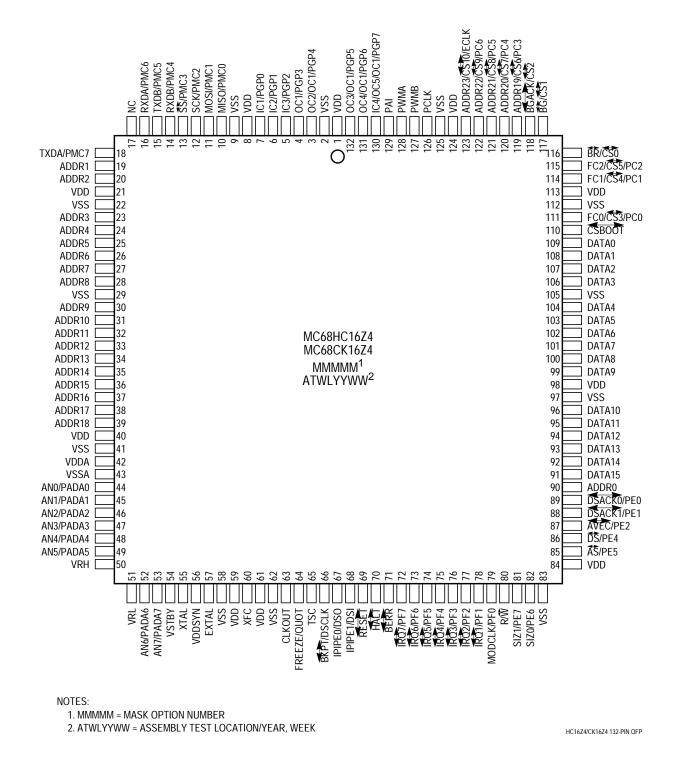

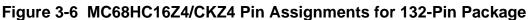

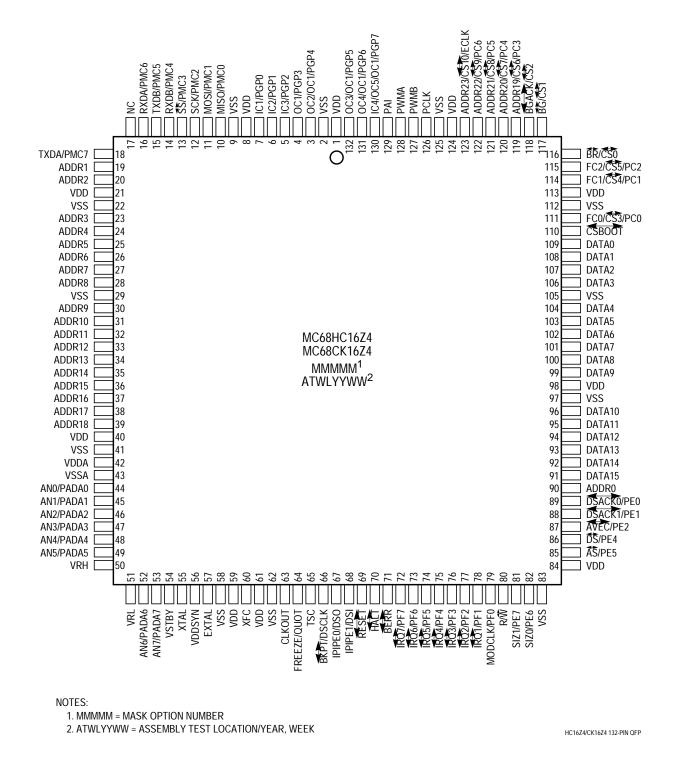

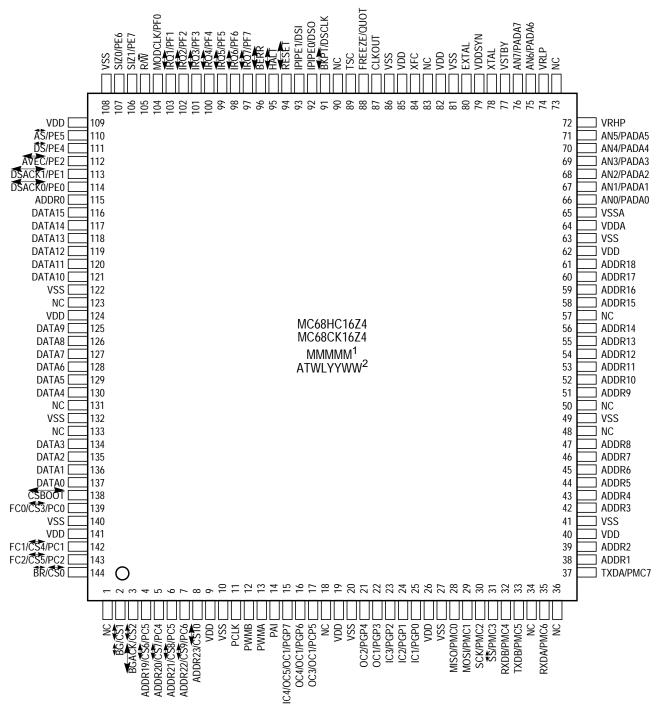

| 3-6    | MC68HC16Z4/CKZ4 Pin Assignments for 132-Pin Package               |      |

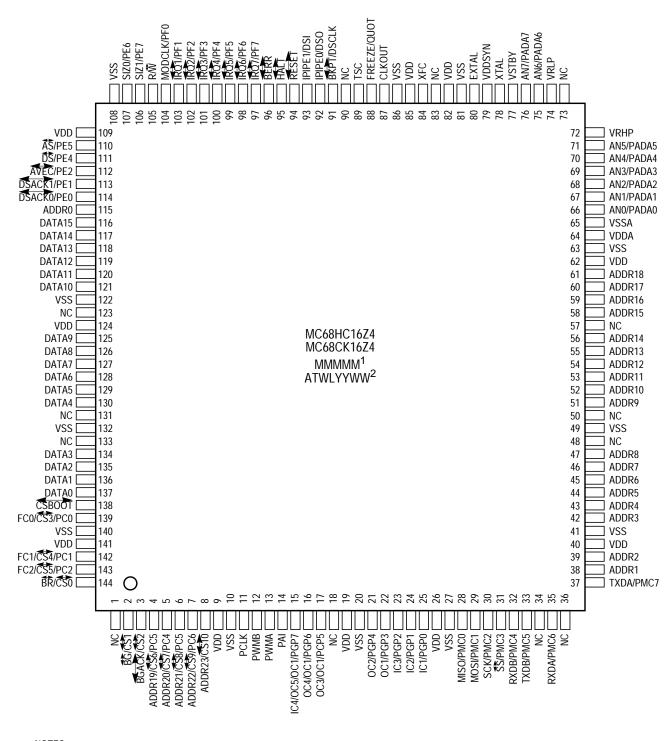

| 3-7    | MC68HC16Z4/CKZ4 Pin Assignments for 144-Pin Package               |      |

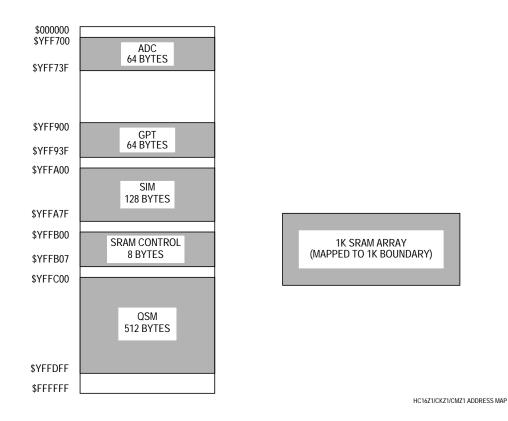

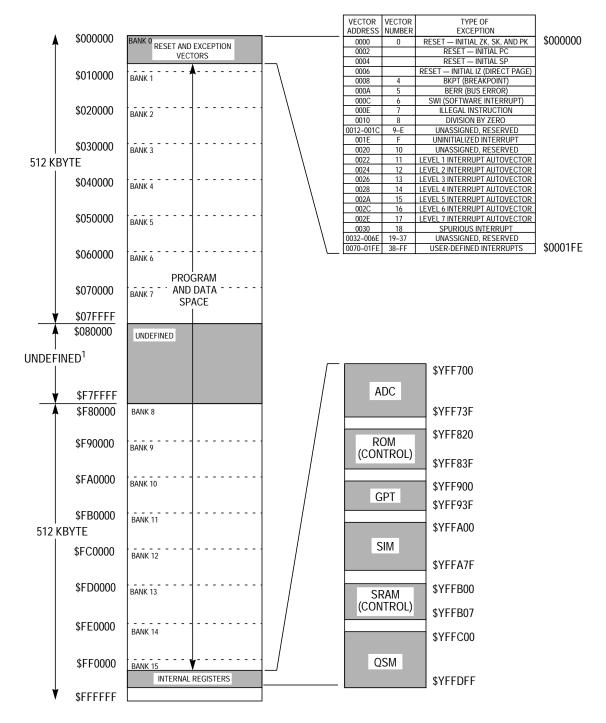

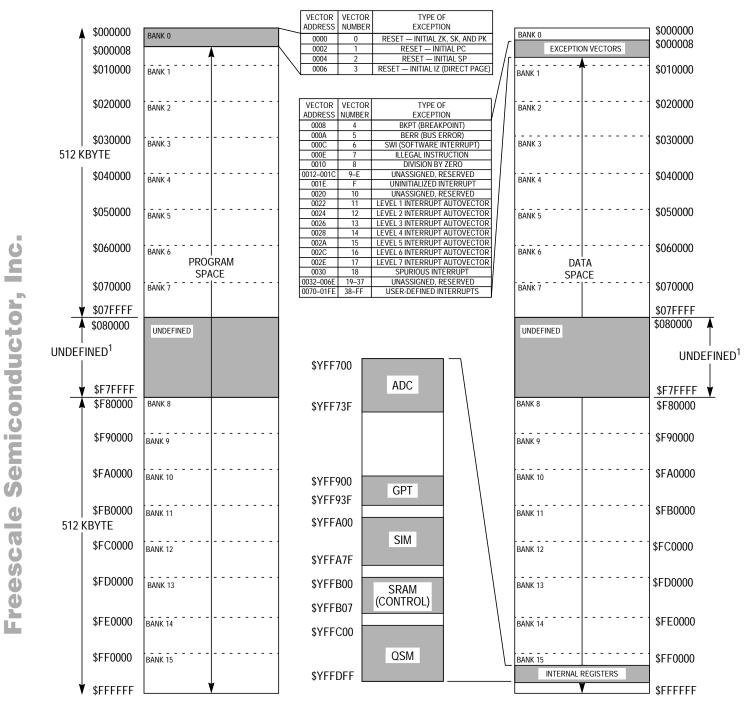

| 3-8    | MC68HC16Z1/CKZ1/CMZ1 Address Map                                  |      |

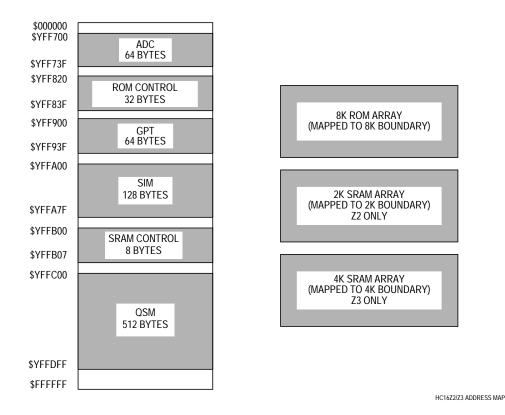

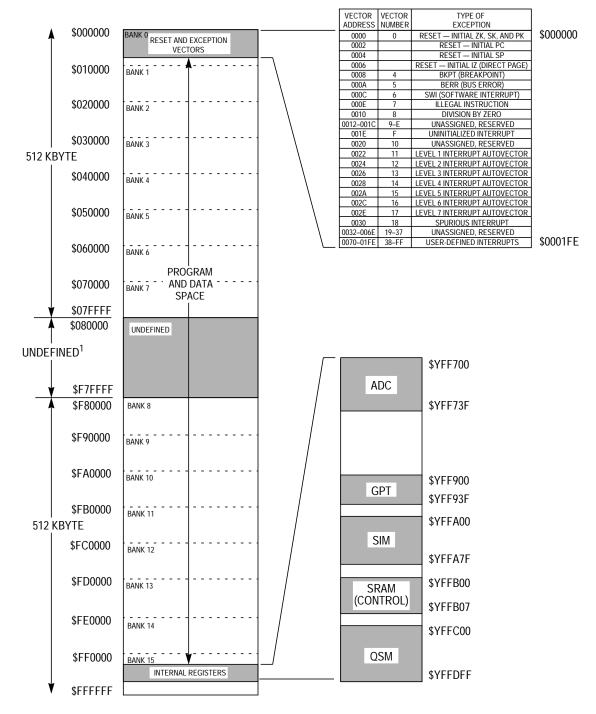

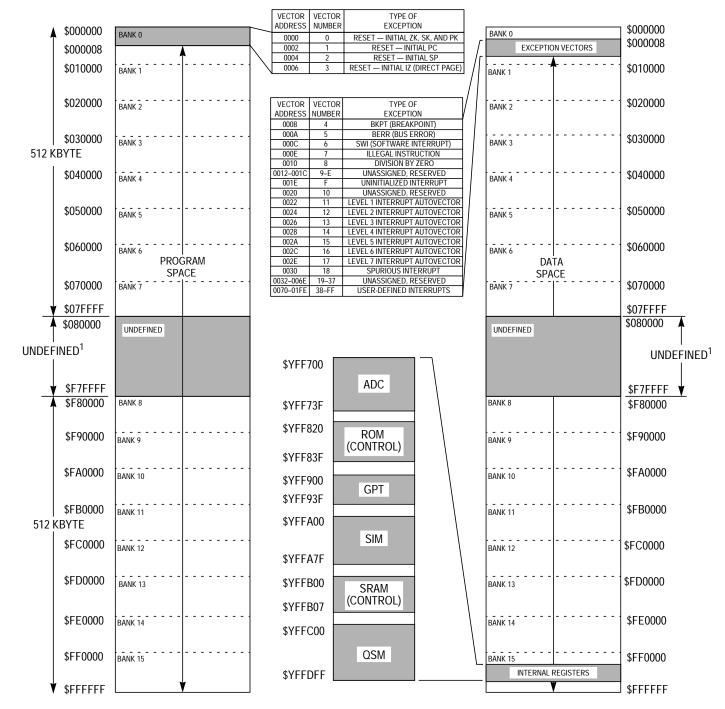

| 3-9    | MC68HC16Z2/Z3 Address Map                                         |      |

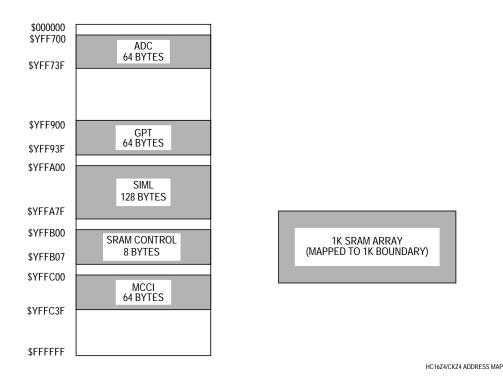

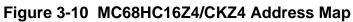

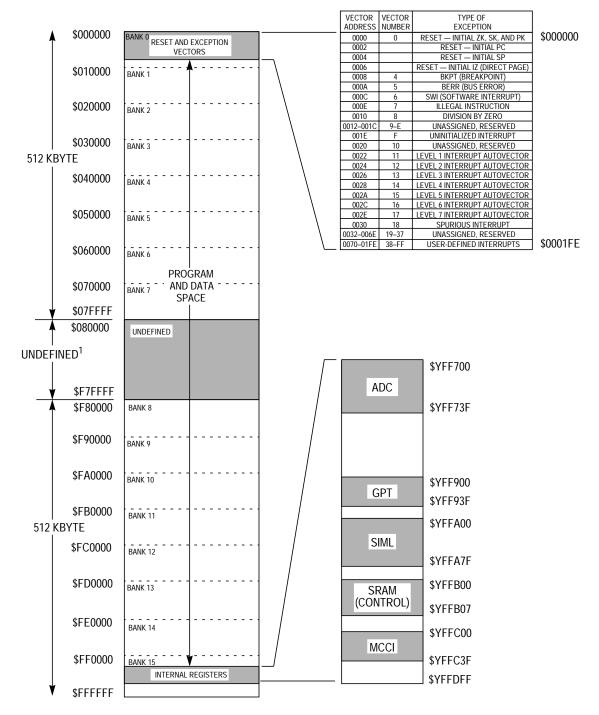

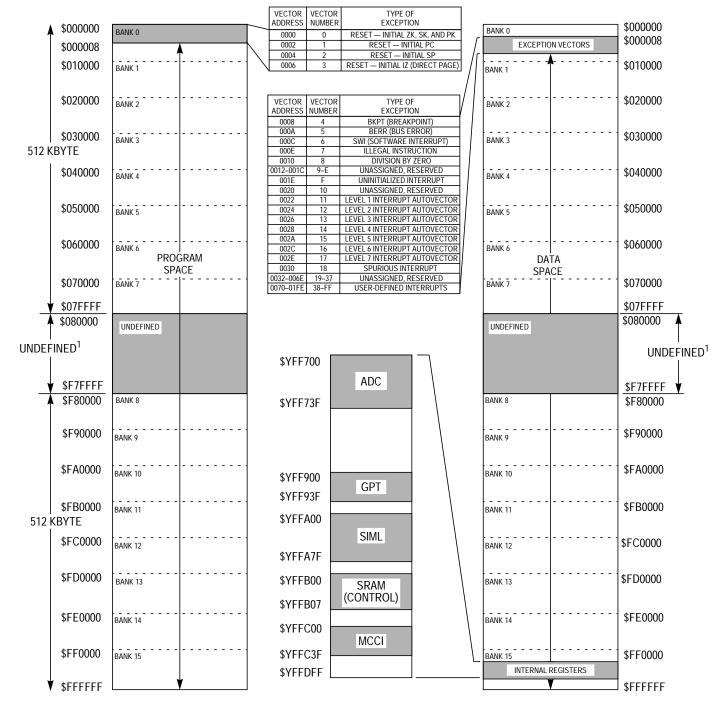

| 3-10   | MC68HC16Z4/CKZ4 Address Map                                       |      |

| 3-11   | MC68HC16Z1/CKZ1/CMZ1 Combined Program                             |      |

|        | and Data Space Map                                                |      |

| 3-12   | MC68HC16Z2/Z3 Combined Program and Data Space Map                 |      |

| 3-13   | MC68HC16Z4/CKZ4 Combined Program and Data Space Map               |      |

| 3-14   | MC68HC16Z1/CKZ1/CMZ1 Separate Program                             |      |

|        | and Data Space Map                                                |      |

| 3-15   | MC68HC16Z2/Z3 Separate Program and Data Space Map                 |      |

| 3-16   | MC68HC16Z4/CKZ4 Separate Program and Data Space Map               |      |

| 4-1    | CPU16 Register Model                                              |      |

| 4-2    | Condition Code Register                                           |      |

| 4-3    | Data Types and Memory Organization                                | 4-8  |

| 4-4    | Basic Instruction Formats                                         | 4-34 |

| 4-5    | Instruction Execution Model                                       | 4-35 |

| 4-6    | Exception Stack Frame Format                                      |      |

| 4-7    | BDM Serial I/O Block Diagram                                      |      |

| 4-8    | BDM Connector Pinout                                              |      |

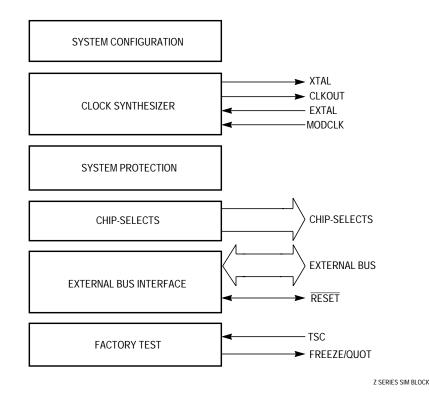

| 5-1    | System Integration Module Block Diagram                           |      |

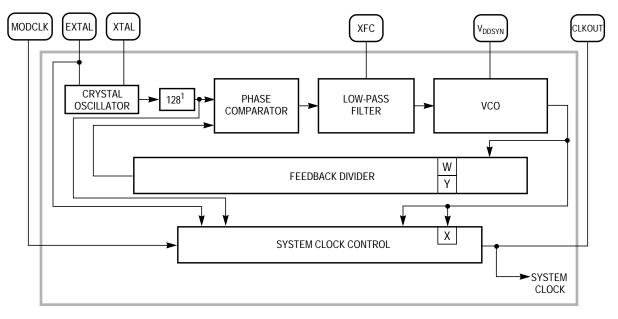

| 5-2    | System Clock Block Diagram                                        |      |

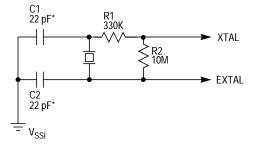

| 5-3    | Slow Reference Crystal Circuit                                    |      |

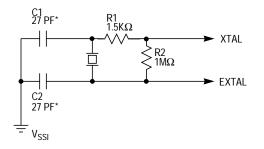

| 5-4    | Fast Reference Crystal Circuit                                    |      |

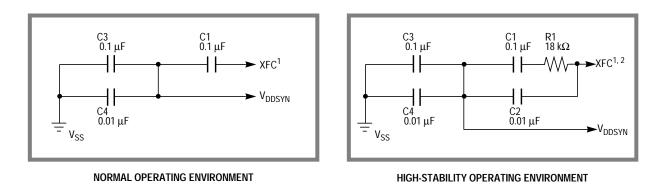

| 5-5    | System Clock Filter Networks                                      | 5-7  |

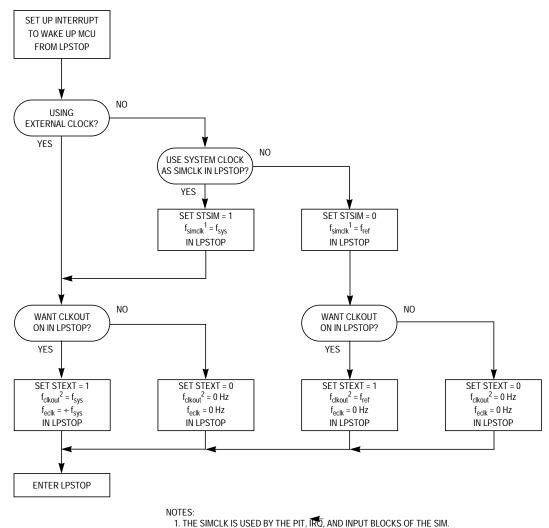

| 5-6    | SIM LPSTOP Flowchart                                              |      |

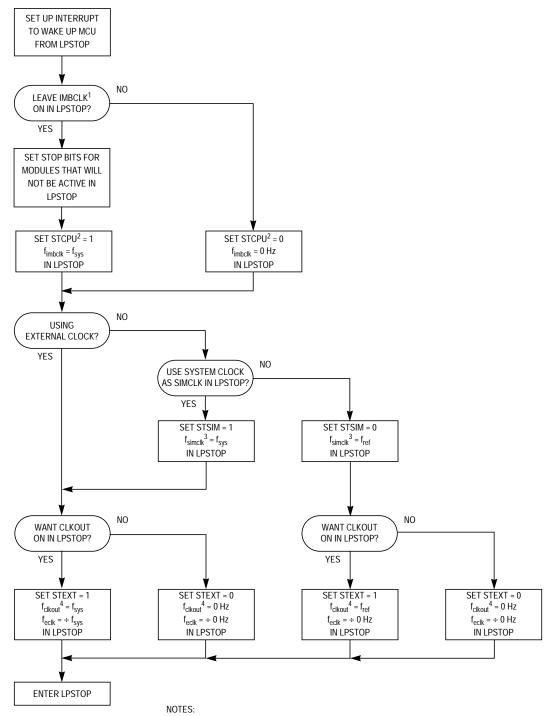

| 5-7    | SIML LPSTOP Flowchart                                             | 5-23 |

| 5-8    | System Protection                                                 | 5-24 |

| 5-9    | Periodic Interrupt Timer and Software Watchdog Timer              | 5-27 |

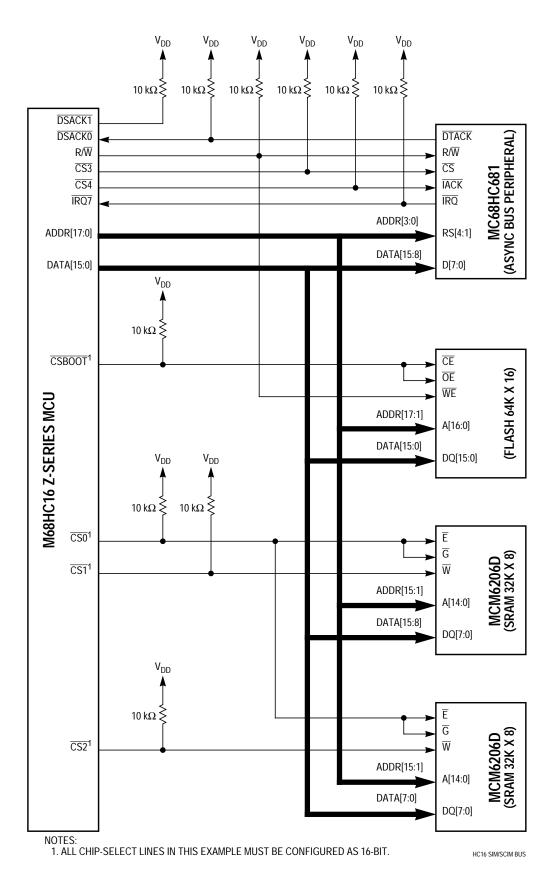

| 5-10   | MCU Basic System                                                  | 5-30 |

| 5-11   | Operand Byte Order                                                | 5-34 |

|        |                                                                   |      |

### LIST OF ILLUSTRATIONS (Continued) Title

### Figure

Page

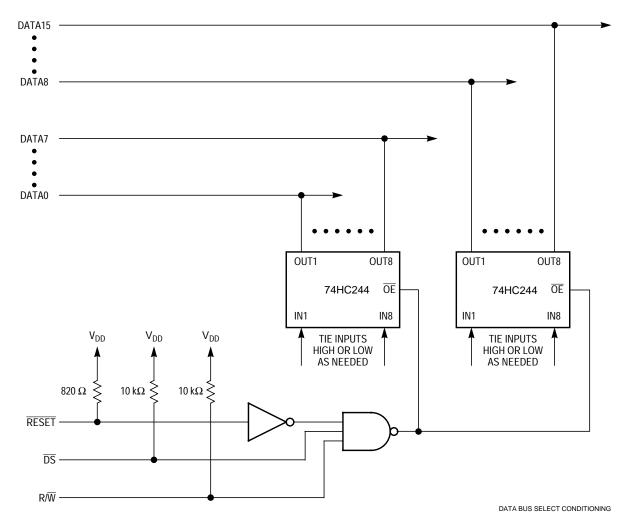

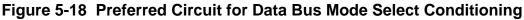

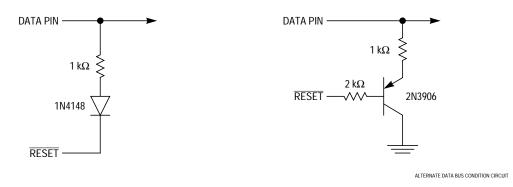

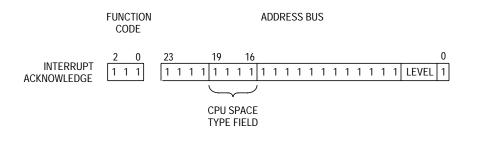

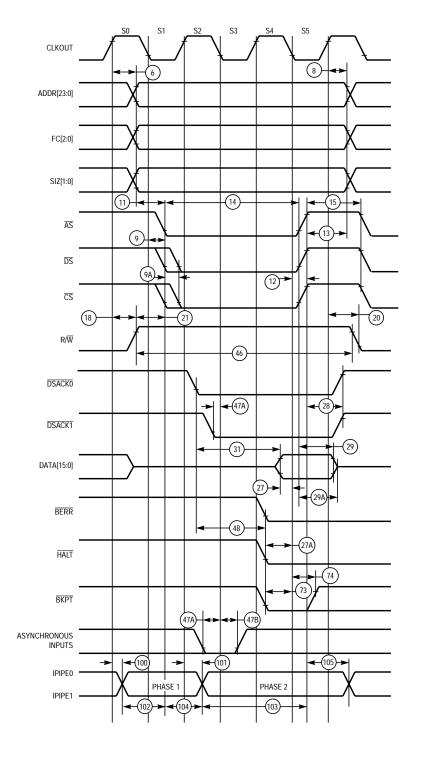

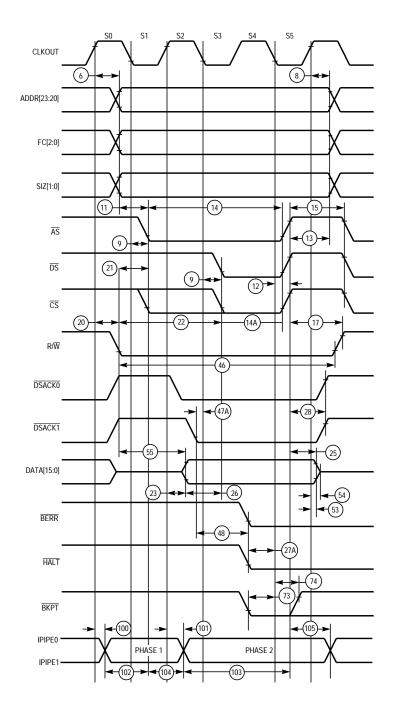

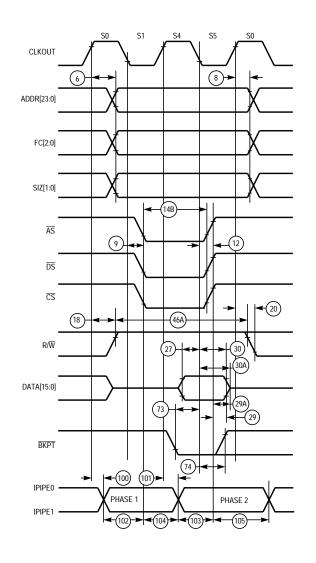

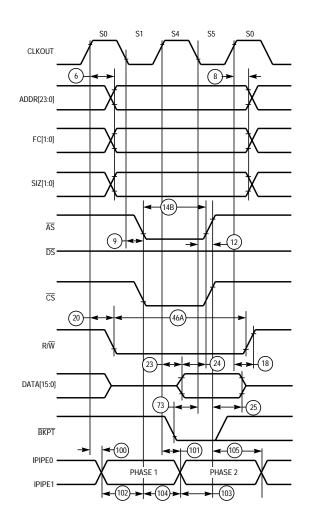

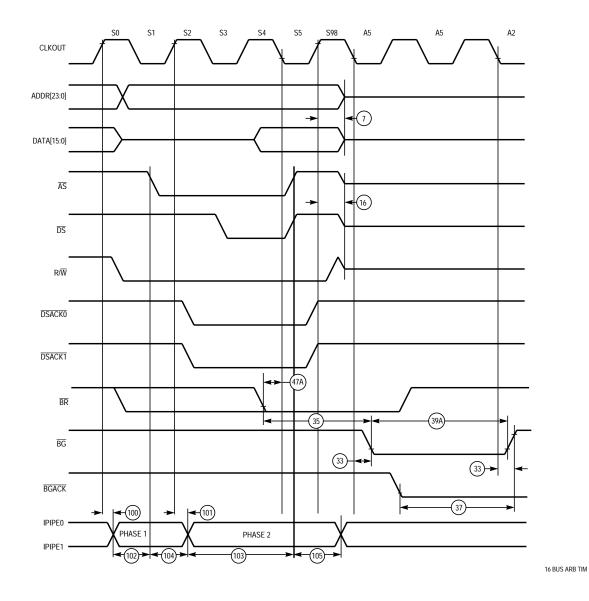

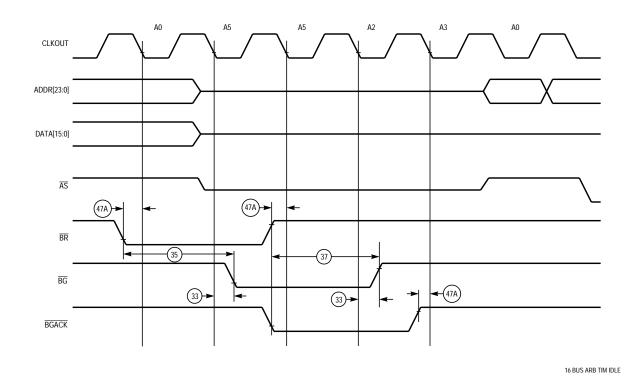

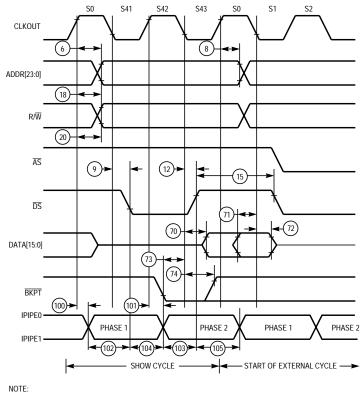

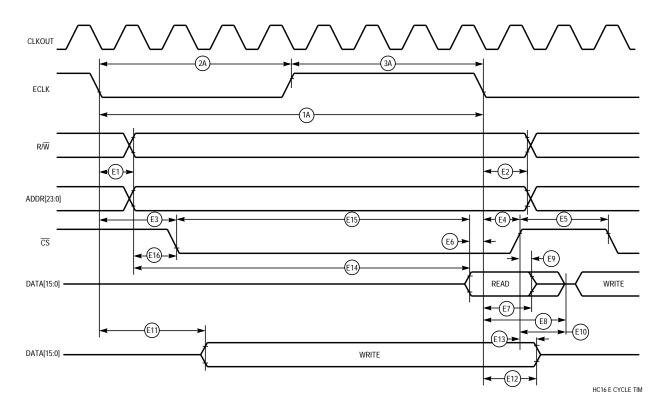

| 5-12<br>5-13<br>5-14<br>5-15<br>5-16<br>5-17<br>5-18<br>5-19<br>5-20<br>5-21<br>5-22<br>5-23 | Word Read Cycle Flowchart5-38Write Cycle Flowchart5-39CPU Space Address Encoding5-47Breakpoint Operation Flowchart5-42LPSTOP Interrupt Mask Level5-42Bus Arbitration Flowchart for Single Request5-47Preferred Circuit for Data Bus Mode Select Conditioning5-57Alternate Circuit for Data Bus Mode Select Conditioning5-56Basic MCU System5-62Chip-Select Circuit Block Diagram5-62CPU Space Encoding for Interrupt Acknowledge5-68                     | 9<br>1<br>2<br>3<br>7<br>0<br>1<br>6<br>2<br>3 |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

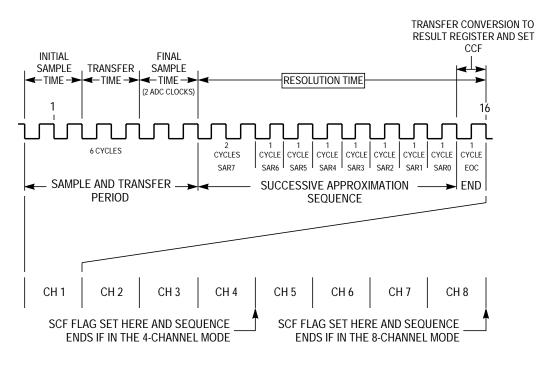

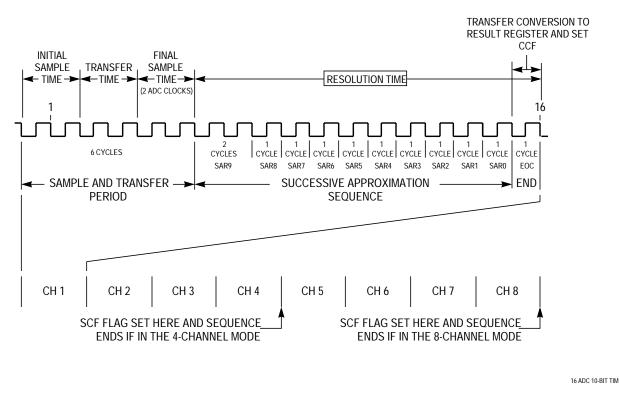

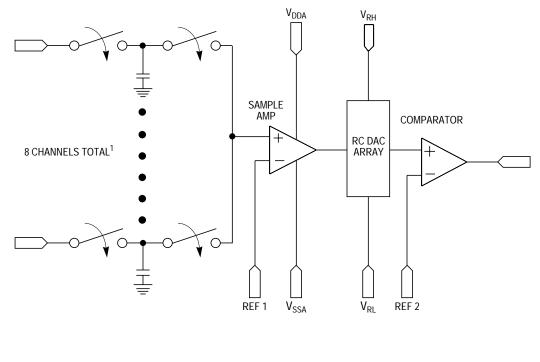

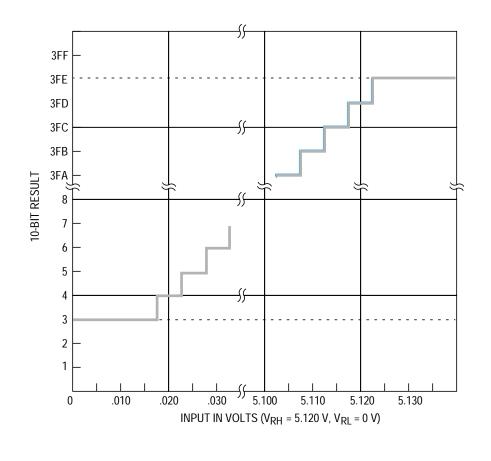

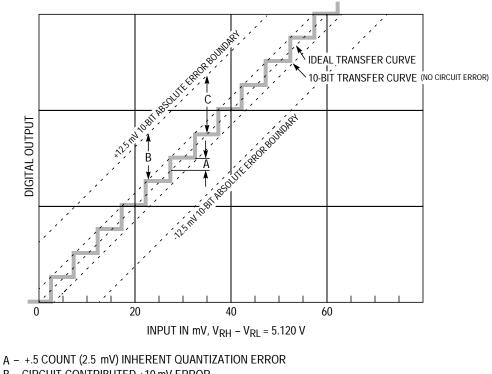

| 8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-5<br>8-6<br>8-7<br>8-8<br>8-9<br>8-10                   | ADC Block Diagram8-28-Bit Conversion Timing8-1210-Bit Conversion Timing8-1310-Bit Conversion Timing8-14Analog Input Circuitry8-16Errors Resulting from Clipping8-16Star-Ground at the Point of Power Supply Origin8-17Input Pin Subjected to Negative Stress8-18Voltage Limiting Diodes in a Negative Stress Circuit8-18External Multiplexing of Analog Signal Sources8-20Electrical Model of an A/D Input Pin8-27                                       | 2<br>3<br>5<br>6<br>7<br>8<br>9<br>0           |

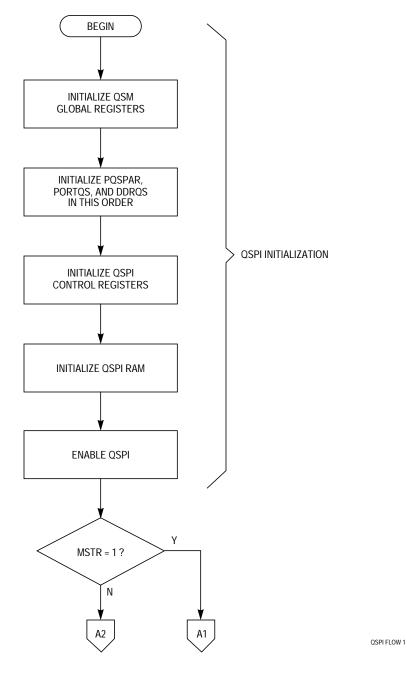

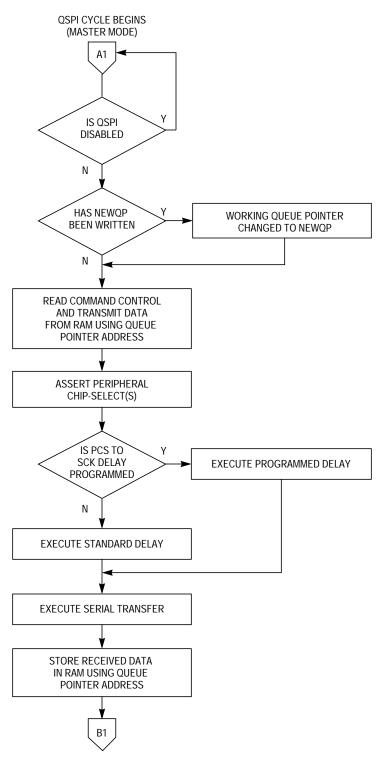

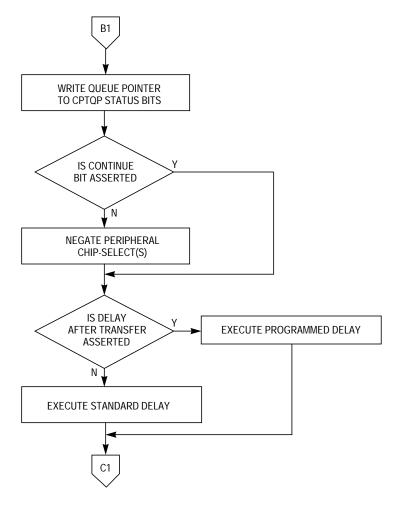

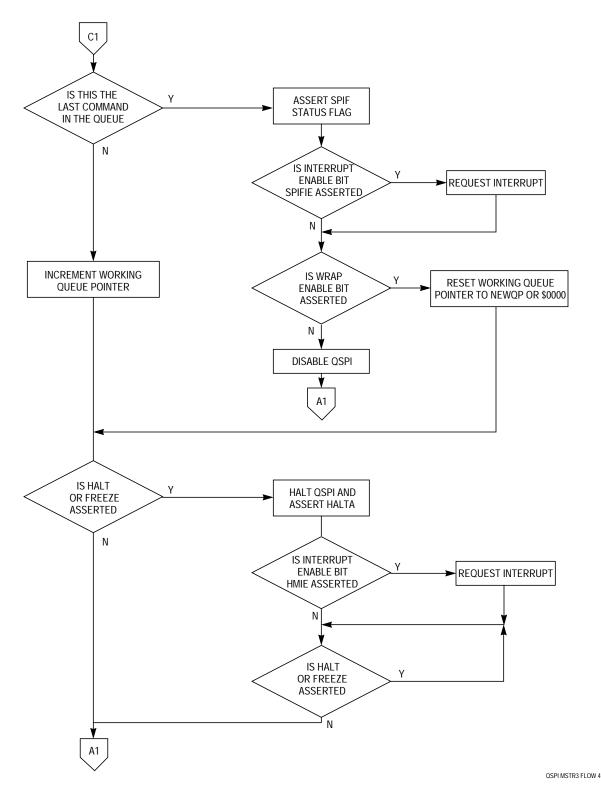

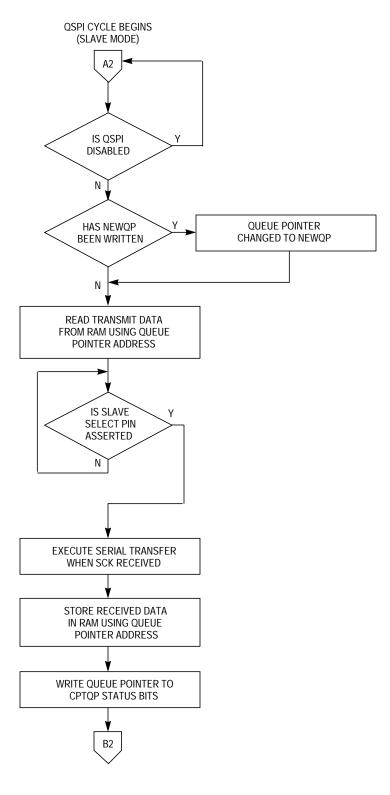

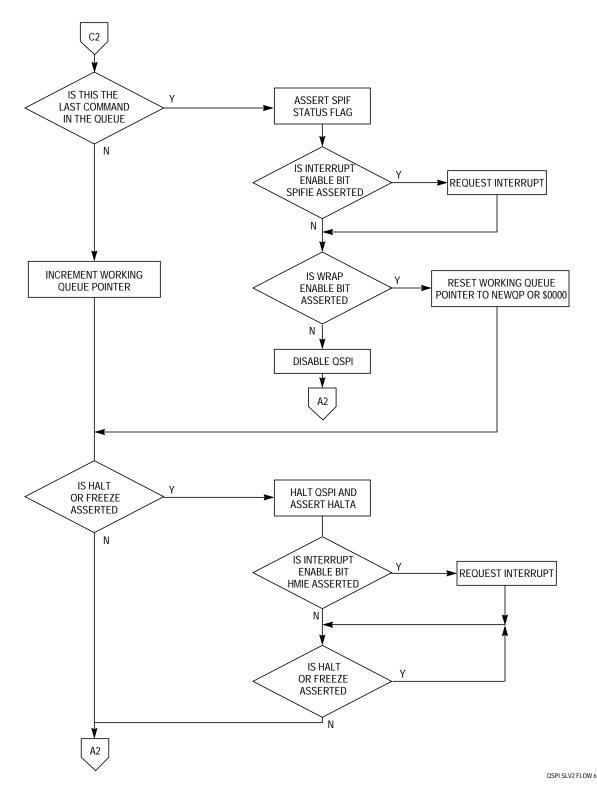

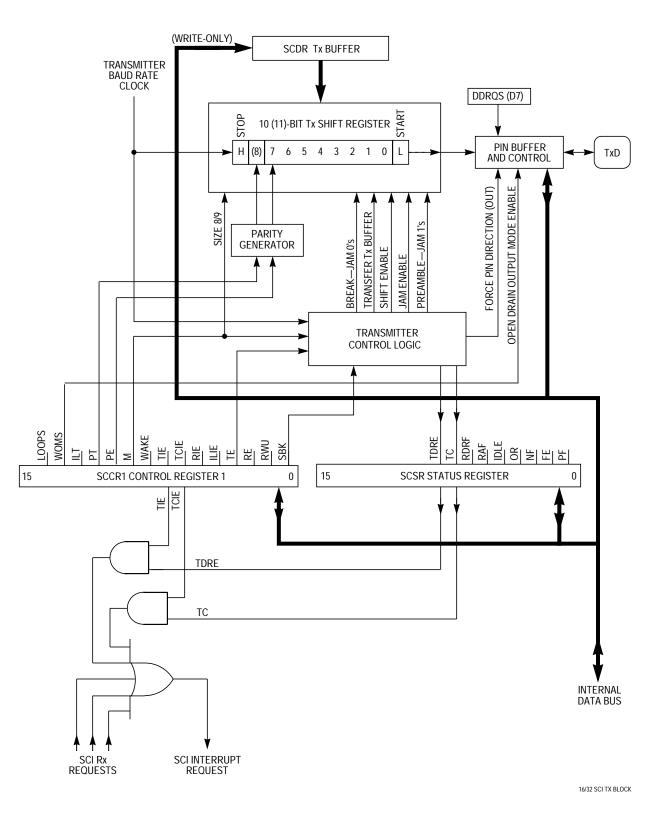

| 9-1<br>9-2<br>9-3<br>9-4<br>9-5<br>9-6<br>9-7<br>9-8<br>9-9<br>9-10<br>9-11                  | QSM Block Diagram9-7QSPI Block Diagram9-8QSPI RAM9-7Flowchart of QSPI Initialization Operation9-10Flowchart of QSPI Master Operation (Part 1)9-17Flowchart of QSPI Master Operation (Part 2)9-12Flowchart of QSPI Master Operation (Part 3)9-12Flowchart of QSPI Slave Operation (Part 1)9-14Flowchart of QSPI Slave Operation (Part 1)9-14Flowchart of QSPI Slave Operation (Part 2)9-14SCI Transmitter Block Diagram9-24SCI Receiver Block Diagram9-24 | 5<br>7<br>0<br>1<br>2<br>3<br>4<br>5<br>2      |

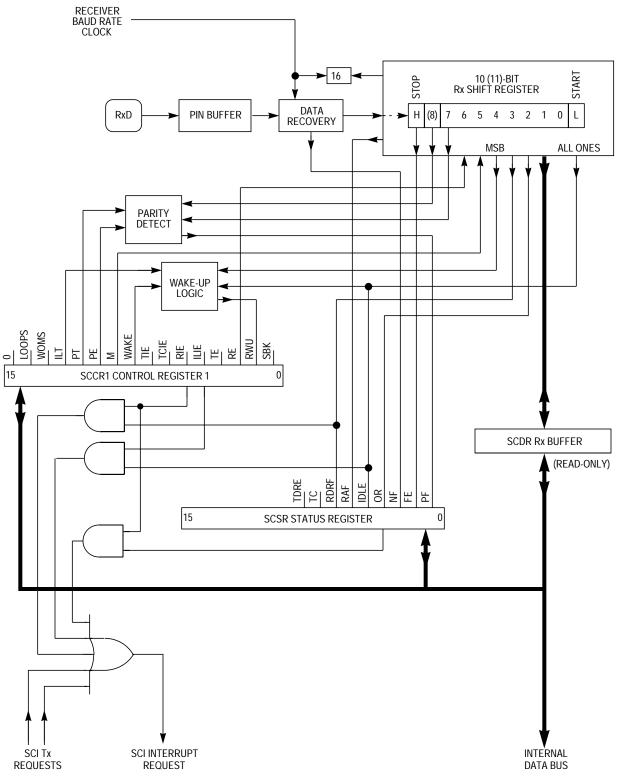

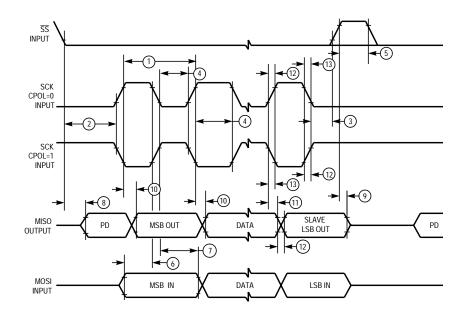

| 10-1<br>10-2<br>10-3<br>10-4<br>10-5                                                         | MCCI Block Diagram10-7SPI Block Diagram10-8CPHA = 0 SPI Transfer Format10-9CPHA = 1 SPI Transfer Format10-10SCI Transmitter Block Diagram10-10                                                                                                                                                                                                                                                                                                           | 5<br>9<br>0                                    |

### LIST OF ILLUSTRATIONS (Continued) Title

### Figure

| 10-6                                                                                                                                                                                                                | SCI Receiver Block Diagram 10-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

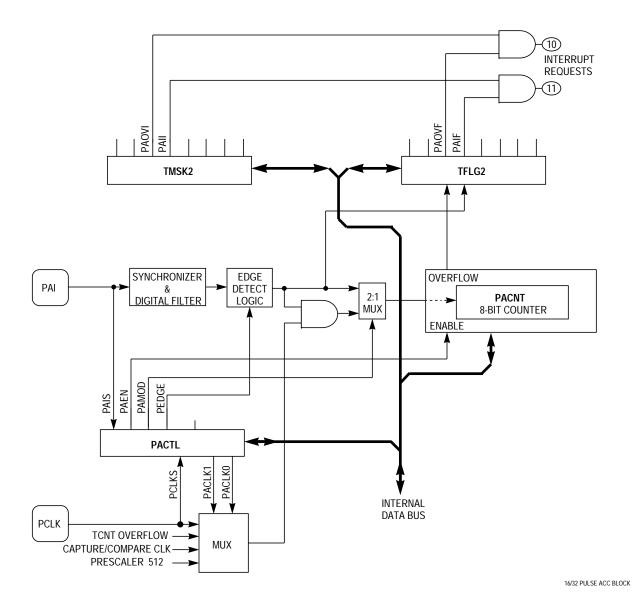

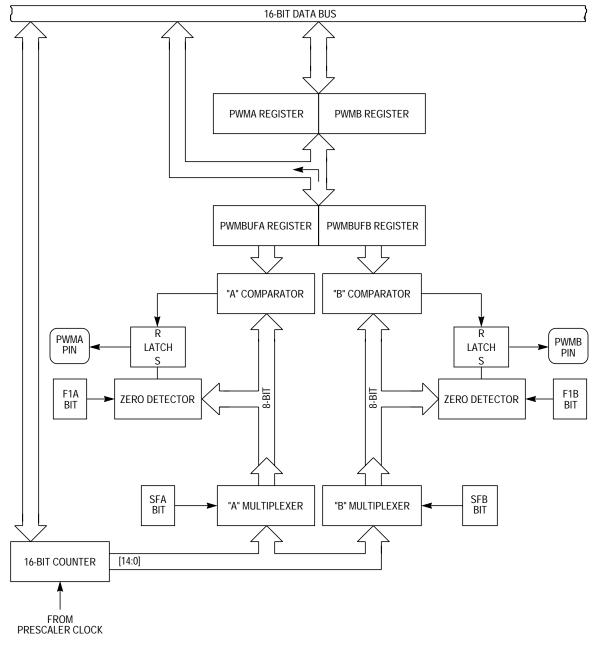

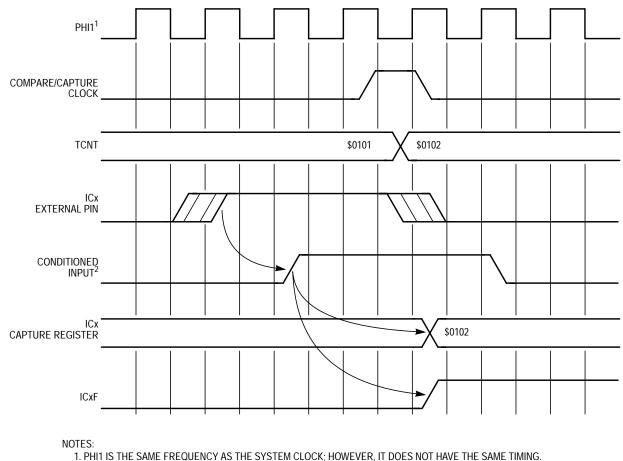

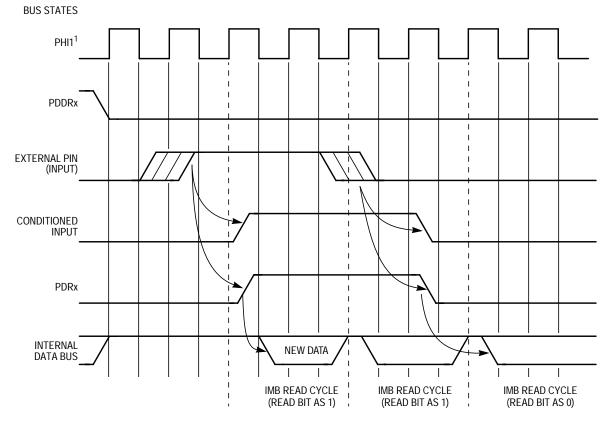

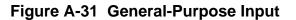

| 11-1<br>11-2<br>11-3<br>11-4<br>11-5<br>11-6                                                                                                                                                                        | GPT Block Diagram11-2Prescaler Block Diagram11-9Capture/Compare Unit Block Diagram11-11Input Capture Timing Example11-13Pulse Accumulator Block Diagram11-15PWM Block Diagram11-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

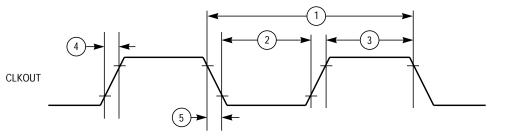

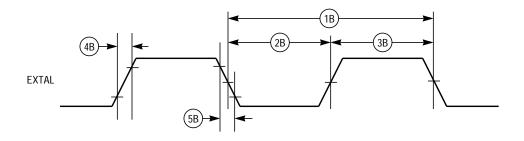

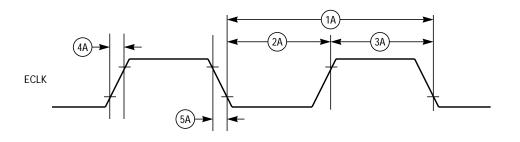

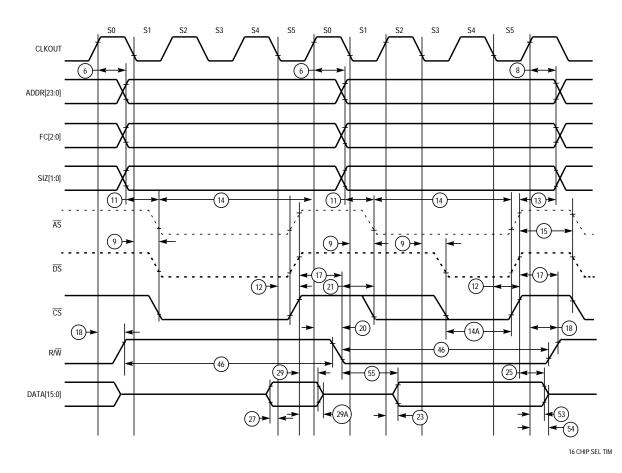

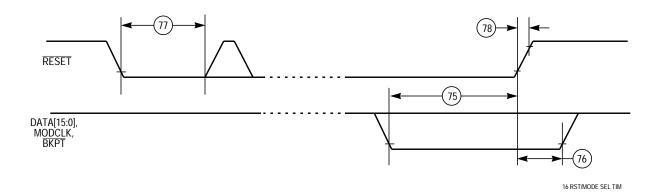

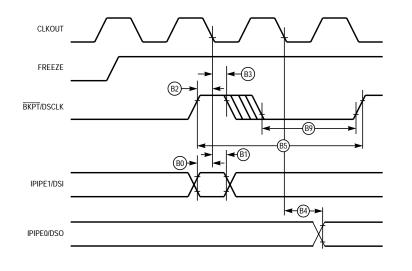

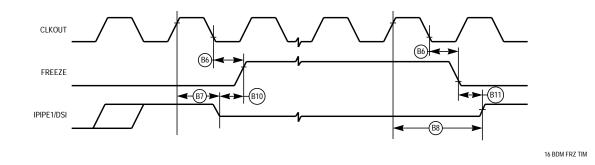

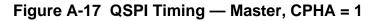

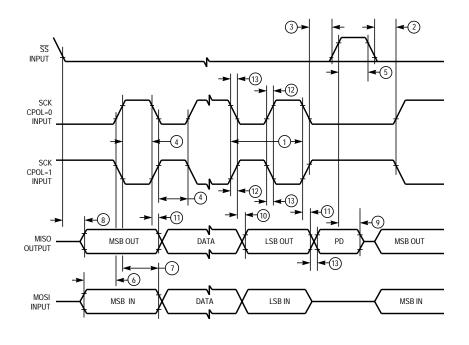

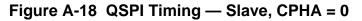

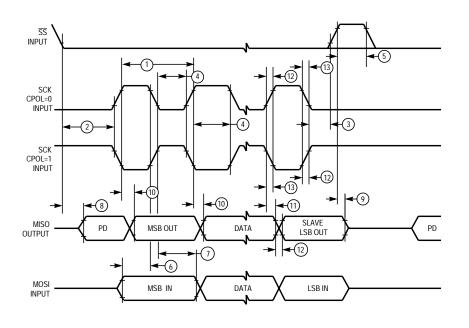

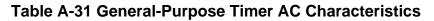

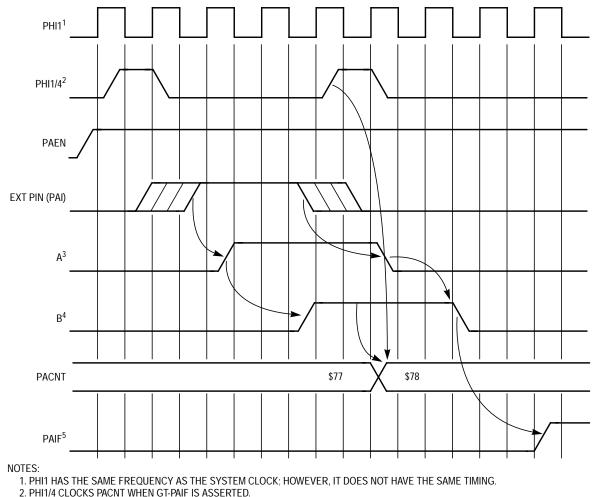

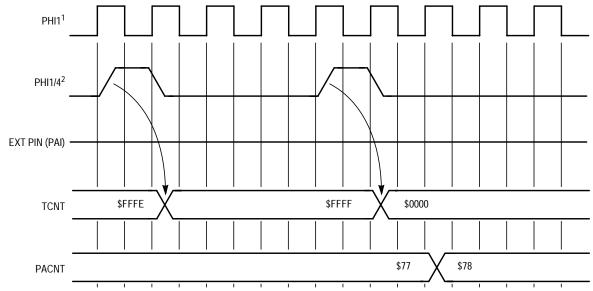

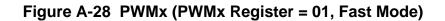

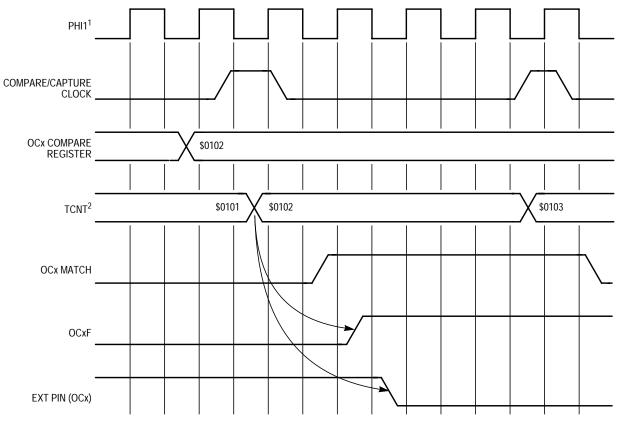

| A-1<br>A-2<br>A-3<br>A-4<br>A-5<br>A-6<br>A-7<br>A-8<br>A-9<br>A-10<br>A-12<br>A-13<br>A-14<br>A-15<br>A-16<br>A-17<br>A-18<br>A-20<br>A-21<br>A-23<br>A-24<br>A-25<br>A-26<br>A-27<br>A-28<br>A-29<br>A-30<br>A-31 | CLKOUT Output Timing DiagramA-28External Clock Input Timing DiagramA-28ECLK Output Timing DiagramA-28Read Cycle Timing DiagramA-29Write Cycle Timing DiagramA-30Fast Termination Read Cycle Timing DiagramA-31Fast Termination Write Cycle Timing DiagramA-32Bus Arbitration Timing DiagramA-32Bus Arbitration Timing DiagramA-diteBus Arbitration Timing DiagramA-35Chip-Select Timing DiagramA-36Reset and Mode Select Timing DiagramA-36Background Debug Mode Timing DiagramA-44QSPI Timing — Master, CPHA = 0A-47QSPI Timing — Master, CPHA = 1A-44QSPI Timing — Slave, CPHA = 1A-48QSPI Timing — Master, CPHA = 0A-51SPI Timing — Slave, CPHA = 1A-51SPI Timing — Slave, CPHA = 1A-52SPI Timing — Slave, CPHA = 1A-53SPUSe Accumulator — Event Counting Mode (Leading Edge)A-54Pulse Accumulator — Event |

| A-32                                                                                                                                                                                                                | General-Purpose Output (Causes Input Capture)A-60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### LIST OF ILLUSTRATIONS (Continued) Title

### Figure

Page

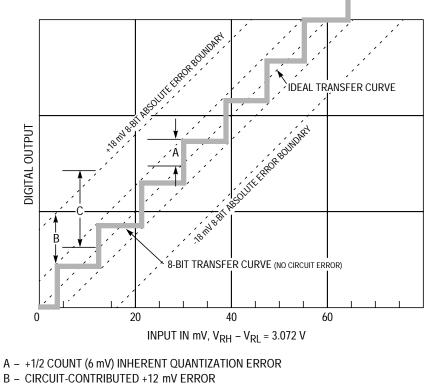

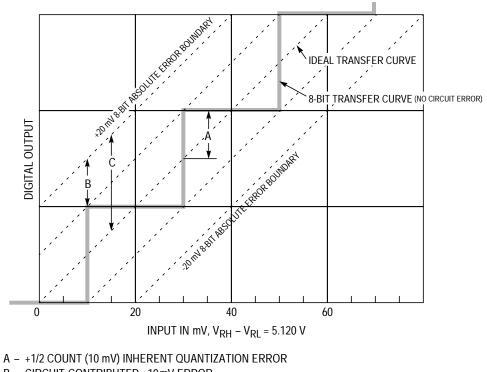

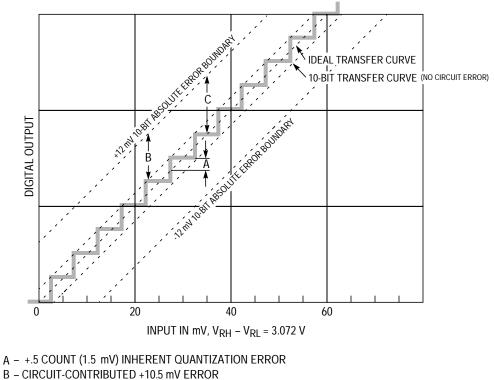

| A-33<br>A-34<br>A-35<br>A-36<br>A-37 | Force Compare (CLEAR)<br>Low Voltage 8-Bit ADC Conversion Accuracy | A-68<br>A-69<br>A-70 |

|--------------------------------------|--------------------------------------------------------------------|----------------------|

| B-1                                  | MC68HC16Z1/CKZ1/CMZ1/Z2/Z3 Pin Assignments                         | <b>D</b> o           |

|                                      | for 132-Pin Package                                                |                      |

| B-2                                  | MC68HC16Z4/CKZ4 Pin Assignments for 132-Pin Package                | B-3                  |

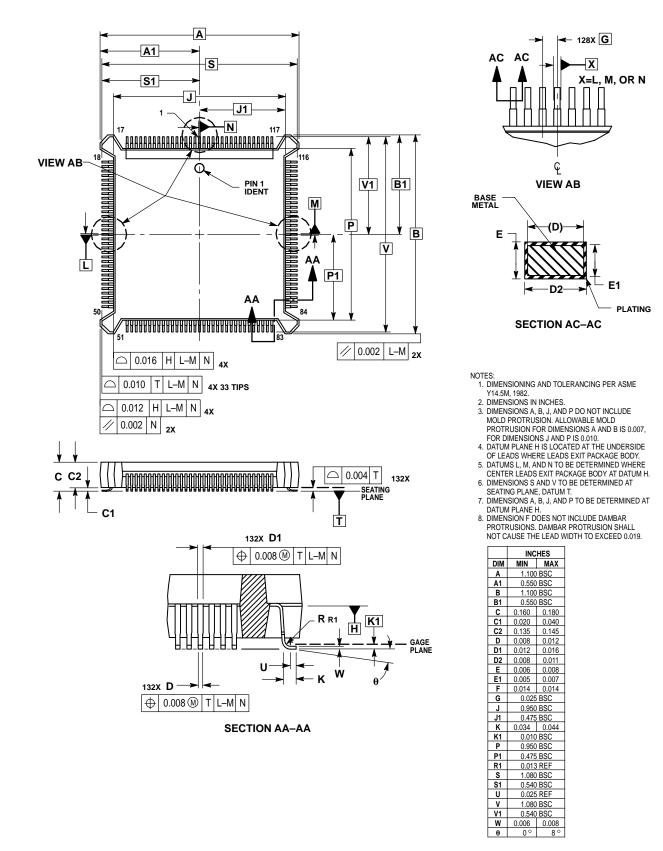

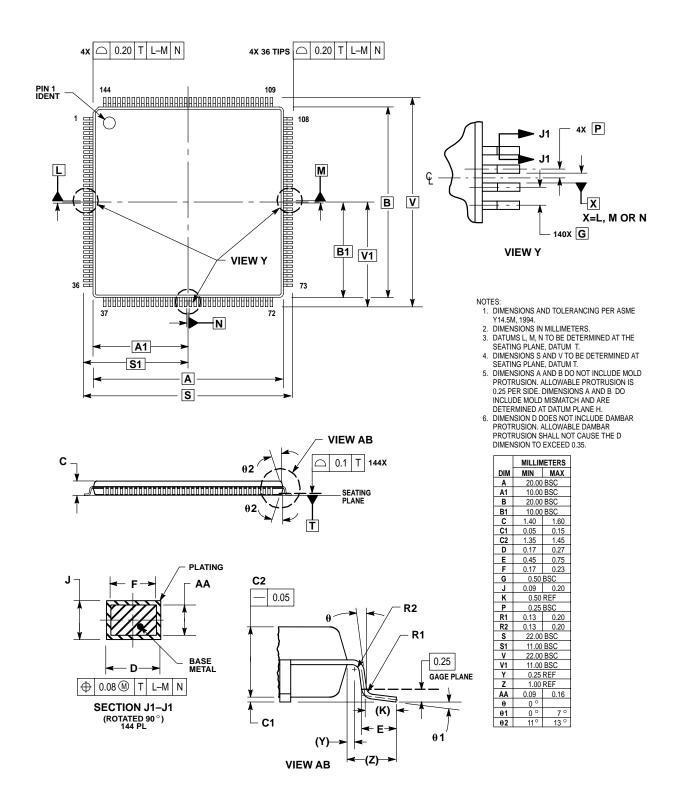

| B-3                                  | Case 831A-01 — 132-Pin Package Dimensions                          | B-4                  |

| B-4                                  | MC68HC16Z1/CKZ1/CMZ1/Z2/Z3 Pin Assignments                         |                      |

|                                      | for 144-Pin Package                                                | B-5                  |

| B-5                                  | MC68HC16Z4/CKZ4 Pin Assignments for 144-Pin Package                |                      |

| B-6                                  | Case 918 — 144-Pin Package Dimensions                              | B-7                  |

| D-1                                  | CPU16 Register Model                                               | D-2                  |

### LIST OF TABLES

| Table | Title                                            | Page |

|-------|--------------------------------------------------|------|

| 1-1   | M68HC16 Z-Series MCUs                            | 1-1  |

| 1-2   | Z-Series MCU Reference Frequencies               | 1-2  |

| 3-1   | M68HC16 Z-Series Pin Characteristics             |      |

| 3-2   | M68HC16 Z-Series Driver Types                    |      |

| 3-3   | M68HC16 Z-Series Power Connections               |      |

| 3-4   | M68HC16 Z-Series Signal Characteristics          |      |

| 3-5   | M68HC16 Z-Series Signal Function                 |      |

| 4-1   | Addressing Modes                                 |      |

| 4-2   | Instruction Set Summary                          |      |

| 4-3   | Instruction Set Abbreviations and Symbols        |      |

| 4-4   | CPU16 Implementation of M68HC11 CPU Instructions |      |

| 4-5   | Exception Vector Table                           |      |

| 4-6   | IPIPE0/IPIPE1 Encoding                           |      |

| 4-7   | Command Summary                                  |      |

| 5-1   | Show Cycle Enable Bits                           |      |

| 5-2   | 16.78-MHz Clock Control Multipliers              |      |

| 5-3   | 20.97-MHz Clock Control Multipliers              |      |

| 5-4   | 25.17-MHz Clock Control Multipliers              |      |

| 5-5   | 16.78-MHz System Clock Frequencies               |      |

| 5-6   | System Clock Frequencies for a 20.97-MHz System  |      |

| 5-7   | System Clock Frequencies for a 25.17-MHz System  |      |

| 5-8   | Bus Monitor Period                               |      |

| 5-9   | MODCLK Pin and SWP Bit During Reset              |      |

| 5-10  | Software Watchdog Divide Ratio                   |      |

| 5-11  | MODCLK Pin and PTP Bit at Reset                  |      |

| 5-12  | Periodic Interrupt Priority                      |      |

| 5-13  | Size Signal Encoding                             |      |

| 5-14  | Address Space Encoding                           |      |

| 5-15  | Effect of DSACK Signals                          |      |

| 5-16  | Operand Alignment                                |      |

| 5-17  | DSACK, BERR, and HALT Assertion Results          |      |

| 5-18  | Reset Source Summary                             |      |

| 5-19  | Reset Mode Selection                             |      |

| 5-20  | Module Pin Functions                             |      |

| 5-21  | SIM Pin Reset States                             |      |

| 5-22  | Chip-Select Pin Functions                        |      |

| 5-23  | Pin Assignment Field Encoding                    |      |

| 5-24  | Block Size Encoding                              |      |

Table

# Freescale Semiconductor, Inc.

### LIST OF TABLES (Continued) Title

Page

| 5-25<br>5-26                                                                    | Chip-Select Base and Option Register Reset Values                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6-1<br>6-2                                                                      | SRAM Configuration                                                                                                                                                                                                                                                                                                                                                                  |

| 7-1<br>7-2                                                                      | ROM Array Space Field7-2Wait States Field7-3                                                                                                                                                                                                                                                                                                                                        |

| 8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7<br>8-8<br>8-9<br>8-10<br>8-11     | FRZ Field Selection8-4Multiplexer Channel Sources8-5Prescaler Output8-7TS Field Selection8-7Conversion Parameters Controlled by ADCTL18-8ADC Conversion Modes8-8Single-Channel Conversions (MULT = 0)8-10Multiple-Channel Conversions (MULT = 1)8-11Result Register Formats8-14External Circuit Settling Time (10-Bit Conversions)8-23Error Resulting From Input Leakage (IOFF)8-23 |

| 0-11                                                                            |                                                                                                                                                                                                                                                                                                                                                                                     |

| 9-1<br>9-2<br>9-3<br>9-4<br>9-5                                                 | Effect of DDRQS on QSM Pin Function9-4QSPI Pins9-8Bits Per Transfer9-18Serial Frame Formats9-26Effect of Parity Checking on Data Size9-27                                                                                                                                                                                                                                           |

| 9-1<br>9-2<br>9-3<br>9-4                                                        | Effect of DDRQS on QSM Pin Function                                                                                                                                                                                                                                                                                                                                                 |

| 9-1<br>9-2<br>9-3<br>9-4<br>9-5<br>10-1<br>10-2<br>10-3<br>10-4<br>10-5<br>10-6 | Effect of DDRQS on QSM Pin Function9-4QSPI Pins9-8Bits Per Transfer9-18Serial Frame Formats9-26Effect of Parity Checking on Data Size9-27MCCI Interrupt Vectors10-3Pin Assignments10-4SPI Pin Functions10-7SCK Frequencies10-11SCI Pins10-17Serial Frame Formats10-18                                                                                                               |

### LIST OF TABLES (Continued) Title

### Table

Page

| A-3          | Typical Ratings, 5V, 16.78-MHz OperationA-3               |

|--------------|-----------------------------------------------------------|

| A-4          | Typical Ratings, 20.97-MHz Operation                      |

| A-5          | Typical Ratings, 25.17-MHz                                |

| A-6          | Thermal Characteristics                                   |

| A-7          | Low Voltage Clock Control TimingA-6                       |

| A-8          | 16.78-MHz Clock Control TimingA-7                         |

| A-9          | 20.97-MHz Clock Control Timing                            |

| A-10         | 25.17-MHz Clock Control Timing                            |

| A-11         | Low Voltage 16.78-MHz DC Characteristics                  |

| A-12         | 16.78-MHz DC Characteristics                              |

| A-13         | 20.97-MHz DC Characteristics                              |

| A-14         | 25.17-MHz DC Characteristics                              |

| A-15         | Low Voltage 16.78-MHz AC TimingA-19                       |

| A-16         | 16.78-MHz AC Timing                                       |

| A-17         | 20.97-MHz AC Timing                                       |

| A-18         | 25.17-MHz AC Timing                                       |

| A-19         | Low Voltage 16.78-MHz Background Debug Mode Timing        |

| A-20         | 16.78-MHz Background Debug Mode Timing                    |

| A-21         | 20.97-MHz Background Debug Mode Timing                    |

| A-22         | 25.17-MHz Background Debug Mode Timing                    |

| A-23         | Low Voltage ECLK Bus Timing                               |

| A-24         | 16.78-MHz ECLK Bus Timing                                 |

| A-25         | 20.97-MHz ECLK Bus Timing                                 |

| A-26         | 25.17-MHz ECLK Bus Timing                                 |

| A-20<br>A-27 | Low Voltage QSPI Timing                                   |

| A-27<br>A-28 | QSPI Timing                                               |

| A-20<br>A-29 | Low Voltage SPI Timing                                    |

| A-29<br>A-30 | SPI Timing                                                |

| A-30<br>A-31 | General-Purpose Timer AC Characteristics                  |

| A-31<br>A-32 |                                                           |

|              | ADC Maximum Ratings                                       |

| A-33         | Low Voltage ADC DC Electrical Characteristics (Operating) |

| A-34         | Low Voltage ADC AC Characteristics (Operating)            |

| A-35         | 5V ADC DC Electrical Characteristics (Operating)          |

| A-36         | ADC AC Characteristics (Operating)                        |

| A-37         | Low Voltage ADC Conversion Characteristics (Operating)    |

| A-38         | ADC Conversion Characteristics (Operating)A-67            |

| B-1          | M68HC16 Z-Series Ordering InformationB-8                  |

| D-1          | Module Address MapD-1                                     |

| D-2          | SIM Address MapD-4                                        |

|              |                                                           |

### LIST OF TABLES (Continued) Title

### Table

Page

| D-3         | Show Cycle Enable BitsD-6                              |

|-------------|--------------------------------------------------------|

| D-4         | Port E Pin AssignmentsD-10                             |