# Dual Bootstrapped, 12 V MOSFET Driver with Output Disable

The ADP3120A is a single Phase 12 V MOSFET gate drivers optimized to drive the gates of both high-side and low-side power MOSFETs in a synchronous buck converter. The high-side and low-side driver is capable of driving a 3000 pF load with a 45 ns propagation delay and a 25 ns transition time.

With a wide operating voltage range, high or low side MOSFET gate drive voltage can be optimized for the best efficiency. Internal adaptive nonoverlap circuitry further reduces switching losses by preventing simultaneous conduction of both MOSFETs.

The floating top driver design can accommodate VBST voltages as high as 35 V, with transient voltages as high as 40 V. Both gate outputs can be driven low by applying a low logic level to the Output Disable  $(\overline{OD})$  pin. An Undervoltage Lockout function ensures that both driver outputs are low when the supply voltage is low, and a Thermal Shutdown function provides the IC with overtemperature protection.

#### **Features**

- All-In-One Synchronous Buck Driver

- Bootstrapped High-Side Drive

- One PWM Signal Generates Both Drives

- Anticross Conduction Protection Circuitry

- OD for Disabling the Driver Outputs Meets CPU VR Requirement when Used with Patented FlexMode™ Controller

- These are Pb-Free Devices

# **Applications**

- Multiphase Desktop CPU Supplies

- Single-Supply Synchronous Buck Converters

# ON Semiconductor®

http://onsemi.com

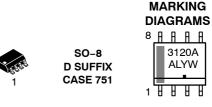

DFN8 MN SUFFIX CASE 506BJ

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb–Free Package

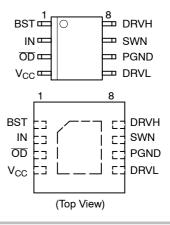

# PIN CONNECTIONS

#### **ORDERING INFORMATION**

| Device          | Package           | Shipping <sup>†</sup> |

|-----------------|-------------------|-----------------------|

| ADP3120AJRZ     | SO-8<br>(Pb-Free) | 98 Units / Rail       |

| ADP3120AJRZ-RL  | SO-8<br>(Pb-Free) | 2500 Tape & Reel      |

| ADP3120AJCPZ-RL | DFN8<br>(Pb-Free) | 5000 Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

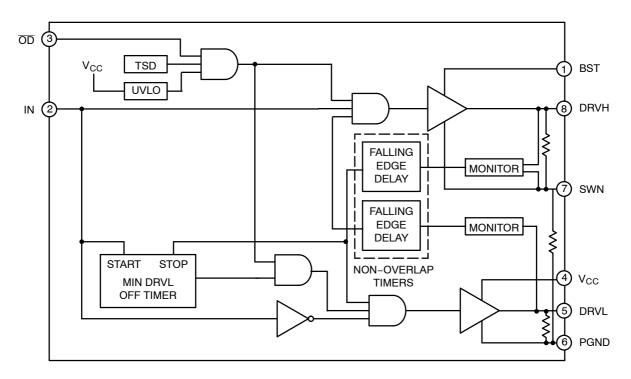

Figure 1. Block Diagram

# **PIN DESCRIPTION**

| SO-8 | DFN8 | Symbol          | Description                                                                                                                                                                                                                                                                        |  |  |  |

|------|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | 1    | BST             | Upper MOSFET Floating Bootstrap Supply. A capacitor connected between BST and SW pins holds this bootstrap voltage for the high–side MOSFET as it is switched. The recommended capacitor value is between 100 nF and 1.0 $\mu$ F. An external diode is required with the ADP3120A. |  |  |  |

| 2    | 2    | IN              | Logic-Level Input. This pin has primary control of the drive outputs.                                                                                                                                                                                                              |  |  |  |

| 3    | 3    | OD              | Output Disable. When low, normal operation is disabled forcing DRVH and DRVL low.                                                                                                                                                                                                  |  |  |  |

| 4    | 4    | V <sub>CC</sub> | Input Supply. A 1.0 μF ceramic capacitor should be connected from this pin to PGND.                                                                                                                                                                                                |  |  |  |

| 5    | 5    | DRVL            | Output drive for the lower MOSFET.                                                                                                                                                                                                                                                 |  |  |  |

| 6    | 6    | PGND            | Power Ground. Should be closely connected to the source of the lower MOSFET.                                                                                                                                                                                                       |  |  |  |

| 7    | 7    | SWN             | Switch Node. Connect to the source of the upper MOSFET.                                                                                                                                                                                                                            |  |  |  |

| 8    | 8    | DRVH            | Output drive for the upper MOSFET.                                                                                                                                                                                                                                                 |  |  |  |

# **MAXIMUM RATINGS**

| Rating                                                                                                                                                                                                                                                                            | Value                   | Unit                   |                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|----------------------|

| Operating Ambient Temperature, T <sub>A</sub>                                                                                                                                                                                                                                     |                         | -20 to 85              | °C                   |

| Operating Junction Temperature, T <sub>J</sub> (Note 1)                                                                                                                                                                                                                           |                         | -20 to 150             | °C                   |

| Package Thermal Resistance: SO-8<br>Junction-to-Case, $R_{\theta JC}$<br>Junction-to-Ambient, $R_{\theta JA}$ (2-Layer Board)<br>Package Thermal Resistance: DFN8 (Note 2)<br>Junction-to-Case, $R_{\theta JC}$ (From die to exposed pad)<br>Junction-to-Ambient, $R_{\theta JA}$ |                         | 45<br>123<br>7.5<br>55 | °C/W<br>°C/W<br>°C/W |

| Storage Temperature Range, T <sub>S</sub>                                                                                                                                                                                                                                         |                         | -65 to 150             | °C                   |

| Lead Temperature Soldering (10 sec): Reflow (SMD styles only)                                                                                                                                                                                                                     | Pb-Free (Note 3)        | 260 peak               | °C                   |

| JEDEC Moisture Sensitivity Level                                                                                                                                                                                                                                                  | SO-8 (260 peak profile) | 1                      | -                    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. Internally limited by thermal shutdown, 150°C min.

2. 2 layer board, 1 in<sup>2</sup> Cu, 1 oz thickness.

3. 60–180 seconds minimum above 237°C.

NOTE: This device is ESD sensitive. Use standard ESD precautions when handling.

### **MAXIMUM RATINGS**

| Pin Symbol      | Pin Name                                    | V <sub>MAX</sub>                                      | V <sub>MIN</sub>                        |

|-----------------|---------------------------------------------|-------------------------------------------------------|-----------------------------------------|

| V <sub>CC</sub> | Main Supply Voltage Input                   | 15 V                                                  | -0.3 V                                  |

| PGND            | Ground                                      | 0 V                                                   | 0 V                                     |

| BST             | Bootstrap Supply Voltage Input              | 35 V wrt/PGND<br>40 V < 50 ns wrt/PGND<br>15 V wrt/SW | −0.3 V wrt/SW                           |

| SW              | Switching Node<br>(Bootstrap Supply Return) | 35 V<br>40 V < 50 ns                                  | −5.0 V<br>−10 V < 200 ns                |

| DRVH            | High-Side Driver Output                     | BST + 0.3 V                                           | −0.3 V wrt/SW<br>−2.0 V < 200 ns wrt/SW |

| DRVL            | Low-Side Driver Output                      | V <sub>CC</sub> + 0.3 V                               | −0.3 V DC<br>−5.0 V < 200 ns            |

| IN              | DRVH and DRVL Control Input                 | 6.5 V                                                 | -0.3 V                                  |

| ŌD              | Output Disable                              | 6.5 V                                                 | -0.3 V                                  |

NOTE: All voltages are with respect to PGND except where noted.

| Characteristic                      | Symbol                                           | Condition                                                                                 | Min  | Тур      | Max        | Unit       |

|-------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|------|----------|------------|------------|

| Supply                              |                                                  |                                                                                           |      |          |            |            |

| Supply Voltage Range                | $V_{CC}$                                         | -                                                                                         | 4.6  | -        | 13.2       | V          |

| Supply Current                      | I <sub>SYS</sub>                                 | BST = 12 V, IN = 0 V                                                                      | -    | 0.7      | 2.0        | mA         |

| OD Input                            | •                                                |                                                                                           | •    | •        | •          |            |

| Input Voltage High                  | V <sub>OD_HI</sub>                               | -                                                                                         | 2.0  | -        | -          | V          |

| Input Voltage Low                   | V <sub>OD</sub> LO                               | -                                                                                         | -    | -        | 0.8        | V          |

| Hysteresis                          | _                                                | -                                                                                         | -    | 400      | -          | mV         |

| Input Current                       |                                                  | No internal pullup or pulldown resistors                                                  | -1.0 | -        | +1.0       | μΑ         |

| PWM Input                           | •                                                |                                                                                           | •    | •        | •          |            |

| Input Voltage High                  | V <sub>PWM_HI</sub>                              | -                                                                                         | 2.0  | _        | _          | V          |

| Input Voltage Low                   | V <sub>PWM LO</sub>                              | -                                                                                         | _    | _        | 0.8        | V          |

| Hysteresis                          | _                                                | _                                                                                         | _    | 400      | _          | mV         |

| Input Current                       | _                                                | No internal pullup or pulldown resistors                                                  | -1.0 | -        | +1.0       | μΑ         |

| High-Side Driver                    |                                                  |                                                                                           |      | •        |            | <u>. '</u> |

| Output Resistance, Sourcing Current | -                                                | BST - SW = 12 V; T <sub>A</sub> = -20°C to 85°C<br>BST - SW = 12 V; T <sub>A</sub> = 25°C | -    | 2.2<br>- | 3.9<br>3.3 | Ω          |

| Output Resistance, Sinking Current  | -                                                | BST – SW = 12 V; T <sub>A</sub> = -20°C to 85°C<br>BST – SW = 12 V; T <sub>A</sub> = 25°C | _    | 1.0<br>- | 2.6<br>1.8 | Ω          |

| Output Resistance, Unbiased         | -                                                | BST - SW = 0 V                                                                            | _    | 15       | -          | kΩ         |

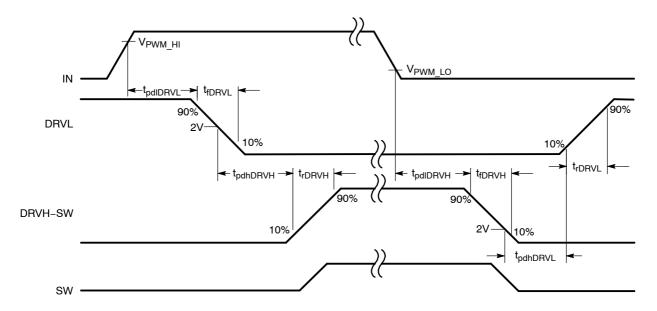

| Transition Times                    | t <sub>rDRVH</sub><br>t <sub>fDRVH</sub>         | BST – SW = 12 V, C <sub>LOAD</sub> = 3.0 nF<br>(See Figure 3)                             | _    | 20<br>11 | 40<br>30   | ns         |

| Propagation Delay Times (Note 5)    | t <sub>pdhDRVH</sub>                             | BST - SW = 12 V, C <sub>LOAD</sub> = 3.0 nF                                               | 32   | 45       | 70         | ns         |

|                                     | t <sub>pdlDRVH</sub>                             | (See Figure 3) BST – SW = 12 V, C <sub>LOAD</sub> = 3.0 nF (See Figure 3)                 |      | 25       | 35         |            |

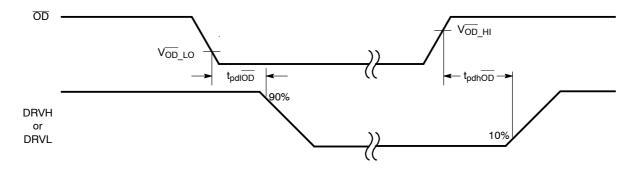

|                                     | t <sub>pdlOD</sub><br>t <sub>pdhOD</sub>         | (See Figure 2)<br>(See Figure 2)                                                          |      | 20<br>25 | 35<br>55   |            |

| SW Pulldown Resitance               | _                                                | SW to PGND                                                                                | _    | 15       | _          | kΩ         |

| Low-Side Driver                     |                                                  |                                                                                           |      |          |            | 1          |

| Output Resistance, Sourcing Current | -                                                | $T_A = -20^{\circ}\text{C to } 85^{\circ}\text{C}$<br>$T_A = 25^{\circ}\text{C}$          | _    | 1.8<br>- | 3.9<br>3.3 | Ω          |

| Output Resistance, Sinking Current  | -                                                | T <sub>A</sub> = -20°C to 85°C<br>T <sub>A</sub> = 25°C                                   | _    | 1.0<br>- | 2.6<br>1.8 | Ω          |

| Output Resistance, Unbiased         | _                                                | V <sub>CC</sub> = PGND                                                                    | _    | 15       | -          | kΩ         |

| Transition Times                    | t <sub>rDRVL</sub><br>t <sub>fDRVL</sub>         | C <sub>LOAD</sub> = 3.0 nF, (See Figure 3)                                                | _    | 16<br>11 | 35<br>30   | ns         |

| Propagation Delay Times (Note 5)    | t <sub>pdhDRVL</sub>                             | C <sub>LOAD</sub> = 3.0 nF, (See Figure 3)                                                | _    | 12       | 35         | ns         |

|                                     | t <sub>pdlDRVL</sub>                             | (Note 6, t <sub>pdhDRVL</sub> only)                                                       |      | 15       | 45         |            |

|                                     | t <sub>pdlOD</sub>                               | (See Figure 2)<br>(See Figure 2)                                                          |      | 20<br>20 | 35<br>35   |            |

| Timeout Delay                       | -                                                | DRVH - SW = 0                                                                             | _    | 85       | -          | ns         |

| Undervoltage Lockout                |                                                  |                                                                                           | 1    |          |            | 1          |

| UVLO Startup                        | _                                                | _                                                                                         | 3.9  | 4.3      | 4.5        | V          |

| UVLO Shutdown                       | _                                                | _                                                                                         | 3.7  | 4.1      | 4.3        | V          |

|                                     | <del>                                     </del> |                                                                                           | 0.1  | 0.2      | 0.4        | V          |

All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC).

For propagation delays, "tpdh" refers to the specified signal going high; "tpdl" refers to it going low.

Guaranteed by design; not tested in production.

#### **APPLICATIONS INFORMATION**

# **Theory of Operation**

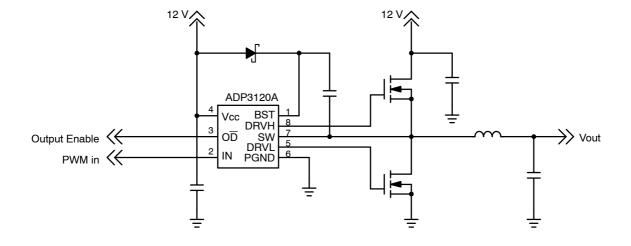

The ADP3120A are single phase MOSFET drivers designed for driving two N-channel MOSFETs in a synchronous buck converter topology. The ADP3120A will operate from 5.0 V or 12 V, but have been optimized for high current multi-phase buck regulators that convert 12 V rail directly to the core voltage required by complex logic chips. A single PWM input signal is all that is required to properly drive the high-side and the low-side MOSFETs. Each driver is capable of driving a 3 nF load at frequencies up to 1 MHz.

#### Low-Side Driver

The low-side driver is designed to drive a ground-referenced low RDS(on) N-Channel MOSFET. The voltage rail for the low-side driver is internally connected to the VCC supply and PGND.

#### **High-Side Driver**

The high-side driver is designed to drive a floating low RDS(on) N-channel MOSFET. The gate voltage for the high side driver is developed by a bootstrap circuit referenced to Switch Node (SW) pin.

The bootstrap circuit is comprised of an external diode, and an external bootstrap capacitor. When the ADP3120A are starting up, the SW pin is at ground, so the bootstrap capacitor will charge up to VCC through the bootstrap diode See Figure 4. When the PWM input goes high, the high–side driver will begin to turn on the high–side MOSFET using the stored charge of the bootstrap capacitor. As the high–side MOSFET turns on, the SW pin will rise. When the high–side MOSFET is fully on, the switch node will be at 12 V, and the BST pin will be at 12 V plus the charge of the bootstrap capacitor (approaching 24 V).

The bootstrap capacitor is recharged when the switch node goes low during the next cycle.

# **Safety Timer and Overlap Protection Circuit**

It is very important that MOSFETs in a synchronous buck regulator do not both conduct at the same time. Excessive shoot–through or cross conduction can damage the MOSFETs, and even a small amount of cross conduction will cause a decrease in the power conversion efficiency.

The ADP3120A prevent cross conduction by monitoring the status of the external mosfets and applying the appropriate amount of "dead-time" or the time between the turn off of one MOSFET and the turn on of the other MOSFET.

When the PWM input pin goes high, DRVL will go low after a propagation delay (tpdlDRVL). The time it takes for the low–side MOSFET to turn off (tfDRVL) is dependent on the total charge on the low–side MOSFET gate. The ADP3120A monitor the gate voltage of both MOSFETs and the switchnode voltage to determine the conduction status of the MOSFETs. Once the low–side MOSFET is turned off an internal timer will delay (tpdhDRVH) the turn on of the high–side MOSFET

Likewise, when the PWM input pin goes low, DRVH will go low after the propagation delay (tpdDRVH). The time to turn off the high-side MOSFET (tfDRVH) is dependent on the total gate charge of the high-side MOSFET. A timer will be triggered once the high-side mosfet has stopped conducting, to delay (tpdhDRVL) the turn on of the low-side MOSFET

### **Power Supply Decoupling**

The ADP3120A can source and sink relatively large currents to the gate pins of the external MOSFETs. In order to maintain a constant and stable supply voltage ( $V_{CC}$ ) a low ESR capacitor should be placed near the power and ground pins. A 1  $\mu$ F to 4.7  $\mu$ F multi layer ceramic capacitor (MLCC) is usually sufficient.

#### **Input Pins**

The PWM input and the Output Disable pins of the ADP3120A have internal protection for Electro Static Discharge (ESD), but in normal operation they present a relatively high input impedance. If the PWM controller does not have internal pulldown resistors, they should be added externally to ensure that the driver outputs do not go high before the controller has reached its under voltage lockout threshold. The NCP5381 controller does include a passive internal pulldown resistor on the drive—on output pin.

#### **Bootstrap Circuit**

The bootstrap circuit uses a charge storage capacitor (CBST) and the internal (or an external) diode. Selection of these components can be done after the high-side MOSFET has been chosen. The bootstrap capacitor must have a voltage rating that is able to withstand twice the maximum supply voltage. A minimum 50 V rating is recommended. The capacitance is determined using the following equation:

$$C_{BST} = \frac{Q_{GATE}}{\Delta V_{BST}}$$

where QGATE is the total gate charge of the high-side MOSFET, and  $\Delta$ VBST is the voltage droop allowed on the high-side MOSFET drive. For example, a NTD60N03 has a total gate charge of about 30 nC. For an allowed droop of 300 mV, the required bootstrap capacitance is 100 nF. A good quality ceramic capacitor should be used.

The bootstrap diode must be rated to withstand the maximum supply voltage plus any peak ringing voltages that may be present on SW. The average forward current can be estimated by:

$$I_{F(AVG)} = Q_{GATE} \times f_{MAX}$$

where fMAX is the maximum switching frequency of the controller. The peak surge current rating should be checked in-circuit, since this is dependent on the source impedance of the 12 V supply and the ESR of CBST.

Figure 2. Output Disable Timing Diagram

Figure 3. Nonoverlap Timing Diagram

Figure 4. ADP3120A Example Circuit

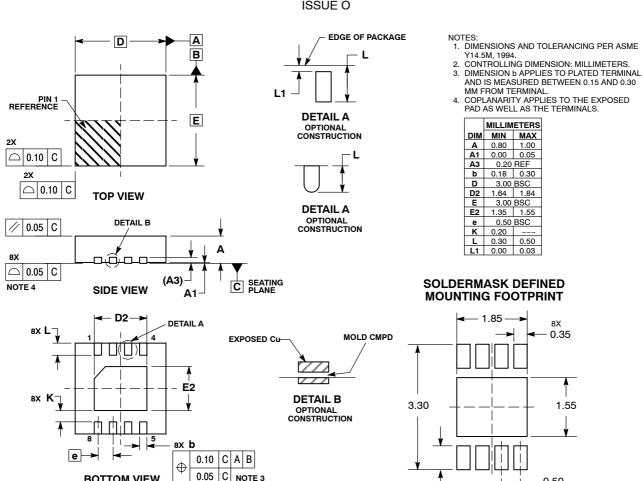

#### PACKAGE DIMENSIONS

# DFN8 3x3, 0.5P CASE 506BJ ISSUE O

**BOTTOM VIEW**

**DIMENSION: MILLIMETERS**

0.50

**PITCH**

8X 0.63

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

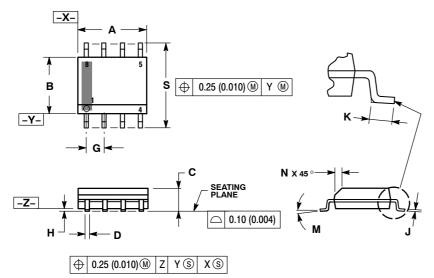

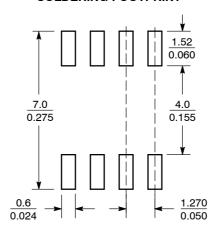

# **PACKAGE DIMENSIONS**

### SOIC-8 **D SUFFIX** CASE 751-07 **ISSUE AK**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |      | INCHES    |       |  |

|-----|-------------|------|-----------|-------|--|

| DIM | MIN         | MAX  | MIN       | MAX   |  |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |  |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |  |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |  |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |  |

| G   | 1.27 BSC    |      | 0.050 BSC |       |  |

| Н   | 0.10        | 0.25 | 0.004     | 0.010 |  |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |  |

| K   | 0.40        | 1.27 | 0.016     | 0.050 |  |

| М   | 0 °         | 8 °  | 0 °       | 8 °   |  |

| N   | 0.25        | 0.50 | 0.010     | 0.020 |  |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |  |

#### **SOLDERING FOOTPRINT\***

(mm inches) SCALE 6:1

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

FlexMode is a trademark of Analog Devices, Inc.

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered readerlands of semiconductor Components industries, Ite (SCILLC) . Solitude services are inject to make triangles without further holice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative