# LA6324N

# Monolithic Linear IC High-Performance Quad Operational Amplifier

#### Overview

The LA6324 consists of four independent, high-performance, internally phase compensated operational amplifiers that are designed to operate from a single power supply over a wide range of voltages. These four operational amplifiers are packaged in a single package. As in case of conventional general-purpose operational amplifiers, operation from dual power supplies is also possible and the power dissipation is low. It can be applied to various uses in commercial and industrial equipment including all types of transducer amplifiers and DC amplifiers.

#### Features

- No phase compensation required

- Wide operating voltage range:

- 3.0 V to 30.0 V (single supply)

- $\pm 1.5$  V to  $\pm 15.0$  V (dual supplies)

- Highly resistant to dielectric breakdown

- Input voltag range includes the neighborhood of GND level and output voltage range  $V_{OUT}$  is from 0 to  $V_{CC}$  -1.5 V.

- Small current dissipation: I<sub>CC</sub> = 0.6 mA typ/V<sub>CC</sub> = + 5 V, R<sub>L</sub> =  $\infty$

# **Specitications**

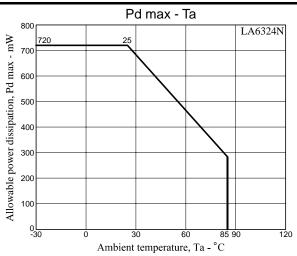

#### Absolute Maximum Ratings at $Ta = 25 \ ^{\circ}C$

| Parameter                   | Symbol              | Conditions | Ratings     | Unit |

|-----------------------------|---------------------|------------|-------------|------|

| Maximum Supply voltage      | V <sub>CC</sub> max |            | 32          | V    |

| Differential input voltage  | V <sub>ID</sub>     |            | 32          | V    |

| Maximum input voltage       | V <sub>IN</sub> max |            | -0.3 to +32 | V    |

| Allowable power dissipation | Pd max              | LA6324N    | 720         | mW   |

| Operating temperature       | Topr                |            | -30 to +85  | °C   |

| Storage temperature         | Tstg                |            | -55 to +125 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# Operating Characteristics at $Ta=25\ ^{o}C,\ V_{CC}=+5\ V$

| Parameter                       | Symbol              | Conditions                                           | Test circuit | Ratings |     |                      | L la it |

|---------------------------------|---------------------|------------------------------------------------------|--------------|---------|-----|----------------------|---------|

|                                 |                     |                                                      |              | min     | typ | max                  | Unit    |

| Input offset voltage            | VIO                 |                                                      | 1            |         | ±2  | ±7                   | mV      |

| Input offset current            | IIO                 | I <sub>IN</sub> (+) / I <sub>IN</sub> (–)            | 2            |         | ±5  | ±50                  | nA      |

| Input bias current              | Ι <sub>Β</sub>      | I <sub>IN</sub> (+) / I <sub>IN</sub> (–)            | 3            |         | 45  | 250                  | nA      |

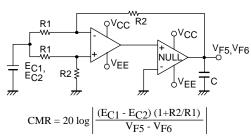

| Common-mode input voltage range | VICM                |                                                      | 4            | 0       |     | V <sub>CC</sub> –1.5 | V       |

| Common-mode rejection ratio     | CMR                 |                                                      | 4            | 65      | 80  |                      | dB      |

| Voltage gain                    | VG                  | $V_{CC}$ = 15 V, $R_L \ge 2 k\Omega$                 | 5            | 25      | 100 |                      | V/mV    |

| Output voltage range            | VOUT                |                                                      |              | 0       |     | V <sub>CC</sub> –1.5 | V       |

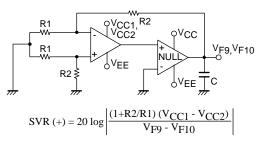

| Supply voltage rejection ratio  | SVR                 |                                                      | 6            | 65      | 100 |                      | dB      |

| Channel separation              | CS                  | f = 1 k to 20 kHz                                    | 7            |         | 120 |                      | dB      |

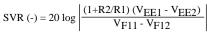

| Current drain                   | ICC                 |                                                      | 8            |         | 0.6 | 2                    | mA      |

|                                 | ICC                 | V <sub>CC</sub> = 30 V                               | 8            |         | 1.5 | 3                    | mA      |

| Output current (Source)         | IO source           | $V_{IN}^{+} = 1 \text{ V}, V_{IN}^{-} = 0 \text{ V}$ | 9            | 20      | 40  |                      | mA      |

| Output current (Sink)           | I <sub>O</sub> sink | $V_{IN}^{+} = 0 V, V_{IN}^{-} = 1 V$                 | 10           | 10      | 20  |                      | mA      |

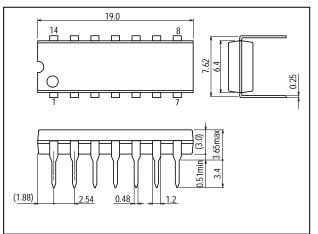

# Package Dimensions

unit : mm 3003B [LA6324N]

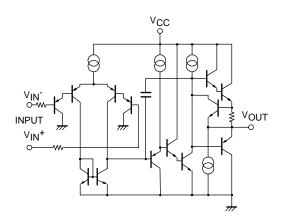

# **Equivalent Circuit**

(1 unit)

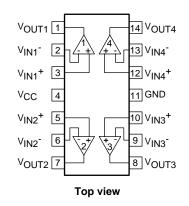

# **Pin Assignment**

(LA6324N)

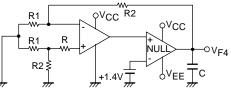

2. Input offset current IIO

R1

R1

R2

R

R

$I_{IO} =$

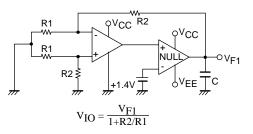

#### **Test Circuit**

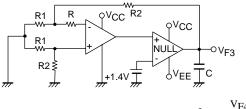

1. Input offset voltage VIO

3. Input bias current IB

ovcc<sup>™R2</sup>

γVcc

VF7,VF8

$\frac{v_{F2} - v_{F1}}{R(1 + R2/R1)}$

γVcc

γ<sup>EE</sup>⊥c

<sup>OV</sup>F2

NULÌ

- $I_{B} = \frac{V_{F4} V_{F3}}{2R(1 + R2/R1)}$

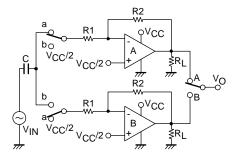

- 4. Common-mode rejection ratio CMR Common-mode input voltage range VICM

5. Voltage gain VG

R1

R1

R2

VG =

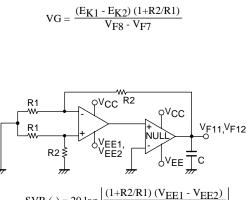

6. Supply voltage rejection ratio SVR

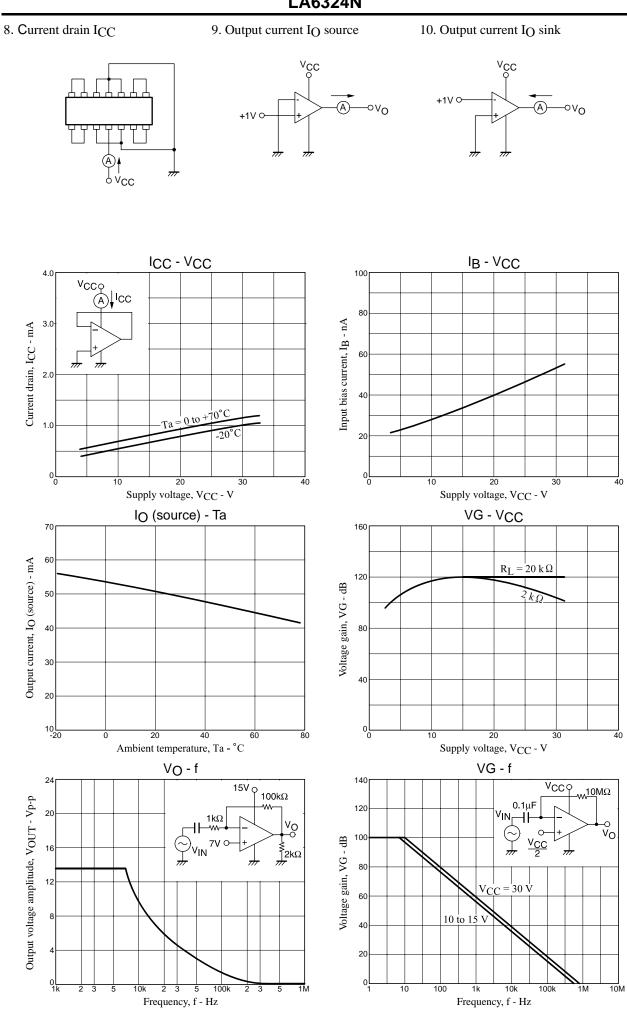

7. Channel separation CS

- SW: a Sw: a $CS (A \rightarrow B) = 20 \log \frac{\kappa_2 v_{OA}}{R1 V_{OB}}$ R2 VOA SW: b SW: b CS (B $\rightarrow$ A) = 20 log  $\frac{\text{R2 V}_{\text{OB}}}{\text{R1 V}_{\text{OA}}}$

- These apply also to other channels.

No.2704-4/5

#### LA6324N

#### **Sample Application Circuits**

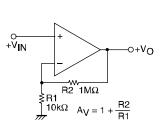

Noninverting DC amplifier

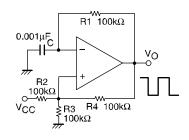

Rectangular wave oscillator

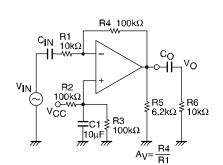

#### Inverting AC amplifier

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affimative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.