**Monolithic Digital IC**

# Direct PWM Drive Brushless Motor Predriver IC

www.onsemi.com

#### Overview

The LB11696V is a direct PWM drive predriver IC designed for three-phase power brushless motors. A motor driver circuit with the desired output power (voltage and current) can be implemented by adding discrete transistors in the output circuits. Furthermore, the LB11696V provides a full complement of protection circuits allowing it to easily implement high-reliability drive circuits. This device is optimal for driving all types of large-scale motors such as those used in air conditioners and on-demand water heaters.

SSOP30 (275mil)

#### **Features**

- Three-phase bipolar drive

- Direct PWM drive (controlled either by control voltage or PWM variable duty pulse input)

- Built-in forward/reverse switching circuit

- Start/stop mode switching circuit (stop mode power saving function)

- Built-in input amplifier

- 5 V regulator output (VREG pin)

- Current limiter circuit (Supports 0.25 V (typical) reference voltage sensing based high-precision detection)

- Undervoltage protection circuit (The operating voltage can be set with a zener diode)

- Automatic recovery type constraint protection circuit with protection operating state discrimination output (RD pin)

- Four types of Hall signal pulse outputs

- Supports thermistor based thermal protection of the output transistors

## **Specifications**

#### **Absolute Maximum Ratings** at Ta = 25°C

| Parameter                     | Symbol              | Conditions                                                              | Ratings     | unit |

|-------------------------------|---------------------|-------------------------------------------------------------------------|-------------|------|

| Supply voltage 1              | V <sub>CC</sub> max | V <sub>CC</sub> pin                                                     | 18          | V    |

| Output current                | I <sub>O</sub> max  | UL, VL, WL, UH, VH, and WH pins                                         | 30          | mA   |

| LVS pin applied voltage       | LVS max             | LVS pin                                                                 | 18          | V    |

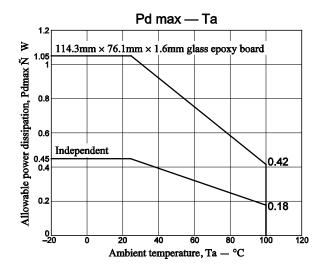

| Allowable power dissipation 1 | Pd max 1            | Independent IC                                                          | 0.45        | W    |

| Allowable power dissipation 2 | Pd max 2            | When mounted on a 114.3 $\times$ 76.1 $\times$ 1.6 mm glass epoxy board | 1.05        | W    |

| Operating temperature         | Topr                |                                                                         | -20 to +100 | °C   |

| Storage temperature           | Tstg                |                                                                         | -55 to +150 | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 17 of this data sheet.

# Allowable Operating Ranges at Ta = 25 °C

| Parameter                           | Symbol              | Conditions                                                    | Ratings    | Unit |

|-------------------------------------|---------------------|---------------------------------------------------------------|------------|------|

| Supply voltage range 1-1            | V <sub>CC</sub> 1-1 | V <sub>CC</sub> pin                                           | 8 to 17    | ٧    |

| Supply voltage range 1-2            | V <sub>CC</sub> 1-2 | V <sub>CC</sub> pin, when V <sub>CC</sub> is shorted to VREG. | 4.5 to 5.5 | ٧    |

| Output current                      | lo                  | UL, VL, WL, UH, VH, and WH pins                               | 25         | mA   |

| 5 V constant voltage output current | IREG                |                                                               | -30        | mΑ   |

| HP pin applied voltage              | VHP                 |                                                               | 0 to 17    | ٧    |

| HP pin output current               | IHP                 |                                                               | 0 to 15    | mΑ   |

| RD pin applied voltage              | VRD                 |                                                               | 0 to 17    | ٧    |

| RD pin output current               | IRD                 |                                                               | 0 to 15    | mA   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# Electrical Characteristics at Ta = 25 °C, $V_{CC} = 12$ V

| Parameter  Current drain 1               | Symbol                | Conditions                                            |                       |                       | Ratings               |       |  |

|------------------------------------------|-----------------------|-------------------------------------------------------|-----------------------|-----------------------|-----------------------|-------|--|

|                                          |                       |                                                       | min                   | typ                   | max                   | Unit  |  |

| O                                        | I <sub>CC</sub> 1     |                                                       |                       | 12                    | 16                    | mA    |  |

| Current drain 2                          | l <sub>CC</sub> 2     | Stop mode                                             |                       | 2.5                   | 4                     | mA    |  |

| [5 V Constant Voltage Output (VREG pin)] |                       |                                                       |                       |                       |                       |       |  |

| Output voltage                           | VREG                  |                                                       | 4.7                   | 5.0                   | 5.3                   | ٧     |  |

| Line regulation                          | ∆VREG1                | V <sub>CC</sub> = 8 to 17 V                           |                       | 40                    | 100                   | mV    |  |

| Load regulation                          | ΔVREG2                | $I_0 = -5 \text{ to } -20 \text{ mA}$                 |                       | 10                    | 30                    | mV    |  |

| Temperature coefficient                  | ΔVREG3                | Design target value                                   |                       | 0                     |                       | mV/°C |  |

| [Output Block]                           |                       |                                                       |                       |                       |                       |       |  |

| Output voltage 1-1                       | V <sub>OUT</sub> 1-1  | Low level, I <sub>O</sub> = 400 μA                    |                       | 0.2                   | 0.5                   | ٧     |  |

| Output voltage 1-2                       | V <sub>OUT</sub> 1-2  | Low level, I <sub>O</sub> = 10 mA                     |                       | 0.9                   | 1.2                   | ٧     |  |

| Output voltage 2                         | V <sub>OUT</sub> 2    | High level, I <sub>O</sub> = -20 mA                   | V <sub>CC</sub> - 1.1 | V <sub>CC</sub> - 0.9 |                       | ٧     |  |

| Output leakage current                   | l <sub>O</sub> leak   |                                                       |                       |                       | 10                    | μA    |  |

| [Hall Amplifier Block]                   |                       |                                                       |                       |                       |                       |       |  |

| Input bias current                       | IHB (HA)              |                                                       | -2                    | -0.5                  |                       | μA    |  |

| Common-mode input voltage range 1        | VICM1                 | When a Hall effect device is used                     | 0.5                   |                       | V <sub>CC</sub> - 2.0 | ٧     |  |

| Common-mode input voltage range 2        | VICM2                 | Single-sided input bias mode (when a Hall IC is used) | 0                     |                       | Vcc                   | V     |  |

| Hall Input Sensitivity                   |                       |                                                       | 80                    |                       |                       | mVp-p |  |

| Hysteresis                               | ΔVIN (HA)             |                                                       | 15                    | 24                    | 40                    | mV    |  |

| Input voltage low → high                 | VSLH (HA)             |                                                       | 5                     | 12                    | 20                    | mV    |  |

| Input voltage high → low                 | VSHL (HA)             |                                                       | -20                   | -12                   | <b>-</b> 5            | mV    |  |

| [CTL Amplifier]                          |                       |                                                       |                       |                       |                       |       |  |

| Input offset voltage                     | V <sub>IO</sub> (CTL) |                                                       | -10                   |                       | 10                    | mV    |  |

| Input bias current                       | I <sub>B</sub> (CTL)  |                                                       | -1                    |                       | 1                     | μA    |  |

| Common-mode input voltage range          | VICM                  |                                                       | 0                     |                       | VREG - 1.7            | ٧     |  |

| High-level output voltage                | V <sub>OH</sub> (CTL) | ITOC = -0.2 mA                                        | VREG - 1.2            | VREG - 0.8            |                       | ٧     |  |

| Low-level output voltage                 | V <sub>OL</sub> (CTL) | ITOC = 0.2 mA                                         |                       | 0.8                   | 1.05                  | ٧     |  |

| Open-loop gain                           | G (CTL)               | f (CTL) = 1 kHz                                       | 45                    | 51                    |                       | dB    |  |

| [PWM Oscillator (PWM pin)]               |                       |                                                       |                       |                       |                       |       |  |

| High-level output voltage                | V <sub>OH</sub> (PWM) |                                                       | 2.75                  | 3.0                   | 3.25                  | V     |  |

|                                          | V <sub>OL</sub> (PWM) |                                                       | 1.2                   | 1.35                  | 1.5                   | ٧     |  |

| External capacitor charge current        | ICHG                  | VPWM = 2.1 V                                          | -120                  | -90                   | -65                   | μA    |  |

| Oscillator frequency                     | f (PWM)               | C = 2000 pF                                           |                       | 22                    |                       | kHz   |  |

| Amplitude                                | V (PWM)               | -                                                     | 1.4                   | 1.6                   | 1.9                   | Vp-p  |  |

| [TOC pin]                                |                       |                                                       |                       |                       |                       |       |  |

| Input voltage 1                          | VTOC1                 | Output duty: 100%                                     | 2.68                  | 3.0                   | 3.34                  | ٧     |  |

| Input voltage 2                          | VTOC2                 | Output duty: 0%                                       | 1.2                   | 1.35                  | 1.5                   | V     |  |

| Input voltage 1 low                      | VTOC1L                | Design target value, when VREG = 4.7 V, 100%          | 2.68                  | 2.82                  | 2.96                  | ٧     |  |

| Input voltage 2 low                      | VTOC2L                | Design target value, when VREG = 4.7 V, 0%            | 1.23                  | 1.29                  | 1.34                  | ٧     |  |

| Input voltage 1 high                     | VTOC1H                | Design target value, when VREG = 5.3 V, 100%          | 3.02                  | 3.18                  | 3.34                  | ٧     |  |

| Input voltage 2 high                     | VTOC2H                | Design target value, when VREG = 5.3 V, 0%            | 1.37                  | 1.44                  | 1.50                  | ٧     |  |

| [HP Pin]                                 |                       | , , ,                                                 |                       |                       |                       |       |  |

| Output saturation voltage                | VHPL                  | I <sub>O</sub> = 10 mA                                |                       | 0.2                   | 0.5                   | ٧     |  |

| Output leakage current                   | IHPleak               | V <sub>O</sub> = 18 V                                 |                       |                       | 10                    | μA    |  |

Continued on next page.

# Continued from preceding page.

|                                             |                       | Conditions                           |            | Ratings |       | 1154  |

|---------------------------------------------|-----------------------|--------------------------------------|------------|---------|-------|-------|

| Parameter                                   | Symbol                | Conditions                           | min        | typ     | max   | Unit  |

| [CSD Oscillator (CSD pin)]                  |                       |                                      |            | •       |       |       |

| High-level output voltage                   | V <sub>OH</sub> (CSD) |                                      | 2.7        | 3.0     | 3.3   | ٧     |

| Low-level output voltage                    | V <sub>OL</sub> (CSD) |                                      | 0.7        | 1.0     | 1.3   | ٧     |

| External capacitor charge current           | ICHG1                 | VCSD = 2 V                           | -3.15      | -2.5    | -1.85 | μA    |

| External capacitor discharge current        | ICHG2                 | VCSD = 2 V                           | 0.1        | 0.14    | 0.18  | μA    |

| Charge/discharge current ratio              | RCSD                  | (Charge current)/(discharge current) | 15         | 18      | 21    | times |

| [RD Pin]                                    |                       |                                      |            | •       |       |       |

| Low-level output voltage                    | VRDL                  | I <sub>O</sub> = 10 mA               |            | 0.2     | 0.5   | V     |

| Output leakage current                      | I <sub>L</sub> (RD)   | V <sub>O</sub> = 18 V                |            |         | 10    | μA    |

| [Current Limiter Circuit (RF pin)]          | •                     |                                      |            | •       | •     |       |

| Limiter voltage                             | VRF                   | RF-RFGND                             | 0.225      | 0.25    | 0.275 | V     |

| [Undervoltage Protection Circuit (LVS pin)] | •                     |                                      |            |         | '     |       |

| Operating voltage                           | VSDL                  |                                      | 3.5        | 3.7     | 3.9   | V     |

| Release voltage                             | VSDH                  |                                      | 3.95       | 4.15    | 4.35  | ٧     |

| Hysteresis                                  | ΔVSD                  |                                      | 0.3        | 0.45    | 0.6   | ٧     |

| [PWMIN Pin]                                 | 1                     | •                                    |            |         | -     |       |

| Input frequency                             | f (PI)                |                                      |            |         | 50    | kHz   |

| High-level input voltage                    | V <sub>IH</sub> (PI)  |                                      | 2.0        |         | VREG  | V     |

| Low-level input voltage                     | V <sub>IL</sub> (PI)  |                                      | 0          |         | 1.0   | V     |

| Input open voltage                          | V <sub>IO</sub> (PI)  |                                      | VREG - 0.5 |         | VREG  | V     |

| Hysteresis                                  | V <sub>IS</sub> (PI)  |                                      | 0.2        | 0.25    | 0.4   | V     |

| High-level input current                    | I <sub>IH</sub> (PI)  | VPWMIN = VREG                        | -10        | 0       | +10   | μA    |

| Low-level input current                     | I <sub>IL</sub> (PI)  | VPWMIN = 0 V                         | -130       | -90     |       | μA    |

| [S/S Pin]                                   |                       |                                      |            | •       | •     |       |

| High-level input voltage                    | V <sub>IH</sub> (SS)  |                                      | 2.0        |         | VREG  | ٧     |

| Low-level input voltage                     | V <sub>IL</sub> (SS)  |                                      | 0          |         | 1.0   | ٧     |

| Hysteresis                                  | V <sub>IS</sub> (SS)  |                                      | 0.2        | 0.25    | 0.4   | V     |

| High-level input current                    | I <sub>IH</sub> (SS)  | VS/S = VREG                          | -10        | 0       | +10   | μA    |

| Low-level input current                     | I <sub>IL</sub> (SS)  | VS/S = 0 V                           | -10        | -1      |       | μA    |

| [F/R Pin]                                   | •                     |                                      |            | •       |       |       |

| High-level input voltage                    | V <sub>IH</sub> (FR)  |                                      | 2.0        |         | VREG  | V     |

| Low-level input voltage                     | V <sub>IL</sub> (FR)  |                                      | 0          |         | 1.0   | V     |

| Input open voltage                          | V <sub>IO</sub> (FR)  |                                      | VREG - 0.5 |         | VREG  | V     |

| Hysteresis                                  | V <sub>IS</sub> (FR)  |                                      | 0.2        | 0.25    | 0.4   | ٧     |

| High-level input current                    | I <sub>IH</sub> (FR)  | VF/R = VREG                          | -10        | 0       | +10   | μA    |

| Low-level input current                     | I <sub>IL</sub> (FR)  | VF/R = 0 V                           | -130       | -90     |       | μA    |

| [N1 Pin]                                    |                       |                                      |            |         | !     |       |

| High-level input voltage                    | V <sub>IH</sub> (N1)  |                                      | 2.0        |         | VREG  | V     |

| Low-level input voltage                     | V <sub>IL</sub> (N1)  |                                      | 0          |         | 1.0   | V     |

| Input open voltage                          | V <sub>IO</sub> (N1)  |                                      | VREG - 0.5 |         | VREG  | ٧     |

| High-level input current                    | I <sub>IH</sub> (N1)  | VN1 = VREG                           | -10        | 0       | +10   | μA    |

| Low-level input current                     | I <sub>IL</sub> (N1)  | VN1 = 0 V                            | -130       | -100    |       | μA    |

| [N2 Pin]                                    | •                     |                                      |            | '       | •     |       |

| High-level input voltage                    | V <sub>IH</sub> (N2)  |                                      | 2.0        |         | VREG  | V     |

| Low-level input voltage                     | V <sub>IL</sub> (N2)  |                                      | 0          |         | 1.0   | V     |

| Input open voltage                          | V <sub>IO</sub> (N2)  |                                      | VREG - 0.5 |         | VREG  | V     |

| High-level input current                    | I <sub>IH</sub> (N2)  | VN2 = VREG                           | -10        | 0       | +10   | μА    |

| Low-level input current                     | I <sub>IL</sub> (N2)  | VN2 = 0 V                            | -130       | -100    |       | μA    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Three-Phase Logic Truth Table ("IN = 'H'" indicates the state where IN+ > IN-.)

|   |     | F/R = L |     | F/R = H |     |     | Output |    |

|---|-----|---------|-----|---------|-----|-----|--------|----|

|   | IN1 | IN2     | IN3 | IN1     | IN2 | IN3 | PWM    | _  |

| 1 | Н   | L       | Н   | L       | Н   | L   | VH     | UL |

| 2 | Н   | L       | L   | L       | Н   | Н   | WH     | UL |

| 3 | Н   | Н       | L   | L       | L   | Н   | WH     | VL |

| 4 | L   | Н       | L   | Н       | L   | Н   | UH     | VL |

| 5 | L   | Н       | Н   | Н       | L   | L   | UH     | WL |

| 6 | L   | L       | Н   | Н       | Н   | L   | VH     | WL |

### S/S Pin

| Input state | State |

|-------------|-------|

| Н           | Stop  |

| L           | Start |

## **PWMIN Pin**

| Input state  | State      |

|--------------|------------|

| High or open | Output off |

| L            | Output on  |

#### N1 and N2 Pins

| Input state  |              | HP output                                         |  |

|--------------|--------------|---------------------------------------------------|--|

| N1 pin       | N2 pin       | не оцфи                                           |  |

| L            | L            | Single Hall sensor period divided by 2            |  |

| L            | High or open | Single Hall sensor period                         |  |

| High or open | L            | Three Hall sensor synthesized period divided by 2 |  |

| High or open | High or open | Three Hall sensor synthesized period              |  |

Since the S/S pin does not have an internal pull-up resistor, an external pull-up resistor or equivalent is required to set the IC to the stop state. If either the S/S or PWMIN pins are not used, the unused pin input must be set to the low-level voltage.

The HP output can be selected (by the N1 and N2 settings) to be one of the following four functions: the IN1 Hall input converted to a pulse output (one-Hall output), the one-Hall output divided by two, the three-phase output synthesized from the Hall inputs (three-Hall synthesized output) or the three-Hall synthesized output divided by two.

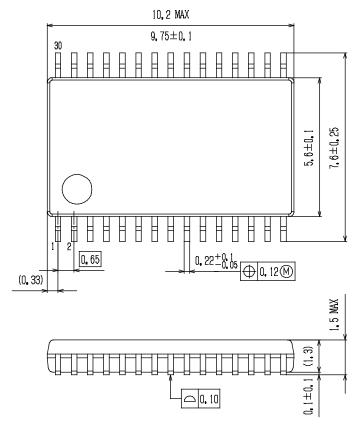

# **Package Dimensions**

unit: mm

# SSOP30 (275mil)

CASE 565AT ISSUE A

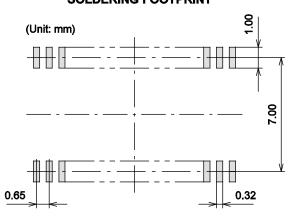

# **SOLDERING FOOTPRINT\***

NOTE: The measurements are not to guarantee but for reference only.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code

Y = Year

M = Month

DDD = Additional Traceability Data

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "=", may or may not be present.

### ORDERING INFORMATION

| Device         | Package                                     | Wire bond | Shipping (Qty / Packing) |

|----------------|---------------------------------------------|-----------|--------------------------|

| LB11696V-MPB-E | SSOP30 (275mil)<br>(Pb-Free)                | Au wire   | 48 / Fan-Fold            |

| LB11696V-TLM-E | SSOP30 (275mil)<br>(Pb-Free)                | Au wire   | 1000 / Tape & Reel       |

| LB11696V-TRM-E | SSOP30 (275mil)<br>(Pb-Free)                | Au wire   | 1000 / Tape & Reel       |

| LB11696V-TLM-H | SSOP30 (275mil)<br>(Pb-Free / Halogen Free) | Au wire   | 1000 / Tape & Reel       |

| LB11696V-W-AH  | SSOP30 (275mil)<br>(Pb-Free / Halogen Free) | Cu wire   | 1000 / Tape & Reel       |

<sup>†</sup> For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. http://www.onsemi.com/pub\_link/Collateral/BRD8011-D.PDF

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent re