# LV5781

## 3A, Point-of-load, Chopper-type Step-down Converter

#### Overview

The LV5781 is a 1-channel chopper-type (low-side Schottky diode) step-down switching regulator. It incorporates an  $80m\Omega$  (typical) power MOSFET to achieve high-efficiency operation for 3A output currents.

The output voltage is set internally to 3.3V. By adding two external resistors, it is possible to set the voltage to any desired setting above 0.85V. Inrush current at startup can be prevented by the soft start function.

Using the ON/OFF pins, the converter can be set to standby mode in which the current consumption is  $10\mu$ A or less. Both the load and the IC are protected by means of the overcurrent and thermal protection functions. The converter uses the HSSOP14 miniature package.

### **Functions**

- 3A, 1-channel chopper-type, step-down switching regulator

- Output voltage: 3.3V

- Setting of any output voltage enabled (external resistors required)

- High efficiency: 90% at  $I_{OUT}=1A$ ,  $V_{O}=3.3V$

- Miniature package: HSSOP14

- Soft start function

- Standby mode

- Overcurrent protection

- Thermal shutdown

- Fixed frequency: 180kHz

## Applications

- LCD TVs

- Game machines

## **Specifications**

## Absolute Maximum Ratings at Ta=25°C

| Parameter                                  | Symbol              | Conditions                    | Ratings     | Unit |

|--------------------------------------------|---------------------|-------------------------------|-------------|------|

| Maximum input voltage                      | V <sub>IN</sub> max |                               | 6.5         | V    |

| Maximum CBOOT pin voltage                  | VBT max             |                               | 13          | V    |

| Maximum SW pin voltage                     | VSW max             |                               | 6.5         | V    |

| Maximum voltage between CBOOT and SW pins  | VBS max             |                               | 6.5         | V    |

| Maximum voltage at FB, SS, and ENABLE pins | Vfs max             |                               | 6.5         | V    |

| Junction temperature                       | Tj max              |                               | 125         | °C   |

| Allowable power dissipation                | Pd max              | Mounted on a circuit board *1 | 0.85        | W    |

| Operating temperature range                | Topr                |                               | -30 to +80  | °C   |

| Storage temperature range                  | Tstg                |                               | -40 to +125 | °C   |

\*1: Mounted on a specified board: 114.3mm×76.1mm×1.6mm, glass epoxy.

\*2: To ensure that the maximum voltage is not exceeded even for an instant, check that the coil voltage and other surge voltage levels are factored in.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### Recommended Operating Conditions at Ta= $25^{\circ}C$

| Parameter                      | Symbol | Conditions | Ratings  | Unit |

|--------------------------------|--------|------------|----------|------|

| V <sub>IN</sub> pin voltage    | VIN    |            | 4.5 to 6 | V    |

| CBOOT pin voltage              | VBT    |            | 0 to 6   | V    |

| SW pin voltage                 | VSW    |            | 6        | V    |

| FB, SS, and ENABLE pin voltage | VFSO   |            | 6        | V    |

#### Electrical Characteristics at Ta=25°C, V<sub>IN</sub>=5V (Unless specifically specified)

| Parameter                                  | Oursels al         | Oraditions                                 | Ratings |       |      | 11.3 |

|--------------------------------------------|--------------------|--------------------------------------------|---------|-------|------|------|

|                                            | Symbol             | Symbol Conditions                          | min     | typ   | max  | Unit |

| Output voltage 1                           | VOUT1              | FB2 pin selected                           | 3.2     | 3.3   | 3.4  | V    |

| Output voltage 2                           | V <sub>OUT</sub> 2 | Dependent on the external voltage divider  | 0.85    |       |      | V    |

| Standby mode IC consumption current        | ICC1               | ENABLE=0V                                  |         | 1     | 10   | μΑ   |

| Operating time IC consumption current      | ICC2               | ENABLE=3V                                  |         | 2     | 5    | mA   |

| ENABLE high level voltage                  | VENH               |                                            | 3       |       |      | V    |

| ENABLE low level voltage                   | VENL               |                                            |         |       | 0.7  | V    |

| Efficiency                                 | Effcy              | I <sub>OUT</sub> =1A, V <sub>O</sub> =3.3V |         | 90    |      | %    |

| Reference voltage                          | Vref               | V <sub>IN</sub> =4.5V to 6V(±2%)           | 0.76    | 0.8   | 0.84 | V    |

| FB pin bias current                        | Iref               |                                            |         | 50    | 200  | nA   |

| On resistance                              | Ron                | CBOOT=5V                                   |         | 80    |      | mΩ   |

| Soft start current                         | ISS                |                                            | 3       | 6.5   | 13   | μΑ   |

| Oscillation frequency                      | Fosc               |                                            | 145     | 180   | 225  | kHz  |

| Maximum on duty ratio                      | D max              |                                            | 85      |       |      | %    |

| Current limiting value                     | lcl                |                                            | 4.1     |       |      | А    |

| Under voltage detection                    | VI                 |                                            | 3.3     | 3.7   | 4.2  | V    |

| Under voltage detection hysteresis         | Vlh                |                                            | 0.15    | 0.185 | 0.25 | V    |

| Thermal shutdown temperature               | Ttsd               | Design guarantee value*                    |         | 180   |      | °C   |

| Thermal shutdown temperature<br>hysteresis | Dtsd               | Design guarantee value*                    |         | 20    |      | °C   |

\*These are design guarantee values and no measurements are made.

## Package Dimensions

unit : mm (typ) 3313

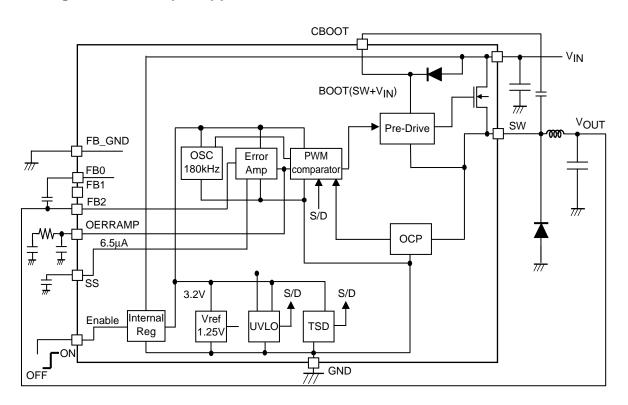

## **Block Diagram and Sample Application Circuits**

\*The capacitor between the FB0 and V<sub>OUT</sub> pins and capacitor between the OERRAMP pin and GND (the capacitors shown inside the broken lines in the diagram) are used for phase compensation. Their capacitance is intended to stop oscillation when oscillation is caused by the status of the output capacitor. As such, they can be left open under normal circumstances.

## **Pin Functions**

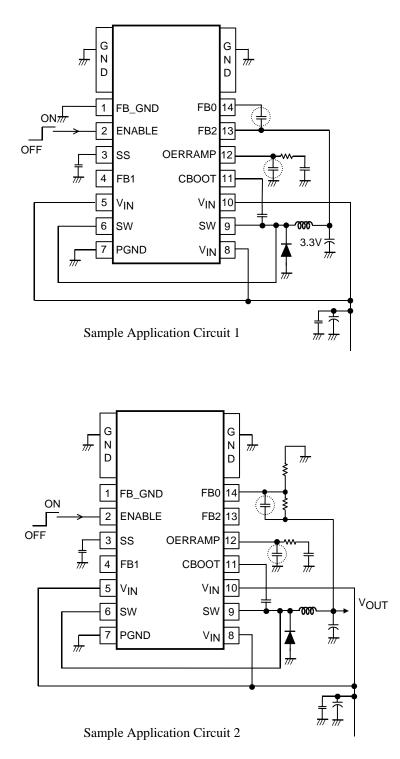

| Pin No.       | Pin name | Description                                                                                                                                                                                                                                                 |  |  |  |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

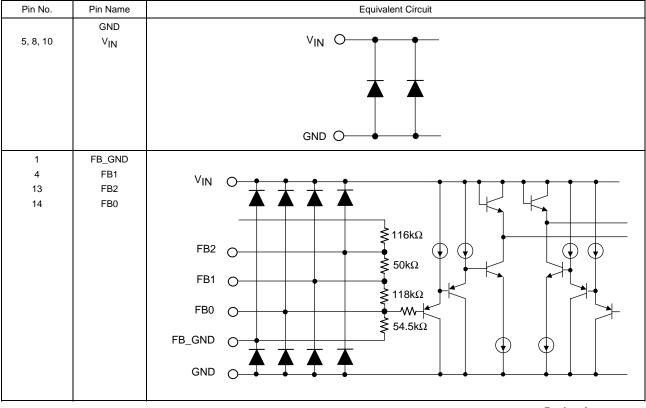

| 1             | FB_GND   | GND of output voltage setting pins FB0 and FB2. It is connected to GND for use when pin FB2 is used.                                                                                                                                                        |  |  |  |

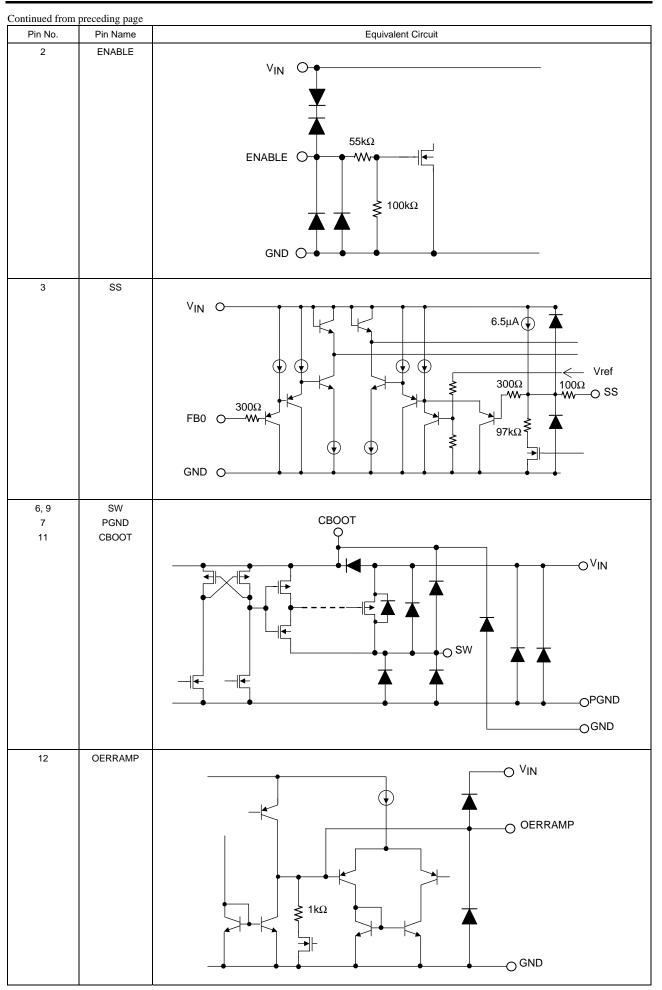

| 2             | ENABLE   | Output ON/OFF with an active-high polarity. When set to L, the current consumption is reduced to $10\mu A$ less.                                                                                                                                            |  |  |  |

| 3             | SS       | Soft start time constant setting. The charge current is set to approx. $6.5\mu$ A and when a capacitor of $0.1\mu$ F connected between this pin and GND, the output rises in approx. 12ms.                                                                  |  |  |  |

| 4             | FB1      | Test pin for verifying the internal reference voltage. It must be set to open for actual use.                                                                                                                                                               |  |  |  |

| 5, 8, 10      | VIN      | Power input. It is used with voltages ranging from 4.5V to 6V.                                                                                                                                                                                              |  |  |  |

| 6, 9          | SW       | Inductor drive output                                                                                                                                                                                                                                       |  |  |  |

| 7             | PGND     | Power GND pin. This is the output GND. It is connected so that where at all possible, no impedance is shared with other GND pins (GND, FB_GND).                                                                                                             |  |  |  |

| 11            | CBOOT    | For generating the gate voltage of the internal high-side n-channel MOS transistor. A capacitor with a capacitance of at least $0.1\mu$ F (max. $2.2\mu$ F) is connected between this pin and the SW pin for use.                                           |  |  |  |

| 12            | OERRAMP  | Transconductance-type Error_Amp output. An integration constant is provided between this pin and GND to implement phase compensation.                                                                                                                       |  |  |  |

| 13            | FB2      | Used to feed back the output voltage to this pin when the output voltage is to be set to 3.3V. In such a case, FB_GND is connected to GND. Refer to application circuit 1.                                                                                  |  |  |  |

| 14            | FB0      | When the output voltage is to be set to a desired value, connect resistors between FB0 and GND and between FB0 and V <sub>OUT</sub> to feed back the output voltage to this pin. In such a case, leave FB_GND and FB2 open. Refer to application circuit 2. |  |  |  |

| Heat sink fin | GND      | Analog GND (connected to GND).                                                                                                                                                                                                                              |  |  |  |

## **Input Equivalent Circuits**

Continued on next page

LV5781

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employeer. This literature is subject to all applicable copyright laws and is not for resale in any manner.