# High Safety, Latched Mode, GreenLine<sup>™</sup> PWM Controller for (Multi) Synchronized Applications

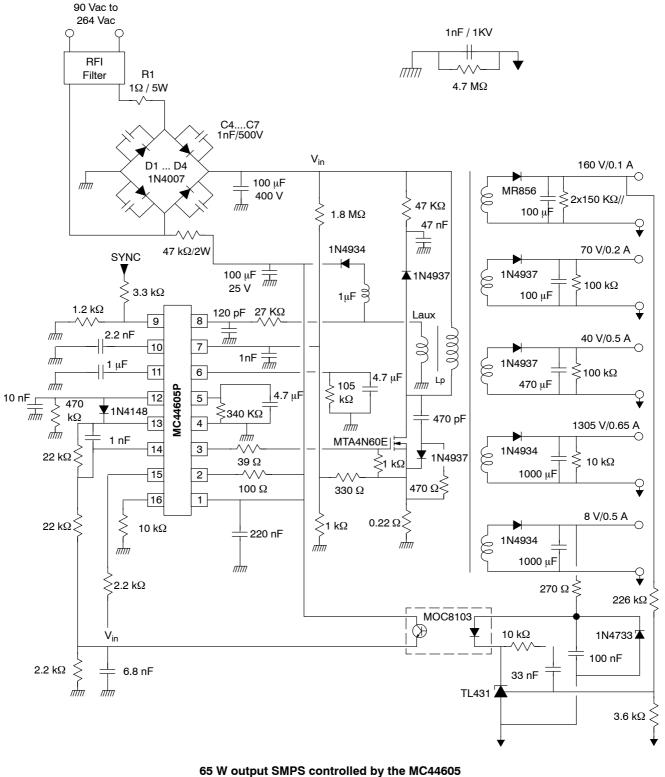

The MC44605 is a high performance current mode controller that is specifically designed for off-line converters. This circuit has several distinguishing features that make it particularly suitable for multisynchronized monitor applications.

The MC44605 synchronization arrangement enables operation from 16 kHz up to 130 kHz. This product was optimized to operate with universal mains voltage, i.e., from 80 V to 280 V, and its high current totem pole output makes it ideally suited for driving a power MOSFET.

The MC44605 protections enable a well–controlled and safe power management. Four major faults while detected, activate the analogic counter of a disabling block designed to perform a latched circuit output inhibition.

### Features

• This is a Pb-Free Device\*

## **Current Mode Controller**

- Current Mode Operation up to 250 kHz Output Switching Frequency

- Inherent Feed Forward Compensation

- Latching PWM for Cycle-by-Cycle Current Limiting

- Oscillator with Precise Frequency Control

- Externally Programmable Reference Current

- Secondary or Primary Sensing (Availability of Error Amplifier Output)

- Synchronization Facility

- High Current Totem Pole Output

- V<sub>cc</sub> Undervoltage Lockout with Hysteresis

- Low Output dV/dT for Low EMI Radiations

## • Low Startup and Operating Current

- Safety/Protection Features

- Soft-Start Feature

- Demagnetization (Zero Current Detection) Protection

- Overvoltage Protection Facility against Open Loop

- EHT Overvoltage Protection (E.H.T.OVP): Detection of too High Synchronization Pulses

- Winding Short Circuit Detection (W.S.C.D.)

- Limitation of the Maximum Input Power (M.P.L.): Calculation of Input Power for Overload Protection

- Overheating Detection (O.H.D.): to Prevent the Power Switch from an Excessive Heating

## Latched Disabling Mode

- When one of the following faults is detected: EHT overvoltage, Winding Short Circuit (WSCD), a too high input power (M.P.L.), power switch overheating (O.H.D.), an analogic counter is activated

- If the counter is activated for a time that is long enough, the circuit gets definitively disabled. The latch can only be reset by making decrease the  $V_{cc}$  down to about 3.0 V, i.e., practically by unplugging or turning off the SMPS.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# **ON Semiconductor®**

http://onsemi.com

- WL = Wafer Lot

- YY = Year

- WW = Work Week

- G = Pb-Free Package

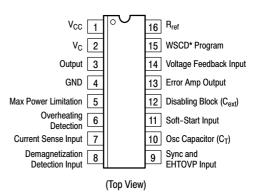

## **PIN CONNECTIONS**

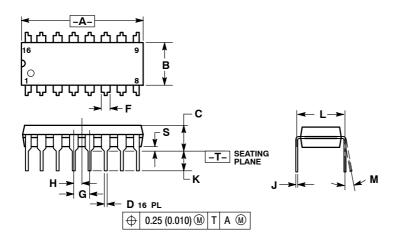

## **ORDERING INFORMATION**

| Device    | Package              | Shipping      |

|-----------|----------------------|---------------|

| MC44605PG | PDIP-16<br>(Pb-Free) | 25 Units/Rail |

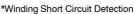

## **Block Diagram**

## **MAXIMUM RATINGS**

| Rating                                                                                                                                     | Pin #  | Symbol                                                         | Value         | Unit      |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------|---------------|-----------|

| Total Power Supply and Zener Current                                                                                                       |        | (I <sub>CC</sub> + I <sub>Z</sub> )                            | 40            | mA        |

| Output Supply Voltage with Respect to Ground                                                                                               | 2<br>1 | V <sub>C</sub><br>V <sub>CC</sub>                              | 18            | V         |

| Output Current<br>Source<br>Sink                                                                                                           | 3      | I <sub>O(Source)</sub><br>I <sub>O(Sink)</sub>                 | -750<br>750   | mA        |

| Output Energy (Capacitive Load per Cycle)                                                                                                  |        | W                                                              | 5.0           | μJ        |

| Soft-Start                                                                                                                                 |        | V <sub>SS</sub>                                                | –0.3 to 2.2 V | V         |

| Current Sense, Voltage Feedback, E/A Output, C <sub>T</sub> , R <sub>ref</sub> , MPL, OHD, C <sub>ext</sub> , WSCD                         |        | V <sub>in</sub>                                                | –0.3 to 5.5 V | V         |

| E.H.T.OVP, Sync Input Current                                                                                                              |        |                                                                |               | mA        |

| Source                                                                                                                                     | 9<br>6 | I <sub>sync</sub> (Source)<br>I <sub>EHT</sub> (Source)        | -4.0          |           |

| Sink                                                                                                                                       | 9<br>6 | l <sub>sync</sub> (Sink)<br>I <sub>EHT</sub> (Sink)            | 10            |           |

| Demagnetization Detection Input Current<br>Source<br>Sink                                                                                  | 8      | l <sub>demag-ib (Source)</sub><br>I <sub>demag-ib (Sink)</sub> | -4.0<br>10    | mA        |

| Error Amplifier Output Sink Current                                                                                                        | 13     | I <sub>E/A</sub> (Sink)                                        | 20            | mA        |

| Power Dissipation and Thermal Characteristics<br>Maximum Power Dissipation at T <sub>A</sub> = 85°C<br>Thermal Resistance, Junction-to-Air |        | P <sub>D</sub><br>R <sub>θJA</sub>                             | 0.6<br>100    | W<br>°C/W |

| Operating Junction Temperature                                                                                                             |        | TJ                                                             | 150           | °C        |

| Operating Ambient Temperature                                                                                                              |        | T <sub>A</sub>                                                 | -25 to +85    | °C        |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

**ELECTRICAL CHARACTERISTICS** (V<sub>CC</sub> and V<sub>C</sub> = 12 V, R<sub>ref</sub> = 10 k $\Omega$ , C<sub>T</sub> = 2.2 nF, for typical values T<sub>A</sub> = 25°C, for min/max values T<sub>A</sub> = -25° to +85°C unless otherwise noted.) (Note 1)

| Characteristic                                                                                                                                                                                                                                                                | Pin # | Symbol                             | Min         | Тур                      | Max                      | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------|-------------|--------------------------|--------------------------|------|

| OUTPUT SECTION (Note 2)                                                                                                                                                                                                                                                       |       |                                    |             |                          |                          |      |

| Output Voltage (Note 3)       (I <sub>Sink</sub> = 100 mA)         Low Level Drop Voltage       (I <sub>Sink</sub> = 500 mA)         High Level Drop Voltage       (I <sub>Source</sub> = 200 mA)         (I <sub>Source</sub> = 500 mA)       (I <sub>Source</sub> = 500 mA) | 3     | V <sub>OL</sub><br>V <sub>OH</sub> | -<br>-<br>- | 1.0<br>1.4<br>1.5<br>2.0 | 1.2<br>2.0<br>2.0<br>2.7 | V    |

| Output Voltage During Initialization Phase $V_{CC} - 0$ to 1.0 V, $I_{Sink} = 10 \ \mu A$ $V_{CC} - 1.0$ to 5.0 V, $I_{Sink} = 100 \ \mu A$ $V_{CC} - 5.0$ to 13 V, $I_{Sink} = 1.0 \ \mu A$                                                                                  |       | V <sub>OL</sub>                    | -<br>-<br>- | _<br>0.1<br>0.1          | 1.0<br>1.0<br>1.0        | V    |

| Output Voltage Rising Edge Slew-Rate (C <sub>L</sub> = 1.0 nF, T <sub>J</sub> = 25°C)                                                                                                                                                                                         |       | dVo/dT                             | -           | 300                      | -                        | V/µs |

| Output Voltage Falling Edge Slew-Rate (C <sub>L</sub> = 1.0 nF, T <sub>J</sub> = $25^{\circ}$ C)                                                                                                                                                                              |       | dVo/dT                             | -           | -300                     | -                        | V/μs |

1. Adjust V<sub>CC</sub> above the startup threshold before setting to 12 V. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

2. No output signal when the Error Amplifier output is in Low State, i.e., when for instance,  $V_{FB} = 2.7 \text{ V}$ . 3.  $V_C$  must be greater than 5.0 V.

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>CC</sub> and V <sub>C</sub> = 12 V, $R_{ref}$ = 10 k $\Omega$ , C <sub>T</sub> = 2.2 nF, for typical values T <sub>A</sub> = 25°C, for the typical values T <sub>A</sub> = 25°C, for typical values T <sub>A</sub> = 25°C, | r |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|

| min/max values $T_A = -25^{\circ}$ to +85°C unless otherwise noted.) (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |  |  |

| Characteristic                                                                                                                                                                                                                                                                                                                                   | Pin #  | Symbol                                   | Min         | Тур        | Max        | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------|-------------|------------|------------|------|

| ERROR AMPLIFIER SECTION                                                                                                                                                                                                                                                                                                                          | •      |                                          |             | •          |            |      |

| Voltage Feedback Input (V <sub>E/A out</sub> = 2.5 V)                                                                                                                                                                                                                                                                                            | 14     | V <sub>FB</sub>                          | 2.4         | 2.5        | 2.6        | V    |

| Input Bias Current (V <sub>FB</sub> = 2.5 V)                                                                                                                                                                                                                                                                                                     | 14     | I <sub>FB-ib</sub>                       | -2.0        | -0.6       | -          | μA   |

| Open Loop Voltage Gain (V <sub>E/A out</sub> = 2.0 V to 4.0 V)                                                                                                                                                                                                                                                                                   |        | A <sub>VOL</sub>                         | 65          | 70         | _          | dB   |

| Unity Gain Bandwidth<br>$T_J = 25^{\circ}C$<br>$T_A = -25^{\circ}$ to +85°C                                                                                                                                                                                                                                                                      |        | BW                                       |             |            | _<br>5.5   | MHz  |

| Voltage Feedback Input Line Regulation ( $V_{CC}$ = 10 V to 15 V)                                                                                                                                                                                                                                                                                |        | V <sub>FBline-reg</sub>                  | -10         | -          | 10         | mV   |

| $\begin{array}{l} \text{Output Current} \\ \text{Sink (V}_{E/A \ out} = 1.5 \ \text{V}, \ \text{V}_{FB} = 2.7 \ \text{V}) \\ \text{T}_A = -25^\circ \ \text{to} \ +85^\circ \text{C} \\ \text{Source (V}_{E/A \ out} = 5.0 \ \text{V}, \ \text{V}_{FB} = 2.3 \ \text{V}) \\ \text{T}_A = -25^\circ \ \text{to} \ +85^\circ \text{C} \end{array}$ | 13     | I <sub>Sink</sub><br>I <sub>Source</sub> | 2.0<br>-2.0 | 12<br>-    | -<br>-0.2  | mA   |

| $\begin{array}{l} \text{Output Voltage Swing} \\ \text{High State (I}_{\text{E/A out (source)}} = 0.5 \text{ mA, V}_{\text{FB}} = 2.3 \text{ V}) \\ \text{Low State (I}_{\text{E/A out (sink)}} = 0.33 \text{ mA, V}_{\text{FB}} = 2.7 \text{ V}) \end{array}$                                                                                   | 13     | V <sub>OH</sub><br>V <sub>OL</sub>       | 5.5<br>_    | 6.5<br>1.0 | 7.5<br>1.1 | V    |

| CURRENT SENSE SECTION                                                                                                                                                                                                                                                                                                                            | -<br>- |                                          |             |            |            |      |

| Maximum Current Sense Input Threshold<br>(V <sub>Feedback (pin14)</sub> = 2.3 V and V <sub>Soft-Start (pin11)</sub> = 1.2 V)                                                                                                                                                                                                                     | 7      | V <sub>cs-th</sub>                       | 0.96        | 1.0        | 1.04       | V    |

| Input Bias Current                                                                                                                                                                                                                                                                                                                               | 7      | I <sub>cs-ib</sub>                       | -10         | -2.0       | _          | μA   |

| Propagation Delay (Current Sense Input to Output at $V_{TH} \mbox{ of MOS}$ transistor = 3.0 V)                                                                                                                                                                                                                                                  |        | t <sub>PLH(In/Out)</sub>                 | -           | 120        | 200        | ns   |

| OSCILLATOR AND SYNCHRONIZATION SECTION                                                                                                                                                                                                                                                                                                           |        |                                          |             | •          |            |      |

| Frequency (T <sub>A</sub> = $-25^{\circ}$ to $+85^{\circ}$ C)                                                                                                                                                                                                                                                                                    |        | F <sub>OSC</sub>                         | 16          | -          | 20         | kHz  |

| Frequency Change with Voltage ( $V_{CC}$ = 10 V to 15 V)                                                                                                                                                                                                                                                                                         |        | $\Delta F_{OSC} / \Delta V$              | -           | 0.05       | -          | %/V  |

| Frequency Change with Temperature (T <sub>A</sub> = $-25^{\circ}$ to $+85^{\circ}$ C)                                                                                                                                                                                                                                                            |        | $\Delta F_{OSC} / \Delta T$              | -           | 0.05       | -          | %/°C |

| Ratio Charge Current/Reference Current (T <sub>A</sub> = $-25^{\circ}$ to $+85^{\circ}$ C)                                                                                                                                                                                                                                                       |        | I <sub>charge</sub> /I <sub>ref</sub>    | 0.39        | -          | 0.48       | -    |

| Free Mode Oscillator Ratio = I <sub>discharge</sub> /(I <sub>discharge</sub> + I <sub>charge</sub> )                                                                                                                                                                                                                                             |        | D                                        | 72          | 75         | 78         | %    |

| Synchronization Input Threshold Voltage                                                                                                                                                                                                                                                                                                          | 9      | V <sub>syncth</sub>                      | -250        | -200       | -150       | mV   |

| Negative Clamp Level (I <sub>syncth-in</sub> = 2.0 mA)                                                                                                                                                                                                                                                                                           |        | NEG-SYNC                                 | -0.65       | -0.5       | -0.34      | V    |

| UNDERVOLTAGE LOCKOUT SECTION                                                                                                                                                                                                                                                                                                                     |        |                                          |             | •          |            | •    |

| Startup Threshold                                                                                                                                                                                                                                                                                                                                | 1      | V <sub>stup-th</sub>                     | 13.6        | 14.5       | 15.4       | V    |

| Disable Voltage After Threshold Turn–On (UVLO 1) $(T_A = -25^{\circ} \text{ to } +85^{\circ}\text{C})$                                                                                                                                                                                                                                           | 1      | V <sub>disable1</sub>                    | 8.3         | -          | 9.6        | V    |

| Disable Voltage After Threshold Turn–On (UVLO 2) $(T_A = -25^{\circ} \text{ to } +85^{\circ}\text{C})$                                                                                                                                                                                                                                           | 1      | V <sub>disable2</sub>                    | 7.0         | 7.5        | 8.0        | V    |

|                                                                                                                                                                                                                                                                                                                                                  |        |                                          |             |            |            |      |

Adjust V<sub>CC</sub> above the startup threshold before setting to 12 V. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>CC</sub> and V <sub>C</sub> = 12 V, R <sub>ref</sub> = 10 k $\Omega$ , C <sub>T</sub> = 2.2 nF, for typical values T <sub>A</sub> = 25°C, for |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| min/max values $T_A = -25^{\circ}$ to +85°C unless otherwise noted.) (Note 5)                                                                                                           |

| Characteristic                                                                                                                                                                                             | Pin # | Symbol                                                                     | Min             | Тур            | Max          | Unit           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------|-----------------|----------------|--------------|----------------|

| REFERENCE SECTION                                                                                                                                                                                          | •     | •                                                                          | -               | •              | •            |                |

| Reference Output Voltage ( $V_{CC}$ = 10 V to 15 V)                                                                                                                                                        | 16    | V <sub>ref</sub>                                                           | 2.4             | 2.5            | 2.6          | V              |

| Reference Current Range (I <sub>ref</sub> = V <sub>ref</sub> /R <sub>ref</sub> , R = 5.0 k to 25 k $\Omega$ )                                                                                              | 16    | I <sub>ref</sub>                                                           | -500            | -              | -100         | μA             |

| Reference Voltage Over Iref Range                                                                                                                                                                          |       | $\Delta V_{ref}$                                                           | -40             | -              | 40           | mV             |

| DEMAGNETIZATION DETECTION SECTION (Note 6)                                                                                                                                                                 |       |                                                                            |                 | •              | •            |                |

| Demagnetization Detect Input<br>Demagnetization Comparator Threshold (V <sub>pin9</sub> Decreasing)<br>Propagation Delay (Input to Output, Low to High)<br>Input Bias Current (V <sub>demag</sub> = 65 mV) | 8     | V <sub>demag-th</sub><br>t <sub>PLH(In/Out)</sub><br>I <sub>demag-Ib</sub> | 50<br>_<br>_0.5 | 65<br>0.5<br>– | 80<br>-<br>- | mV<br>μs<br>μA |

| Minimum Off-Time when the pin 8 is grounded                                                                                                                                                                |       | T <sub>DEM-GND</sub>                                                       | 1.5             | 3.0            | 4.5          | μs             |

| Negative Clamp Level (I <sub>demag</sub> = -2.0 mA)                                                                                                                                                        |       | CLVL-neg                                                                   | -0.50           | -0.38          | -0.25        | V              |

| Positive Clamp Level (I <sub>demag</sub> = +2.0 mA)                                                                                                                                                        |       | CLVL-pos                                                                   | 0.50            | 0.72           | 0.85         | V              |

| SOFT-START SECTION (Note 7)                                                                                                                                                                                | ·     |                                                                            |                 |                |              |                |

| Ratio Charge Current/I <sub>ref</sub> (T <sub>A</sub> = $-25^{\circ}$ to $+85^{\circ}$ C)                                                                                                                  |       | I <sub>ss-ch</sub> /I <sub>ref</sub>                                       | 0.37            | -              | 0.43         | -              |

| Discharge Current (V <sub>soft-start</sub> = 1.0 V)                                                                                                                                                        |       | I <sub>discharge</sub>                                                     | 1.5             | 5.0            | -            | mA             |

| Clamp Level                                                                                                                                                                                                |       | V <sub>SS-CLVL</sub>                                                       | 2.2             | 2.4            | 2.6          | V              |

| Circuit Inhibition Threshold (Note 8)                                                                                                                                                                      |       | V <sub>SSinhi</sub>                                                        | 30              | -              | 150          | mV             |

| $V_{CS}$ Soft–Start Clamp Level ( $R_{soft-start} = 5 \text{ k}\Omega$ )                                                                                                                                   |       | V <sub>CSsoft-start</sub>                                                  | 0.45            | 0.5            | 0.55         | V              |

| OVERVOLTAGE SECTION                                                                                                                                                                                        |       |                                                                            |                 | •              | •            | •              |

| Propagation Delay ( $V_{CC}$ > 18.1 V to $V_{out}$ Low)                                                                                                                                                    |       | T <sub>PHL(In/Out)</sub>                                                   | 1.0             | -              | 4.0          | μs             |

| Protection Level on $V_{CC}$ (T <sub>A</sub> = -25° to +85°C)                                                                                                                                              |       | V <sub>CC prot</sub>                                                       | 15.9            | -              | 18.1         | V              |

| EHT OVP SECTION (Note 9)                                                                                                                                                                                   | ·     |                                                                            |                 |                |              |                |

| Negative Clamp Level (I <sub>synch-in</sub> = -2.0 mA)                                                                                                                                                     |       | NEG-SYN<br>C                                                               | -0.65           | -0.5           | -0.35        | V              |

| EHT OVP Input Threshold                                                                                                                                                                                    |       | V <sub>ref</sub>                                                           | 7.0             | 7.4            | 7.8          | V              |

| EHT OVP Input Bias Current (V <sub>EHT OVP(pin 9)</sub> = 0 V)                                                                                                                                             | 9     | I <sub>EHTOVP</sub>                                                        | -5.0            | -              | 0            | μΑ             |

| WINDING SHORT CIRCUIT DETECTION SECTION                                                                                                                                                                    |       |                                                                            |                 | •              | •            |                |

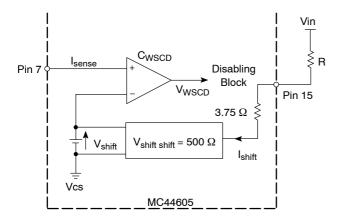

| WSCD Threshold with $I_{pin15} = 200 \ \mu A$                                                                                                                                                              |       | Vshift                                                                     | 70              | 100            | 120          | mV             |

| MPL & OHD SECTION                                                                                                                                                                                          |       |                                                                            |                 | •              | •            |                |

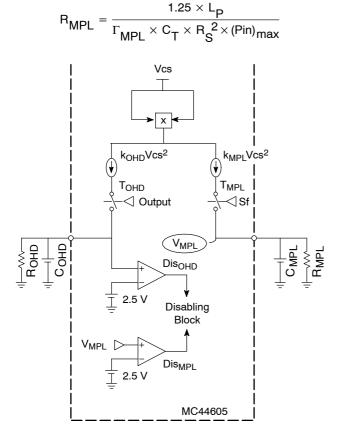

| MPL Parameter (Note 10)                                                                                                                                                                                    |       | $\Gamma_{MPL}$                                                             | 0.185           | 0.240          | 0.295        | V-1            |

| MPL Comparator Threshold (Note 11)                                                                                                                                                                         |       | V <sub>MPL-th</sub>                                                        | 2.4             | 2.5            | 2.6          | V              |

| OHD Parameter (Note 12)                                                                                                                                                                                    |       | Г <sub>ОНD</sub>                                                           | 1.15            | 1.50           | 1.85         | V-1            |

| OHD Comparator Threshold (Note 13)                                                                                                                                                                         |       | V <sub>OHD-th</sub>                                                        | 2.4             | 2.5            | 2.6          | V              |

5. Adjust V<sub>CC</sub> above the startup threshold before setting to 12 V. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

6. This function can be inhibited by connecting pin 8 to GND. In this case, there is a minimum off-time equal to T<sub>DEM-GND</sub>.

7. The MC44605 can be shut down by connecting soft-start pin (pin 11) to GND.

8. The circuit is shutdown if the soft-start pin voltage is lower than this level.

9. This function can be inhibited by connecting pin 9 to GND. In this case, the synchronization block is inhibited too and the MC44605 works in free mode.

10. This parameter is defined in the MPL §. This parameter is obtained by measuring the MPL pin average current and dividing this result by the corresponding squared V<sub>CS</sub>, the measured frequency value and the C<sub>T</sub> value deducted from the measured frequency value. Measurement conditions:  $V_{Feedback(pin 14)} = 2.3 \text{ V}$ ,  $V_{soft-start(pin 11)} = 0.5 \text{ V}$  and pins 7, 8, and 9 connected to GND (the working frequency is typically equal to 18 kHz -  $R_{ref} = 10 \text{ k}\Omega \pm 1\%$ ,  $C_T = 2.2 \text{ nF}$ ).

11. The MPL comparator output is Dis<sub>MPL</sub>.

12. This parameter is defined in the OHD §. This parameter is obtained by measuring the OHD pin average current and dividing this result by the corresponding squared V<sub>CS</sub> value and multiplying it by the R<sub>ref</sub> value.

Measurement conditions:  $V_{Feedback(pin 14)} = 2.3 \text{ V}$ ,  $V_{soft-start(pin 11)} = 0.5 \text{ V}$  and pins 7, 8, and 9 connected to GND (the working frequency is typically equal to 18 kHz -  $R_{ref} = 10 \text{ k}\Omega \pm 1\%$ ,  $C_T = 2.2 \text{ nF}$ ).

13. The OHD comparator output is DisOHD.

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>CC</sub> and V <sub>C</sub> = 12 V, R <sub>ref</sub> = 10 k $\Omega$ , C <sub>T</sub> = 2.2 nF, for typical values T <sub>A</sub> = 25°C, for |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| min/max values $T_A = -25^{\circ}$ to +85°C unless otherwise noted.) (Note 14)                                                                                                          |  |

| Characteristic                                                       |  | Symbol                               | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------------------|--|--------------------------------------|------|------|------|------|

| DISABLING BLOCK SECTION                                              |  |                                      |      |      |      |      |

| Delay Pulse Width                                                    |  | T <sub>WSCD</sub>                    | -    | 4.0  | -    | μs   |

| Ratio (EHTOVP and WSCD Disabling Capacitor Charge Current) $I_{ref}$ |  | I <sub>Dis-H</sub> /I <sub>ref</sub> | 90   | 100  | 110  | %    |

| Ratio (MPL and OHD Disabling Capacitor Charge Current)Iref           |  | I <sub>Dis-L</sub> /I <sub>ref</sub> | 2.7  | 3.1  | 3.5  | %    |

| Minimum $V_{CC}$ Value Enabling the Disabling Block Latch (Note 15)  |  | V <sub>CCDis</sub>                   | 1.0  | -    | 5.0  | V    |

| TOTAL DEVICE                                                         |  |                                      | •    | •    |      |      |

| Power Supply Current                                                 |  | I <sub>CC</sub>                      |      |      |      | mA   |

| Startup–Up ( $V_{CC}$ = 5.0 V with $V_{CC}$ increasing)              |  |                                      | -    | 0.35 | 0.55 |      |

| Startup–Up ( $V_{CC}$ = 9.0 V with $V_{CC}$ increasing)              |  |                                      | -    | 0.35 | 0.55 |      |

| Startup–Up ( $V_{CC}$ = 12 V with $V_{CC}$ increasing)               |  |                                      | -    | 0.35 | 0.55 |      |

| Operating $T_A = -25^{\circ}C$ to +85°C (Note 16)                    |  |                                      | -    | 20   | 25   |      |

| Disabling Mode ( $V_{CC} = 6.0 \text{ V}$ ) (Note 17)                |  |                                      | -    | -    | 0.55 |      |

| Power Supply Zener Voltage (I <sub>CC</sub> = 35 mA)                 |  | VZ                                   | 18.5 | -    | -    | V    |

| Thermal Shutdown                                                     |  | _                                    | -    | 155  | -    | °C   |

14. Adjust V<sub>CC</sub> above the startup threshold before setting to 12 V. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

15. Once a fault detection activated it, the Disabling Block Latch gets reset when the V<sub>CC</sub> becomes lower than this threshold.

16. Refer to Note 14.

17. This consumption is measured while the circuit is inhibited by the Definitive Latch.

| Pin | Name                                             | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>CC</sub>                                  | This pin is the positive supply of the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2   | V <sub>C</sub>                                   | The output high state, $V_{OH}$ , is set by the voltage applied to this pin. With a separate connection to the power source, it gives the possibility to set by means of an external resistor the output source current at a different value than the sink current.                                                                                                                                                                                                                                                                                                       |

| 3   | Output                                           | The output current capability is suited for driving a power MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4   | GND                                              | The ground pin is a single return typically connected back to the power source. It is used as control and power ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5   | Maximum Power Limitation                         | This block enables to estimate the input power. When this calculated power is detected as too high, a fault information is sent to the disabling block in order to definitively disable the circuit.                                                                                                                                                                                                                                                                                                                                                                      |

| 6   | Over-Heating Detection                           | This block estimates the MOSFET heating. When this calculated heating is too high, the device gets definitively disabled (disabling block action).                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7   | Current Sense Input                              | A voltage proportional to the current flowing into the power switch is connected to this input.<br>The PWM latch uses this information to terminate the conduction of the output buffer. A<br>maximum level of 1 V allows to limit the inductor current.                                                                                                                                                                                                                                                                                                                  |

| 8   | Demagnetization Detection                        | A voltage delivered by an auxiliary transformer winding provides to the demagnetization pin<br>an indication of the magnetization state of the flyback energy reservoir. A zero voltage<br>detection corresponds to a complete core demagnetization. The demagnetization detection<br>prevents the oscillator from a re-start and so the circuit from a new conduction phase, if the<br>fly-back is not in a dead-time state. This function can be inhibited by connecting Pin 8 to<br>GND but in this case, there is a minimum off-time typically equal to 3 µs.         |

| 9   | Synchronization and<br>E.H.T.OVP Input           | Activating the synchronization input pin with a pulse higher or equal to the negative threshold (typically –200 mV) allows the next switching period to be reinitialized. The oscillator is free when connecting Pin 9 to GND. When the E.H.T.OVP pin receives a voltage that is greater than 7.5 V, the disabling block $C_{ext}$ capacitor is charged so that the circuit gets definitively disabled if the $C_{ext}$ voltage becomes higher than $V_{ref}$ . This block is incorporated to detect and disable the device when the synchronization pulses are too high. |

| 10  | Oscillator Capacitor C <sub>T</sub>              | The free mode oscillator frequency is programmed by the capacitor $C_T$ choice together with the $R_{ref}$ resistance value. $C_T$ , connected between pin 10 and GND, generates the oscillator sawtooth.                                                                                                                                                                                                                                                                                                                                                                 |

| 11  | Soft-Start                                       | A capacitor connected to this pin can temporary reduce the maximum inductor peak<br>current. By this way, a soft-start can be performed. By connecting pin 11 to Ground, the<br>MC44605 is shutdown.                                                                                                                                                                                                                                                                                                                                                                      |

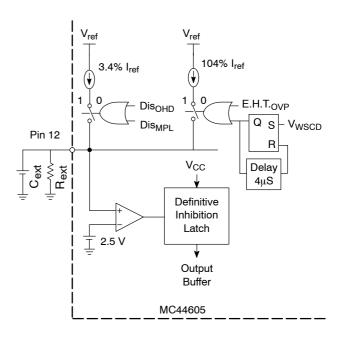

| 12  | C <sub>ext</sub> (Disabling Block)               | When a too high synchronization pulse voltage (E.H.T.OVP) or a winding short circuit (WSCD) is detected, the capacitor $C_{ext}$ is charged using a current source $I_{Dis-H}$ . In the case of a MPL or OHD fault detection, $C_{ext}$ is charged using $I_{Dis-L}$ . If the $C_{ext}$ capacitor voltage gets higher than $V_{ref}$ , the circuit is definitively disabled. Then, to re-start, the converter must be switched off in order to make $V_{CC}$ decrease down to about 0 V.                                                                                  |

| 13  | E/A Output                                       | The error amplifier output is made available for loop compensation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14  | Voltage Feedback                                 | This is the inverting input of the Error Amplifier. It can be connected to the Switching Mode Power Supply output through an optical (or else) feedback loop or to the subdivided $V_{CC}$ voltage in case of primary sensing technic.                                                                                                                                                                                                                                                                                                                                    |

| 15  | Winding Short Circuit<br>Detection Programmation | The W.S.C.D. block is incorporated to detect the transformer Winding Short Circuits. This function is performed by detecting the inductor overcurrents thanks to a comparator which threshold is programmable to be well adapted to any application.                                                                                                                                                                                                                                                                                                                      |

| 16  | R <sub>ref</sub>                                 | The R <sub>ref</sub> value fixes the internal reference current that is particularly used to perform the precise oscillator waveform. The current range goes from 100 $\mu$ A up to 500 $\mu$ A.                                                                                                                                                                                                                                                                                                                                                                          |

|     |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## **Summary of the Main Design Equations**

The following table consists of equations enabling to dimension a multisynchronized SMPS operating in discontinuous mode.

| _                                                                                                                                                       | Pout <sub>max</sub> is the maximum power the load may draw in normal working.                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $Pin_{max} = \frac{Pout_{max}}{\eta}$                                                                                                                   | The maximum input power $Pin_{max}$ is easily deducted by dividing $Pout_{max}$ by the efficiency ( $\eta$ ). In this kind of application, the efficiency is generally taken equal to 80%.                                                                      |

| [√2·Vac <sub>min</sub> ×NVo] <sup>2</sup>                                                                                                               | The inductor value Lp must be chosen lower than Lp <sub>max</sub> or ideally equal to this value (to optimize the application design–in).                                                                                                                       |

| $Lp_{max} = \frac{\left[\frac{\sqrt{2} \cdot Vac_{min} \times NVo}}{\sqrt{2} \cdot Vac_{min} + NVo}\right]^{2}}{2 \times Pin_{max} \times fsync_{max}}$ | In effect, if Lp was higher than Lp <sub>max</sub> , a synchronized and discontinuous working could not be guaranteed (in some cases, the demagnetization phase would not be finished while a new conduction phase should start to follow the synchronization). |

| $lpk_{max} = \sqrt{\frac{2 \times Pin_{max}}{L \times fsync_{min}}}$                                                                                    | Ipk <sub>max</sub> is the maximum inductor peak current. This current is obtained when the power to transfer is maximum at the minimum synchronization frequency (60 W output, 30 kHz in the proposed application).                                             |

| $d_{\text{max}} = \frac{\sqrt{Pin_{\text{max}} \times Lp \times fsync_{\text{max}}}}{Vac_{\text{min}}}$                                                 | ${\rm d}_{\rm max}$ is the maximum duty cycle. The duty cycle is maximum at the lowest input voltage when the power demand is maximum while the synchronization frequency also is maximum.                                                                      |

| $Pon_{max} = \frac{1}{3} \times Rds_{on} \times Ipk_{max}^2 \times d_{max}$                                                                             | $Pon_{max}$ is the maximum MOSFET on-time losses that are proportional to $Ipk_{max}, d_{max}$ and $Rds_{on}$ (on-time MOSFET resistor).                                                                                                                        |

|                                                                                                                                                         | This conduction losses estimation enables to dimension the power MOSFET.                                                                                                                                                                                        |

| $(V_{DS}) \max = (\sqrt{2} \times Vac_{max}) + (N \times Vout)$                                                                                         | $(V_{DS})$ max is the maximum voltage the power switch must be able to face. In fact, this calculation does not take into account the turnings off spikes. So, it is necessary to take a margin of at least about 50 V.                                         |

| $(V_D) \max = \left(\sqrt{2} \times \frac{Vac_{max}}{N}\right) + Vout$                                                                                  | $(V_D)$ max is the maximum voltage the high voltage secondary diode must be able to face. Because of the turning off spikes, a margin must also be taken.                                                                                                       |

|                                                                                                                                                         | (A <sub>L</sub> ) and (ni) are the magnetic parameters.                                                                                                                                                                                                         |

| $(ni)_{max} = N \times n_{Vout} \times lpk_{max}$                                                                                                       | (ni) <sub>max</sub> must not exceed the ferrite (ni). Otherwise, the transformer may get saturated when the peak current is high.                                                                                                                               |

| $A_{L} = \frac{L_{P}}{(N \times n_{Vout})^{2}}$                                                                                                         | (A <sub>L</sub> ) is the ferrite constant that links the primary inductor value to the squared number of primary turns: Lp = A <sub>L</sub> x $n_p^2$ .                                                                                                         |

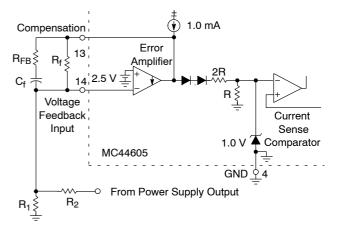

### **Error Amplifier**

A fully compensated Error Amplifier with access to the inverting input and output is provided. It features a typical DC voltage gain of 70 dB. The non inverting input is internally biased at 2.5 V and is not pinned out. The converter output voltage is typically divided down and monitored by the inverting input at 2.5 V is  $-2.0 \,\mu$ A. This can cause an output voltage error that is equal to the product of the input bias current and the equivalent input divider source resistance.

Figure 1. Error Amplifier Compensation

The Error Amp Output (Pin 13) is provided for external loop compensation. The output voltage is offset by two diodes drops ( $\approx$  1.4 V) and divided by three before it connects to the inverting input of the Current Sense Comparator. This guarantees that no drive pulses appear at the Source Output (Pin 3) when Pin 13 is at its lowest state (V<sub>OL</sub>). This occurs when the power supply is operating and the load is removed, or at the beginning of a soft–start interval. The Error Amp minimum feedback resistance is limited by the amplifier's minimum source current (0.2 mA) and the required output voltage (V<sub>OH</sub>) to reach the current sense comparator's 1.0 V clamp level:

R1(min) =

$$\frac{(3 \times 1 \text{ V}) + 1.4 \text{ V}}{0.2 \text{ mA}}$$

= 22 kΩ

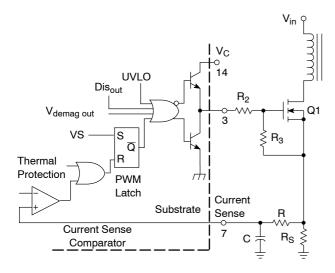

#### **Current Sense Comparator and PWM Latch**

The MC44605 operates as a current mode controller. The circuit uses a current sense comparator to compare the inductor current to the threshold level established by the Error Amplifier output (Pin 13). When the current reaches the threshold, the current sense comparator terminates the output switch conduction that has been initiated by the oscillator, by resetting the PWM Latch. Thus the error signal controls the peak inductor current on a cycle–by–cycle basis. This configuration ensures that only one single pulse appears at the Source Output during the appropriate oscillator cycle.

Figure 2. Output Totem Pole

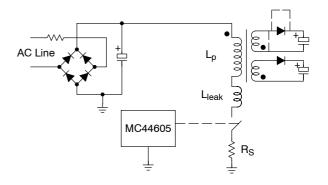

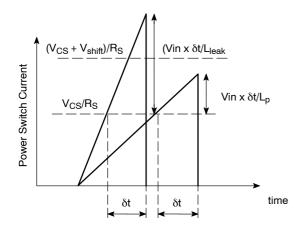

The inductor current is converted to a voltage by inserting the ground referenced sense resistor  $R_S$  in series with the power switch Q1.

This voltage is monitored by the Current Sense Input (Pin 7) and compared to a level derived from the Error Amp output. The peak inductor current under normal operating conditions is controlled by the voltage at Pin 13 where:

$$I_{pk} \approx \frac{V_{(pin13)} - 1.4 \text{ V}}{3 \times \text{ R}_{S}}$$

The Current Sense Comparator threshold is internally clamped to 1.0 V. Therefore the maximum peak switch current is:

$$I_{pk(max)} = \frac{1 V}{R_S}$$

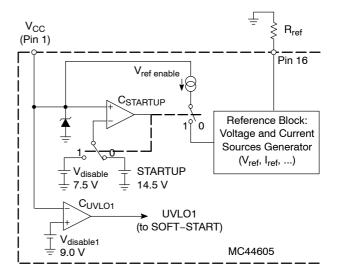

#### **Undervoltage Lockout Section**

As depicted in Figure 3, an undervoltage lockout has been incorporated to guarantee that the IC is fully functional before allowing the system working.

In effect, the  $V_{CC}$  is connected to the non inverting input of a comparator that has an upper threshold equal to 14.5 V (typical  $V_{stup-th}$ ) and a lower one equal to 7.5 V (typical  $V_{disable 2}$ ). This hysteresis comparator enables or disables the reference block that generates the voltage and current sources required by the system.

This block particularly, produces  $V_{ref}$  (pin 16 voltage) and  $I_{ref}$  that is determined by the resistor  $R_{ref}$  connected between pin 16 and the ground:

$$I_{ref} = \frac{V_{ref}}{R_{ref}}$$

where  $V_{ref} = 2.5 V$  (typically)

Figure 3. V<sub>CC</sub> Management

In addition to this,  $V_{CC}$  is compared to a second threshold level that is nearly equal to 9.0 V ( $V_{disable1}$ ) so that a signal UVLO1 is generated to reset the soft-start block and so, to disable the output stage (refer to the Soft-Start §) as soon as  $V_{CC}$  becomes lower than  $V_{disable 1}$ . In this way, the circuit is reset and made ready for a next startup, before the reference block is disabled (refer to Figure 3). Thus, finally the upper limit for the minimum normal operating voltage is 9.4 V (maximum value of  $V_{disable 1}$ ) and so the minimum hysteresis is 4.2 V. [( $V_{stup-th}$ )min = 13.6 V].

The large hysteresis and the low startup current of the MC44605 make it ideally suited for off-line converter applications where efficient bootstrap startup techniques are required.

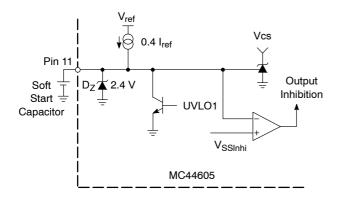

#### Soft-Start Control Section

The V<sub>cs</sub> value is clamped down to the pin 11 voltage.

So, if a capacitor is connected to this pin, its voltage increases slowly at the startup (the capacitor is charged by an internal current source  $0.4 I_{ref}$ ). So,  $V_{cs}$  is limited during the startup and then a soft–start is performed.

This pin can be used to inhibit the circuit by applying a voltage that is lower than  $V_{SSinhi}$  (refer to page 4). Particularly, the MC44605 can be shutdown by connecting the soft-start pin to ground.

As soon as  $V_{dis1}$  is detected (that is  $V_{cc}$  lower than  $V_{disable1}$ ), a signal UVLO1 is generated until the  $V_{cc}$  falls down to  $V_{dis2}$  (refer to the undervoltage lockout section §). During the delay between the disable1 and the disable2, using a transistor controlled by UVLO1, the pin 11 voltage is made equal to zero in order to make the soft-start arrangement ready to work for the next re-start.

Figure 4. Soft-Start

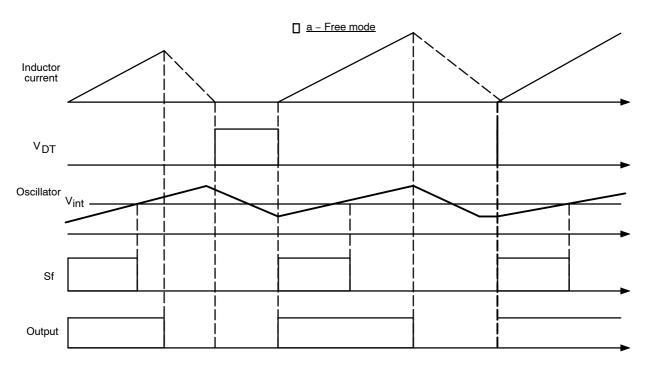

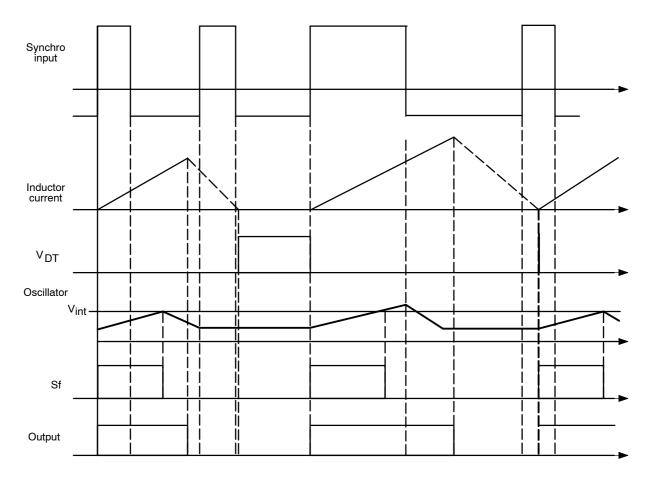

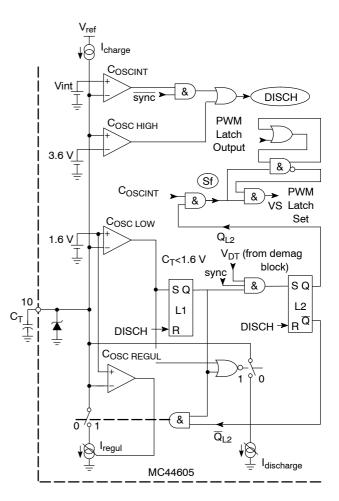

#### Oscillator Section (Figures 5 & 5b)

The oscillator and synchronization behavior is represented in Figure 5b.

The MC44605 oscillator achieves four functions:

- it fixes the free mode frequency

- it takes into account the synchronization signal

- it does not allow a new power switch conduction if the flyback is not in a dead-time state when the circuit works in demagnetization mode (pin 8 connected)

- it builds the Sf pulse required by the MPL block During the operating mode, the oscillator sawtooth can

vary between a valley value (1.6 V typically) and a peak one (3.6 V typically) and presents three distinct phases:

- the C<sub>T</sub> charge

- the  $C_T$  discharge

- the phase during which the oscillator voltage is maintained equal to its valley value. This happens at the end of a discharge cycle when the synchronization or demagnetization condition does not allow a new  $C_T$ charge phase. During this sequence,  $I_{REGUL}$ compensates the charge current  $I_{charge}$ .

The oscillator has two working modes:

- a free one when there is no synchronization

- a synchronized one.

In the free working, the oscillator grows up from its valley value to its peak one for the charge phase and when once the peak value is reached, a discharge sequence makes the  $C_T$  voltage decrease down to its valley value. When the decrease phase is finished, a new charge cycle occurs if the demagnetization condition is achieved ( $V_{DT}$  high). Otherwise there is a REGUL phase until  $V_{DT}$  gets high.

In the synchronized mode, the charge cycle is only allowed when the synchronization signal gets high while a dead time has been detected ( $V_{DT}$  high). This charge phase is stopped when the synchronization signal has got low and when the oscillator voltage is higher than  $V_{int}$ , the intermediary voltage level used to generate the calibrated pulse Sf by comparing the  $C_T$  voltage to this threshold. So, when these two conditions are performed, a discharge sequence is set until the oscillator voltage is maintained constant thanks to the "REGUL" arrangement until the next synchronization pulse.

In both cases, during the charge phase, a signal  $V_S$  is generated. When Sf becomes high.  $V_S$  gets high and remains in this state until the PWN latch is set of Sf is low. Then,  $V_S$ keeps low until the next Sf high level. This oscillator behavior is obtained using the process described in Figure 5b.

## b – Synchronized mode

In effect, the output of the latch L1 is:

- high during the oscillator capacitor charge and during the REGUL phase

- low for the oscillator capacitor discharge

Now, the latch L2 is set when the L1 output is high and the synchronization condition is performed (that is: sync = 1 -free mode or synchro signal high state) and during the dead-time (V<sub>DT</sub> high). So, this latch is set for the C<sub>T</sub> charge.

On the other hand, this latch is reset by the signal used to reset L1. Consequently, it is reset at the end of the charge phase.

- So, in any case, Q<sub>L2</sub> is:

- high during the C<sub>T</sub> charge cycle

- low in the other cases

Thus, this latch enables to obtain a signal that is high for the charge phase and low in the other cases, whatever the mode (synchronized or free) and whatever the synchronization pulses width (higher than the delay necessary for the oscillator to reach its intermediary value or lower than this delay) in the synchronized mode.

That is why:

- the discharge current source must be connected to the oscillator capacitor when  $Q_{L1}$  is low. The condition ( $C_T$  voltage higher than the valley value) is added to stop the discharge phase as soon as the oscillator voltage is detected as lower than the valley value (without any delay due to the L1 latch propagation time).

- the REGUL current source must be connected when:

- Q<sub>L1</sub> is high (charge or REGUL phase)

- $Q_{L2}$  is low (the oscillator is not in a charge phase) On the other hand, the oscillator charge is stopped when:

- the oscillator voltage reaches the peak value in the free mode

- the oscillator voltage is higher than the intermediary value (V<sub>int</sub>) and the synchronization signal is negative, in the synchronized mode.

Consequently, in any case,  $Q_{L2}$  that is high during the oscillator charge phase, is high for the delay during which the oscillator voltage grows from the valley value up to the intermediary one. That is why the signal Sf (refer to the MPL block) that must be high when the oscillator voltage is between the valley value and the intermediary one during the charge phase ( $Q_{L2}$  high), is obtained using an AND gate with the following inputs:

- Q<sub>L2</sub> (Q<sub>L2</sub> high <=> charge phase)

- C<sub>OSCINT</sub> (C<sub>OSCINT</sub> high <=> the C<sub>T</sub> voltage is lower than the intermediary value).

So, using the output of this AND gate, Sf is obtained.

This signal Sf is connected to a logic block consisting of two AND gates and an OR one. This block aims at supplying a signal VS that:

- gets high as soon as Sf becomes high if the PWM latch output is low

- gets low as soon as the PWM latch is set and then remains low until the next cycle.

Figure 5. Oscillator

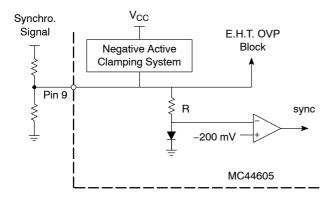

#### Synchronization Section (Note 1)

The synchronization block consists of a protection arrangement similar to the demagnetization block one (a diode + a negative active clamping system (Note 2)). In addition to this, a high value resistor (R – about 50 k $\Omega$ ) is incorporated as the pin 9 input is also used by the EHTOVP section.

The signal obtained at the output of this protection arrangement, is compared to a negative threshold (-200 mV, typically) so that when the synchronization pulse applied to the pin 9 (through a resistor or a resistors divider to adapt this input to the EHTOVP function), is higher than this threshold, the system considers that the synchronization condition is performed (free mode or synchronization signal high level).

- Note 1. The synchronization can be inhibited by connecting the pin 9 to the ground. By this means, a free mode is obtained.

- Note 2. This negative active clamping system works even if the circuit is off. This feature is really useful as synchronization pulses may be applied while the product is off.

Figure 6. Synchronization

#### **Demagnetization Section**

This block is incorporated to detect the complete core demagnetization in order to prevent the power MOSFET from switching on if the converter is not in a dead time phase. That is why this block inhibits any oscillator re-start as long as the inductor current is not finished (from the beginning of the on-time to the end of the demagnetization phase).

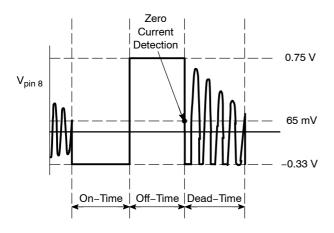

In a fly–back, a good means to detect the demagnetization phase consists in using the  $V_{CC}$  winding voltage. In effect, this voltage is:

- negative during the on-time,

- positive during the off-time,

- equal to zero for the dead-time with generally a ringing (refer to Figure 7).

Figure 7. Demagnetization Detection

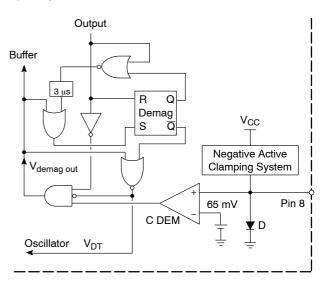

That is why, the MC44605 demagnetization detection consists of a comparator that compares the  $V_{CC}$  winding voltage to a reference that is typically equal to 65 mV.

A diode D is incorporated to clamp the positive applied voltages while an active clamping system limit the negative voltages to typically -0.33 V. This negative clamp level is high enough to avoid the substrate diode switching on.

A latch system is incorporated to keep the demagnetization block output level low as soon as a voltage lower than 65 mV is detected and as long as a new restart is produced (high level on the output (refer to Figure 8). This process avoids that any ringing on the signal used on the pin 8, disrupts the demagnetization detection (refer to Figure 7). Finally, this method results in a very accurate demagnetization phase detection, and the signal  $V_{DT}$  drawn from this block is high only for the dead time. Therefore, an oscillator re–start and so, a new power switch conduction is only allowed during the dead–time.

For a higher safety, the  $V_{demagout}$  output of the demagnetization block is also directly connected to the output, to disable it during the demagnetization phase (refer to the block diagram).

The demagnetization detection can be inhibited by connecting pin 8 to the ground but in this case, a timer (about  $3 \mu s$ ) that is incorporated to set the latch when it can not be set by V<sub>demagout</sub>, results in a minimum off-time (refer to Figure 8).

Figure 8. Demagnetization Block

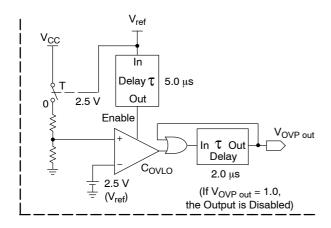

#### **Overvoltage Protection Section**

The overvoltage arrangement compares a portion  $V_{cc}$  to  $V_{ref}$  (2.5 V) (refer to Figure 9). In fact, this threshold corresponds to a  $V_{CC}$  equal to to 17 V. When the  $V_{cc}$  is higher than this level, the output is latched off until a new circuit re-start.

**Figure 9. Overvoltage Protection**

A delay (2  $\mu$ s) is incorporated in order to avoid any activation due to interferences by only taking into account the overvoltages that last at least 2  $\mu$ s.

The  $V_{CC}$  is connected when once the circuit has started-up in order to limit the circuit startup consumption (T is switched on when once  $V_{ref}$  has been generated).

The overvoltage section is enabled 5  $\mu$ s after the regulator has started to allow the reference V<sub>ref</sub> to stabilize.

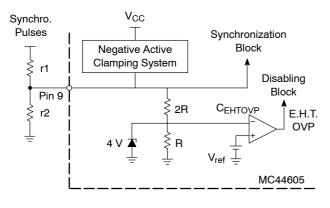

#### E.H.T. Overvoltage Protection Section

This block uses the synchronization input as this section is incorporated to detect too high synchronization pulses and then to activate the device definitive latch in this case.

Figure 10. E.H.T. OVP

This block consists of a high impedance resistors bridge (R is nearly equal to 50 k $\Omega$  – refer to Figure 10) so that the EHTovp threshold is 7.5 V. So, using an external resistors bridge (r1, r2 <<R), the synchronization pulse level above which the working must be considered as wrong, can be adjusted.

For instance, if this threshold value is required to be equal to 30 V,  $V_{\text{pin9}}$  must be equal to 7.5 V when the synchronization pulse value is 30 V.

So, in this case:

and:

$$30 \times \frac{r2}{r1 + r2} = 7.5$$

Then, the ratio (r1/r2) can be deducted:

$$\frac{r1}{r2} = 3$$

So, as r1 and r2 must be negligible in relation to R (about 50 k $\Omega$ ), the couple of resistors can be chosen as follows:

$r2 = 1 k\Omega$